息山员

# Band-pass filter for spectral analyzers BA3830S

The BA3830S is a 6+1 band band-pass filter for spectral analyzer displays with internal recording indicator output. All of the capacitors comprising the filter are internal capacitors, making it possible to significantly reduce the number of attached components. This enables configuration of compact sets with a high level of reliability.

### Applications

CD radio cassette players, mini-components, car stereos

### Features

- 1) Six internal band-pass filters for spectral analyzers

- 2) Internal input/output for recording indicators

- Internal capacitors reduce the number of attachments.

### ● Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol | Limits          | Unit |  |

|-----------------------|--------|-----------------|------|--|

| Power supply voltage  | Vcc    | 9               | V    |  |

| Power dissipation     | Pd     | 600*            | mW   |  |

| Operating temperature | Topr   | <b>−25~+75</b>  | C    |  |

| Storage temperature   | Tstg   | <b>−55~+150</b> | °C   |  |

<sup>\*</sup> Reduced by 6.0mW for each increase in Ta of 1°C over 25°C.

### ● Recommended operating conditions (Ta = 25°C)

| Parameter                      | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------|--------|------|------|------|------|

| Operating power supply voltage | Vcc    | 4.5  | _    | 8.0  | ٧    |

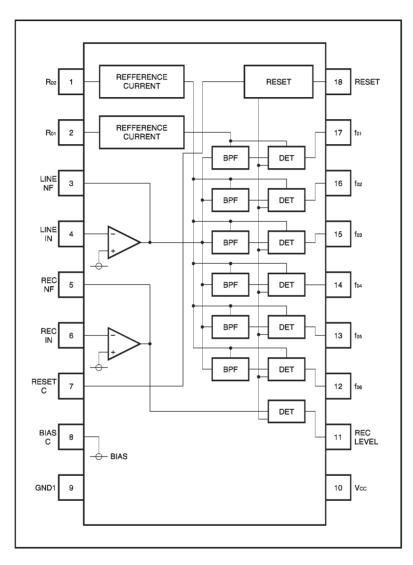

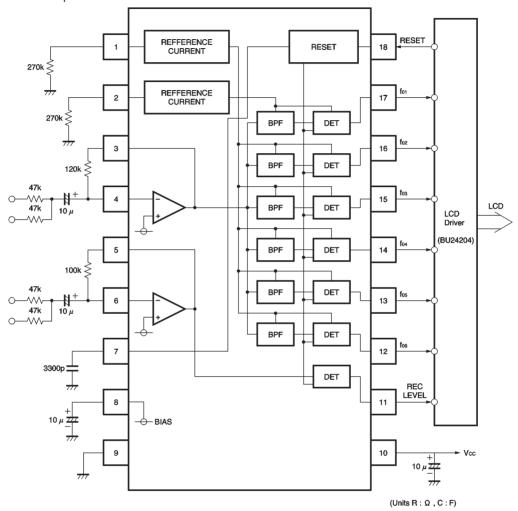

# ●Block diagram

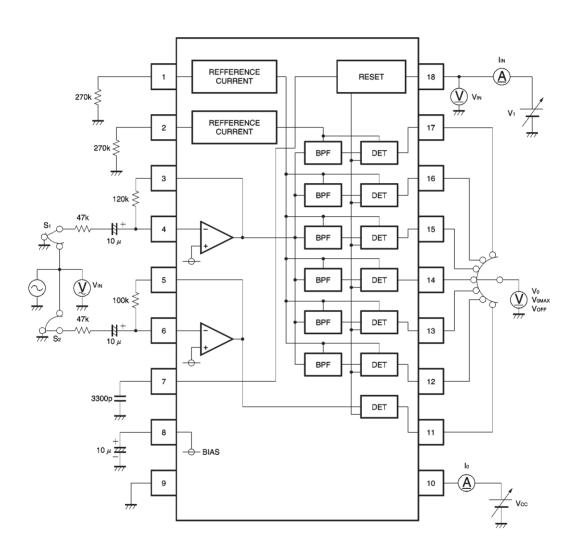

•Electrical characteristics (unless otherwise noted, Ta = 25 °C, Vcc = 5V, RL = 10MΩ, R $\phi$ 1 = 270kΩ, R $\phi$ 2 = 270kΩ)

| Parameter                             | Symbol      | Min. | Тур. | Max. | Unit | Coniditions                                                                     |

|---------------------------------------|-------------|------|------|------|------|---------------------------------------------------------------------------------|

| Quiescent current                     | lo          | _    | 3.8  | 5.2  | mA   |                                                                                 |

| Reference output level (LEVEL)        | Vol         | -3   | 0    | 3    | dB   | V <sub>IN</sub> =−30dBV,<br>V₀=1.5V (0dB)<br>When f=center frequencies is input |

| Max. output level (LEVEL)             | Volmax      | 3.2  | 4.2  | _    | ٧    | V <sub>IN</sub> =-14dBV,<br>When f=center frequencies is input                  |

| Reference output level (REC LEVEL)    | Vor         | -3   | 0    | 3    | dB   | V <sub>IN</sub> =−30dBV,<br>V <sub>o</sub> =1.5V (0dB)<br>f=1kHz                |

| Max. output level<br>(REC LEVEL)      | Volmax      | 3.8  | 4.8  | _    | ٧    | V <sub>IN</sub> =-14dBV, f=1kHz                                                 |

| Output offset voltage                 | Voff        | _    | 30   | 90   | mV   | With no signal                                                                  |

| Center frequency 1                    | fo1         | 49   | 63   | 77   | Hz   | V <sub>IN</sub> =-30dBV                                                         |

| Center frequency 2                    | <b>f</b> 02 | 117  | 150  | 183  | Hz   | V <sub>IN</sub> =-30dBV                                                         |

| Center frequency 3                    | foз         | 257  | 330  | 403  | Hz   | V <sub>IN</sub> =-30dBV                                                         |

| Center frequency 4                    | <b>f</b> 04 | 0.78 | 1    | 1.22 | kHz  | V <sub>IN</sub> =-30dBV                                                         |

| Center frequency 5                    | <b>f</b> 05 | 2.55 | 3.3  | 4.03 | kHz  | V <sub>IN</sub> =-30dBV                                                         |

| Center frequency 6                    | fo6         | 7.8  | 10   | 12.2 | kHz  | V <sub>IN</sub> =-30dBV                                                         |

| Input current when Reset pin is HIGH  | lin         | 150  | 215  | 280  | μΑ   | V <sub>IN</sub> =5V                                                             |

| Threshold level when Reset pin is ON  | Vth         | _    | 1.4  | 1.8  | ٧    |                                                                                 |

| Threshold level when Reset pin is OFF | Vth         | 1.0  | 1.4  | _    | ٧    |                                                                                 |

<sup>\*</sup>Q is set to 4.5.

ONot designed for radiation resistance.

### Measurement circuit

Fig.1

### Circuit operation

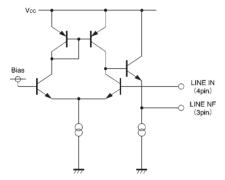

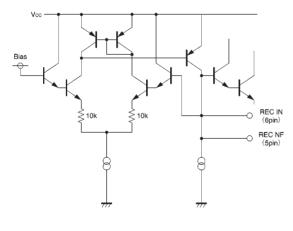

# (1) LINE and REC input circuits

The LINE and REC input circuits are configured as differential amplifiers, and the gain can be set to any desired value using an external resistor. The input impedance is determined by the external resistor.

(Note: All resistance values in the internal circuit diagrams noted here are reference values.)

Fig.2

Fig.3

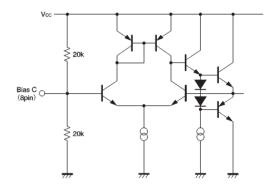

### (2) Bias circuit

A bias voltage of Vcc/2 is applied to each of the circuits. Since the output stage uses a push-pull configuration, a stable bias source can be obtained.

(Note: All resistance values in the internal circuit diagrams noted here are reference values.)

Fig.4

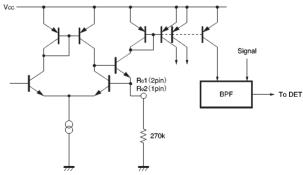

# (3) BPF circuit

This is a circuit that selects the required frequency component from the input signal and amplifies it. With this configuration, no external capacitor is needed. In addition, the center frequency is set based on the current, so for and for to for can be set individually, using separate external resistors (pins1 and 2).

Q is set to 4.5V (Typ.).

Fig.5

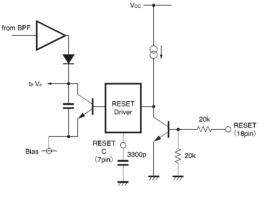

### (4) DET circuit

This circuit carries out phase detection on the signal selected and amplified by the BPF, and holds it at the peak level. It is configured so that all of the capacitors are internal.

The charge that was charged by the internal capacitors in the DET circuit is set to be discharged at 75ms/V (Typ.), but in order to eliminate any effects of disparity, a reset circuit is also included.

Fig.6

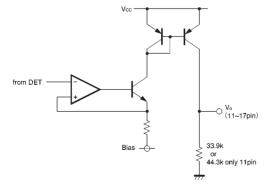

# (5) Output section circuit

The signal level held at peak level by the DET undergoes V/I conversion and is output. Since the next stage supports MOS (high-input impedance), there is a resistance of  $33.9 k\Omega$  (44.3k $\Omega$  for REC output only) between the output pin and the GND in the IC, so the output value changes based on the input impedance.

Fig.7

# Application example

Fig.8

### Operation notes

- (1) Precautions concerning the load resistance The various characteristics were measured at the output resistance value of  $10M\Omega$  noted in the specifications manual. Moreover, because the output of this IC supports the MOS configuration, be aware that it is current output, and the output changes depending on the input impedance at the next stage.

- (2) Precautions concerning the RESET capacitor If the reset function is to be used, a capacitor of at least 3300pF is required for RESET C (pin 7). Failing to connect this capacitor can result in erroneous displays, so make sure a sufficient capacitance is provided.

(3) Precautions concerning the coupling capacitor When determining the polarity of the input electrolytic coupling capacitor, the potential relation with the other end of the coupling must be taken into consideration.

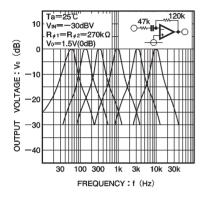

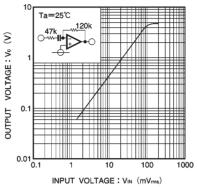

### Electrical characteristic curves

Fig.9 Output vs. frequency

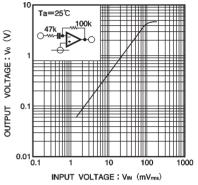

Fig.10 Input vs. output level (for to foe modes)

Fig.11 Input vs. output level (REC mode)

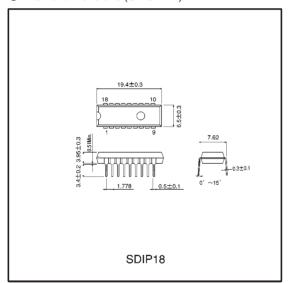

# ●External dimensions (Units: mm)