19-3121: Rev 0: 1/04 **EVALUATION KIT AVAILABLE**

#

# Dual, 300mA, Low-Noise Linear Regulator with Independent Shutdown in UCSP or TDFN

### **General Description**

The MAX8559 dual, low-noise, low-dropout (LDO) linear regulator operates from a 2.5V to 6.5V input voltage and delivers at least 300mA of continuous output current. It offers low output noise and low dropout of only 60mV at 100mA. Typical output noise for this device is 32µV<sub>RMS</sub>, and PSRR is 70dB at 10kHz. Designed with an internal P-channel MOSFET pass transistor, the MAX8559 maintains a low 115µA supply current per LDO, independent of the load current and dropout voltage. Other features include short-circuit protection and thermal-shutdown protection. The MAX8559 includes two independent logic-controlled shutdown inputs and is capable of operating without a bypass capacitor to further reduce total solution size. The MAX8559 is available in a miniature 8-bump UCSP (2mm x 1mm) or 8-pin TDFN (3mm x 3mm) package.

### **Applications**

Cellular and Cordless Phones

PDAs and Palmtop Computers

Notebook Computers

Digital Cameras

**PCMCIA Cards**

Wireless LAN Cards

Hand-Held Instruments

# **Features**

- Two Low-Dropout-Voltage Regulators

- ♦ Low 32µVRMs Output Noise

- 300mA Output Current for Each LDO

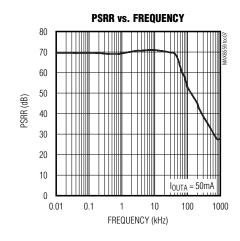

- 70dB PSRR at 10kHz

- ♦ Independent Shutdown Controls

- ♦ Low 60mV Dropout at 100mA Load

- ♦ 115µA Operating Supply Current per LDO

- ♦ 1.5V to 3.3V Factory-Preset Output

- ♦ Small Ceramic Output Capacitors

- Output Current Limit

- ◆ Thermal-Overload and Short-Circuit Protection

- ◆ 1.95W Power-Dissipation Capability (TDFN)

- ♦ 2mm² Footprint (UCSP)

### **Ordering Information**

| PART           | TEMP RANGE     | PIN-PACKAGE   |

|----------------|----------------|---------------|

| MAX8559EBAxy*† | -40°C to +85°C | 8 UCSP (B8-1) |

| MAX8559ETAxy*  | -40°C to +85°C | 8 TDFN-EP**   |

<sup>\*</sup>xy = Output voltage code (see the Output Voltage Selector Guide).

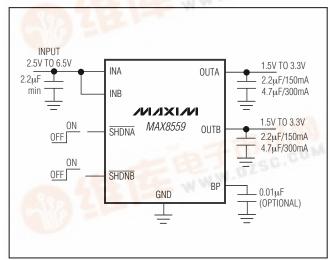

# Typical Operating Circuit

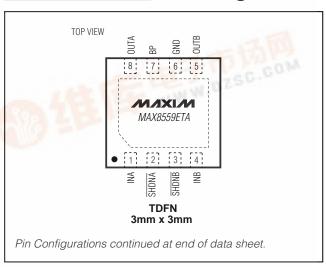

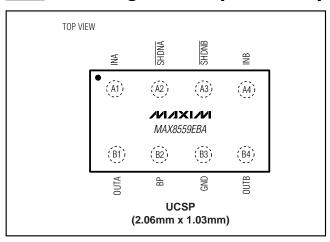

## **Pin Configurations**

Output Voltage Selector Guide appears at end of data sheet.

Maxim Integrated Products 1

<sup>\*\*</sup>EP = Exposed pad.

<sup>†</sup>Future product—contact factory for availability.

#### **ABSOLUTE MAXIMUM RATINGS**

| INA, INB, SHDNA, SHDNB, BP to GND0.3V to +7V          |

|-------------------------------------------------------|

| INA to INB0.3V to +0.3V                               |

| OUTA, OUTB to GND0.3V to (V <sub>IN</sub> + 0.3V)     |

| Output Short-Circuit DurationContinuous               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| 8-Bump UCSP (derate 4.7mW/°C above +70°C)379mW        |

| 8-Pin TDFN (derate 24.4mW/°C above +70°C)1951mW       |

| Operating Temperature Range             |                |

|-----------------------------------------|----------------|

| Junction Temperature                    | +150°C         |

| Storage Temperature Range               | 65°C to +150°C |

| 8-Pin TDFN Lead Temperature (soldering, | 10s)+300°C     |

| 8-Bump UCSP Solder Profile              | (Note 1)       |

Note 1: For UCSP solder profile information, please refer to the application note APP\_1891 on the Maxim website, www.maxim-ic.com.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.8V, \overline{SHDNA} = \overline{SHDNB} = IN_, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                      | SYMBOL             | CON                                                                       | DITIONS                                       | MIN   | TYP  | MAX   | UNITS |

|--------------------------------|--------------------|---------------------------------------------------------------------------|-----------------------------------------------|-------|------|-------|-------|

| Input Voltage                  | V <sub>IN</sub>    |                                                                           |                                               | 2.5   |      | 6.5   | V     |

| Undervoltage-Lockout Threshold | $V_{UVLO}$         | V <sub>IN</sub> rising, hysteresis                                        | s is 40mV (typ)                               | 2.15  | 2.35 | 2.45  | V     |

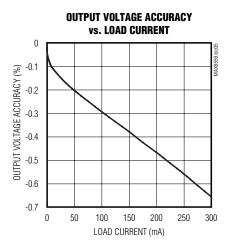

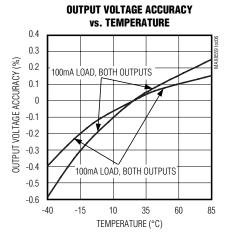

|                                |                    | $T_A = +25^{\circ}C$ , $I_{OUTA} =$                                       | = I <sub>OUTB</sub> = 1mA                     | -1    |      | +1    |       |

| Output Voltage Accuracy        |                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                             | $C$ , $I_{OUTA} = I_{OUTB} = 1mA$             | -2    |      | +2    | %     |

| Output Vollage Accuracy        |                    | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$<br>0.1mA to 300mA     | C, IOUTA or IOUTB =                           | -3    |      | +3    | /0    |

| Maximum Output Current         | lout_              |                                                                           |                                               | 300   |      |       | mA    |

| Output Current Limit           | I <sub>LIM</sub> _ |                                                                           |                                               | 310   | 550  | 920   | mA    |

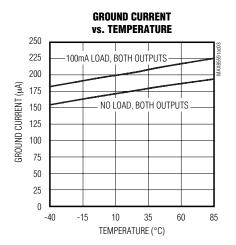

|                                |                    | No load                                                                   |                                               |       | 180  | 290   |       |

| Ground Current                 | IQ                 | No load, one LDO st                                                       | hutdown                                       |       | 115  |       | μΑ    |

|                                |                    | I <sub>OUTA</sub> = I <sub>OUTB</sub> = 100                               | DmA                                           |       | 220  |       |       |

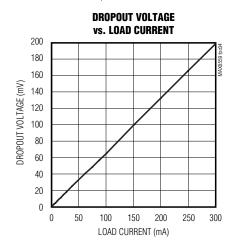

| Dropout Voltage                | Vout               | $I_{OUT} = 1mA$                                                           |                                               |       | 0.6  |       | mV    |

| (Note 2)                       | V <sub>IN</sub> _  | $I_{OUT} = 100mA$                                                         |                                               |       | 60   | 120   | IIIV  |

| Line Regulation                | $\Delta V_{LNR}$   | $V_{IN} = (V_{OUT} + 0.1)$                                                | V) to 6.5V, $I_{OUT} = 1mA$                   | -0.15 | 0    | +0.15 | %/V   |

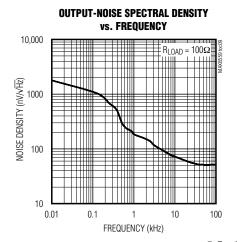

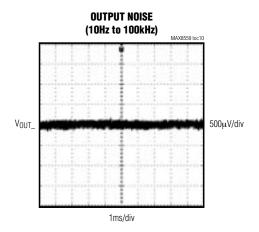

| Outro d Walte va Naisa         |                    | 100Hz to 100kHz, Color                                                    |                                               |       | 32   |       |       |

| Output Voltage Noise           |                    | 100Hz to 100kHz, C<br>I <sub>OUT</sub> = 1mA, C <sub>BP</sub> =           |                                               |       | 254  |       | μVRMS |

|                                |                    | V <sub>IN</sub> _ = V <sub>OUT</sub> _ + 1V,<br>C <sub>BP</sub> = 0.01µF, | 10kHz                                         |       | 70   |       |       |

| Power-Supply Ripple Rejection  | PSRR               | C <sub>OUT</sub> = 2.2µF,<br>I <sub>OUT</sub> = 50mA                      | 100kHz                                        |       | 54   |       | dB    |

| SHUTDOWN                       |                    |                                                                           |                                               |       |      |       |       |

| Charteless Coursely Coursely   | 1.                 | SHDN_ = 0V                                                                | T <sub>A</sub> = +25°C                        |       | 0.01 | 1     |       |

| Shutdown Supply Current        | ISHDN              | 2טחט\_ = 0\                                                               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |       | 0.1  |       | μΑ    |

| SHDN Input Threshold           | VIH                | Input high voltage                                                        |                                               | 1.6   |      |       | V     |

| אטחא ווויףענ דוויפאווטוע  <br> | VIL                | Input low voltage                                                         |                                               |       |      | 0.4   | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.8V, \overline{SHDNA} = \overline{SHDNB} = IN_, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                           | SYMBOL            | CON                   | DITIONS                    | MIN | TYP  | MAX | UNITS |

|-----------------------------------------------------|-------------------|-----------------------|----------------------------|-----|------|-----|-------|

| CLIDN Input Dies Current                            | launu             | SHDN_ = IN or         | $T_A = +25^{\circ}C$       |     | 10   | 100 | nA    |

| SHDN Input Bias Current                             | ISHDN             | GND                   | $T_A = -40$ °C to $+85$ °C |     | 100  |     | ΠA    |

| V <sub>OUT</sub> _ Discharge Resistance in Shutdown |                   | SHDN_ = GND           |                            |     | 385  |     | Ω     |

| THERMAL PROTECTION                                  |                   |                       |                            |     |      |     |       |

| Thermal-Shutdown Temperature                        | T <sub>SHDN</sub> | T <sub>J</sub> rising |                            |     | +160 |     | °C    |

| Thermal-Shutdown Hysteresis                         | $\Delta T_{SHDN}$ |                       |                            |     | 10   |     | °C    |

Note 1: All units are 100% production tested at TA = +25°C. Limits over the operating temperature range are guaranteed by design.

Note 2: The dropout voltage is defined as V<sub>IN</sub> - V<sub>OUT</sub> when V<sub>OUT</sub> is 100mV below the nominal value of V<sub>OUT</sub>. Specification only applies when V<sub>OUT</sub> ≥ 2.5V.

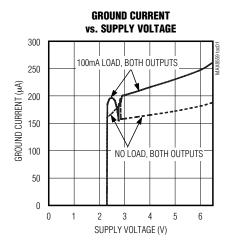

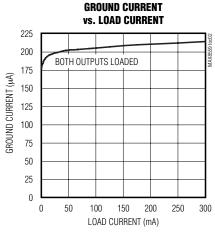

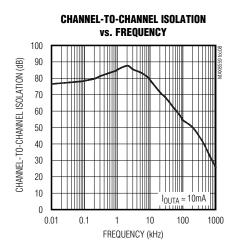

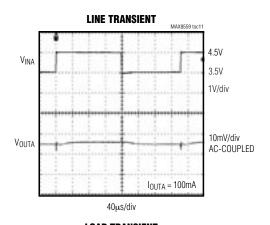

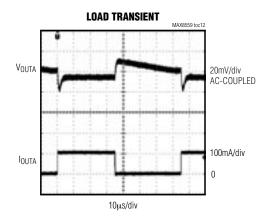

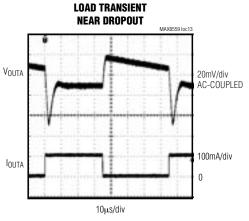

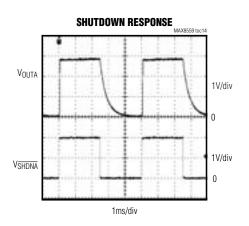

## Typical Operating Characteristics

$(V_{OUTA} = V_{OUTB} = 2.85V, V_{INA} = V_{INB} = 3.8V, C_{OUT} = 2.2\mu F$  (or  $4.7\mu F$  for 300mA),  $C_{BP} = 0.01\mu F$ , and  $C_{IN} = 2.2\mu F$  (or  $4.7\mu F$  for 300mA), unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{OUTA} = V_{OUTB} = 2.85V, V_{INA} = V_{INB} = 3.8V, C_{OUT} = 2.2\mu F$  (or  $4.7\mu F$  for 300mA),  $C_{BP} = 0.01\mu F$ , and  $C_{IN} = 2.2\mu F$  (or  $4.7\mu F$  for 300mA), unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{OUTA} = V_{OUTB} = 2.85V, V_{INA} = V_{INB} = 3.8V, C_{OUT} = 2.2\mu F$  (or  $4.7\mu F$  for 300mA),  $C_{BP} = 0.01\mu F$ , and  $C_{IN} = 2.2\mu F$  (or  $4.7\mu F$  for 300mA), unless otherwise noted.)

**Pin Description**

| PI   | N    | NARAE             | FUNCTION                                                                                                                                                                                                                                                                                                                                 |

|------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDFN | UCSP | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                 |

| 1    | A1   | INA               | LDO A Regulator Input. Connect to INB. Input voltage can range from 2.5V to 6.5V. Bypass INA with a ceramic capacitor to GND (see the <i>Capacitor Selection and Regulator Stability</i> section).                                                                                                                                       |

| 2    | A2   | SHDNA             | Shutdown A Input. A logic-low on SHDNA shuts down regulator A. If SHDNA and SHDNB are both low, both regulators and the internal reference are off and the supply current is reduced to 10nA (typ). If either SHDNA or SHDNB is a logic high, the internal reference is on. Connect SHDNA to INA for always-on operation of regulator A. |

| 3    | А3   | SHDNB             | Shutdown B Input. A logic-low on SHDNB shuts down regulator B. If SHDNA and SHDNB are both low, both regulators and the internal reference are off and the supply current is reduced to 10nA (typ). If either SHDNA or SHDNB is a logic high, the internal reference is on. Connect SHDNB to INB for always-on operation of regulator B. |

| 4    | A4   | INB               | LDO B Regulator Input. Connect to INA. Input voltage can range from 2.5V to 6.5V. Bypass INB with a ceramic capacitor to GND (see the <i>Capacitor Selection and Regulator Stability</i> section).                                                                                                                                       |

| 5    | B4   | OUTB              | Regulator B Output. OUTB can source up to 300mA continuous current. Bypass OUTB with a ceramic capacitor to GND (see the <i>Capacitor Selection and Regulator Stability</i> section). During shutdown, OUTB is internally discharged to GND through a $385\Omega$ resistor.                                                              |

| 6    | В3   | GND               | Ground                                                                                                                                                                                                                                                                                                                                   |

| 7    | B2   | BP                | Reference Noise Bypass. Bypass BP with a low-leakage 0.01µF ceramic capacitor for reduced noise at both outputs.                                                                                                                                                                                                                         |

| 8    | B1   | OUTA              | Regulator A Output. OUTA can source up to 300mA continuous current. Bypass OUTA with a ceramic capacitor to GND (see the <i>Capacitor Selection and Regulator Stability</i> section). During shutdown, OUTB is internally discharged to GND through a $385\Omega$ resistor.                                                              |

| EP   | _    | Exposed<br>Paddle | Connect to ground plane. EP also functions as a heatsink. Solder to the circuit-board ground plane to maximize thermal dissipation.                                                                                                                                                                                                      |

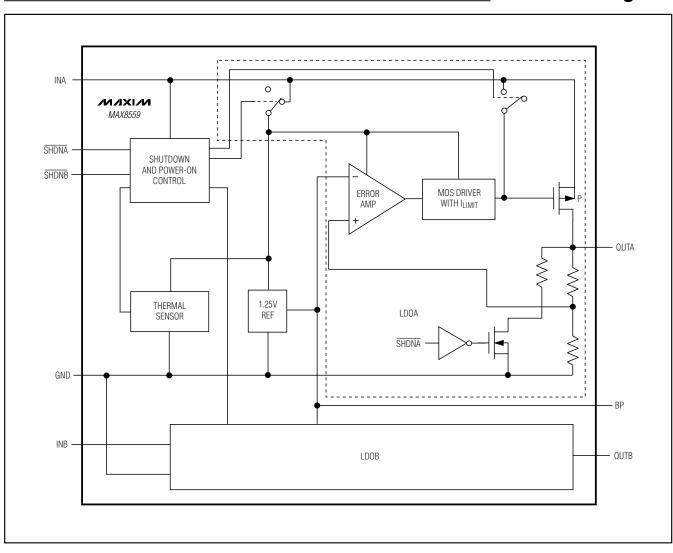

### **Detailed Description**

The MAX8559 is a dual, low-noise, low-dropout, low-quiescent-current linear regulator designed primarily for battery-powered applications. The regulators are available with preset 1.5V to 3.3V output voltages. These outputs can supply loads up to 300mA with a 4.7 $\mu$ F output capacitor, or up to 150mA with a 2.2 $\mu$ F output capacitor. As illustrated in the *Functional Diagram*, the MAX8559 consists of a 1.25V reference, error amplifiers, P-channel pass transistors, internal feedback voltage-dividers, and autodischarge circuitry.

#### Feedback Control Loop

The 1.25V bandgap reference is connected to the error amplifier's inverting input. The error amplifier compares this reference with the feedback voltage and amplifies the difference. If the feedback voltage is lower than the reference voltage, the pass-transistor gate is pulled

lower, allowing more current to pass to the output and increasing the output voltage. If the feedback voltage is too high, the pass-transistor gate is pulled up, allowing less current to pass to the output. The output voltage is fed back through an internal resistor voltage-divider connected to OUT\_.

#### Internal P-Channel Pass Transistor

The MAX8559 features two  $0.6\Omega$  P-channel MOSFET pass transistors. A P-channel MOSFET provides several advantages over similar designs using PNP pass transistors, including longer battery life. It requires no base drive, reducing quiescent current considerably. PNP-based regulators waste considerable current in dropout when the pass transistor saturates, and they also use high base-drive currents under large loads. The MAX8559 does not suffer from these problems, and with both outputs on it only consumes 180 $\mu$ A of

quiescent current at no load and 220µA with 100mA load current on both outputs (see the *Typical Operating Characteristics*). A PNP-based regulator has a high dropout voltage that is independent of the load. A P-channel MOSFET's dropout voltage is proportional to load current, providing for low dropout voltage at heavy loads and extremely low dropout at lighter loads.

#### **Current Limit**

The MAX8559 contains two independent current limiters, one for each regulator output, monitoring and controlling the pass transistor's gate voltage and limiting the output current to 310mA (min). The outputs can be shorted to ground continuously without damaging the part.

#### **Low-Noise Operation**

An external  $0.01\mu\text{F}$  bypass capacitor at BP in conjunction with an internal resistor creates a lowpass filter. The MAX8559 exhibits less than  $32\mu\text{V}_{RMS}$  of output voltage noise with CBP =  $0.01\mu\text{F}$  and COUT =  $10\mu\text{F}$ . The Typical Operating Characteristics show a graph of Output-Noise Spectral Density with these values. If output noise is not critical, the BP capacitor can be removed to reduce total solution size and cost.

#### **Shutdown**

The MAX8559 has independent shutdown control inputs (SHDNA and SHDNB). Drive SHDNA low to shut down OUTA. Drive SHNDB low to shut down OUTB. Drive both SHDNA and SHDNB low to shut down the entire chip, reducing supply current to 0.01μA. Connect SHDNA or SHDNB to a logic high or IN\_ for always-on operation of the corresponding LDO. Each LDO output is internally discharged to ground through a 385Ω resistor in shutdown mode.

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the MAX8559. Each regulator has its own independent thermal detector. When one of the regulators junction temperature exceeds  $T_J = +160^{\circ}\text{C}$ , that regulator's pass transistor is turned off allowing the IC to cool. The thermal sensor turns the pass transistor on again after the IC's junction temperature cools by 10°C. This results in a pulsed output during continuous thermal-overload conditions.

#### **Operating Region and Power Dissipation**

The MAX8559 maximum power dissipation depends on the thermal resistance of the case and the circuit board, the temperature difference between the die junction and ambient air, and the rate of airflow. The power dissipation across the device is  $P = I_{OUT} \times (V_{IN} - V_{OUT})$ .

The maximum power dissipation allowed is:

$P_{MAX} = (T_J - T_A) / (R_{\theta JB} + R_{\theta BA})$

where T<sub>J</sub> - T<sub>A</sub> is the temperature difference between the MAX8559 die junction and the surrounding air, R<sub>θJB</sub> (R<sub>θJC</sub>) is the thermal resistance of the package, and R<sub>θBA</sub> is the thermal resistance through the printed circuit board, copper traces, and other materials to the surrounding air.

The exposed paddle of the TDFN package performs the function of channeling heat away. Connect the exposed paddle to the board ground plane.

### **Applications Information**

#### Capacitor Selection and Regulator Stability

For load currents up to 150mA, use a single 2.2µF capacitor to bypass both inputs of the MAX8559 and a 2.2µF capacitor to bypass each output. Larger input-capacitor values and lower ESRs provide better supply-noise rejection and line-transient response. To reduce output noise and improve load-transient voltage dips, use larger output capacitors up to 10µF. For stable operation over the full temperature range with load currents up to 300mA, input and output capacitors should be a minimum of 4.7µF.

Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature. With dielectrics such as Z5U and Y5V, it may be necessary to use 4.7µF or more for up to 150mA load current to ensure stability at temperatures below -10°C. With X7R or X5R dielectrics, 2.2µF is sufficient at all operating temperatures. These regulators are optimized for ceramic capacitors. Tantalum capacitors are not recommended.

Use a 0.01µF bypass capacitor at BP for low-output voltage noise. Increasing the capacitance slightly decreases the output noise, but increases the startup time.

# PSRR and Operation from Sources Other than Batteries

The MAX8559 is designed to deliver low-dropout voltages and low quiescent currents in battery-powered systems. Power-supply rejection ratio is 70dB at 10kHz (see Power-Supply Rejection Ratio vs. Frequency in the *Typical Operating Characteristics*). When operating from sources other than batteries, improved supply-noise rejection and transient response is achieved by increasing the values of the input and output bypass capacitors and through passive RC or CRC filtering techniques.

#### **Load-Transient Considerations**

The MAX8559 load-transient response graphs (see the *Typical Operating Characteristics*) show two components of the output response: a DC shift in the output voltage due to the different load currents and the transient response. Typical overshoot for step changes in the load current from 10µA to 100mA is 15mV. Increase the output capacitor's value and decrease its ESR to attenuate transient spikes.

#### **Dropout Voltage**

A regulator's minimum input-output voltage differential (or dropout voltage) determines the lowest usable supply voltage. In battery-powered systems, this determines the useful end-of-life battery voltage. Because the MAX8559 uses an internal P-channel MOSFET pass transistor, its dropout voltage is a function of the drainto-source on-resistance (RDS(ON)) multiplied by the load current (see the *Typical Operating Characteristics*).

# Calculating the Maximum Output Power in UCSP

The maximum output power of the MAX8559 is limited by the maximum power dissipation of the package. By calculating the power dissipation of the package as a function of the input voltage, output voltages, and output currents, the maximum input voltage can be obtained. The maximum power dissipation should not exceed the package's maximum power rating.

P = (VIN(MAX) - VOUTA) X IOUTA + (VIN(MAX) - VOUTB) X IOUTB where:

V<sub>IN(MAX)</sub> = maximum input voltage

P<sub>MAX</sub> = maximum power dissipation of the package (379mW for the UCSP and 1951mW for the TDFN)

**VOUTA** = output voltage of OUTA

Voutb = output voltage of OUTB

IOUTA = maximum output current of OUTA

IOUTB = maximum output current of OUTB

P should be less than  $P_{MAX}$ . If P is greater than  $P_{MAX}$ , consider the TDFN.

#### **Layout Guidelines**

Due to the low output noise and tight output voltage accuracy required by most applications, careful PC board layout is required. An evaluation kit (MAX8559EVKIT) is available to speed design.

Follow these guidelines for good PC board layout:

- Keep the input and output paths short and wide if possible, especially at the ground terminals.

- Use thick copper PC boards (2oz vs. 1oz) to enhance thermal capabilities.

- Place output, input, and bypass capacitors as close as possible to the IC.

- Ensure traces to BP and the BP capacitor are away from noisy sources to ensure low output voltage noise.

# **Functional Diagram**

## **Output Voltage Selector Guide**

| PART         | V <sub>OUTA (x)</sub> | V <sub>OUTB</sub> (y) | TOP MARK |

|--------------|-----------------------|-----------------------|----------|

| MAX8559EBA8A | 1.50                  | 3.30                  | AAE      |

| MAX8559EBA2G | 1.80                  | 3.00                  | AAF      |

| MAX8559EBAP2 | 2.50                  | 1.80                  | AAG      |

| MAX8559EBAK2 | 2.80                  | 1.80                  | AAH      |

| MAX8559EBAJJ | 2.85                  | 2.85                  | AAC      |

| MAX8559EBAJG | 2.85                  | 3.00                  | AAI      |

| MAX8559EBAII | 2.90                  | 2.90                  | AAB      |

| MAX8559EBAG2 | 3.00                  | 1.80                  | AAJ      |

| MAX8559EBAGJ | 3.00                  | 2.85                  | AAD      |

| MAX8559EBAGG | 3.00                  | 3.00                  | AAA      |

| MAX8559ETA8A | 1.50                  | 3.30                  | AIM      |

| MAX8559ETA2G | 1.80                  | 3.00                  | ALK      |

| MAX8559ETAP2 | 2.50                  | 1.80                  | ALL      |

| MAX8559ETAK2 | 2.80                  | 1.80                  | ALM      |

| MAX8559ETAKG | 2.80                  | 3.00                  | AIN      |

| MAX8559ETAJ2 | 2.85                  | 1.80                  | ALD      |

| MAX8559ETAJJ | 2.85                  | 2.85                  | AIG      |

| MAX8559ETAJG | 2.85                  | 3.00                  | ALN      |

| MAX8559ETAII | 2.90                  | 2.90                  | AIF      |

| MAX8559ETAG2 | 3.00                  | 1.80                  | ALO      |

| MAX8559ETAGG | 3.00                  | 3.00                  | AIE      |

**Note:** Standard voltage options, shown in bold, are available. Contact the factory for other output voltages between 1.5V and 3.3V. Minimum order quantity is 15,000 units.

## Pin Configurations (continued)

**Chip Information**

TRANSISTOR COUNT: 634

PROCESS: BICMOS

\_\_\_ /N/1X1/N

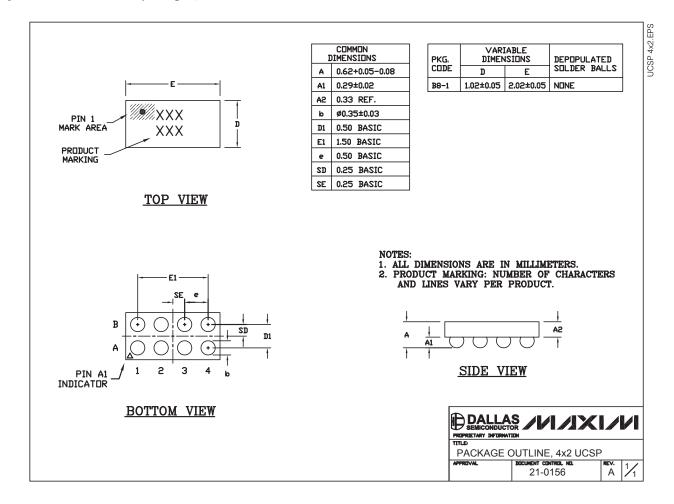

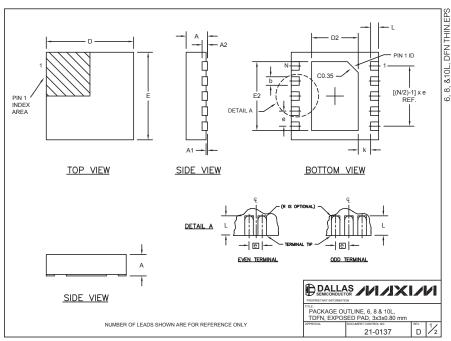

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|                     | JNI DIME | NSIONS          | 1               |               |                            |                |               |  |

|---------------------|----------|-----------------|-----------------|---------------|----------------------------|----------------|---------------|--|

| SYMBOL              | MIN.     | MAX.            |                 |               |                            |                |               |  |

| A                   | 0.70     | 0.80            |                 |               |                            |                |               |  |

| D                   | 2.90     |                 | ł               |               |                            |                |               |  |

| F                   | 2.90     | 3.10            | 1               |               |                            |                |               |  |

| A1                  | 0.00     | 0.05            |                 |               |                            |                |               |  |

| L                   | 0.20     | 0.40            | 1               |               |                            |                |               |  |

| k                   | 0.:      | 25 MIN.         | 1               |               |                            |                |               |  |

| A2                  | 0.2      | 20 REF.         | 1               |               |                            |                |               |  |

| PACKAGE VAR         | N        | D2              | E2              | e<br>0.05 BCC | JEDEC SPEC                 | b              | [(N/2)-1] x e |  |

|                     |          |                 | F2              | e.            | JEDEC SPEC                 | b              | [(N/2)-1] x e |  |

|                     |          |                 | E2<br>2.30±0.10 | e<br>0.95 BSC | JEDEC SPEC<br>MO229 / WEEA | b<br>0.40±0.05 | [(N/2)-1] x e |  |

| PKG. CODE           | N        | D2              |                 |               |                            | -              | * / *         |  |

| PKG. CODE<br>T633-1 | N<br>6   | D2<br>1.50±0.10 | 2.30±0.10       | 0.95 BSC      | MO229 / WEEA               | 0.40±0.05      | 1.90 REF      |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600