Optical diaga Sole F供应商

自出货

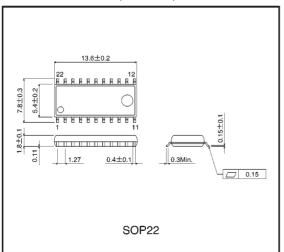

# Post amplifier applicable with 1-bit D / A converter BH3562F

The BH3562F is a post amplifier applicable with 1-bit D/A converter for compact disc players.

### Applications

Portable CD players, etc.

#### Features

- 1) 2-chancel analog filter IC for 1-bit D/A converts.

- Internal partial CR for two channels (left and right) LPF.

- 3) Operates on a single power supply.

- 4) Operates on a power supply voltage as low as 3.1V.

## •Absolute maximum ratings (Ta = $25^{\circ}$ C)

| Parameter             | Symbol | Limits   | Unit |

|-----------------------|--------|----------|------|

| Power supply voltage  | Vcc    | 5.5      | V    |

| Power dissipation     | Pd     | 450*     | mW   |

| Operating temperature | Topr   | -35~+85  | Ĵ    |

| Storage temperature   | Tstg   | -55~+150 | Ĵ    |

\* Reduced by 4.5 mW for each increase in Ta of 1°C over 25°C.

#### •Recommended operating conditions (Ta = $25^{\circ}$ C)

| Parameter              | Symbol | Limits  | Unit |  |

|------------------------|--------|---------|------|--|

| Power supply voltage 1 | Vcc1   | 3.1~5.5 | V    |  |

| Power supply voltage 2 | Vcc2   | 2.0~5.5 | V    |  |

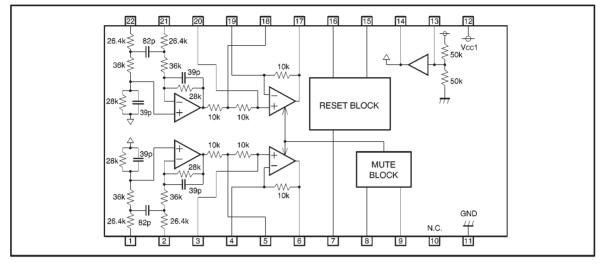

## Block diagram

## Pin descriptions

| Pin No. | Pin name     | Function                                              |  |  |

|---------|--------------|-------------------------------------------------------|--|--|

| 1       | IN1 (+)      | Channel 1 positive input                              |  |  |

| 2       | IN1 (—)      | Channel 1 negative input                              |  |  |

| 3       | FILTER 1-1   | Filter setting (1-1)                                  |  |  |

| 4       | GAIN 1       | Gain adjustment (1)                                   |  |  |

| 5       | FILTER 2-1   | Filter setting (2-1)                                  |  |  |

| 6       | OUT 1        | Channel 1 output                                      |  |  |

| 7       | OUTMUTE 1    | Output mute transistor drive (1)                      |  |  |

| 8       | Сτ           | Attached capacitor for setting the mute time constant |  |  |

| 9       | MUTE         | Mute control                                          |  |  |

| 10      | N.C.         | -                                                     |  |  |

| 11      | GND          | Ground                                                |  |  |

| 12      | Vcc1         | Power supply                                          |  |  |

| 13      | BIAS IN      | Bias input                                            |  |  |

| 14      | BIAS OUT     | Bias output                                           |  |  |

| 15      | Vcc2         | Reset block idling power supply                       |  |  |

| 16      | OUTMUTE 2    | Output mute transistor drive (2)                      |  |  |

| 17      | OUT 2        | Channel 2 output                                      |  |  |

| 18      | FILTER 2-2   | Filter setting (2-2)                                  |  |  |

| 19      | GAIN 2       | Gain adjustment (2)                                   |  |  |

| 20      | FILTER 1 - 2 | Filter setting (1-2)                                  |  |  |

| 21      | IN2 (—)      | Channel 2 negative input                              |  |  |

| 22      | IN2 (+)      | Channel 2 positive input                              |  |  |

| Electrical characteristics (       | unless oth         | erwise n | oted, Ta | = 25°C, | Vcc1 = 2 | 5°C, Vcc2 = 3.5V, RL = 10kΩ)                                                                                         |

|------------------------------------|--------------------|----------|----------|---------|----------|----------------------------------------------------------------------------------------------------------------------|

| Parameter                          | Symbol             | Min.     | Тур.     | Max.    | Unit     | Conditions                                                                                                           |

| Quiescent current (1)              | <b>I</b> Q1        | 3.0      | 4.5      | 6.0     | mA       | MUTE OFF, R∟=∞                                                                                                       |

| Quiescent current (2)              | lQ2                | 7        | 10       | 13      | mA       | MUTE ON, R₁=∞                                                                                                        |

| Standby current (1)                | ls1                | —        | 0        | 1       | μA       | MUTE OFF, RL=∞, Vcc1 OFF                                                                                             |

| Standby current (2)                | Is2                | _        | 0        | 1       | μA       | MUTE ON, RL=∞, VCC1 OFF                                                                                              |

| Offset voltage (1)                 | V <sub>off2</sub>  | -15      | 0        | 15      | mV       | MUTE OFF, reference BIAS OUTPUT                                                                                      |

| Offset voltage (2)                 | V <sub>off2</sub>  | -15      | 0        | 15      | mV       | MUTE ON, reference BIAS OUTPUT                                                                                       |

| Bias voltage                       | Vво                | 1.60     | 1.75     | 1.90    | V        |                                                                                                                      |

| Bias voltage, load regulation 1    | $\Delta V_{BO1}$   | —        | —        | 50      | mV       | $I_B=+5mA$ (discharge)                                                                                               |

| Bias voltage, load regulation 2    | $\Delta V_{BO2}$   | _        | —        | 50      | mV       | I <sub>B</sub> =−5mA (intake)                                                                                        |

| C $\tau$ source current            | Min.               | 10.5     | 14.0     | 17.5    | μA       | C $\tau$ = 1.4 V, MUTE OFF                                                                                           |

| C $\tau$ sink current              | Mout               | 10.5     | 14.0     | 17.5    | μA       | C <i>τ</i> = 1.4 V, MUTE ON                                                                                          |

| C τ sink / source<br>current ratio | OUT / IN           | 0.8      | 1        | 1.2     | _        |                                                                                                                      |

| MUTE ON voltage                    | VthON1             | 1.6      | —        | -       | V        | Verifies : output voltage is at BIAS level.                                                                          |

| MUTE OFF voltage                   | VthOFF1            | _        | _        | 1.2     | V        | Verifies : output voltage is at HIGH level.                                                                          |

| C τ ON voltage (1)                 | VthON2             | 0.7      | -        | —       | V        | Verifies : ext. mute trans. drive current is ON.                                                                     |

| C τ OFF voltage (1)                | VthOFF2            | _        | -        | 1.3     | V        | Verifies : ext. mute trans. drive current in OFF.                                                                    |

| C τ ON voltage (2)                 | V <sub>thON3</sub> | _        | -        | 1.10    | V        | Verifies : output voltage is at BIAS level.                                                                          |

| C τ voltage (2)                    | VthOFF3            | 1.64     | —        | -       | V        | Verifies : output voltage is at HIGH level.                                                                          |

| External mute transistor current   | Імите              | 1.0      | 1.5      | 2.0     | mA       | Converted from current at $100\Omega$                                                                                |

| Output high level voltage          | Vон                | 2.55     | 2.70     | _       | v        | GAIN = 6 dB UP (10 k $\Omega$ external)<br>Pos. phase input =3.5 V, neg. phase input 0 V<br>Opposite side = BIAS OUT |

| Output low level voltage           | Vol                | _        | 0.75     | 0.90    | v        | GAIN = 6 dB UP (10 k $\Omega$ external)<br>Pos. phase input =0 V, neg. phase input 3.5 V<br>Opposite side = BIAS OUT |

| Close loop voltage gain            | Gvc                | -10.8    | -7.8     | -4.8    | dB       | VIN=1kHz, 0.5Vms                                                                                                     |

| Frequency characteristics (1)      | fc1                | -10.8    | -7.8     | -4.8    | dB       | VIN=15kHz, 0.5Vrms                                                                                                   |

| Frequency characteristics (2)      | fc2                | -21      | -16      | -11     | dB       | VIN=40kHz, 0.5Vrms                                                                                                   |

| Mute attenuation                   | ATT                | 80       | -        | -       | dB       | VIN=1kHz, 0.5Vrms                                                                                                    |

| Crosstalk                          | СТ                 | _        | 90       | -       | dB       | VIN=1kHz, 0.5Vms                                                                                                     |

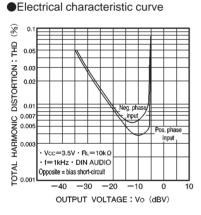

| Total harmonic distortion          | THD                | _        | 0.01     | 0.02    | %        | VIN=1kHz, 0.5Vms                                                                                                     |

| Signal to noise ratio              | S/N                | 90       | 100      | -       | dB       | 0 dB at 1 Vrms output                                                                                                |

| L-R Channel balance (1)            | CB1                | -1       | 0        | 1       | dB       | Positive phase input, V <sub>IN</sub> = 1 kHz, 0.5 V <sub>rms</sub>                                                  |

| L-R Channel balance (2)            | CB2                | -1       | 0        | 1       | dB       | Negative phase input, V <sub>IN</sub> = 1 kHz, 0.5 V <sub>rms</sub>                                                  |

|                                    |                    | 45       |          | _       | 1        |                                                                                                                      |

•Electrical characteristics (unless otherwise noted, Ta =  $25^{\circ}$ C, Vcc1 =  $25^{\circ}$ C, Vcc2 = 3.5V, RL = 10k $\Omega$ )

Note: A weighing filter is used when measuring AC parameters (excluding frequency characteristics).  $\bigcirc$ Not designed for radiation resistance.

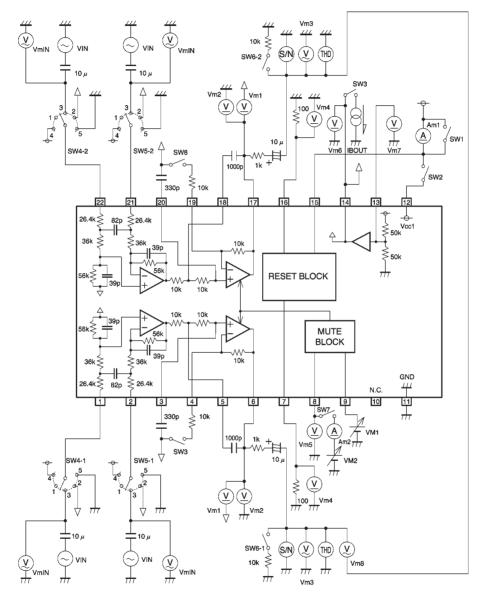

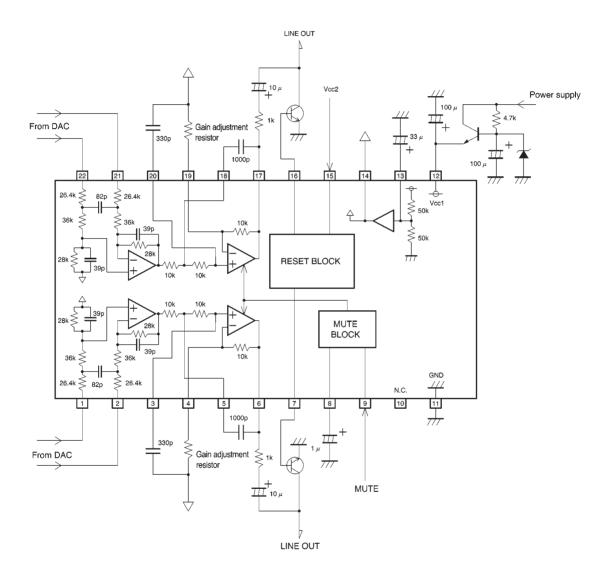

#### Measurement circuit

Note 1: Arrows indicate the positive current direction. Note 2: Unless otherwise noted, AC input (VIN) = 1 kHz sine waves. Note 3: Unless otherwise noted, SW8 = Off.

Operation notes

(1) When the MUTE pin voltage reaches 1.5V or higher, the output voltage is muted and the bias level is output.

(2) Frequency characteristics can be changed by adjusting the capacitor attached to pin 3 (20 pin) or pin 5 (18 pin).

(3) Gain can be changed by attaching a resistor to pin 4 (19 pin).

(4) Attach a transistor to pin 7 (16 pin) to mute popping sounds. Recommended transistor: 2SD1781K

(5) The reset block idling power supply for pin 15 should be left on as it prevents popping sounds.

(6) To prevent popping sounds due to sudden fluctuation in the power supply voltage, attach a ripple filter.

(7) To prevent popping sounds due to sudden changes in the mute pin voltage, connect pin 8 to  $1\mu F$  (approx.) capacitor.

(8) Attach a by-pass capacitor (approx.  $0.1\mu F$ ) at the base of the IC between the power supply.

Fig. 3 Output voltage vs. distortion