- **Organization**

- 512K-Byte Main Array

- 24K-Byte Protected Overlay-Block

- **User-Defined x16 or x32 Data Bus**

- **Read Transfer Data Rates Up to 100 MBytes/s at Bus Frequencies Up to 40 MHz**

- **Burstable Pipelined Read Interface With Programmable Latency, Length, and Order**

- **10000 Program/Erase Cycles**

- **Three Temperature Ranges**

- Commercial . . . 0°C to 70°C

- Extended . . . – 40°C to 85°C

- Automotive . . . – 40°C to 125°C

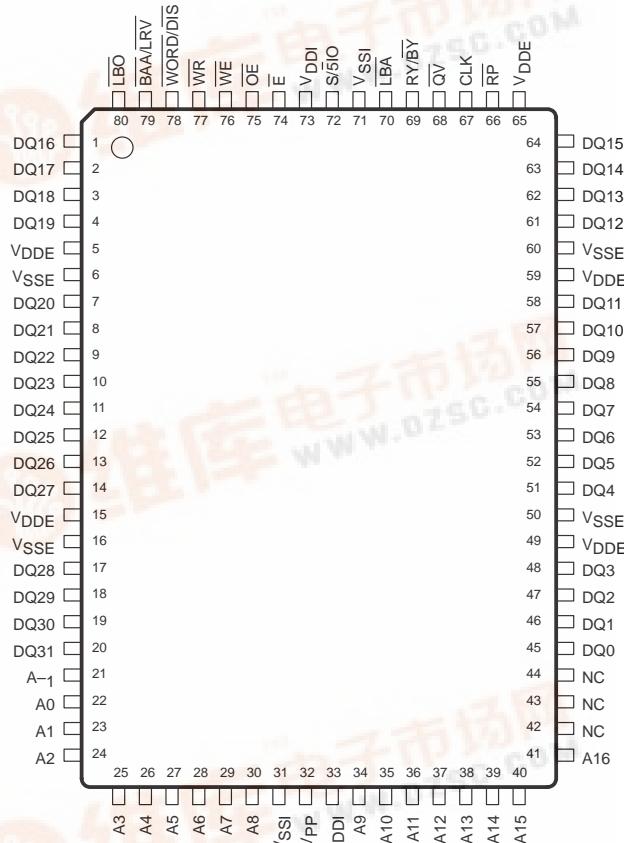

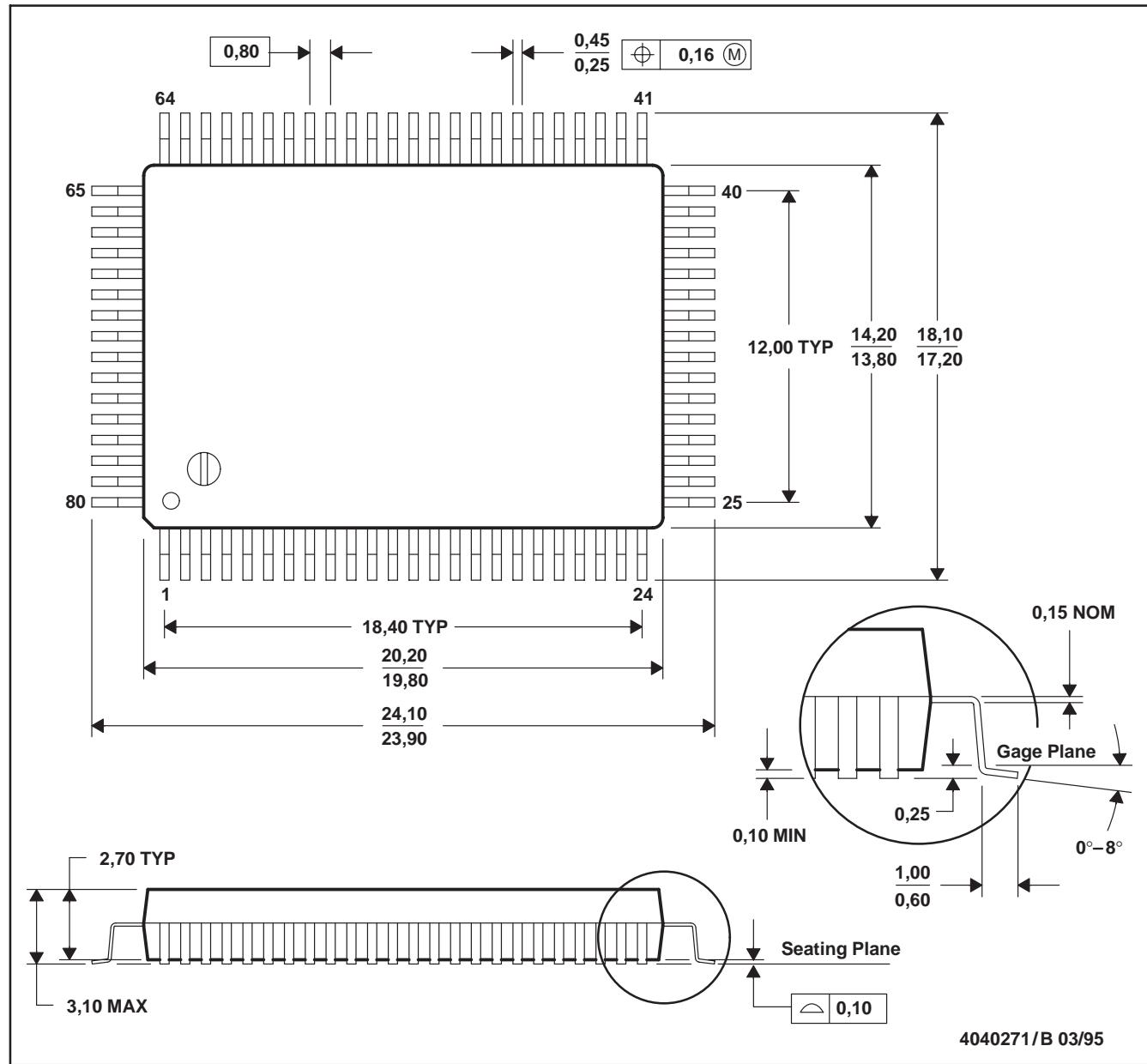

- **80-Pin Plastic Quad Flatpack (PQFP) (PAF Suffix)**

- **Fully Automated On-Chip Erase and Program Operations**

- **Three Separate Voltage Supplies**

- I/O Supply – Configurable 3.3 V/5 V

- Read Supply – 5 V

- Programming Supply – 12 V

- **All Inputs/Outputs TTL-Compatible**

PAF

80-PIN PACKAGE

(TOP VIEW)

## description

The TMS28F033 is the first synchronous nonvolatile flash memory device to offer a configurable burst interface to 16/32-bit microprocessors and microcontrollers operating at frequencies up to 40 MHz.

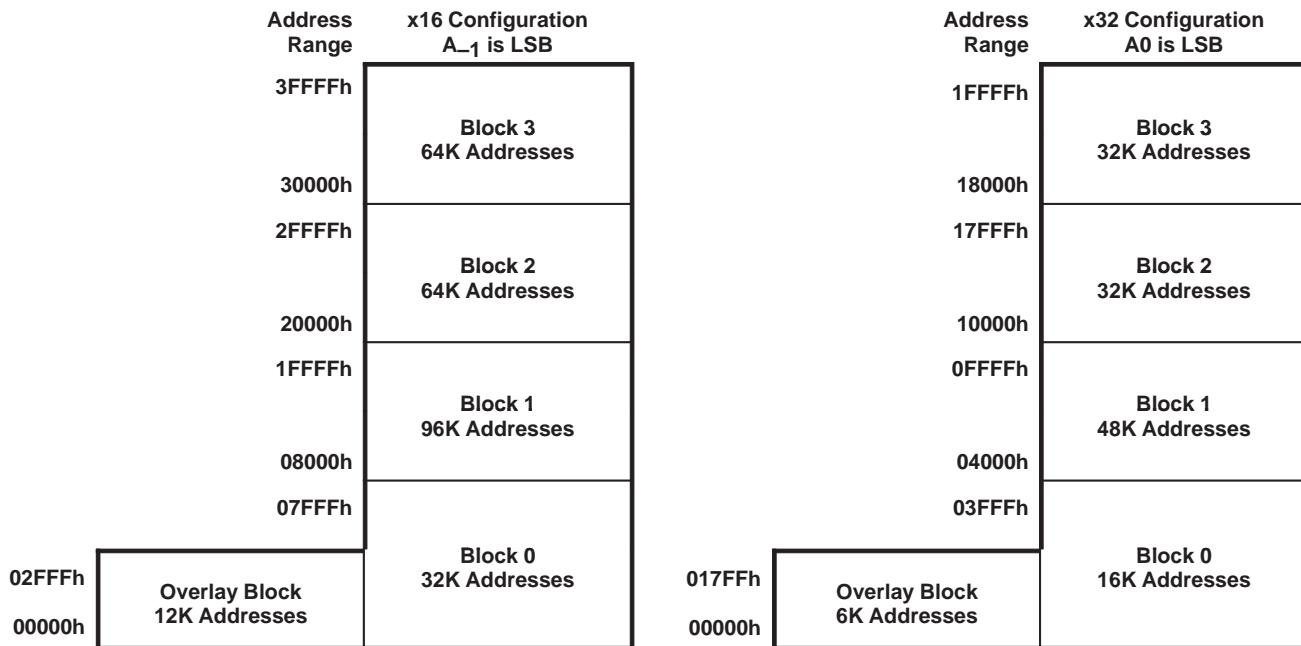

The TMS28F033 contains 4M bits of main memory that is user-configurable as either three or four independently erasable blocks. In addition to the main memory array, there is a protected overlay memory block that is normally hidden from the memory address map. The following table shows the three- and four-block main-memory-array configurations for both 16-bit and 32-bit data bus widths.

Table 1. Memory Configurations

| DATA BUS WIDTH | 3-BLOCK MAIN ARRAY | 4-BLOCK MAIN ARRAY     | PROTECTED OVERLAY BLOCK |

|----------------|--------------------|------------------------|-------------------------|

| 16 bits        | 32K, 160K, and 64K | 32K, 96K, 64K, and 64K | 12K                     |

| 32 bits        | 16K, 80K, and 32K  | 16K, 48K, 32K, and 32K | 6K                      |

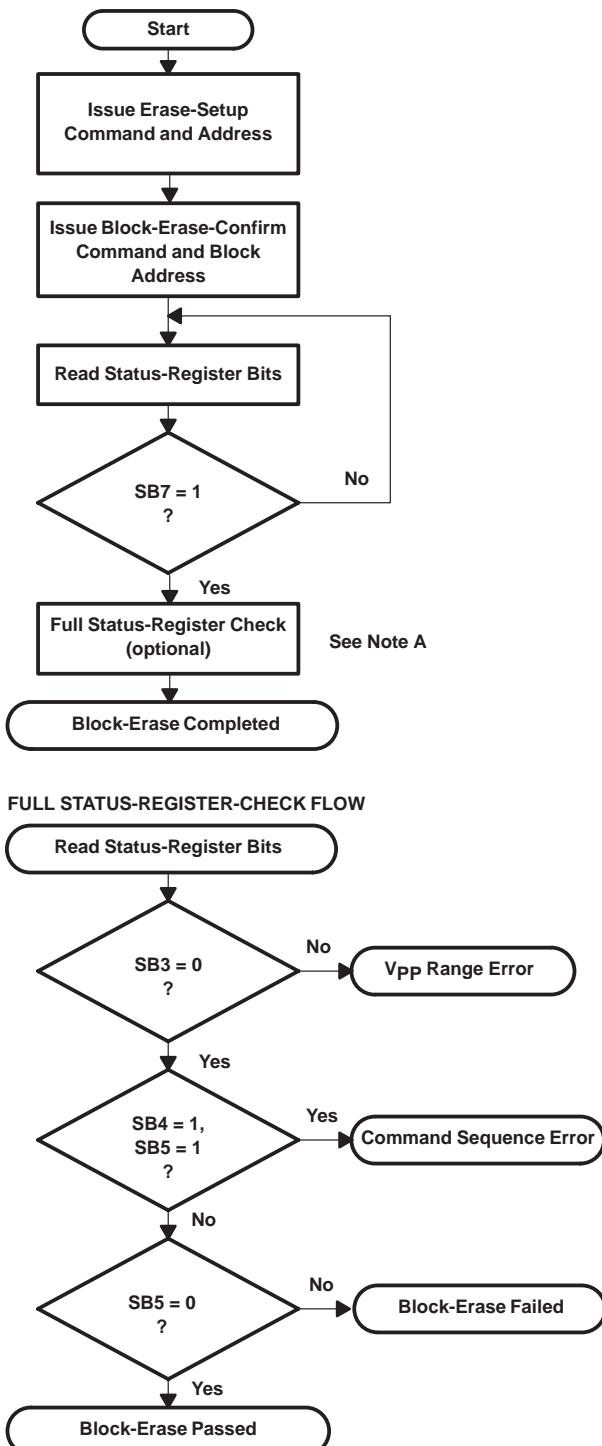

Embedded program and block-erase functions are fully automated by an on-chip write state machine (WSM), which simplifies these operations and relieves the system microcontroller of these secondary tasks. WSM status can be monitored by the on-chip status register to determine the progress of program/erase tasks.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

**TMS28F033**

**4194304-BIT**

**SYNCHRONOUS FLASH MEMORY**

SMJS833 – NOVEMBER 1997

---

**description (continued)**

The TMS28F033 flash memory requires 12 V for erasure and programming, and 5 V for memory-array access while interfacing with either a 3.3-V or 5-V bus.

The TMS28F033 flash memory is fabricated using CMOS technology and is packaged in an 80-pin plastic quad flatpack (PQFP) (PAF suffix).

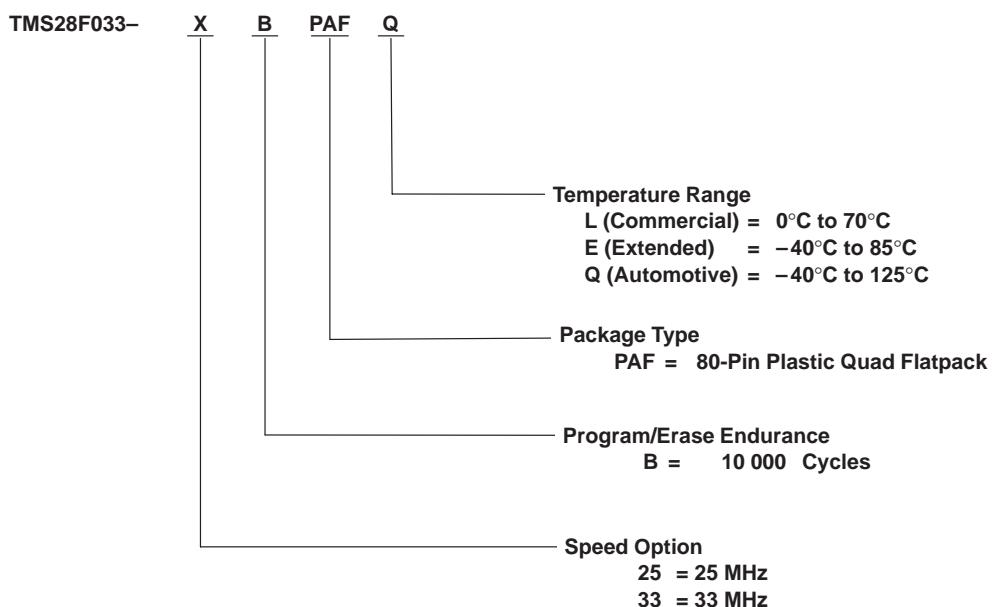

**device symbol nomenclature**

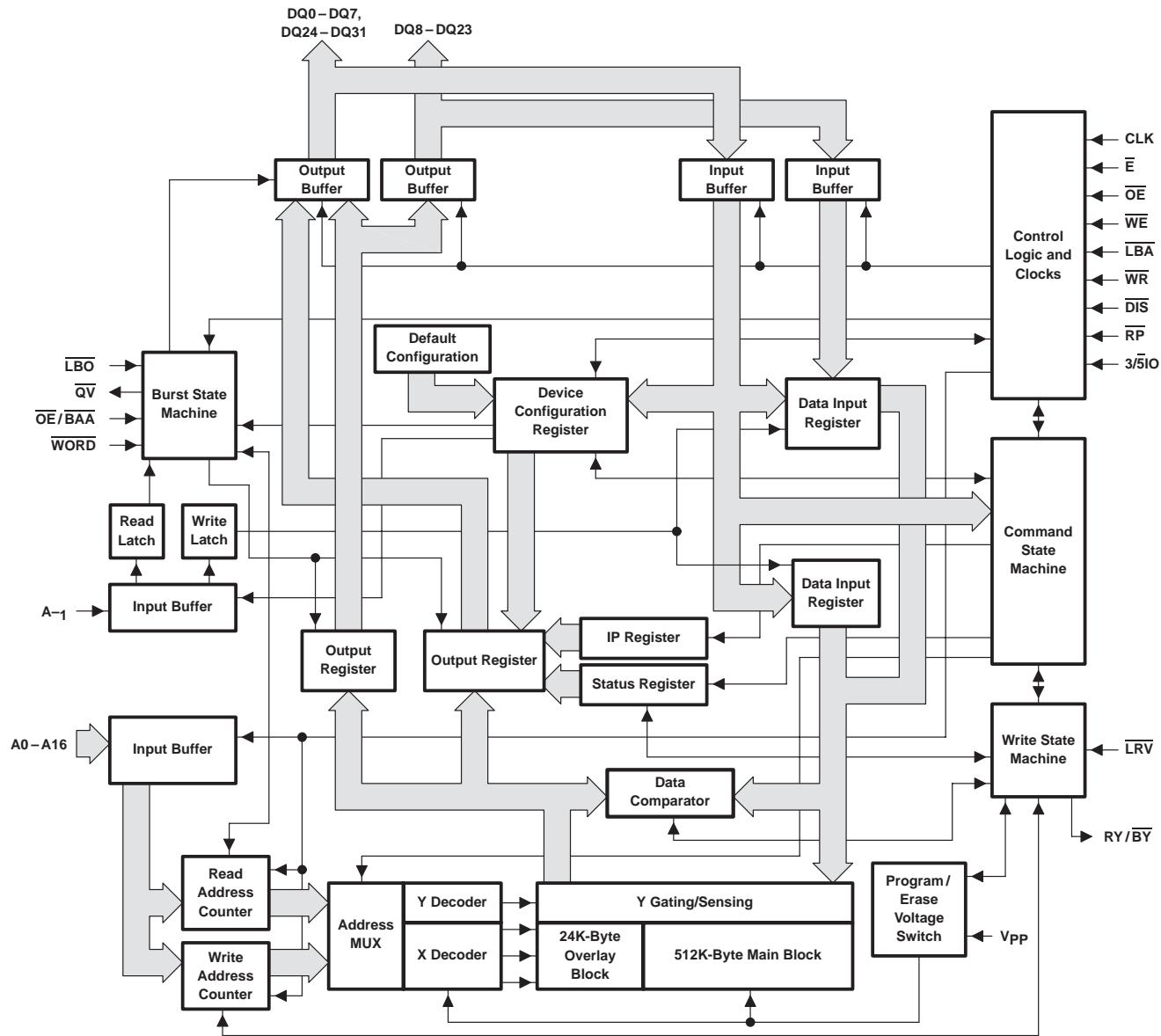

functional block diagram

**TMS28F033**

**4194304-BIT**

**SYNCHRONOUS FLASH MEMORY**

SMJS833 – NOVEMBER 1997

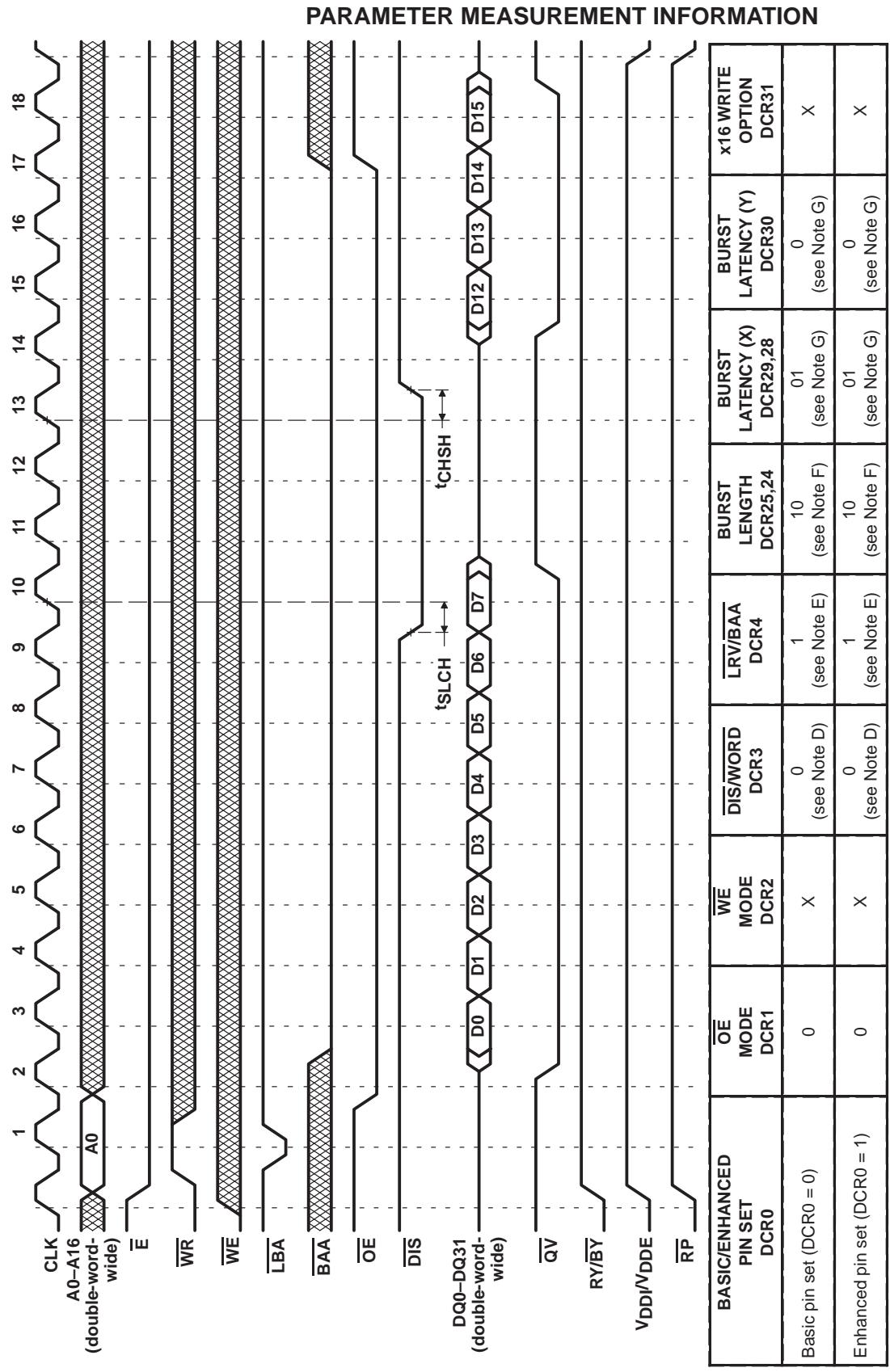

**Terminal Functions**

| TERMINAL NAME                     | TYPE† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>-1</sub>                   | I     | Word select address. A <sub>-1</sub> is the low-order address for the 16-bit data bus, and selects between the high and low word. A <sub>-1</sub> is not used for the 32-bit data bus.                                                                                                                                                                                                                                                                                                  |

| A <sub>0</sub> –A <sub>16</sub>   | I     | Address bus. A <sub>0</sub> –A <sub>16</sub> select one of the 131 072 32-bit segments (double-words), or, with A <sub>-1</sub> , selects one of the 262 144 16-bit segments (words). A <sub>0</sub> is the low-order address for the 32-bit data bus.                                                                                                                                                                                                                                  |

| DQ <sub>0</sub> –DQ <sub>31</sub> | I/O   | Data bus. Bidirectional data bus, where for both 16-bit and 32-bit data bus widths, DQ <sub>31</sub> is the most significant bit (MSB) and DQ <sub>0</sub> is the least significant bit (LSB). The 16-bit data bus uses DQ <sub>0</sub> –DQ <sub>7</sub> and DQ <sub>24</sub> –DQ <sub>31</sub> .                                                                                                                                                                                       |

| LBA                               | I     | Load-burst address. For synchronous operation, when <u>LBA</u> = V <sub>IL</sub> on a rising CLK edge, the address is latched for the beginning of a read or write operation.                                                                                                                                                                                                                                                                                                           |

| BAA                               | I     | Burst-address advance. When <u>BAA</u> = V <sub>IL</sub> , the burst state machine increments the burst address for each required data beat on the rising CLK edge. For BAA usage, see Table 8 and Table 9.                                                                                                                                                                                                                                                                             |

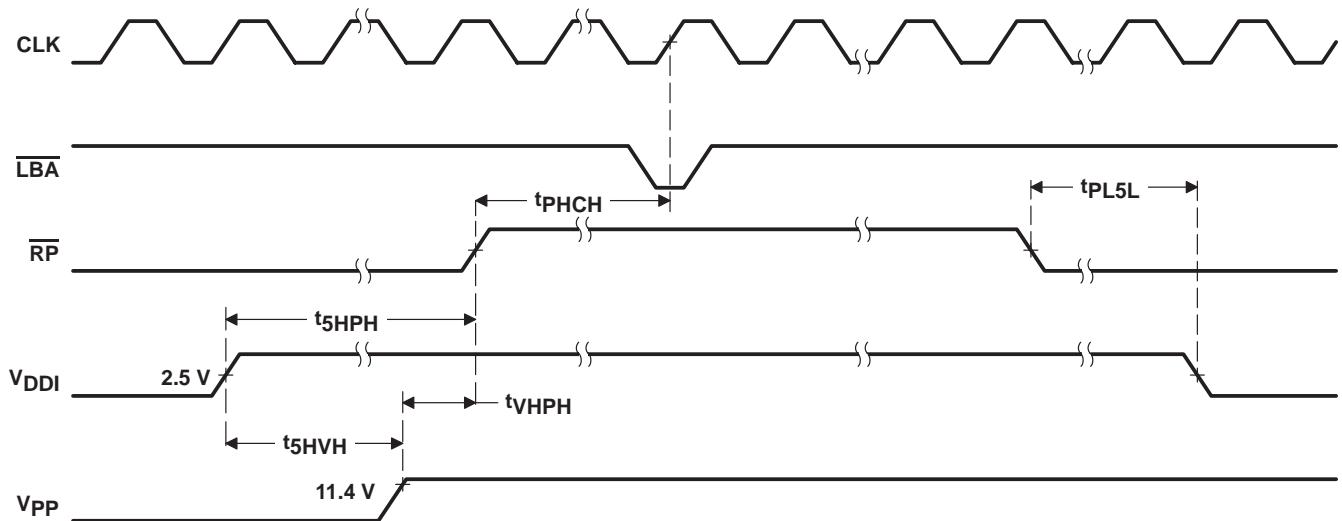

| RP                                | I     | Reset/power-down. When <u>RP</u> = V <sub>IL</sub> , the device terminates any current-state-machine activity and does not respond to read requests and does not accept write commands. On the rising edge of RP, the device sets/clears the OBEB status register bit (SB1) based on the status of V <sub>PP</sub> . When V <sub>PP</sub> ≥ V <sub>PPH</sub> , OBEB is set; if V <sub>PP</sub> ≤ V <sub>PPL</sub> , OBEB is cleared (see Table 3).                                      |

| <u>E</u>                          | I     | Chip enable. When <u>E</u> = V <sub>IL</sub> , the device is enabled for read or write operations. When <u>E</u> = V <sub>IH</sub> , the device is in standby mode. E is an asynchronous signal. For E usage, see Table 8 and Table 9.                                                                                                                                                                                                                                                  |

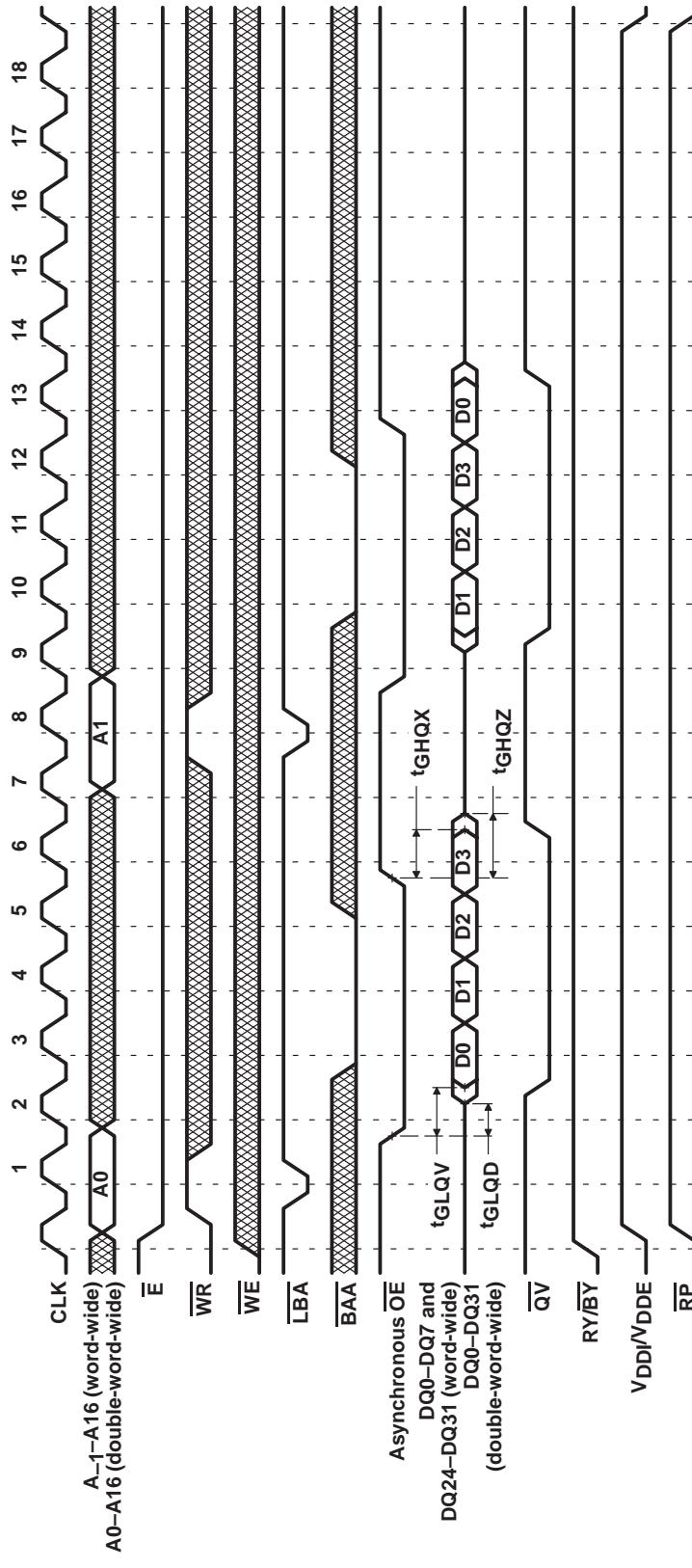

| <u>OE</u>                         | I     | Output enable. <u>OE</u> is used for read operations and can be either synchronous or asynchronous (see Table 8 and Table 9). For synchronous <u>OE</u> , when <u>OE</u> = V <sub>IL</sub> on a rising CLK edge, the output data is latched and becomes valid prior to the next rising CLK edge. <u>OE</u> = V <sub>IH</sub> during write operations.                                                                                                                                   |

| LBO                               | I     | Linear-burst order. When <u>LBO</u> = V <sub>IL</sub> , the address counter is set for linear burst. When <u>LBO</u> = V <sub>IH</sub> , the address counter is set for interleaved burst. For LBO usage, see Table 9 and Table 12.                                                                                                                                                                                                                                                     |

| <u>WR</u>                         | I     | Write. <u>WR</u> is a synchronous signal that controls the read and write operations. If <u>WR</u> = V <sub>IL</sub> when the address is latched (LBA = V <sub>IL</sub> ), then the cycle is a write cycle. If <u>WR</u> = V <sub>IH</sub> when the address is latched, then the cycle is a read cycle.                                                                                                                                                                                 |

| <u>WE</u>                         | I     | Write enable. <u>WE</u> is used for write/erase operations and can be either synchronous or asynchronous (see Table 8 and Table 9). For synchronous <u>WE</u> usage, with the first occurrence of <u>WE</u> = V <sub>IL</sub> (after the address is latched with <u>LBA</u> and <u>WR</u> = V <sub>IL</sub> ) on a rising CLK edge, the input data/command is latched. For asynchronous writes, the data and address are latched on the <u>WE</u> rising edge.                          |

| <u>WORD</u>                       | I     | Word enable. <u>WORD</u> is used for selection of the data bus width. When <u>WORD</u> = V <sub>IL</sub> , the device has a 16-bit data bus, and data is input or output on DQ <sub>0</sub> –DQ <sub>7</sub> and DQ <sub>24</sub> –DQ <sub>31</sub> , and address A <sub>-1</sub> selects between the high and low word. When <u>WORD</u> = V <sub>IH</sub> , the device has a 32-bit data bus and turns off the A <sub>-1</sub> input buffer. For WORD usage, see Table 8 and Table 9. |

| <u>DIS</u>                        | I     | Disable output. When <u>DIS</u> = V <sub>IL</sub> , the synchronous <u>OE</u> , DQ's, and <u>QV</u> signals are disabled. <u>DIS</u> functions as an additional synchronous output enable (opposite in logic to <u>OE</u> ). For DIS usage, see Table 8 and Table 9.                                                                                                                                                                                                                    |

| <u>LRV</u>                        | I     | Low regulator voltage. When <u>LRV</u> = V <sub>IL</sub> during a write/erase operation, the LRV status register bit (SB4) is set (see Table 7). LRV is an asynchronous signal. For LRV usage, see Table 8 and Table 9.                                                                                                                                                                                                                                                                 |

| <u>QV</u>                         | OD O  | Data valid. <u>QV</u> is used for read operations. <u>QV</u> = V <sub>IL</sub> when output data is valid on the data bus for either a single or burst-read operation. When <u>QV</u> = V <sub>IH</sub> , there is no valid data on the data bus. For QV usage, see Table 8 and Table 9.                                                                                                                                                                                                 |

| <u>RY/BY</u>                      | OD O  | Ready/busy. <u>RY/BY</u> indicates the status of the WSM. When <u>RY/BY</u> = V <sub>IL</sub> , the WSM is currently active performing an operation. When <u>RY/BY</u> = V <sub>IH</sub> , the WSM is ready for a new operation. For RY/BY usage, see Table 8 and Table 9.                                                                                                                                                                                                              |

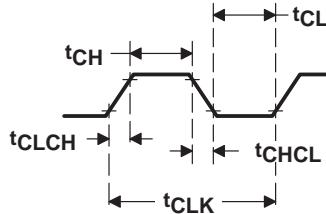

| CLK                               | I     | Clock. Signals on both the address and data buses are transmitted and received relative to this system clock. All synchronous inputs must meet setup and hold times relative to the rising CLK edge.                                                                                                                                                                                                                                                                                    |

| 3/5IO                             | I     | 3.3/5.0 I/O select. 3/5IO is used to select the external power supply, V <sub>DDE</sub> , as either 3.3 V or 5 V. Set 3/5IO = V <sub>IH</sub> for V <sub>DDE</sub> = 3.3 V operation, and set 3/5IO = V <sub>IL</sub> for V <sub>DDE</sub> = 5 V operation. For 3/5IO usage, see Table 8 and Table 9.                                                                                                                                                                                   |

† I = input, O = output, OD = open drain, S = power supply

**Terminal Functions (Continued)**

| TERMINAL NAME    | TYPE <sup>†</sup> | DESCRIPTION                                                                                        |

|------------------|-------------------|----------------------------------------------------------------------------------------------------|

| V <sub>PP</sub>  | S                 | Write/erase power supply. V <sub>PP</sub> is the 12-V power supply for the write/erase operations. |

| V <sub>DDI</sub> | S                 | Internal power supply. V <sub>DDI</sub> is the 5-V power supply for the internal logic.            |

| V <sub>DDE</sub> | S                 | External power supply. V <sub>DDE</sub> is the 3.3-V/5-V power supply for the inputs and outputs.  |

| V <sub>SSE</sub> | S                 | Output ground. V <sub>SSE</sub> is the ground for the outputs DQ0–DQ31, RY/BY, and QV.             |

| V <sub>SII</sub> | S                 | Input ground. V <sub>SII</sub> is the ground for both the inputs and internal logic.               |

| NC               |                   | No connect. These pins are left unconnected inside the memory chip.                                |

<sup>†</sup>I = input, O = output, OD = open drain, S = power supply

## architecture

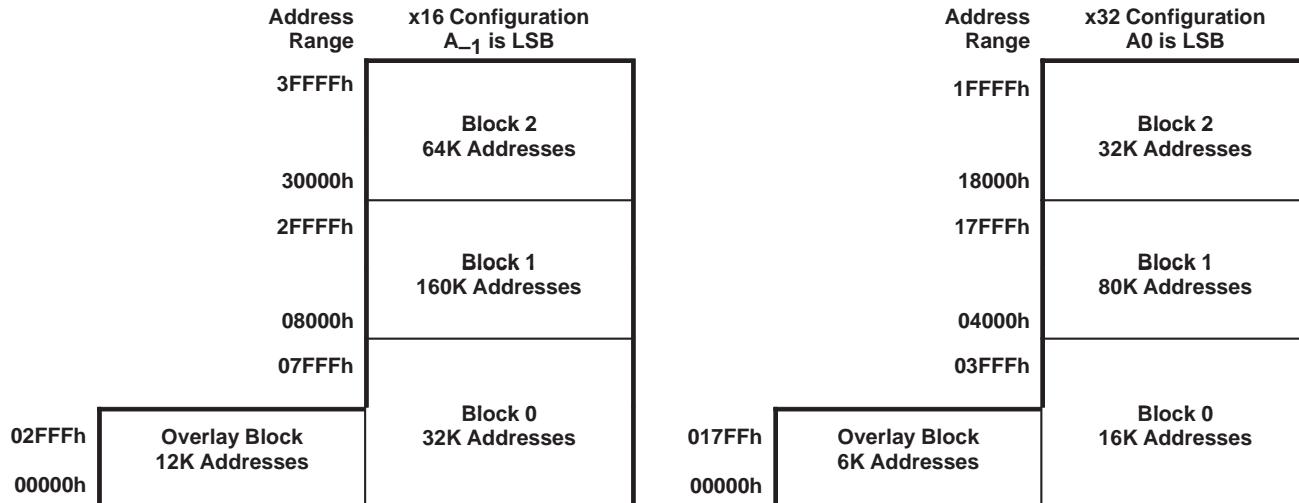

The TMS28F033 uses a blocked architecture to allow independent erasure of selected memory blocks. The block to be erased is selected by using any valid address within the block. Figure 1 and Figure 2 show the memory maps for the two configurations.

## main memory

The TMS28F033 main memory is configurable to either three blocks (DCR5 = 0) or four blocks (DCR5 = 1), see Table 1, and Figure 1 and Figure 2.

Figure 1. TMS28F033 With Three-Block Main-Array Memory Map (DCR5=0)

# TMS28F033

## 4194304-BIT

### SYNCHRONOUS FLASH MEMORY

SMJS833 – NOVEMBER 1997

#### main memory (continued)

Figure 2. TMS28F033 With Four-Block Main-Array Memory Map (DCR5 = 1)

#### overlay block

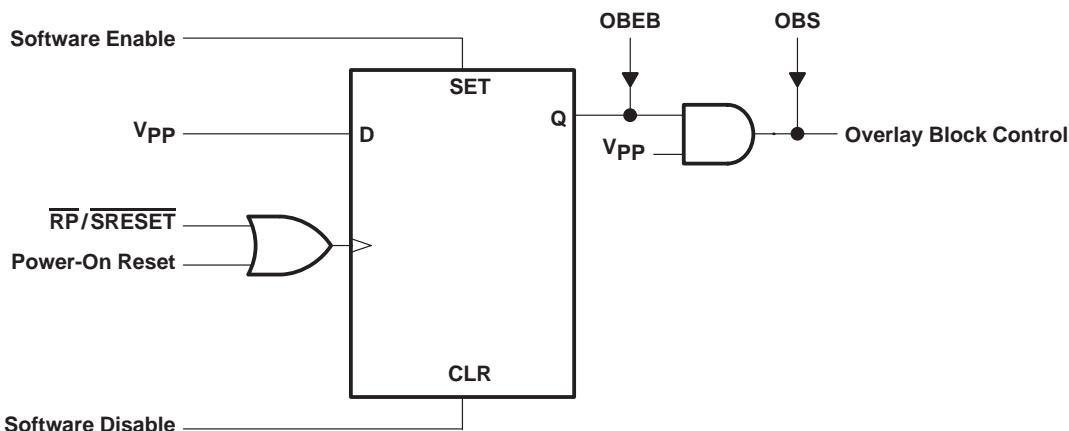

The overlay block is a protected memory region that is programmed or erased using special command state machine (CSM) commands (see Table 4 and Table 5). When enabled, the overlay memory block exists from addresses 00000h to 017FFh for x32 addressing, or from 00000h to 02FFFh for x16 addressing. Two status register bits, OBEB and OBS, are available to monitor the overlay block enable/disable process (see Table 7). The overlay block status (OBS) bit indicates whether the overlay block is enabled (OBS = 1) or disabled (OBS = 0) for reading. See Table 2 for the state of the OBS bit for memory-read accessing. The status of the overlay-block-enable bit (OBEB) does not necessarily indicate that the overlay block is enabled, instead OBEB reflects the state of the overlay block control switch. When OBEB = 1, the switch is set, and when OBEB = 0, the switch is not set (see the overlay-block-control functional diagram in Figure 3). See Table 3 for a listing of methods that set/clear the OBEB.

Table 2. Read-Accessing of the Overlay Block or Main Array

| STATE OF OBEB<br>(SB1) | V <sub>PP</sub> STATUS                                | STATE OF OBS<br>(SB0) | READ ACCESS   |

|------------------------|-------------------------------------------------------|-----------------------|---------------|

| 1                      | V <sub>PP</sub> ≥ V <sub>PPH</sub>                    | 1                     | Overlay Block |

| 1                      | V <sub>PP</sub> ≤ V <sub>PPL</sub>                    | 0                     | Main Array    |

| 0                      | x <sup>†</sup>                                        | 0                     | Main Array    |

| 1                      | V <sub>PPL</sub> < V <sub>PP</sub> < V <sub>PPH</sub> | Not guaranteed        | Unknown       |

<sup>†</sup>X is a don't care.

### overlay block (continued)

**Table 3. Methods of Setting/Clearing the Overlay-Block-Enable Bit (OBEB)**

| METHOD                                                 | PRIOR STATE OF OBEB | NEXT STATE OF OBEB |

|--------------------------------------------------------|---------------------|--------------------|

| Toggle RP with $V_{PP} \geq V_{PPH}$                   | $x^\dagger$         | 1                  |

| Toggle RP with $V_{PP} \leq V_{PPL}$                   | $x^\dagger$         | 0                  |

| Power-on-reset of $V_{DDI}$ with $V_{PP} \geq V_{PPH}$ | $x^\dagger$         | 1                  |

| Power-on-reset of $V_{DDI}$ with $V_{PP} \leq V_{PPL}$ | $x^\dagger$         | 0                  |

| Issue CSM command 06h                                  | 0                   | 1                  |

| Enable/disable overlay block for reads                 | 1                   | 0                  |

$\dagger$  X is a don't care.

The enable/disable-overlay-block CSM command (06h) is used to enable the overlay block for a read operation, or to disable the overlay block after a read operation. When 06h is issued for overlay-block access, both the overlay-block latch and OBEB are set whether  $V_{PP} \geq V_{PPH}$  or not. However, only the overlay block is enabled (and only OBS is set) if  $V_{PP} \geq V_{PPH}$ .

**Figure 3. Overlay-Block-Control Functional Diagram**

### command state machine (CSM)

Commands are issued to the CSM using standard microprocessor write timings. The CSM acts as an interface between the external microprocessor and the internal WSM. The available commands are listed in Table 4 and the corresponding descriptions are in Table 5. When a program or erase command is issued to the CSM, the WSM controls the internal sequences and the CSM responds only to status reads. A command is valid only if the exact sequence of writes is completed. After the WSM completes its task, the WSM status bit (SB7) is set to a logic-high level, allowing the CSM to respond to the full command set again. In addition, Ready/Busy (RY/BY) is an optional output that is available to monitor the WSM status.

### operation

Device operations are selected by entering standard JEDEC 8-bit command codes with conventional microprocessor timing into an on-chip CSM through I/O pins DQ0–DQ7. When the device is powered up, internal reset circuitry initializes the chip to a read-array mode of operation. Changing the mode of operation requires a command code to be entered into the CSM.

The on-chip status register allows the progress of various operations to be monitored. The status register is interrogated by entering a read-status-register command into the CSM (cycle 1) and reading the register data on I/O pins DQ0–DQ7 (cycle 2). Status register bits SB0 through SB7 correspond to DQ0 through DQ7.

**TMS28F033**

**4194304-BIT**

**SYNCHRONOUS FLASH MEMORY**

SMJS833 – NOVEMBER 1997

**operation (continued)**

**Table 4. Command-State-Machine Codes for Device Mode Selection**

| COMMAND CODE ON DQ0–DQ7† | DEVICE MODE                            |

|--------------------------|----------------------------------------|

| 02h                      | Block-erase setup of overlay block     |

| 04h                      | Program setup of overlay block         |

| 06h                      | Enable/disable overlay block for reads |

| 0Dh                      | Block-erase confirm of overlay block   |

| 20h                      | Block-erase setup of main array        |

| 40h                      | Program setup of main array            |

| 50h                      | Clear status register                  |

| 60h                      | Enable/disable low-power programming   |

| 70h                      | Read status register                   |

| 90h                      | Silicon signature selection            |

| 96h                      | Load device-configuration register     |

| D0h                      | Block-erase confirm of main array      |

| F0h                      | Reduced power                          |

| FFh                      | Read array                             |

† DQ0 is the least significant bit. DQ8–DQ31 can be any valid 2-state level.

**command definition**

Once a specific command code has been entered, the WSM executes an internal algorithm that generates the necessary timing signals to program, erase, and verify data. See Table 5 for the CSM command definitions and the data for each of the bus cycles. See Table 6 for the addresses required to access the algorithm selection codes.

**command definition (continued)**

**Table 5. Command Definitions**

| COMMAND                                                 | DATA<br>BUS<br>WIDTH | FIRST BUS CYCLE |         |              | SECOND BUS CYCLE |                |                | THIRD BUS CYCLE |         |                |

|---------------------------------------------------------|----------------------|-----------------|---------|--------------|------------------|----------------|----------------|-----------------|---------|----------------|

|                                                         |                      | OPERATION       | ADDRESS | CSM<br>INPUT | OPERATION        | ADDRESS        | DATA<br>IN/OUT | OPERATION       | ADDRESS | DATA<br>IN/OUT |

| <b>READ OPERATIONS</b>                                  |                      |                 |         |              |                  |                |                |                 |         |                |

| Read Array                                              | x16/x32              | Write           | 00000h† | FFh          | Read             | RA             | DO             |                 |         |                |

| Read Algorithm Selection Code (see Note 1, and Table 6) | x16/x32              | Write           | 00000h† | 90h          | Read             | A1A0           | M/D<br>DCR     |                 |         |                |

| Read Status Register                                    | x16/x32              | Write           | 00000h† | 70h          | Read             | X              | SRB            |                 |         |                |

| <b>PROGRAM OPERATIONS</b>                               |                      |                 |         |              |                  |                |                |                 |         |                |

| Program Setup/Program of Main Array (see Note 1)        | x16                  | Write           | 00000h† | 40h          | Write            | A <sub>1</sub> | PD(L,H)        | Write           | PA      | PD(H,L)        |

|                                                         | x16/x32              | Write           | 00000h† | 40h          | Write            | PA             | PD             |                 |         |                |

| Program Setup/Program of Overlay Block (see Note 1)     | x16                  | Write           | 00000h† | 04h          | Write            | A <sub>1</sub> | PD(L,H)        | Write           | PA      | PD(H,L)        |

|                                                         | x16/x32              | Write           | 00000h† | 04h          | Write            | PA             | PD             |                 |         |                |

| Load DCR                                                | x16/x32              | Write           | 00000h† | 96h          | Write            | X              | CV             |                 |         |                |

| <b>ERASE OPERATIONS</b>                                 |                      |                 |         |              |                  |                |                |                 |         |                |

| Block-Erase Setup/Block-Erase Confirm of Main Array     | x16/x32              | Write           | 00000h† | 20h          | Write            | BBA            | D0h            |                 |         |                |

| Block-Erase Setup/Block-Erase Confirm of Overlay Block  | x16/x32              | Write           | 00000h† | 02h          | Write            | BBA            | 0Dh            |                 |         |                |

| <b>OTHER OPERATIONS</b>                                 |                      |                 |         |              |                  |                |                |                 |         |                |

| Reduced-Power Mode                                      | x16/x32              | Write           | 00000h† | F0h          |                  |                |                |                 |         |                |

| Enable/Disable Low-Power Programming                    | x16/x32              | Write           | 00000h† | 60h          |                  |                |                |                 |         |                |

| Clear Status Register                                   | x16/x32              | Write           | 00000h† | 50h          |                  |                |                |                 |         |                |

| Enable/Disable Overlay Block for Read                   | x16/x32              | Write           | 00000h† | 06h          |                  |                |                |                 |         |                |

† Address is a don't care for asynchronous writes.

NOTE 1: When using x16 (DCR31 = 1 and WORD = V<sub>IL</sub>), programming can be performed in either two or three cycles by configuring the DCR31 bit (see Table 8).

**Legend:**

**ADDRESS**

BBA = Block base address

PA = Address to be programmed

RA = Read address

X = Don't care

**DATA**

CV = Configuration value

DO = Read data out

M/D/DCR = Manufacturer code/device configuration register value

SRB = Status-register data byte on DQ0–DQ7

PD(L,H) = Data to be programmed at PA (low word, high word)

**TMS28F033**

**4194304-BIT**

**SYNCHRONOUS FLASH MEMORY**

SMJS833 – NOVEMBER 1997

**command definition (continued)**

**Table 6. Algorithm Selection Codes (See Note 2)**

| DATA BUS WIDTH         | ADDRESS<br>(A0–A16) | A1              | A0              | A–1 | DATA OUT                    |

|------------------------|---------------------|-----------------|-----------------|-----|-----------------------------|

|                        | X0h                 | V <sub>IL</sub> | V <sub>IL</sub> | X   | Manufacturer Code 0097h     |

| 16-Bit<br>(see Note 3) | X1h                 | V <sub>IL</sub> | V <sub>IH</sub> | X   | Device Code 0068h           |

|                        | X2h                 | V <sub>IH</sub> | V <sub>IL</sub> | X   | DCR Value DDDDh             |

|                        | X0h                 | V <sub>IL</sub> | V <sub>IL</sub> | —   | Manufacturer Code 00000097h |

| 32-Bit<br>(see Note 4) | X1h                 | V <sub>IL</sub> | V <sub>IH</sub> | —   | Device Code 00000068h       |

|                        | X2h                 | V <sub>IH</sub> | V <sub>IL</sub> | —   | DCR Value DD0000DDh         |

NOTES: 2. X is a don't care.

3. When using the 16-bit data bus, the data lines are DQ0–DQ7 and DQ23–DQ31.

4. When using the 32-bit data bus, the data lines are DQ0–DQ31.

**status register**

The status register allows the user to determine whether the state of a program/erase operation is pending or complete. The status register is monitored by writing a read-status command to the CSM and reading the resulting status code on I/O pins DQ0–DQ7. This operation is valid in either the word-wide (x16) or double-word-wide (x32) mode. The high-order I/Os (DQ8–DQ31) are set to 000000h internally.

After a read-status command has been given, the data appearing on DQ0–DQ7 remains as status register data until a new command is issued to the CSM. To return the device to other modes of operation, a new command must be issued to the CSM. Status register data is updated on every clock cycle. During periods when the WSM is active, the status register can be read to determine the WSM status. Table 7 defines the status-register bits and their functions.

**status register (continued)**

**Table 7. Status-Register Bit Definitions and Functions**

| STATUS BIT     | FUNCTION                            | DATA                                                                          | COMMENTS                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SB7            | Write-State-Machine (WSM) Status    | 1 = Ready<br>0 = Busy                                                         | If SB7 = 0 (busy), the WSM has not completed an erase or programming operation. If SB7 = 1 (ready), other operations can be performed.                                                                                                                                                                                  |

| SB6            | Reserved                            | 0                                                                             |                                                                                                                                                                                                                                                                                                                         |

| SB5 (DCR4 = 0) | Operation Status (OS)               | 1 = Commands/operations not successful<br>0 = Commands/operations successful  | The WSM sets the OS bit high (SB5 = 1) after an illegal command has been issued, an error has occurred while erasing a block, or as the result of an error while programming a word. If all past operations have completed successfully, then the OS bit remains low (SB5 = 0); however, the WSM cannot clear this bit. |

| SB5 (DCR4 = 1) | Erase Status (ES)                   | 1 = Block-erase error<br>0 = Block-erase good                                 | SB5 = 0 indicates that a block-erase has been successful. SB5 = 1 indicates that an erase error has occurred. In this case, the WSM has completed the maximum erase pulses determined by the internal algorithm, but this was insufficient to completely erase the device.                                              |

| SB4 (DCR4 = 0) | Low Regulator Voltage Status (LRVS) | 1 = <u>LRV</u> asserted<br>0 = <u>LRV</u> not asserted                        | The LRVS bit is set high (SB4 = 1) when the <u>LRV</u> input is asserted during an erase or program command. The clear-status-register command clears the LRVS bit (SB4 = 0).                                                                                                                                           |

| SB4 (DCR4 = 1) | Program Status (PS)                 | 1 = Program error<br>0 = Program good                                         | SB4 = 0 indicates successful programming has occurred at the addressed location. SB4 = 1 indicates that the WSM was unable to correctly program the addressed location.                                                                                                                                                 |

| SB3            | V <sub>PP</sub> Status (VPPS)       | 1 = Program abort:<br>V <sub>PP</sub> range error<br>0 = V <sub>PP</sub> good | SB3 provides information on the status of V <sub>PP</sub> during programming and erasing. If V <sub>PP</sub> is lower than V <sub>PP</sub> <sub>L</sub> after a program or erase command has been issued, SB3 is set to a 1 to indicate that the operation is aborted.                                                  |

| SB2            | Low-Power Mode (LPM)                | 1 = Byte-program<br>0 = Word-program                                          | When the LPM bit is set high (SB2 = 1), the WSM programs each word in byte increments. When the LPM bit is low (SB2 = 0), the WSM programs in word (x32 or x16) increments.                                                                                                                                             |

| SB1            | Overlay-Block-Enable Bit (OBEB)     | 1 = Overlay block can be enabled<br>0 = Overlay block disabled                | When the OBEB bit, which is V <sub>PP</sub> -independent, is set (SB1 = 1), the overlay block can be enabled for reads. When the OBEB bit is low (SB1 = 0), the overlay block is disabled for reads.                                                                                                                    |

| SB0            | Overlay-Block Status (OBS)          | 1 = Overlay block enabled<br>0 = Overlay block disabled                       | When the OBS bit, with V <sub>PP</sub> ≥ V <sub>PP</sub> <sub>H</sub> , is set (SB0 = 1), the overlay block is enabled for reads. When the OBS bit is cleared (SB0 = 0), the overlay block is disabled for reads.                                                                                                       |

**device configuration register (DCR)**

The DCR is a user-loaded register that determines many of the device functions (see Table 8). Sixteen configurable bits (DCR0–DCR7 and DCR24–DCR31 with DCR26–27 reserved) can be set by using the load-DCR CSM command (96h) (see Table 5). The current value of the DCR can be read with CSM command 90h, provided A1 is set to V<sub>IL</sub> and A0 is set to V<sub>IL</sub> (see Table 6).

# TMS28F033

## 4194304-BIT

### SYNCHRONOUS FLASH MEMORY

SMJS833 – NOVEMBER 1997

#### device configuration defaults

The term “default” denotes the state of a bit in the DCR when the device is first powered up or when a power-on reset is performed. These defaults are set at the factory after fabrication. After the CSM command that loads the DCR (96h) is executed, the defaults no longer define the device operation; instead, the new configuration takes effect. To restore the default state, either perform a power-on reset or load the DCR with the reset-state settings using the 96h command sequence.

The TMS28F033 has two types of defaults: a fuse-bit-option default and a standard default. The difference between the two types is that a fuse-bit-option default can be optionally set (0 or 1) at the factory, whereas a standard default is always set to 0 at the factory. The DCR has eight fuse-bit-option defaults, DCR0–DCR7, and eight standard defaults, DCR24–DCR31. The X-latency bits DCR28–DCR29 are the only exceptions to these two types of defaults. These bits default to 00 (standard defaults), except when the device is in x16 mode ( $\overline{\text{WORD}} = \text{V}_{\text{IL}}$ ) or when  $\overline{\text{OE}}$  is asynchronous (DCR1 = 1). In these exceptions, the DCR28–DCR29 bits function as 10 (see Table 8). It is important to note that even though DCR28–DCR29 functions as 10 for these exceptions, they are still read (with the DCR read command 90h) as 00, instead of 10.

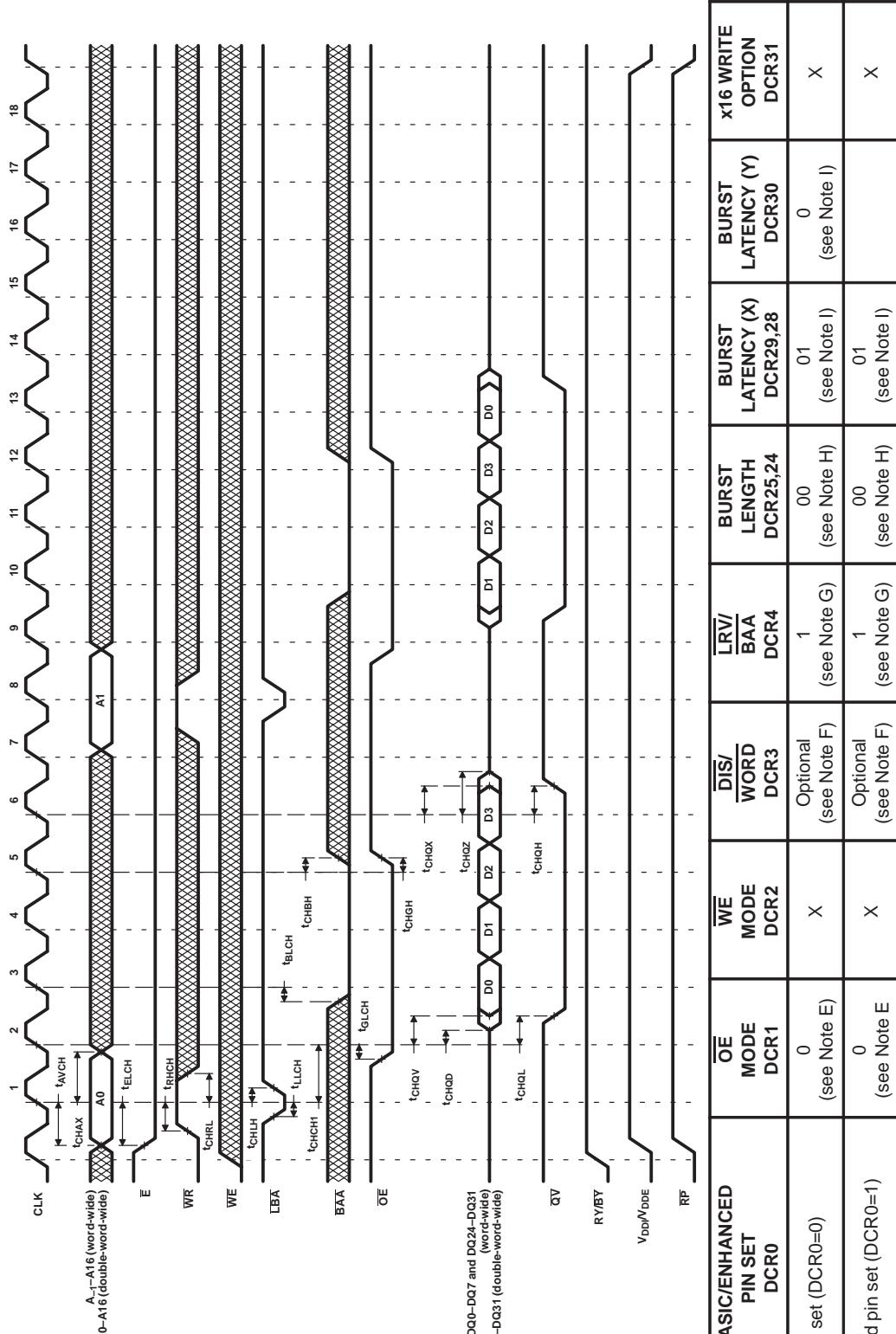

**Table 8. Device Configuration Register Bit Definitions and Functions**

| DCR BIT    | FUNCTION                                   | DATA                                                                                                      | COMMENTS                                                                                                                                                                                                                                                                                                                                               |

|------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCR0       | Control pin configuration                  | 0 = Basic Control Pin Set<br>1 = Enhanced Control Pin Set (see Note 5 and Note 6)                         | When DCR0 = 0, the device functions with the basic pin set, and the internal pullups are enabled for the $\overline{\text{RP}}$ , $\overline{\text{BAA/LRV}}$ , and $\overline{\text{WORD/DIS}}$ pins. When DCR0 = 1, the device functions with the enhanced pin set. See the Terminal Functions table and Table 9                                     |

| DCR1       | $\overline{\text{OE}}$ functionality       | 0 = Synchronous $\overline{\text{OE}}$<br>1 = Asynchronous $\overline{\text{OE}}$ (see Note 5 and Note 6) | When DCR1 = 0, $\overline{\text{OE}}$ functions as a synchronous output enable. When DCR1 = 1, $\overline{\text{OE}}$ functions asynchronously. See the Terminal Functions table and Table 9                                                                                                                                                           |

| DCR2       | $\overline{\text{WE}}$ functionality       | 0 = Synchronous $\overline{\text{WE}}$<br>1 = Asynchronous $\overline{\text{WE}}$ (see Note 5 and Note 6) | When DCR2 = 0, $\overline{\text{WE}}$ functions as a synchronous write enable. When DCR2 = 1, $\overline{\text{WE}}$ functions asynchronously. See the Terminal Functions table and Table 9                                                                                                                                                            |

| DCR3       | $\overline{\text{WORD/DIS}}$ functionality | 0 = $\overline{\text{DIS}}$ , and x32 mode<br>1 = $\overline{\text{WORD}}$ (see Note 5 and Note 6)        | When DCR3 = 0, pin 78 functions as output disable ( $\overline{\text{DIS}}$ ) and the device is forced into x32 mode. When DCR3 = 1, pin 78 functions as $\overline{\text{WORD}}$ (for x16 mode, set $\text{WORD} = \text{V}_{\text{IL}}$ ; and for x32 mode, set $\text{WORD} = \text{V}_{\text{IH}}$ ). See the Terminal Functions table and Table 9 |

| DCR4       | $\overline{\text{BAA/LRV}}$ functionality  | 0 = $\overline{\text{LRV}}$<br>1 = $\overline{\text{BAA}}$ (see Note 5 and Note 6)                        | When DCR4 = 0, pin 79 functions as low regulator voltage ( $\overline{\text{LRV}}$ ) and its status can be monitored in SB4. When DCR4 = 1, pin 79 functions as burst address advance ( $\overline{\text{BAA}}$ ). See the Terminal Functions table and Table 9                                                                                        |

| DCR5       | Main block control                         | 0 = 3 Main Blocks<br>1 = 4 Main Blocks (see Note 5 and Note 6)                                            | When DCR5 = 0, the main memory array has three blocks, as seen in Figure 1. When DCR5 = 1, the main memory array has four blocks, as seen in Figure 2. See Table 1.                                                                                                                                                                                    |

| DCR7, DCR6 | Internal timing control                    | Refer to switching characteristics for $t_{\text{CHCH1}}$ and $t_{\text{CHQV}}$ (see Note 5 and Note 6)   | These bits are used to optimize device performance (see switching characteristics table).                                                                                                                                                                                                                                                              |

NOTES: 5. The default setting for these bits is set at the factory prior to shipping.

6. These bits return to the default setting after a power-on reset is performed; therefore, it is necessary to program these bits to the desired configuration.

**device configuration defaults (continued)**

**Table 8. Device Configuration Register Bit Definitions and Functions (Continued)**

| DCR BIT      | FUNCTION                                                    | DATA                                                                                                                                                                                                                | COMMENTS                                                                                                                                                                                                                                                                       |

|--------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCR8–DCR23   | Reserved for Texas Instruments (TI™) and should not be used | 0000h                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                |

| DCR25, DCR24 | Burst length                                                | 00 = MOD4 (default)<br>01 = MOD8<br>10 = MOD16<br>11 = MOD32<br>(see Note 6)                                                                                                                                        | There are four available burst length settings. The MOD4 burst is a modulo burst of four words/double-words for x16/x32, respectively. The other available burst lengths are MOD8, MOD16, and MOD32 (see Table 12).                                                            |

| DCR27, DCR26 | Reserved for TI and should not be used                      | 00 – (default)<br>(see Note 6)                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                |

| DCR29, DCR28 | Burst latency (X)                                           | 00 = <u>OE</u> -controlled (default if in x32 mode and when <u>OE</u> is synchronous)<br>01 = 3 cycles<br>10 = 4 cycles (default if in x16 mode or when <u>OE</u> is asynchronous)<br>11 = 5 cycles<br>(see Note 6) | The four X latency possibilities are <u>OE</u> -controlled burst, and 3, 4, or 5 clock cycles for BAA-controlled burst. X latency denotes the number of clock cycles required to access the first word from memory (see Table 10 and Table 11).                                |

| DCR30        | Burst latency (Y)                                           | 0 = 1 cycle (default)<br>1 = 2 cycles<br>(see Note 6)                                                                                                                                                               | The two Y latency possibilities are one clock cycle and two clock cycles. Y latency denotes the number of clock cycles required to access the subsequent words to complete the cache fill (see Table 10 and Table 11).                                                         |

| DCR31        | One- or two-word write option for x16 mode                  | 0 = Program one word (two-cycle write) (default)<br>1 = Program two words (three-cycle write)<br>(see Note 6)                                                                                                       | Applicable for x16 mode only. When DCR31 = 0, only one word (16 bits) is programmed in two cycles for each program command received by the CSM. When DCR31 = 1, two words (32 bits) are programmed in three cycles for each program command received by the CSM (see Table 5). |

NOTES: 5. The default setting for these bits is set at the factory prior to shipping.

6. These bits return to the default setting after a power-on reset is performed; therefore, it is necessary to program these bits to the desired configuration.

**control pin functions**

The DCR0 bit is the control pin configuration bit that selects between the basic or enhanced pin set (see Table 8 and Table 9). With the enhanced pin set (DCR0 = 1), five additional pins are available: chip enable (E), data valid (QV), ready/busy (RY/BY), 3.3-V/5-V IO voltage select (3/5IO), and linear burst order (LBO). With the basic pin set (DCR0 = 0), neither QV nor RY/BY are available, both E and LBO are effectively tied low (V<sub>IL</sub>), and 3/5IO is effectively tied high (V<sub>IH</sub>). The DCR1 and DCR2 bits determine the synchronous or asynchronous operation of output enable (OE) and write enable (WE), respectively. DCR3 determines the function of pin 78 as either output disable (DIS) or word enable (WORD) (see the Terminal Functions table). When DCR3 = 0 (for DIS usage) the device is forced into using the 32-bit data bus (see Figure 21). When DCR3 = 1, both the 16-bit and 32-bit data buses are available. The DCR4 bit determines the function of pin 79 as either low-regulator-voltage detection (LRV) or burst-address advance (BAA).

**TMS28F033**

**4194304-BIT**

**SYNCHRONOUS FLASH MEMORY**

SMJS833 – NOVEMBER 1997

**control pin functions (continued)**

**Table 9. DCR-Controlled Pin Functions**

| PIN NUMBER | DCR BIT (x) | DCRx = 0                    | DCRx = 1                     |

|------------|-------------|-----------------------------|------------------------------|

| 68         | 0           | Hi-Z                        | $\overline{QV}$              |

| 69         | 0           | Hi-Z                        | $\overline{RY/BY}$           |

| 72         | 0           | 3.3-V IO                    | $\overline{3/5IO}$           |

| 74         | 0           | Chip Enabled                | $\overline{E}$               |

| 75         | 1           | Synchronous $\overline{OE}$ | Asynchronous $\overline{OE}$ |

| 76         | 2           | Synchronous $\overline{WE}$ | Asynchronous $\overline{WE}$ |

| 78         | 3           | $\overline{DIS}$            | $\overline{WORD}$            |

| 79         | 4           | $\overline{LRV}$            | $\overline{BAA}$             |

| 80         | 0           | Linear Burst                | $\overline{LBO}$             |

**burst length**

The burst length, as determined by DCR24–DCR25, is the length of the data sequence (or number of memory locations) to be read for each entered address. When using  $\overline{BAA}$  (DCR4 = 1), there are four possibilities for burst length: modulo 4 addressing (MOD4), MOD8, MOD16, and MOD32. For MOD4, when the initial address is XXXX0h, the internal burst address order is 0–1–2–3 for linear burst ( $LBO = V_{IL}$ ). MOD8, MOD16, and MOD32 function as 0–1–2 . . . 6–7, 0–1–2 . . . 14–15, and 0–1–2 . . . 30–31, respectively. Burst delivery is critical word first with wrap around.

**burst access and burst performance**

The notation X–Y– . . . –Y is used to denote the X and Y burst latency for the data sequence to be burst. X-latency (DCR28–DCR29) denotes the number of clock cycles required to access the first word/double-word from memory, and Y-latency (DCR30) denotes the number of clock cycles required to access the subsequent words/double-words to complete the cache fill (see Table 10). The four X-latency possibilities are:  $\overline{OE}$ -controlled, and 3, 4, or 5 clock cycles. The two Y-latency possibilities are 1 and 2 clock cycles. The burst performance for <25 MHz, <33 MHz, and <40 MHz for linear and interleave burst order is listed in Table 11.

**Table 10. Burst Access Combinations (see Note 7)**

| DEVICE CONFIGURATION REGISTER BITS |       |       | BURST ACCESS<br>(CLOCK CYCLES TO READ) |

|------------------------------------|-------|-------|----------------------------------------|

| DCR30                              | DCR29 | DCR28 |                                        |

| 0                                  | 0     | 0     | X–1– . . . –1 (see Note 8)             |

| 0                                  | 0     | 1     | 3–1– . . . –1                          |

| 0                                  | 1     | 0     | 4–1– . . . –1                          |

| 0                                  | 1     | 1     | 5–1– . . . –1                          |

| 1                                  | 0     | 0     | X–2– . . . –2 (see Note 8)             |

| 1                                  | 1     | 0     | 4–2– . . . –2                          |

NOTES: 7. These burst access combinations are available for MOD4, MOD8, MOD16, and MOD32.

8. For both DCR30–DCR28 = 000 and DCR30–DCR28 = 100, the X-latency is  $\overline{OE}$ -controlled.

### burst access and burst performance (continued)

**Table 11. Burst Performance (Clock Cycles to Read)**

| FREQUENCY (MHz)          | x16 Mode            |                     |               |               | x32 Mode      |

|--------------------------|---------------------|---------------------|---------------|---------------|---------------|

|                          | LINEAR <sup>†</sup> |                     | INTERLEAVE    | LINEAR        |               |

|                          | A <sub>-1</sub> = 0 | A <sub>-1</sub> = 1 |               |               |               |

| <25 (see Note 9)         | 4–2– . . . –2       | 4–2– . . . –2       | 4–2– . . . –2 | 4–2– . . . –2 | 4–2– . . . –2 |

| <33 (see Note 9)         | 4–2– . . . –2       | 5–1– . . . –1       | 4–1– . . . –1 | 4–2– . . . –2 | 4–2– . . . –2 |

| <40 (see Notes 9 and 10) | —                   | —                   | —             | —             | 5–2– . . . –2 |

<sup>†</sup> The state of A<sub>-1</sub> when the address is latched (at CLK 1 in Figure 14)

NOTES: 9. The Y-latency notation for MOD4 has three 1s/2s (–1–1–1–2–2–2). For MOD8, there are seven 1s/2s (–1–1–1–1–1–1–2–2–2–2–2–2). MOD16 has fifteen 1's/2's, and MOD32 has 31 1's/2's.

10. To obtain 5–2– . . . –2 (40 MHz), the required DCR settings are 4–2– . . . –2, and asynchronous  $\overline{OE}$  with  $\overline{BAA}$ -controlled burst.

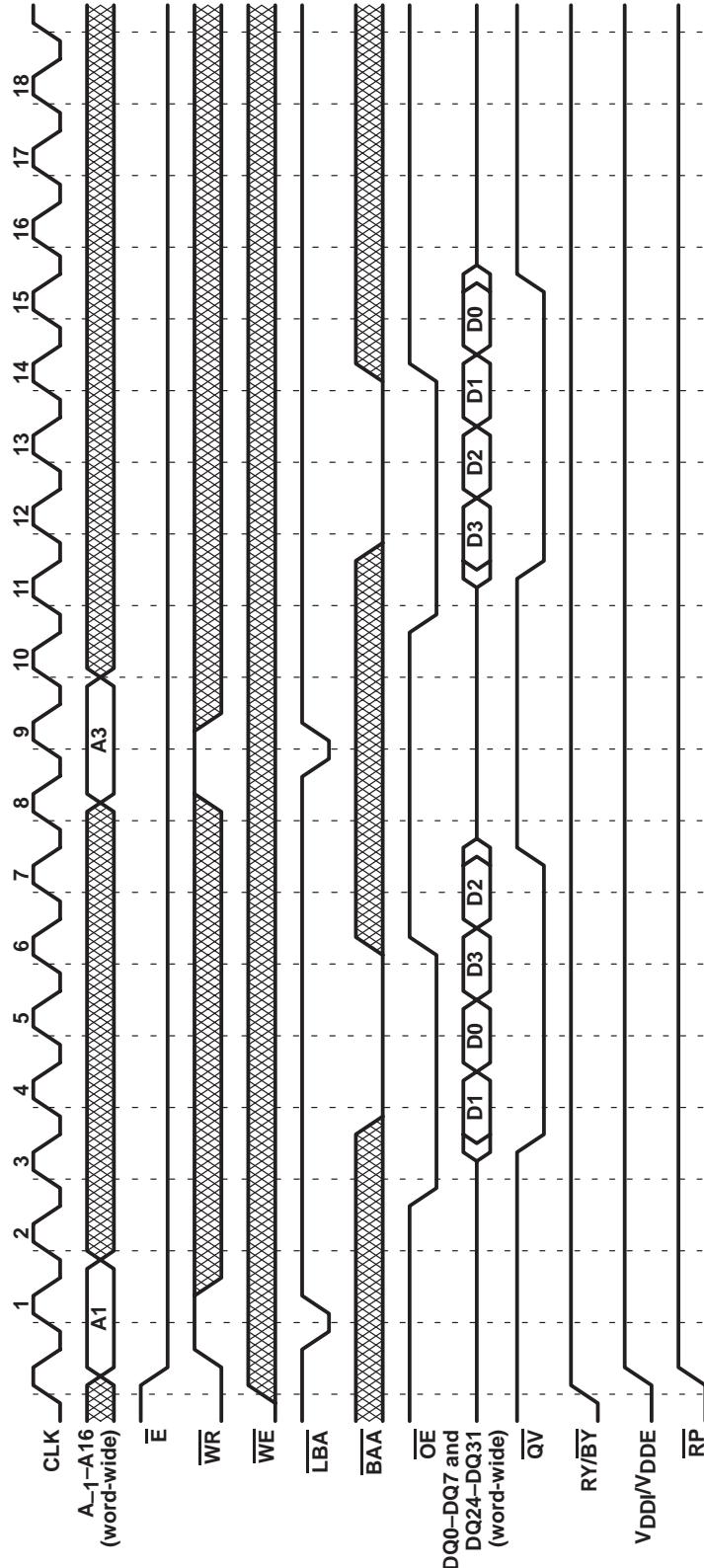

### burst suspend/resume

Burst suspension is the ability to hold the address advance and the data on the output I/Os DQ0–DQ7 and DQ24–DQ31 if in x16 mode, or on DQ0–DQ31 if in x32 mode. For DCR4 = 1, the suspension of a burst sequence is possible by bringing  $\overline{BAA}$  high. To resume the burst, bring  $\overline{BAA}$  low again (see Figure 18). When DCR4 = 0, the suspension of the burst is possible by bringing  $\overline{OE}$  high. To resume the burst, bring  $\overline{OE}$  low again.

### linear burst order (LBO)

When performing a burst read, a single starting address is entered into the device and then the TMS28F033 internally accesses a sequence of locations based on that starting address. The burst sequence is determined by the linear burst order (LBO) setting (see the Terminal Functions table). When  $LBO = V_{IL}$ , the burst order is linear 0–1–2–3 . . . ; and when  $LBO = V_{IH}$ , the burst order is interleave (see Table 12). Linear burst order is available with MOD4, MOD8, MOD16, and MOD32. Interleave burst order is available only with MOD4, and only with the 16-bit data bus.

**Table 12. 2-Bit Linear and Interleaved-Burst Sequences (MOD4)**

| BURST<br>SEQUENCE           | ADDRESS<br>A1–A0 For x32 Mode, AND A0–A <sub>-1</sub> For x16 Mode |     |     |                  |        |     |     |                  |

|-----------------------------|--------------------------------------------------------------------|-----|-----|------------------|--------|-----|-----|------------------|

|                             | DECIMAL                                                            |     |     |                  | BINARY |     |     |                  |

|                             | START                                                              | 2ND | 3RD | 4TH <sup>†</sup> | START  | 2ND | 3RD | 4TH <sup>†</sup> |

| Linear<br>(see Note 11)     | 0                                                                  | 1   | 2   | 3                | 00     | 01  | 10  | 11               |

|                             | 1                                                                  | 2   | 3   | 0                | 01     | 10  | 11  | 00               |

|                             | 2                                                                  | 3   | 0   | 1                | 01     | 10  | 11  | 00               |

|                             | 3                                                                  | 0   | 1   | 2                | 11     | 00  | 01  | 10               |

| Interleave<br>(see Note 12) | 0                                                                  | 1   | 2   | 3                | 00     | 01  | 10  | 11               |

|                             | 1                                                                  | 0   | 3   | 2                | 01     | 00  | 11  | 10               |

|                             | 2                                                                  | 3   | 0   | 1                | 10     | 11  | 00  | 01               |

|                             | 3                                                                  | 2   | 1   | 0                | 11     | 10  | 01  | 00               |

<sup>†</sup> Burst sequence continues until  $OE$  or  $BAA$  is brought high.

NOTES: 11. Linear burst is available with both x16 and x32 for MOD4, MOD8, MOD16, and MOD32. For linear burst set  $LBO = V_{IL}$ .

12. Interleaved burst is available only with MOD4, and only with the 16-bit data bus. For interleave burst set  $LBO = V_{IH}$ .

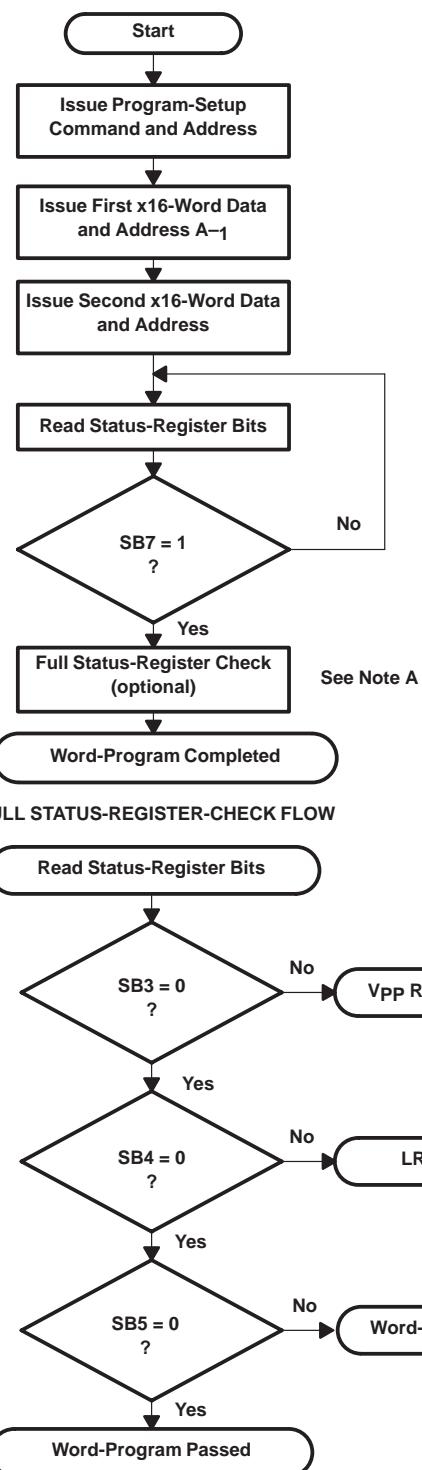

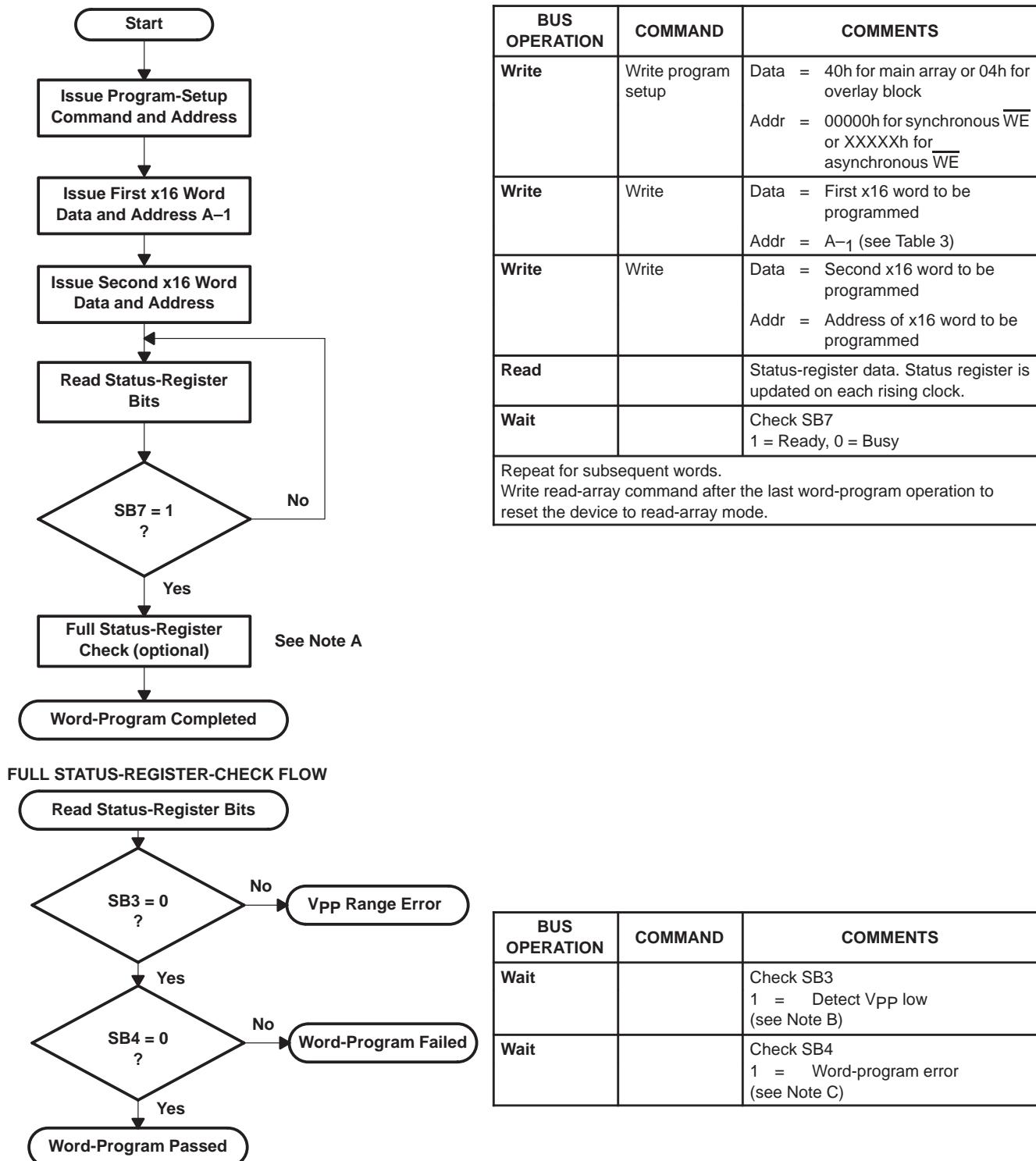

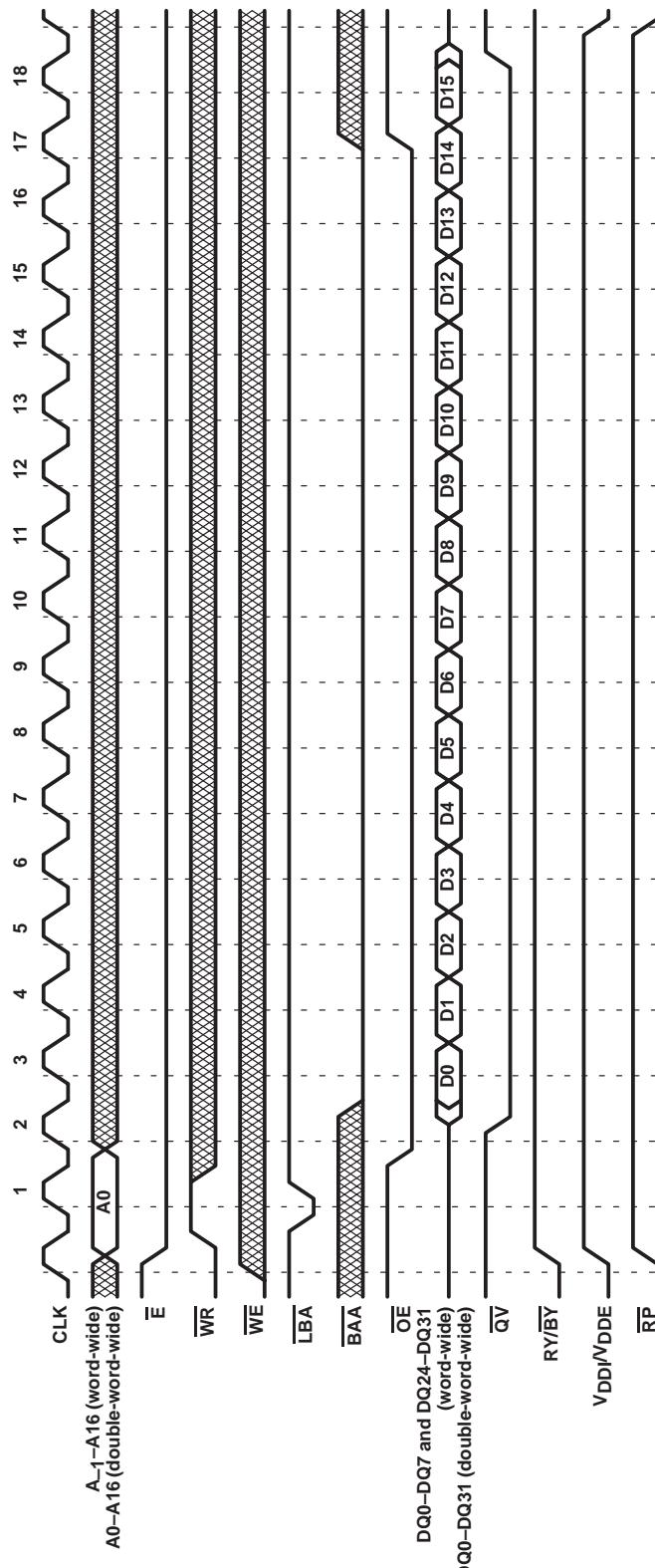

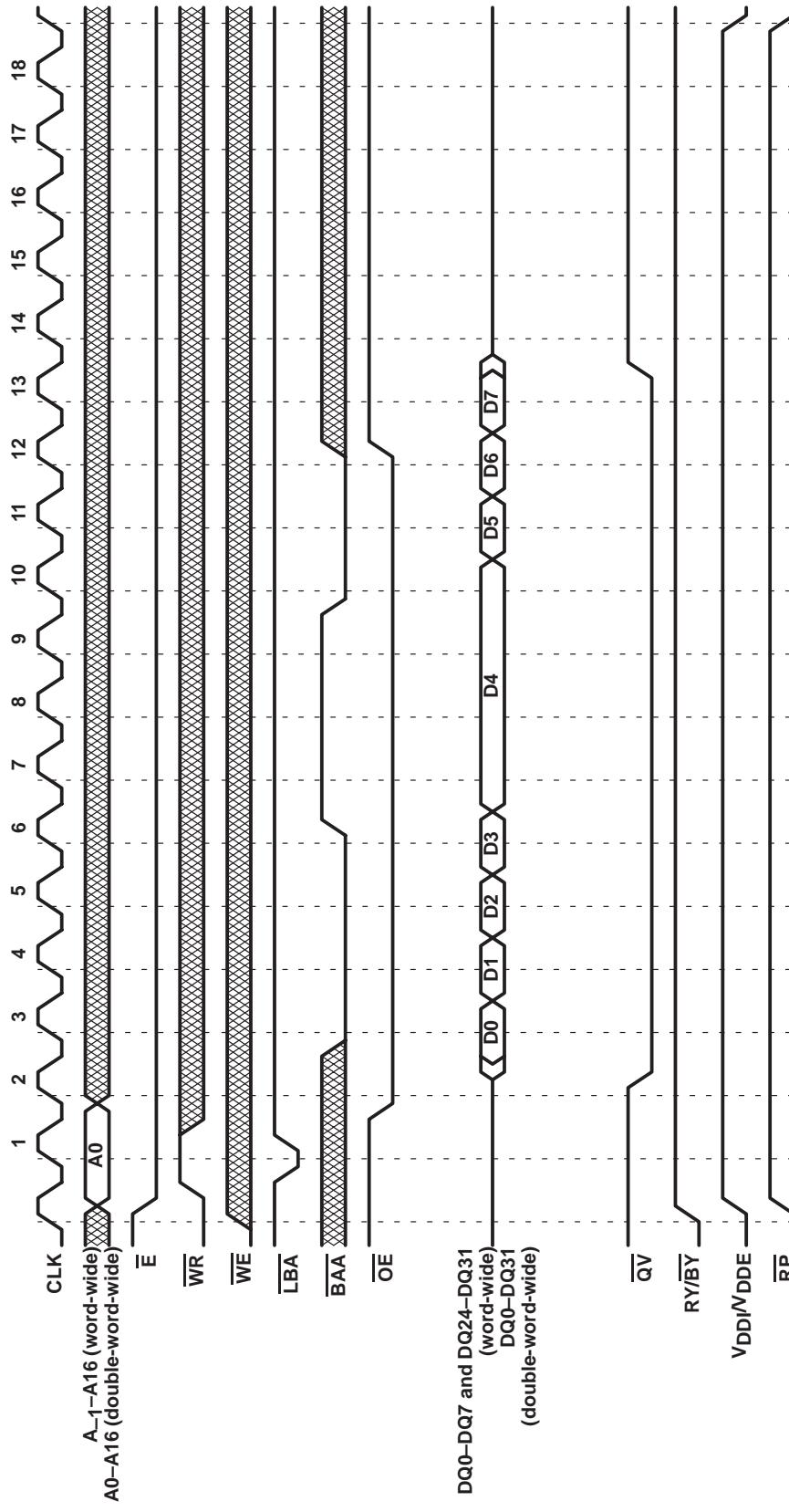

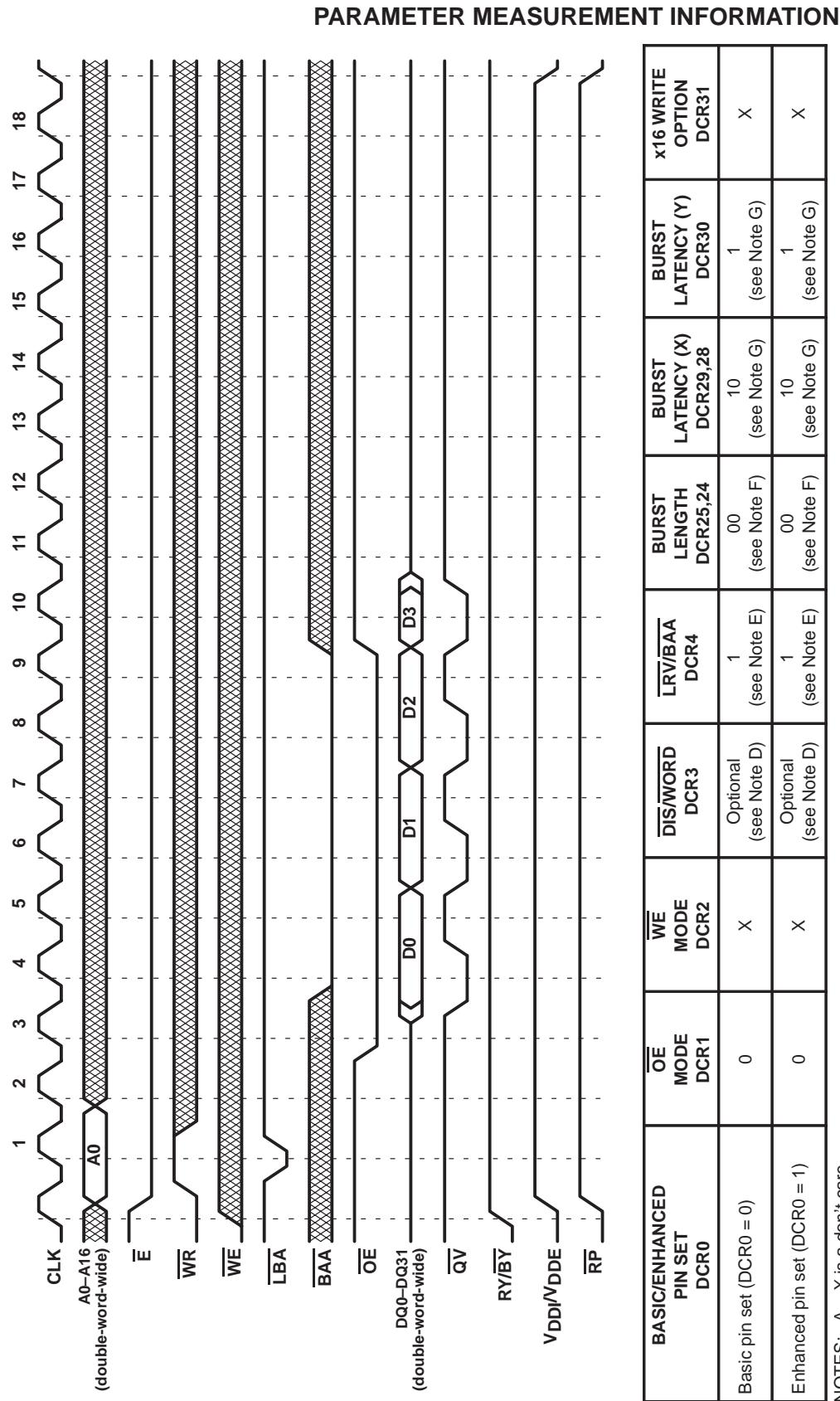

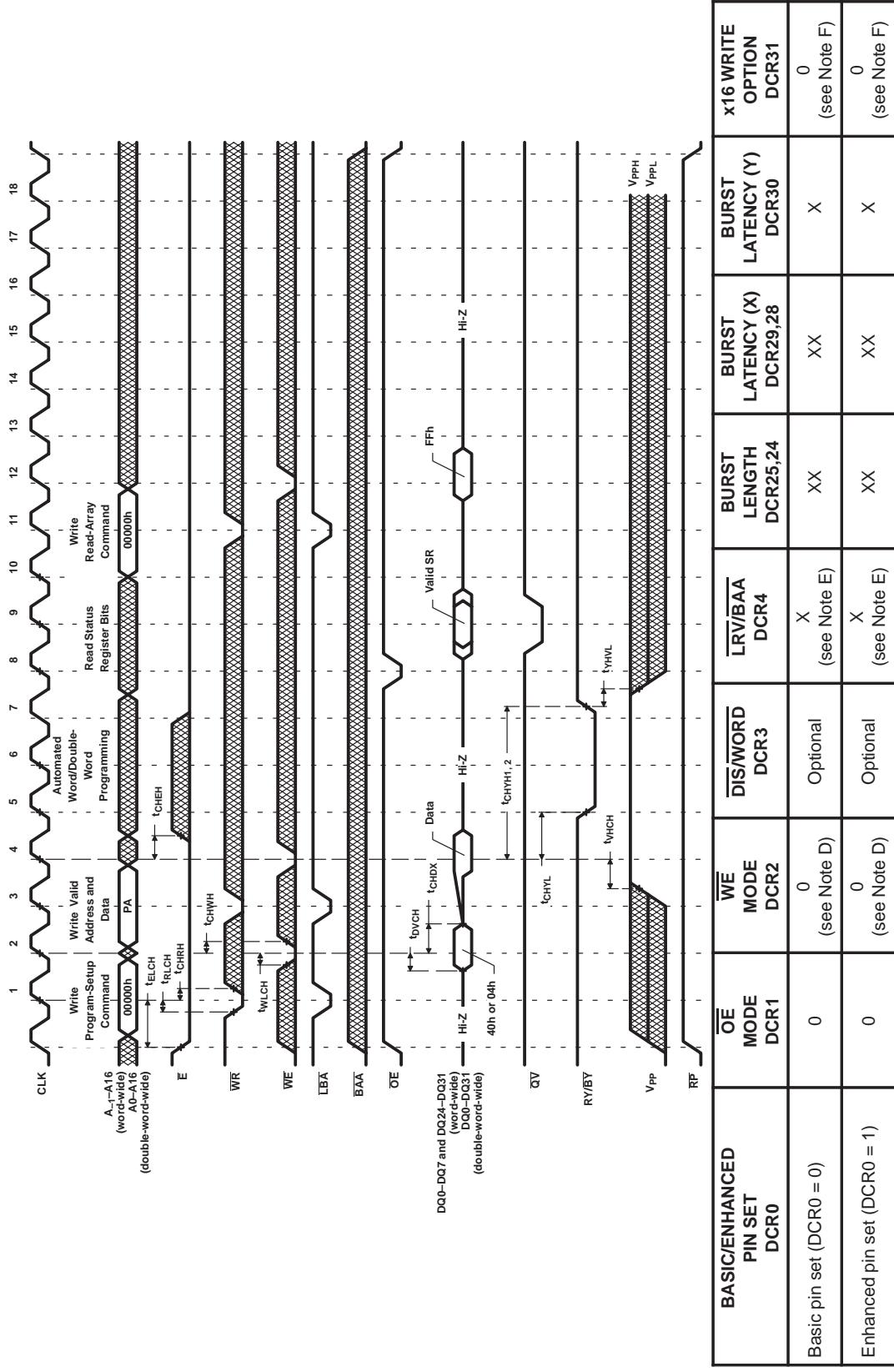

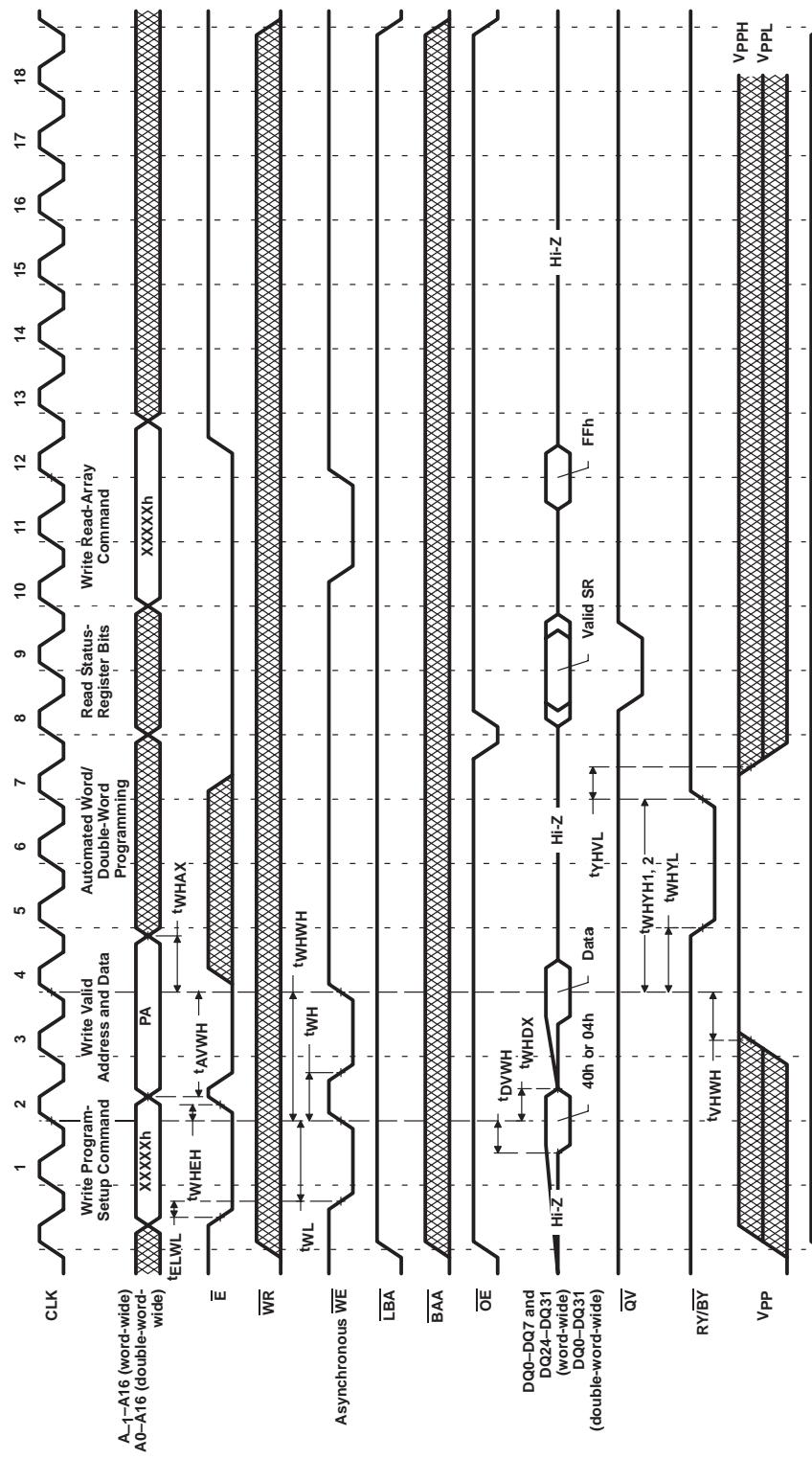

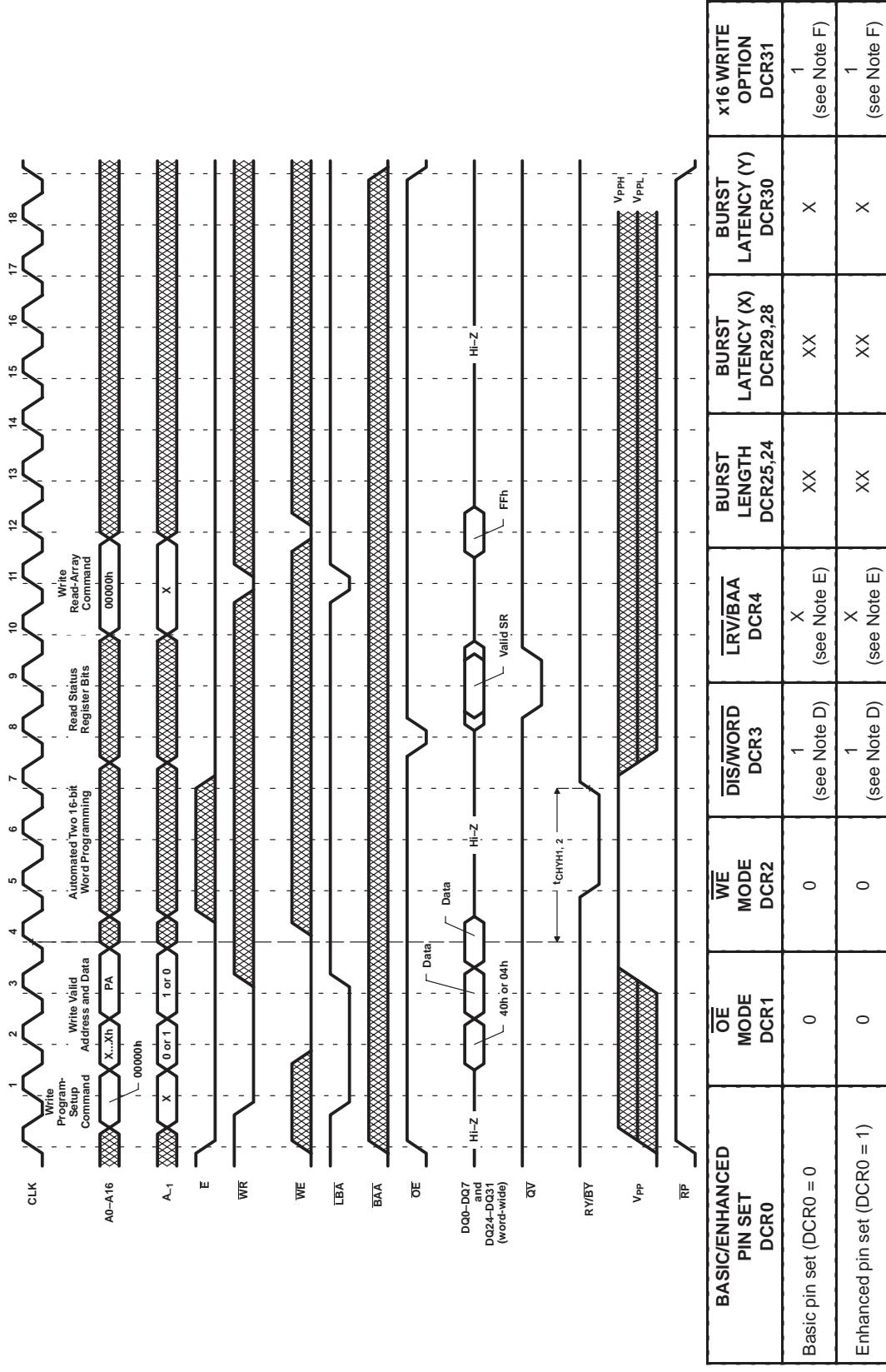

### word (X16) write option

DCR31 determines the number of write cycles for word-wide programming. For DCR31 = 0, the device performs two-cycle writes, or with DCR31 = 1, the device performs three-cycle writes (see Table 5). See Figure 22 and Figure 24 for synchronous two- and three-cycle writes, respectively. For asynchronous two-cycle writes, see Figure 23.

# TMS28F033

## 4194304-BIT

### SYNCHRONOUS FLASH MEMORY

SMJS833 – NOVEMBER 1997

---

#### operation modes for word-wide (x16) or double-word-wide (x32) mode selection

In x32 configuration, the memory array is divided into two parts: a lower half that outputs data through I/O pins DQ0–DQ7 and DQ24–DQ31, and an upper half that outputs data through DQ8–DQ23. Device operation in either x16 mode or x32 mode is user-selectable by configuring DCR3 = 1. This allows the input WORD logic state to determine either x16 or x32 mode. When WORD is at a logic-high level, the device is in the double-word-wide (x32) mode and data is written to or read from I/O pins DQ0–DQ31. When WORD is at a logic-low level, the device is in the word-wide (x16) mode and data is written to or read from I/O pins DQ0–DQ7 and DQ24–DQ31. In the word-wide mode, I/O pins DQ8–DQ23 are placed in the high-impedance state and A<sub>-1</sub> becomes the low-order address pin that selects either the upper or lower half of the array. Array data from the upper half (DQ0–DQ7, DQ24–DQ31) and the lower half (DQ8–DQ23) are multiplexed in order to appear on DQ0–DQ7 and DQ24–DQ31. The operation modes for word-wide and double-word-wide configurations are summarized in Table 13 and Table 14, respectively.

operation modes for word-wide (x16) or double-word-wide (x32) mode selection (continued)

Table 13. Operation Modes for Word-Wide Mode (x16) (See Note 2 and Note 14)

| MODE                                            | CLK | A<br>(Addr Bus) | E               | WR              | WE              | LBA             | BAA             | OE              | DQ<br>(Data Bus)<br>(see Note 14) | QV              | RY/BY           | V <sub>PP</sub>  | RP              |

|-------------------------------------------------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------------------|-----------------|-----------------|------------------|-----------------|

| READ OPERATION MODES                            |     |                 |                 |                 |                 |                 |                 |                 |                                   |                 |                 |                  |                 |

| Latch non-pipelined read address                | L-H | Address         | V <sub>IL</sub> | V <sub>IH</sub> | X               | V <sub>IL</sub> | X               | V <sub>IH</sub> | Hi-Z                              | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| Latch pipelined read address                    | L-H | Address         | V <sub>IL</sub> | V <sub>IH</sub> | X               | V <sub>IL</sub> | X               | V <sub>IH</sub> | Data out                          | V <sub>OL</sub> | Hi-Z            | X                | V <sub>IH</sub> |

| Latch pipelined read address with early overlap | L-H | Address         | V <sub>IL</sub> | V <sub>IH</sub> | X               | V <sub>IL</sub> | X               | V <sub>IL</sub> | Hi-Z                              | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| Wait (prior to first data read)                 | L-H | X               | V <sub>IL</sub> | X               | X               | V <sub>IH</sub> | X               | V <sub>IH</sub> | Hi-Z                              | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| Latch read data                                 | L-H | X               | V <sub>IL</sub> | X               | X               | V <sub>IH</sub> | X               | V <sub>IL</sub> | Hi-Z                              | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| Drive read data                                 | L-H | X               | V <sub>IL</sub> | X               | X               | V <sub>IH</sub> | X               | X               | Data out                          | V <sub>OL</sub> | Hi-Z            | X                | V <sub>IH</sub> |

| Burst read                                      | L-H | X               | V <sub>IL</sub> | X               | X               | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | Data out                          | V <sub>OL</sub> | Hi-Z            | X                | V <sub>IH</sub> |

| Burst terminate                                 | L-H | X               | V <sub>IL</sub> | X               | X               | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Data out                          | V <sub>OL</sub> | Hi-Z            | X                | V <sub>IH</sub> |

| Burst suspend (see Note 15)                     | L-H | X               | V <sub>IL</sub> | X               | X               | V <sub>IH</sub> | V <sub>IH</sub> | X               | Data out                          | V <sub>OL</sub> | Hi-Z            | X                | V <sub>IH</sub> |

| Update status during algorithm                  | L-H | X               | V <sub>IL</sub> | X               | X               | X               | X               | V <sub>IL</sub> | X                                 | X               | X               | X                | V <sub>IH</sub> |

| Read status during algorithm                    | L-H | X               | V <sub>IL</sub> | X               | X               | X               | X               | X               | Status out                        | V <sub>OL</sub> | X               | X                | V <sub>IH</sub> |

| Read overlay                                    | L-H | X               | V <sub>IL</sub> | X               | X               | X               | X               | V <sub>IL</sub> | Overlay data out                  | V <sub>OL</sub> | Hi-Z            | V <sub>PPH</sub> | V <sub>IH</sub> |

| SYNCHRONOUS WRITE OPERATION MODES               |     |                 |                 |                 |                 |                 |                 |                 |                                   |                 |                 |                  |                 |

| Latch write address                             | L-H | Address         | V <sub>IL</sub> | V <sub>IL</sub> | X               | V <sub>IL</sub> | X               | V <sub>IH</sub> | X                                 | X               | Hi-Z            | X                | V <sub>IH</sub> |

| Latch write address/data                        | L-H | Address         | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | X               | V <sub>IH</sub> | Data in                           | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| Latch write data                                | L-H | X               | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | X               | V <sub>IH</sub> | Data in                           | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| ASYNCHRONOUS WRITE OPERATION MODES              |     |                 |                 |                 |                 |                 |                 |                 |                                   |                 |                 |                  |                 |

| Latch write address/data                        | X   | Address         | V <sub>IL</sub> | X               | L-H             | X               | X               | V <sub>IH</sub> | Data in                           | Hi-Z            | Hi-Z            | X                | V <sub>IH</sub> |

| OTHER OPERATION MODES                           |     |                 |                 |                 |                 |                 |                 |                 |                                   |                 |                 |                  |                 |

| Standby                                         | X   | X               | V <sub>IH</sub> | X               | X               | X               | X               | X               | Hi-Z                              | Hi-Z            | X               | X                | V <sub>IH</sub> |

| Reset/deep power down                           | X   | X               | X               | X               | X               | X               | X               | X               | Hi-Z                              | Hi-Z            | V <sub>OH</sub> | X                | V <sub>IL</sub> |

NOTES: 13. X is a don't care.

14. For x16 mode (WORD = V<sub>IL</sub> when DCR3 = 1), the data lines are DQ0–DQ7 and DQ24–DQ31.

15. This mode freezes the burst counter and holds the current data line values.

**TMS28F033**

**4194304-BIT**

**SYNCHRONOUS FLASH MEMORY**

SMJS833 – NOVEMBER 1997

operation modes for word-wide (x16) or double-word-wide (x32) mode selection (continued)

Table 14. Operation Modes for Double-Word-Wide Mode (x32) (See Note 13 and Note 16)

| MODE                                            | CLK | A<br>(Addr Bus) | $\bar{E}$ | $\bar{WR}$ | $\bar{WE}$ | LBA      | $\bar{BAA}$ | $\bar{OE}$ | DQ<br>(Data Bus)<br>(see Note 16) | $\bar{QV}$ | $\bar{RY}/\bar{BY}$ | $V_{PP}$  | $\bar{RP}$ |

|-------------------------------------------------|-----|-----------------|-----------|------------|------------|----------|-------------|------------|-----------------------------------|------------|---------------------|-----------|------------|

| READ OPERATION MODES                            |     |                 |           |            |            |          |             |            |                                   |            |                     |           |            |

| Latch non-pipelined read address                | L-H | Address         | $V_{IL}$  | $V_{IH}$   | X          | $V_{IL}$ | X           | $V_{IH}$   | Hi-Z                              | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| Latch pipelined read address                    | L-H | Address         | $V_{IL}$  | $V_{IH}$   | X          | $V_{IL}$ | X           | $V_{IH}$   | Data out                          | VOL        | Hi-Z                | X         | $V_{IH}$   |

| Latch pipelined read address with early overlap | L-H | Address         | $V_{IL}$  | $V_{IH}$   | X          | $V_{IL}$ | X           | $V_{IL}$   | Hi-Z                              | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| Wait (prior to first data read)                 | L-H | X               | $V_{IL}$  | X          | X          | $V_{IH}$ | X           | $V_{IH}$   | Hi-Z                              | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| Latch read data                                 | L-H | X               | $V_{IL}$  | X          | X          | $V_{IH}$ | X           | $V_{IL}$   | Hi-Z                              | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| Drive read data                                 | L-H | X               | $V_{IL}$  | X          | X          | $V_{IH}$ | X           | X          | Data out                          | VOL        | Hi-Z                | X         | $V_{IH}$   |

| Burst read                                      | L-H | X               | $V_{IL}$  | X          | X          | $V_{IH}$ | $V_{IL}$    | $V_{IL}$   | Data out                          | VOL        | Hi-Z                | X         | $V_{IH}$   |

| Burst terminate                                 | L-H | X               | $V_{IL}$  | X          | X          | $V_{IH}$ | $V_{IH}$    | $V_{IH}$   | Data out                          | VOL        | Hi-Z                | X         | $V_{IH}$   |

| Burst suspend (see Note 15)                     | L-H | X               | $V_{IL}$  | X          | X          | $V_{IH}$ | $V_{IH}$    | X          | Data out                          | VOL        | Hi-Z                | X         | $V_{IH}$   |

| Update status during algorithm                  | L-H | X               | $V_{IL}$  | X          | X          | X        | X           | $V_{IL}$   | X                                 | X          | X                   | X         | $V_{IH}$   |

| Read status during algorithm                    | L-H | X               | $V_{IL}$  | X          | X          | X        | X           | X          | Status out                        | VOL        | X                   | X         | $V_{IH}$   |

| Read overlay                                    | L-H | X               | $V_{IL}$  | X          | X          | X        | X           | $V_{IL}$   | Overlay data out                  | VOL        | Hi-Z                | $V_{PPH}$ | $V_{IH}$   |

| SYNCHRONOUS WRITE OPERATION MODES               |     |                 |           |            |            |          |             |            |                                   |            |                     |           |            |

| Latch write address                             | L-H | Address         | $V_{IL}$  | $V_{IL}$   | X          | $V_{IL}$ | X           | $V_{IH}$   | X                                 | X          | Hi-Z                | X         | $V_{IH}$   |

| Latch write address/data                        | L-H | Address         | $V_{IL}$  | $V_{IL}$   | $V_{IL}$   | $V_{IL}$ | X           | $V_{IH}$   | Data in                           | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| Latch write data                                | L-H | X               | $V_{IL}$  | $V_{IH}$   | $V_{IL}$   | $V_{IH}$ | X           | $V_{IH}$   | Data in                           | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| ASYNCHRONOUS WRITE OPERATION MODES              |     |                 |           |            |            |          |             |            |                                   |            |                     |           |            |

| Latch write address/data                        | X   | Address         | $V_{IL}$  | X          | L-H        | X        | X           | $V_{IH}$   | Data in                           | Hi-Z       | Hi-Z                | X         | $V_{IH}$   |

| OTHER OPERATION MODES                           |     |                 |           |            |            |          |             |            |                                   |            |                     |           |            |

| Standby                                         | X   | X               | $V_{IH}$  | X          | X          | X        | X           | X          | Hi-Z                              | Hi-Z       | X                   | X         | $V_{IH}$   |

| Reset/deep power down                           | X   | X               | X         | X          | X          | X        | X           | X          | Hi-Z                              | Hi-Z       | VOH                 | X         | $V_{IL}$   |

NOTES: 13. X is a don't care.

15. This mode freezes the burst counter and holds the current data line values.

16. For x32 mode (WORD= $V_{IH}$  when DCR3=1, or DCR3=0) the data lines are DQ0–DQ31.

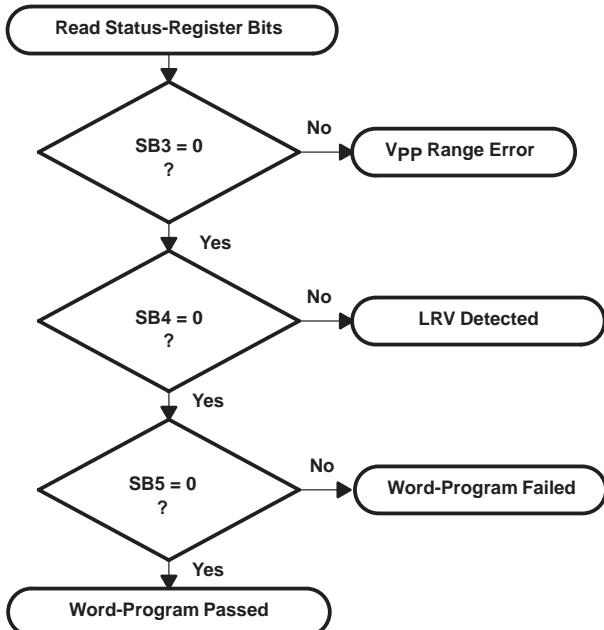

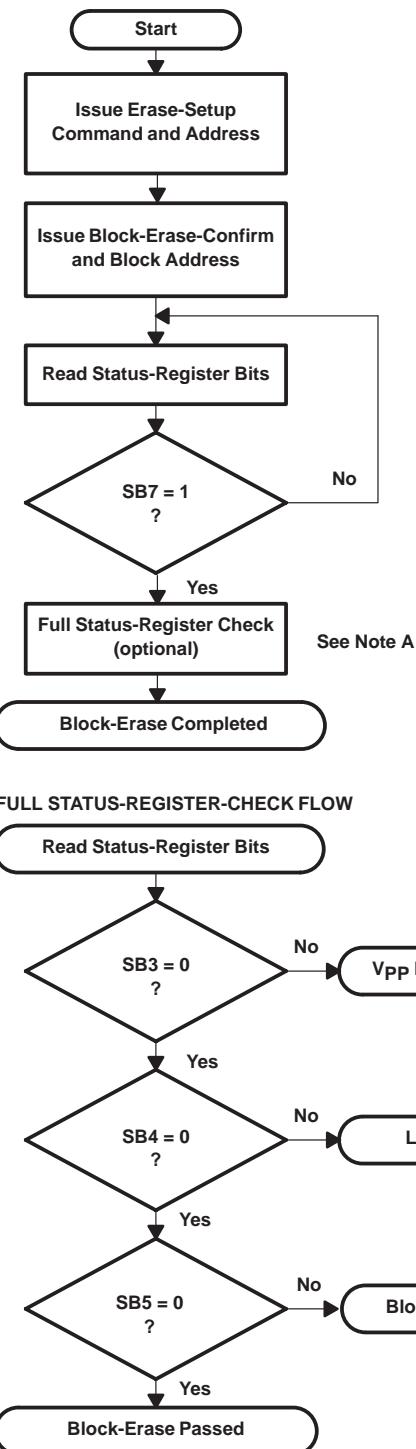

### clear status register

For  $DCR4 = 0$  (LRV usage), the WSM can set the  $V_{PP}$  status bit (SB3), the low-regulator-voltage status bit (SB4), and the operation status bit (SB5). For  $DCR4 = 1$ , the WSM can set the  $V_{PP}$  status bit (SB3), the program status bit (SB4), and the erase status bit (SB5) of the status register. The clear-status-register command (50h) allows the external microprocessor to clear SB3, SB4, and SB5. When the status bits are cleared, the device returns to the read-array mode.

### load device configuration register

The load DCR command is a two-bus-cycle command that loads the device configuration register. When the DCR load command (96h) is written to the CSM, the CSM will set up the device configuration register to be loaded on the next write cycle. On the second cycle, the configuration data DDDDh loads the two bytes of the device configuration register DCR0–DCR7 and DCR24–DCR31 (see Table 5 and Table 6). DCR8–DCR23 and DCR26–DCR27 are reserved and should be loaded with 0s.

### read operations

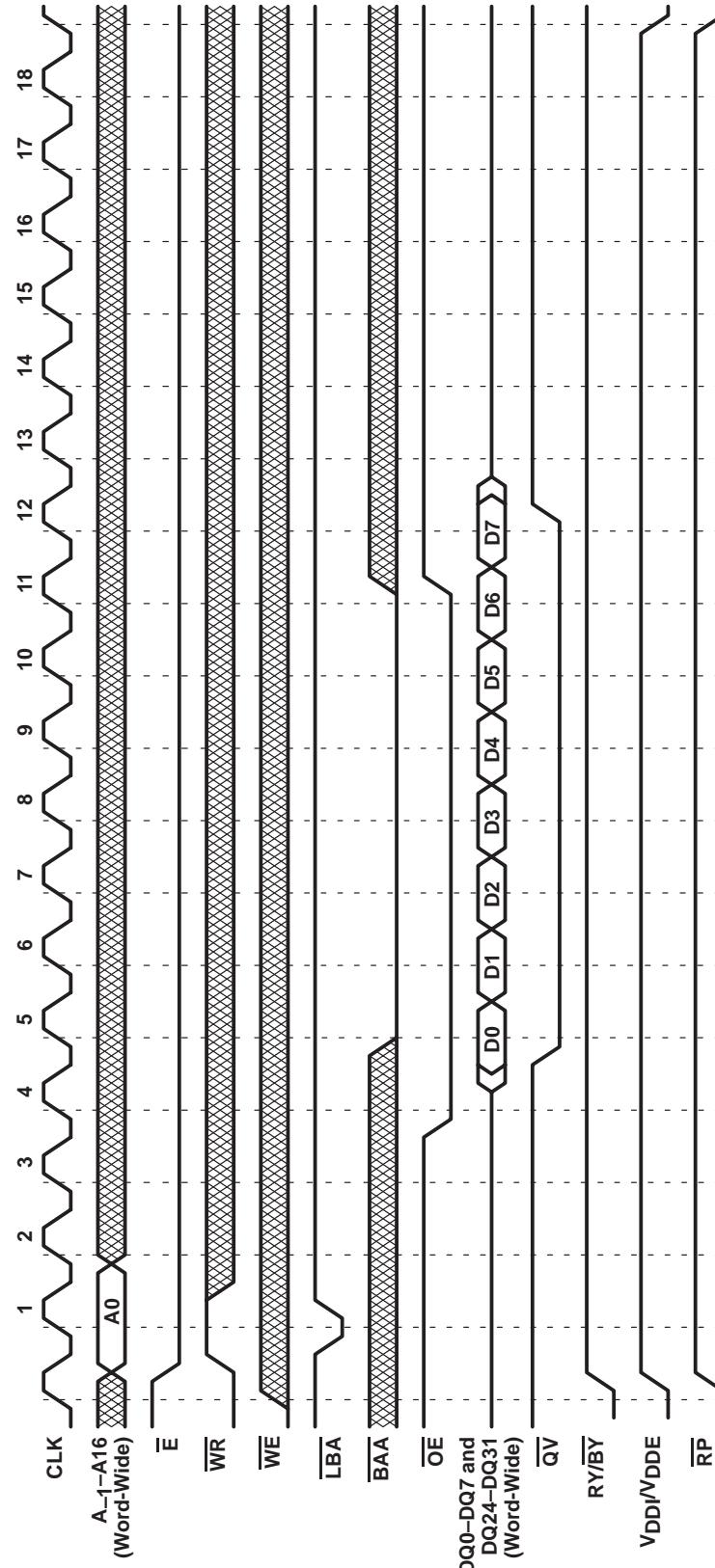

There are three read operations available: read array, read algorithm-selection code, and read status register. See Table 13 and Table 14 for the required control signals needed with synchronous reads.

- Read array

The read-array command consists of two bus cycles, and is listed in Table 5. For synchronous reads on the first bus cycle, the CSM command code FFh on DQ0–DQ7 and the address 00000h are entered.

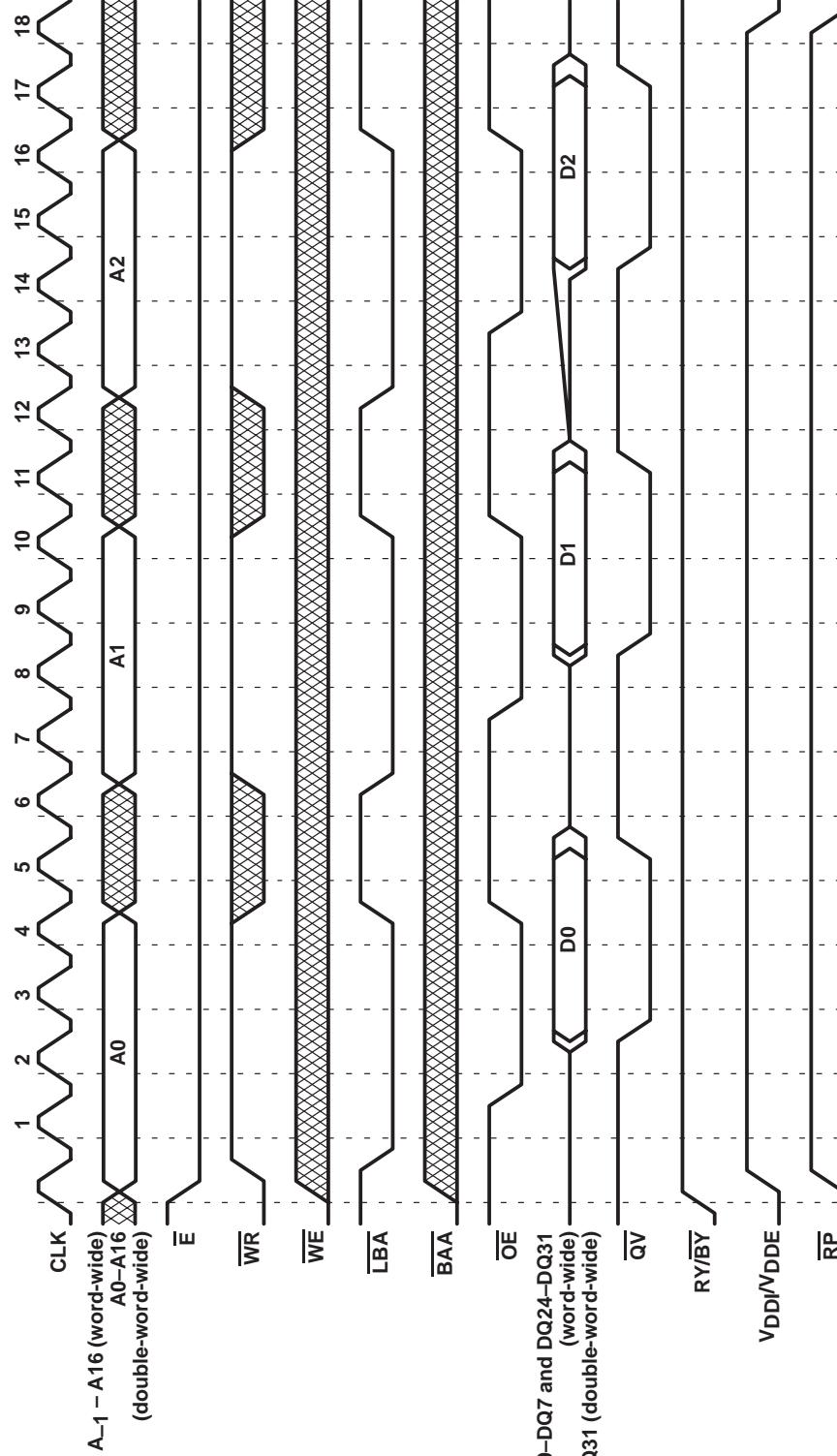

The second bus cycle begins with the address phase where, for synchronous operation,  $\overline{LBA}$  goes low on a rising clock edge. On the same clock (CLK 1 of Figure 14 for burst reads, or CLK 1 of Figure 27 for single reads), the address is latched and  $\overline{WR}$  is sampled. For a read,  $\overline{WR}$  is set high, and the device is ready for the read-data phase. The data phase follows the address phase by one or more clock cycles, where  $\overline{OE}$  goes low on a rising clock edge and the data is driven onto the bus DQ0–DQ31 for x32, and DQ0–DQ7 with DQ24–DQ31 for x16. For single reads, the data is valid for CLK 3 (see Figure 27). For burst reads, on CLK 3 of Figure 14,  $\overline{BAA}$  is brought low to burst the second data segment.  $\overline{OE}$  is kept low for four clock cycles (CLKs 2–5) and  $\overline{BAA}$  is kept low for three CLKs (CLKs 3–5), which bursts four words for MOD4. Burst reads for burst lengths MOD8, MOD16, or MOD32 are accomplished by holding  $\overline{OE}$  and  $\overline{BAA}$  low for each data segment in the same way (see Figure 14 through Figure 21). The optional output valid ( $\overline{QV}$ ) goes low when valid data is output from the device (see the Terminal Functions table, Figure 14 through Figure 21, and Figure 27).

- Read algorithm-selection code

As listed in Table 5, CSM command code 90h is written on DQ0–DQ7. Two bus cycles are required for this operation: the first to enter the command code and a second to read the manufacturer/device code or DCR value by loading the required A1A0 address bits (see Table 5 and Table 6). By loading a new address, the manufacturer-equivalent code is obtained on DQ0–DQ7 with both A1 and A0 at a logic-level  $V_{IL}$ . Similarly, the device-equivalent code is obtained when A1 is set to  $V_{IL}$  and A0 is set to  $V_{IH}$ . The device configuration register value is obtained when A1 is set to  $V_{IH}$  and A0 is set to  $V_{IL}$ .

- Read status register

The status register is read by entering the command code 70h on DQ0–DQ7. Two bus cycles are required for this operation: one to enter the command code and a second to read the status register (see Table 5). The status register contents are updated on every clock cycle.

The device interface is synchronous but supports asynchronous read timings, which hold the address valid and  $\overline{LBA}$  low throughout the address and data phases as required by some microprocessors after power-up (see Figure 13).

# TMS28F033

## 4194304-BIT

### SYNCHRONOUS FLASH MEMORY

SMJS833 – NOVEMBER 1997

---

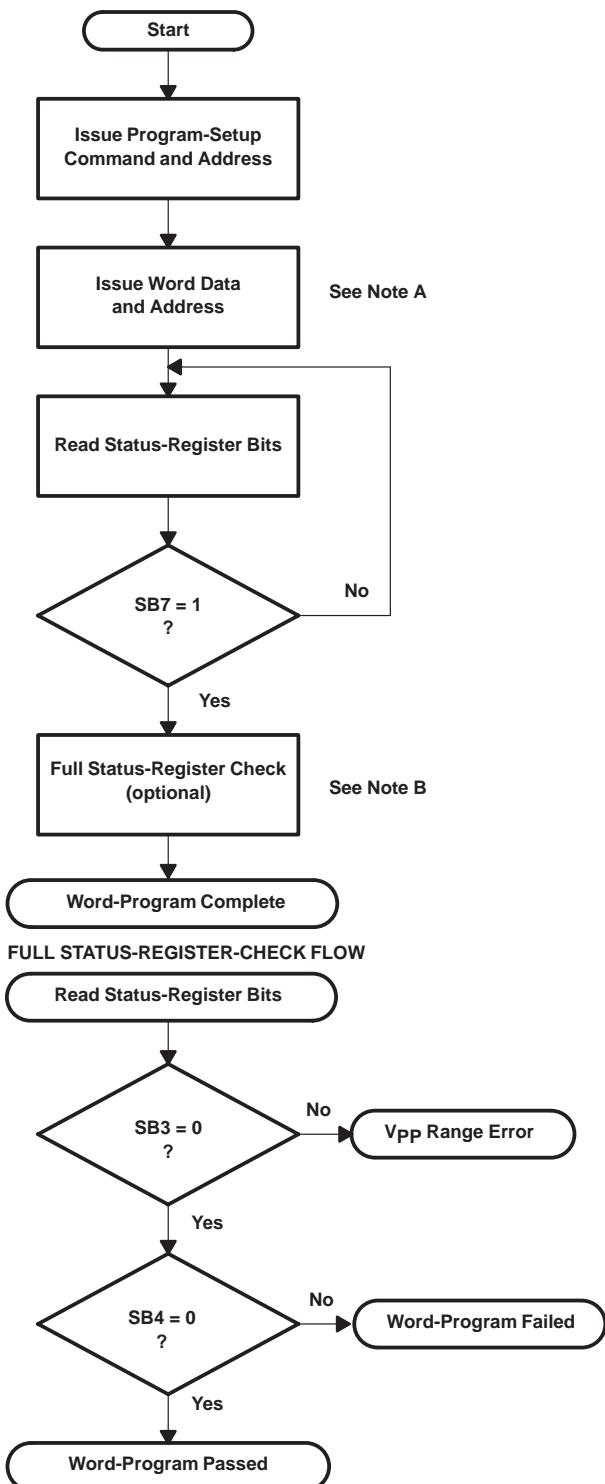

#### programming operations

There are two program operations available: program-setup/program to main array and program-setup/program to overlay block. Both are available with synchronous or asynchronous writes.

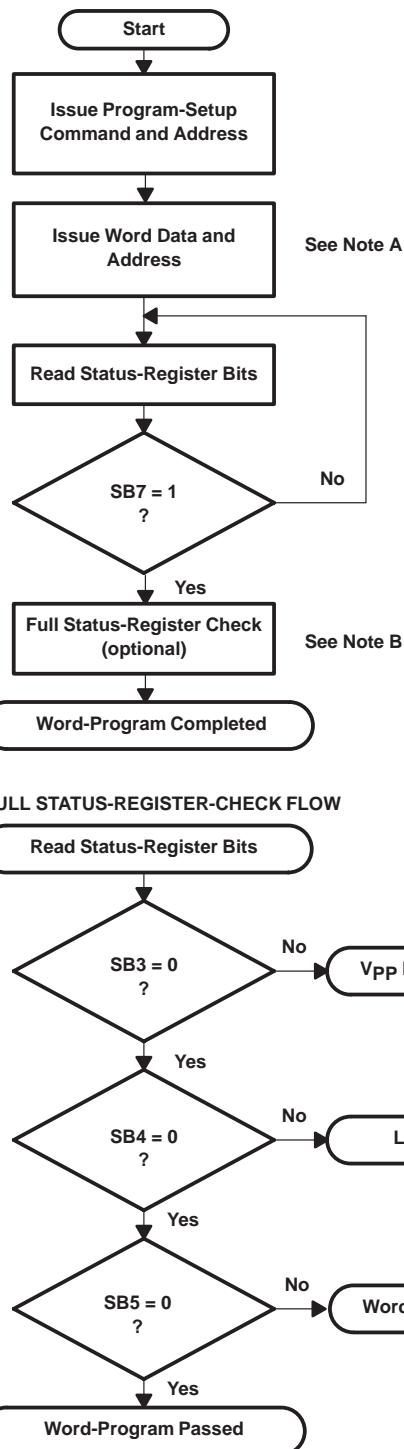

Both the x16 and x32 data bus configurations have a two-bus-cycle write capability, where in two bus cycles, either one 16-bit word or one 32-bit word is programmed, respectively. In addition, three-cycle writes are available with the 16-bit data bus by configuring DCR31 (see Table 8). On the first cycle, which is the command cycle, the CSM command code 40h or 04h is loaded to set up the device for programming either to the main array or to the overlay block array, respectively. On the second cycle, which is the write-data cycle, the data is loaded. After the desired command code and data are loaded, the WSM takes over and correctly sequences the device to complete the program operation. During this time, the CSM responds only to status reads until the program operation has been completed, after which all commands to the CSM become valid again. Once a program command has been issued, the WSM cannot normally be interrupted until the program algorithm is completed. Monitoring of the write operation is possible through the status register or the ready/busy (RY/BY) pin (see Figure 22 and Figure 24). See Figure 22 and Figure 24 for two- and three-cycle synchronous writes respectively. For asynchronous writes, the address and command/data are latched on the rising edge of  $\overline{WE}$  (see Figure 23 for asynchronous write).

Taking  $\overline{RP}$  to  $V_{IL}$  during programming aborts the program operation. During programming,  $V_{PP}$  must remain  $V_{PP} \geq V_{PPH}$  (see Figure 22 and Figure 23). Only 0s are written and compared during a program operation. If 1s are programmed, the memory cell contents do not change and no error occurs.