# 1024Kx8 Nonvolatile SRAM

专业PCB打样工厂

#### Features

Data retention in the absence of power

BENCHMARG

- Automatic write-protection during power-up/power-down cycles

- Conventional SRAM operation; unlimited write cycles

- ► 10-year minimum data retention in absence of power

- Battery internally isolated until power is applied

# **General Description**

The CMOS bq4016 is a nonvolatile 8,388,608-bit static RAM organized as 1,048,576 words by 8 bits. The integral control circuitry and lithium energy source provide reliable nonvolatility coupled with the unlimited write cycles of standard SRAM.

The control circuitry constantly monitors the single 5V supply for an out-of-tolerance condition. When Vcc falls out of tolerance, the SRAM is unconditionally write-protected to prevent an inadvertent write operation. DZSG.COM

At this time the integral energy source is switched on to sustain the memory until after V<sub>CC</sub> returns valid.

,24小时加急出货

The bq4016 uses extremely low standby current CMOS SRAMs, coupled with a small lithium coin cell to provide nonvolatility without long write-cycle times and the writecycle limitations associated with EEPROM.

The bq4016 has the same interface as industry-standard SRAMs and requires no external circuitry.

#### **Pin Connections**

|                      | 38 | Vcc   |

|----------------------|----|-------|

| NC 2                 | 35 | A19   |

| A <sub>18</sub> 3    | 34 |       |

| A <sub>16</sub> 4    | 33 | A15   |

| A <sub>14</sub> 0 5  | 32 | A17   |

| A <sub>12</sub> 0 6  | 31 | WE    |

|                      | 30 | A13   |

| A 8 0 8              | 29 | A C   |

| A 5 0 9              | 28 | A     |

| A 10                 | 27 | An    |

| A3 11                | 26 | OE    |

| A2 12                | 25 | A10   |

| A 1 13               | 24 | CE    |

| A <sub>0</sub> 14    | 23 | DQ7   |

| DQ 0 15              | 22 |       |

| DQ 1 0 16            | 21 | DQ:   |

| DQ 2 0 17            | 20 | DO DO |

| V <sub>SS</sub> 🗆 18 | 19 | DQ:   |

#### Pin Names A0-A19 Address inputs DO<sub>0</sub>-DO<sub>7</sub> Data input/output

CE

OE

WE

Vcc

NC

- Chip enable input

- Output enable input

Write enable input

- +5 volt supply input

- Vss Ground

- No connect

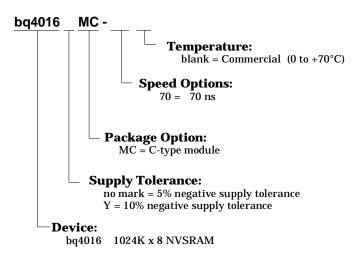

#### Selection Guide

| Part<br>Number | Maximum<br>Access<br>Time (ns) | Negative<br>Supply<br>Tolerance | Part<br>Number | Maximum<br>Access<br>Time (ns) | Negative<br>Supply<br>Tolerance |

|----------------|--------------------------------|---------------------------------|----------------|--------------------------------|---------------------------------|

| bq4016MC -70   | 70                             | -5%                             | bq4016YMC -70  | 70                             | -10%                            |

Sept. 1996 B

# bq4016/bq4016Y

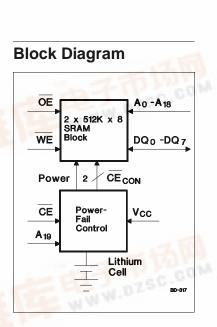

# **Functional Description**

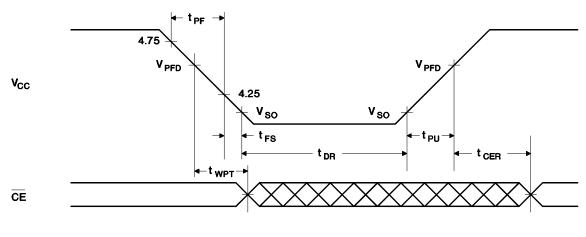

When power is valid, the bq4016 operates as a standard CMOS SRAM. During power-down and power-up cycles, the bq4016 acts as a nonvolatile memory, automatically protecting and preserving the memory contents.

Power-down/power-up control circuitry constantly monitors the V<sub>CC</sub> supply for a power-fail-detect threshold V<sub>PFD</sub>. The bq4016 monitors for V<sub>PFD</sub> = 4.62V typical for use in systems with 5% supply tolerance. The bq4016Y monitors for V<sub>PFD</sub> = 4.37V typical for use in systems with 10% supply tolerance.

When  $V_{CC}$  falls below the  $V_{PFD}$  threshold, the SRAM automatically write-protects the data. All outputs become high impedance, and all inputs are treated as "don't care." If a valid access is in process at the time of power-fail detection, the memory cycle continues to completion. If the memory cycle fails to terminate within time t<sub>WPT</sub>, write-protection takes place.

As  $V_{CC}$  falls past  $V_{PFD}$  and approaches 3V, the control circuitry switches to the internal lithium backup supply, which provides data retention until valid  $V_{CC}$  is applied.

When  $V_{CC}$  returns to a level above the internal backup cell voltage, the supply is switched back to  $V_{CC}$ . After  $V_{CC}$  ramps above the  $V_{PFD}$  threshold, write-protection continues for a time  $t_{CER}$  (120ms maximum) to allow for processor stabilization. Normal memory operation may resume after this time.

The internal coin cells used by the bq4016 have an extremely long shelf life. The bq4016 provides data retention for more than 10 years in the absence of system power.

As shipped from Benchmarq, the integral lithium cells are electrically isolated from the memory. (Self-discharge in this condition is approximately 0.5% per year.) Following the first application of  $V_{CC}$ , this isolation is broken, and the lithium backup provides data retention on subsequent power-downs.

| Mode           | CE | WE | OE | I/O Operation    | Power   |

|----------------|----|----|----|------------------|---------|

| Not selected   | Н  | Х  | Х  | High Z           | Standby |

| Output disable | L  | Н  | Н  | High Z           | Active  |

| Read           | L  | Н  | L  | D <sub>OUT</sub> | Active  |

| Write          | L  | L  | Х  | D <sub>IN</sub>  | Active  |

#### **Absolute Maximum Ratings**

| Symbol            | Parameter                                                             | Value       | Unit | Conditions              |

|-------------------|-----------------------------------------------------------------------|-------------|------|-------------------------|

| Vcc               | DC voltage applied on $V_{CC}$ relative to $V_{SS}$                   | -0.3 to 7.0 | V    |                         |

| VT                | DC voltage applied on any pin excluding $V_{CC}$ relative to $V_{SS}$ | -0.3 to 7.0 | v    | $V_T \leq V_{CC} + 0.3$ |

| TOPR              | Operating temperature                                                 | 0 to +70    | °C   |                         |

| TSTG              | Storage temperature                                                   | -40 to +70  | °C   |                         |

| T <sub>BIAS</sub> | Temperature under bias                                                | -10 to +70  | °C   |                         |

| TSOLDER           | Soldering temperature                                                 | +260        | °C   | For 10 seconds          |

**Note:** Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

| Symbol          | Parameter          | Minimum | Typical | Maximum               | Unit | Notes   |

|-----------------|--------------------|---------|---------|-----------------------|------|---------|

|                 |                    | 4.5     | 5.0     | 5.5                   | V    | bq4016Y |

| Vcc             | Supply voltage     | 4.75    | 5.0     | 5.5                   | v    | bq4016  |

| V <sub>SS</sub> | Supply voltage     | 0       | 0       | 0                     | v    |         |

| VIL             | Input low voltage  | -0.3    | -       | 0.8                   | v    |         |

| V <sub>IH</sub> | Input high voltage | 2.2     | -       | V <sub>CC</sub> + 0.3 | v    |         |

# Recommended DC Operating Conditions (TA = 0 to 70°C)

Note: Typical values indicate operation at  $T_A = 25^{\circ}C$ .

# DC Electrical Characteristics (TA = 0 to 70°C, VCCmin $\leq$ VCC $\leq$ VCCmax)

| Symbol           | Parameter                  | Minimum | Typical | Maximum | Unit | Conditions/Notes                                                                                                                                             |

|------------------|----------------------------|---------|---------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>LI</sub>  | Input leakage current      | -       | -       | ± 2     | μA   | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                |

| ILO              | Output leakage current     | -       | -       | ± 2     | μΑ   | $\overline{\underline{CE}} = V_{IH} \text{ or } \overline{OE} = V_{IH} \text{ or} \\ \overline{WE} = V_{IL}$                                                 |

| Voh              | Output high voltage        | 2.4     | -       | -       | V    | I <sub>OH</sub> = -1.0 mA                                                                                                                                    |

| Vol              | Output low voltage         | -       | -       | 0.4     | V    | $I_{OL} = 2.1 \text{ mA}$                                                                                                                                    |

| I <sub>SB1</sub> | Standby supply current     | -       | 5       | 12      | mA   | $\overline{CE} = V_{IH}$                                                                                                                                     |

| I <sub>SB2</sub> | Standby supply current     | -       | 2.5     | 5       | mA   | $\label{eq:Vindex} \begin{split} & \frac{0V \leq V_{IN} \leq 0.2V,}{CE \geq V_{CC} - 0.2V,} \\ & \text{or } V_{IN} \geq V_{CC} - 0.2 \end{split}$            |

| I <sub>CC</sub>  | Operating supply current   | -       | 75      | 115     | mA   | $\label{eq:min.cycle, duty = 100\%,} \frac{Min. cycle, duty = 100\%,}{CE = V_{IL}, I_{I/O} = 0mA,} \\ A19 < V_{IL} \mbox{ or } A19 > V_{IH}, \\ \end{array}$ |

| VPFD             | Power-fail-detect voltage  | 4.55    | 4.62    | 4.75    | V    | bq4016                                                                                                                                                       |

| v PFD            | rower-fail-detect voltage  | 4.30    | 4.37    | 4.50    | V    | bq4016Y                                                                                                                                                      |

| Vso              | Supply switch-over voltage | -       | 3       | -       | V    |                                                                                                                                                              |

Note: Typical values indicate operation at  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V$ .

| oupaona |                          |         |         |         |      |                     |  |

|---------|--------------------------|---------|---------|---------|------|---------------------|--|

| Symbol  | Parameter                | Minimum | Typical | Maximum | Unit | Conditions          |  |

| CI/O    | Input/output capacitance | -       | -       | 20      | pF   | Output voltage = 0V |  |

| CIN     | Input capacitance        | -       | -       | 20      | pF   | Input voltage = 0V  |  |

#### Capacitance ( $T_A = 25^{\circ}C$ , F = 1MHz, $V_{CC} = 5.0V$ )

**Note:** These parameters are sampled and not 100% tested.

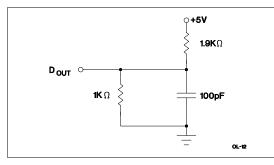

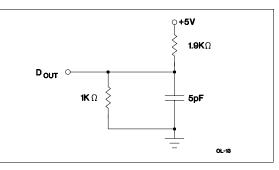

#### **AC Test Conditions**

| Parameter                                | Test Conditions                    |

|------------------------------------------|------------------------------------|

| Input pulse levels                       | 0V to 3.0V                         |

| Input rise and fall times                | 5 ns                               |

| Input and output timing reference levels | 1.5 V (unless otherwise specified) |

# Figure 2. Output Load B

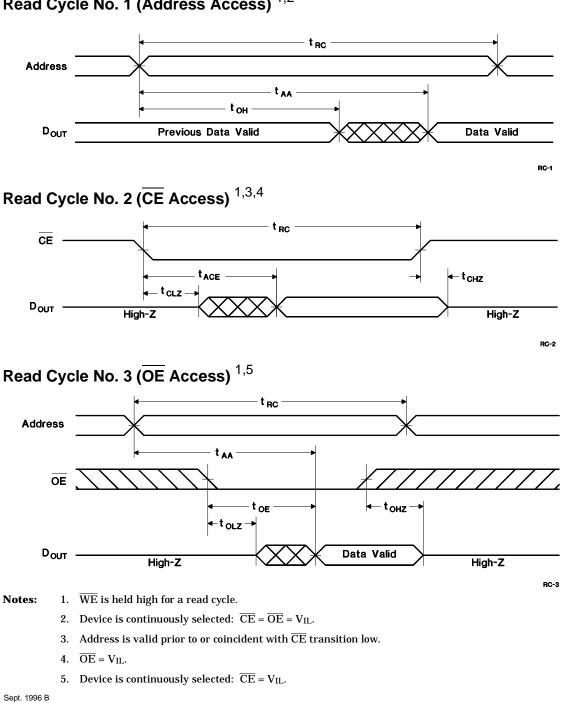

| Read Cycle | (TA = 0 to 70°C, VCCmin $\leq$ VCC $\leq$ VCCmax) |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

|                  |                                    | -    | -70  |      |               |

|------------------|------------------------------------|------|------|------|---------------|

| Symbol           | Parameter                          | Min. | Max. | Unit | Conditions    |

| t <sub>RC</sub>  | Read cycle time                    | 70   | -    | ns   |               |

| t <sub>AA</sub>  | Address access time                | -    | 70   | ns   | Output load A |

| t <sub>ACE</sub> | Chip enable access time            | -    | 70   | ns   | Output load A |

| toE              | Output enable to output valid      | -    | 35   | ns   | Output load A |

| tclz             | Chip enable to output in low Z     | 5    | -    | ns   | Output load B |

| tolz             | Output enable to output in low Z   | 5    | -    | ns   | Output load B |

| t <sub>CHZ</sub> | Chip disable to output in high Z   | 0    | 25   | ns   | Output load B |

| toHz             | Output disable to output in high Z | 0    | 25   | ns   | Output load B |

| toH              | Output hold from address change    | 10   | -    | ns   | Output load A |

Read Cycle No. 1 (Address Access) <sup>1,2</sup>

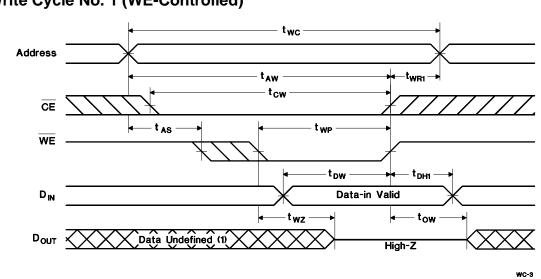

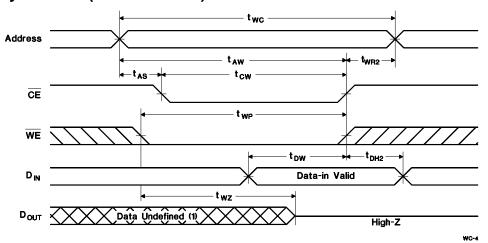

|                  |                                        | -    | 70   |       |                                                                                                       |  |

|------------------|----------------------------------------|------|------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                              | Min. | Max. | Units | Conditions/Notes                                                                                      |  |

| twc              | Write cycle time                       | 70   | -    | ns    |                                                                                                       |  |

| tcw              | Chip enable to end of write            | 65   | -    | ns    | (1)                                                                                                   |  |

| t <sub>AW</sub>  | Address valid to end of write          | 65   | -    | ns    | (1)                                                                                                   |  |

| t <sub>AS</sub>  | Address setup time                     | 0    | -    | ns    | Measured from address valid to beginning of write. (2)                                                |  |

| t <sub>WP</sub>  | Write pulse width                      | 55   | _    | ns    | Measured from beginning of write to end of write. (1)                                                 |  |

| t <sub>WR1</sub> | Write recovery time<br>(write cycle 1) | 5    | -    | ns    | Measured from $\overline{\text{WE}}$ going high to end of write cycle. (3)                            |  |

| t <sub>WR2</sub> | Write recovery time<br>(write cycle 2) | 15   | _    | ns    | Measured from $\overline{CE}$ going high to end of write cycle. (3)                                   |  |

| t <sub>DW</sub>  | Data valid to end of write             | 30   | _    | ns    | Measured to first low-to-high transition of either $\overline{\text{CE}}$ or $\overline{\text{WE}}$ . |  |

| t <sub>DH1</sub> | Data hold time<br>(write cycle 1)      | 0    | -    | ns    | Measured from $\overline{\text{WE}}$ going high to end of write cycle. (4)                            |  |

| tDH2             | Data hold time<br>(write cycle 2)      | 10   | -    | ns    | Measured from $\overline{CE}$ going high to end of write cycle. (4)                                   |  |

| twz              | Write enabled to output in high Z      | 0    | 25   | ns    | I/O pins are in output state. (5)                                                                     |  |

| tow              | Output active from end of write        | 5    | -    | ns    | I/O pins are in output state. (5)                                                                     |  |

#### Write Cycle (TA = 0 to 70°C, VCCmin $\leq$ VCC $\leq$ VCCmax)

**Notes:** 1. A write ends at the earlier transition of  $\overline{CE}$  going high and  $\overline{WE}$  going high.

2. A write occurs during the overlap of a low  $\overline{CE}$  and a low  $\overline{WE}$ . A write begins at the later transition of  $\overline{CE}$  going low and  $\overline{WE}$  going low.

- 3. Either  $t_{WR1}$  or  $t_{WR2}$  must be met.

- 4. Either t<sub>DH1</sub> or t<sub>DH2</sub> must be met.

- 5. If  $\overline{\text{CE}}$  goes low simultaneously with  $\overline{\text{WE}}$  going low or after  $\overline{\text{WE}}$  going low, the outputs remain in high-impedance state.

Write Cycle No. 1 ( $\overline{\text{WE}}$ -Controlled) <sup>1,2,3</sup>

Write Cycle No. 2 ( $\overline{CE}$ -Controlled) <sup>1,2,3,4,5</sup>

1.  $\overline{\text{CE}} \text{ or } \overline{\text{WE}} \text{ must be high during address transition.}$

- 2. Because I/O may be active ( $\overline{\text{OE}}$  low) during this period, data input signals of opposite polarity to the outputs must not be applied.

- 3. If  $\overline{\text{OE}}$  is high, the I/O pins remain in a state of high impedance.

- 4. Either  $t_{WR1}$  or  $t_{WR2}$  must be met.

- 5. Either tDH1 or tDH2 must be met.

#### Sept. 1996 B

| Symbol           | Parameter                                                        | Minimum | Typical | Maximum | Unit  | Conditions                                                                                                    |

|------------------|------------------------------------------------------------------|---------|---------|---------|-------|---------------------------------------------------------------------------------------------------------------|

| t <sub>PF</sub>  | V <sub>CC</sub> slew, 4.75 to 4.25 V                             | 300     | -       | -       | μs    |                                                                                                               |

| t <sub>FS</sub>  | V <sub>CC</sub> slew, 4.25 to V <sub>SO</sub>                    | 10      | -       | -       | μs    |                                                                                                               |

| t <sub>PU</sub>  | V <sub>CC</sub> slew, V <sub>SO</sub> to V <sub>PFD</sub> (max.) | 0       | -       | -       | μs    |                                                                                                               |

| tcer             | Chip enable recovery time                                        | 40      | 80      | 120     | ms    | Time during which<br>SRAM is write-protected<br>after V <sub>CC</sub> passes V <sub>FPD</sub> on<br>power-up. |

| t <sub>DR</sub>  | Data-retention time in absence of $V_{CC}$                       | 10      | -       | -       | years | $T_{\rm A} = 25^{\circ}{\rm C.}$ (2)                                                                          |

| t <sub>WPT</sub> | Write-protect time                                               | 40      | 100     | 150     | μs    | Delay after $V_{CC}$ slews<br>down past $V_{PFD}$ before<br>SRAM is write-protected.                          |

#### Power-Down/Power-Up Cycle (T<sub>A</sub> = 0 to 70°C)

**Notes:** 1. Typical values indicate operation at  $T_A = 25$ °C,  $V_{CC} = 5V$ .

2. Batteries are disconnected from circuit until after  $V_{CC}$  is applied for the first time.  $t_{DR}$  is the accumulated time in absence of power beginning when power is first applied to the device.

Caution: Negative undershoots below the absolute maximum rating of -0.3V in battery-backup mode may affect data integrity.

# Power-Down/Power-Up Timing

PD-B

# **Data Sheet Revision History**

.

| Change No. | Page No. | Description                                      |  |  |  |

|------------|----------|--------------------------------------------------|--|--|--|

| 1          | All      | Changed from "Preliminary" to "Final" data sheet |  |  |  |

**Notes:** Change 1 = Sept 1996 B changes from June 1995.

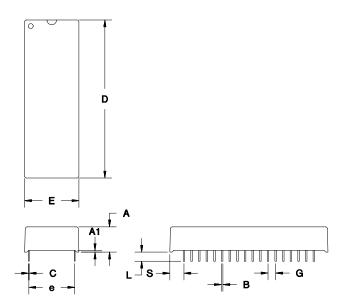

# MC: 36-Pin C-Type Module

#### 36-Pin MC (C-Type Module)

| Dimension | Minimum | Maximum |

|-----------|---------|---------|

| Α         | 0.365   | 0.375   |

| A1        | 0.015   | -       |

| В         | 0.017   | 0.023   |

| С         | 0.008   | 0.013   |

| D         | 2.070   | 2.100   |

| Е         | 0.710   | 0.740   |

| e         | 0.590   | 0.630   |

| G         | 0.090   | 0.110   |

| L         | 0.120   | 0.150   |

| S         | 0.175   | 0.210   |

All dimensions are in inches.

Sept. 1996 B

# **Ordering Information**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated