#### 查询AD9712B供应商

## ANALOG DEVICES

### 捷多邦,专业PCB打样工厂,24小时加急出货

## 12-Bit, 100 MSPS D/A Converters

## AD9712B/AD9713B

FEATURES 100 MSPS Update Rate ECL/TTL Compatibility SFDR @ 1 MHz: 70 dBc Low Glitch Impulse: 28 pV-s Fast Settling: 27 ns Low Power: 725 mW 1/2 LSB DNL (B Grade) 40 MHz Multiplying Bandwidth

#### APPLICATIONS ATE Signal Reconstruction Arbitrary Waveform Generators

Digital Synthesizers Signal Generators

#### **GENERAL DESCRIPTION**

The AD9712B and AD9713B D/A converters are replacements for the AD9712 and AD9713 units which offer improved ac and dc performance. Like their predecessors, they are 12-bit, high speed digital-to-analog converters fabricated in an advanced oxide isolated bipolar process. The AD9712B is an ECLcompatible device featuring update rates of 100 MSPS minimum; the TTL-compatible AD9713B will update at 80 MSPS minimum.

> Designed for direct digital synthesis, waveform reconstruction, and high resolution imaging applications, both devices feature low glitch impulse of 28 pV-s and fast settling times of 27 ns. Both units are characterized for dynamic performance and have excellent harmonic suppression.

> The AD9712B and AD9713B are available in 28-pin plastic DIPs and PLCCs, with an operating temperature range of  $-25^{\circ}$ C to  $+85^{\circ}$ C. Both are also available for extended temperature ranges of  $-55^{\circ}$ C to  $+125^{\circ}$ C in cerdips and 28-pin LCC packages.

REVEALED Internation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its ouse nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any nation or patent rights of Analog Devices

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

## AD9712B/AD9713B-SPECIFICATIONS

# $\label{eq:Electrical characteristics} \begin{array}{l} [-V_{S}=-5.2 \ V; \ +V_{S}=+5 \ V \ (\text{AD9713B only}); \ \text{Reference Voltage}=-1.2 \ V; \\ R_{SET}=7.5 \ k \Omega; \ V_{OUT}=0 \ V \ (\text{virtual ground}); \ \text{unless otherwise noted}] \end{array}$

|                            |       | Test  |       | 12B/AD<br>AN/AP |       |       | 2B/AD9<br>BN/BP | 9713B |       | 12B/A<br>SE/SG |      | AD9712<br>T | B/AD<br>E/TQ | 9713B |       |

|----------------------------|-------|-------|-------|-----------------|-------|-------|-----------------|-------|-------|----------------|------|-------------|--------------|-------|-------|

| Parameter (Conditions)     | Temp  | Level | Min   | Тур             | Max   | Min   | Тур             | Max   | Min   | Тур            | Max  | Min         | Тур          | Max   | Units |

| RESOLUTION                 |       |       |       | 12              |       |       | 12              |       |       | 12             |      |             | 12           |       | Bits  |

| DC ACCURACY                |       |       |       |                 |       |       |                 |       |       |                |      |             |              |       |       |

| Differential Nonlinearity  | +25°C | Ι     | -1.25 | 1.0             | +1.25 | -0.75 | 0.5             | +0.75 | -1.5  | 1.0            | +1.5 | -1.0        | 0.5          | +1.0  | LSB   |

|                            | Full  | VI    | -2.0  |                 | 2.0   | -1.5  |                 | 1.5   | -2.0  |                | 2.0  | -1.5        |              | 1.5   | LSB   |

| Integral Nonlinearity      | +25°C | Ι     | -1.5  | 1.0             | 1.5   | -1.0  | 0.75            | 1.0   | -1.75 | 1.5            | 1.75 | -1.25       | 1.0          | 1.25  | LSB   |

| ("Best Fit" Straight Line) | Full  | VI    | -2.0  |                 | 2.0   | -1.75 |                 | 1.75  | -2.0  |                | 2.0  | -1.75       |              | 1.75  | LSB   |

|                                                                        | <b>T</b> | Test  | M     | AD9712B<br>All Grades | Maria |       | AD9713B<br>All Grades | M         | ¥1*4   |

|------------------------------------------------------------------------|----------|-------|-------|-----------------------|-------|-------|-----------------------|-----------|--------|

| Parameter (Conditions)                                                 | Temp     | Level | Min   | Тур                   | Max   | Min   | Тур                   | Max       | Units  |

| INITIAL OFFSET ERROR                                                   |          |       |       |                       |       |       |                       |           |        |

| Zero-Scale Offset Error                                                | +25°C    | I     |       | 0.5                   | 2.5   |       | 0.5                   | 2.5       | μA     |

|                                                                        | Full     | VI    |       |                       | 5.0   |       |                       | 5.0       | μA     |

| Full-Scale Gain Error <sup>1</sup>                                     | +25°C    | I     |       | 1.0                   | 5     |       | 1.0                   | 5         | %      |

|                                                                        | Full     | VI    |       |                       | 8     |       |                       | 8         | %      |

| Offset Drift Coefficient                                               | +25°C    | V     |       | 0.01                  |       |       | 0.01                  |           | µA/°C  |

| REFERENCE/CONTROL AMP                                                  |          |       |       |                       |       |       |                       |           |        |

| Internal Reference Voltage                                             | +25°C    | I     | -1.14 | -1.18                 | -1.22 | -1.14 | -1.18                 | -1.22     | V      |

|                                                                        | Full     | VI    | -1.12 |                       | -1.24 | -1.12 |                       | -1.24     | V      |

| Internal Reference Voltage Drift                                       | Full     | V     |       | 50                    |       |       | 50                    |           | ppm/°C |

| Internal Reference Output Current                                      | Full     | IV    | -50   |                       | +500  | -50   |                       | +500      | μA     |

| Amplifier Input Impedance                                              | +25°C    | V     |       | 50                    |       |       | 50                    |           | kΩ     |

| Amplifier Bandwidth                                                    | +25°C    | v     |       | 300                   |       |       | 300                   |           | kHz    |

|                                                                        |          |       |       |                       |       |       |                       |           |        |

| REFERENCE INPUT <sup>2</sup>                                           | . 9500   | V     |       | 0                     |       |       | 0                     |           | 10     |

| Reference Input Impedance                                              | +25°C    | V     |       | 3                     |       |       | 3                     |           | kΩ     |

| Reference Multiplying Bandwidth <sup>3</sup>                           | +25°C    | V     |       | 40                    |       |       | 40                    |           | MHz    |

| DYNAMIC PERFORMANCE                                                    |          |       |       |                       |       |       |                       |           |        |

| Full-Scale Output Current <sup>4</sup>                                 | +25°C    | V     |       | 20.48                 |       |       | 20.48                 |           | mA     |

| Output Compliance Range                                                | +25°C    | IV    | -1.2  |                       | +2    | -1.2  |                       | +2        | V      |

| Output Resistance                                                      | +25°C    | IV    | 2.0   | 2.5                   | 3.0   | 2.0   | 2.5                   | 3.0       | kΩ     |

| Output Capacitance                                                     | +25°C    | V     |       | 15                    |       |       | 15                    |           | pF     |

| Output Update Rate <sup>5</sup>                                        | +25°C    | IV    | 100   | 110                   |       | 80    | 100                   |           | MSPS   |

| Output Settling Time (t <sub>ST</sub> ) <sup>6</sup>                   | +25°C    | V     |       | 27                    |       |       | 27                    |           | ns     |

| Output Propagation Delay (t <sub>PD</sub> ) <sup>7</sup>               | +25°C    | V     |       | 6                     |       |       | 7                     |           | ns     |

| Glitch Impulse <sup>8</sup>                                            | +25°C    | V     |       | 28                    |       |       | 28                    |           | pV-s   |

| Output Rise Time <sup>9</sup>                                          | +25°C    | V     |       | 2                     |       |       | 2                     |           | ns     |

| Output Fall Time <sup>9</sup>                                          | +25°C    | V     |       | 2                     |       |       | 2                     |           | ns     |

| DIGITAL INPUTS                                                         |          |       |       |                       |       |       |                       |           |        |

| Logic "1" Voltage                                                      | Full     | VI    | -1.0  | -0.8                  |       | 2.0   |                       |           | v      |

| Logic "0" Voltage                                                      | Full     | VI    | -1.0  | -1.7                  | -1.5  | 2.0   |                       | 0.8       | v      |

| Logic "1" Current                                                      | Full     | VI    |       | -1.7                  | 20    |       |                       | 20        | μA     |

| Logic "0" Current                                                      | Full     | VI    |       |                       | 10    |       |                       | 20<br>600 | μΑ     |

| Input Capacitance                                                      | +25°C    | V     |       | 3                     | 10    |       | 3                     | 000       | pF     |

| Input Capacitatice<br>Input Setup Time (t <sub>s</sub> ) <sup>10</sup> | +25°C    | IV    | 0.5   | -0.3                  |       | 0.5   | -0.3                  |           | ns     |

| input Setup Time (ts)                                                  | Full     | IV    | 0.5   | -0.5                  |       | 0.3   | -0.5                  |           | ns     |

| Input Hold Time (t <sub>H</sub> ) <sup>11</sup>                        | +25°C    | IV    | 1.8   | 1.2                   |       | 1.8   | 1.2                   |           | ns     |

| mpar more mine (rH)                                                    | Full     | IV    | 2.0   | 1.6                   |       | 2.0   | 1.6                   |           | ns     |

| Latch Pulse Width $(t_{LPW})$ (LOW)                                    | +25°C    | IV    | 2.0   | 1.7                   |       | 2.0   | 1.7                   |           | ns     |

|                                                                        | Full     | 11    | 2.5   | 1.7                   |       | 2.3   | 1.7                   |           | ns     |

| (Transparent)                                                          | 1°uii    |       | 2.0   |                       |       | 2.0   |                       |           | 115    |

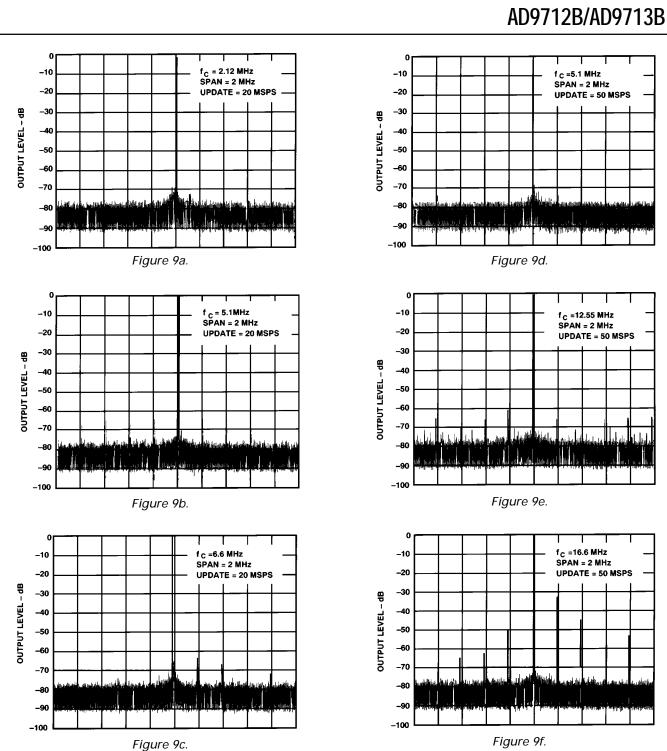

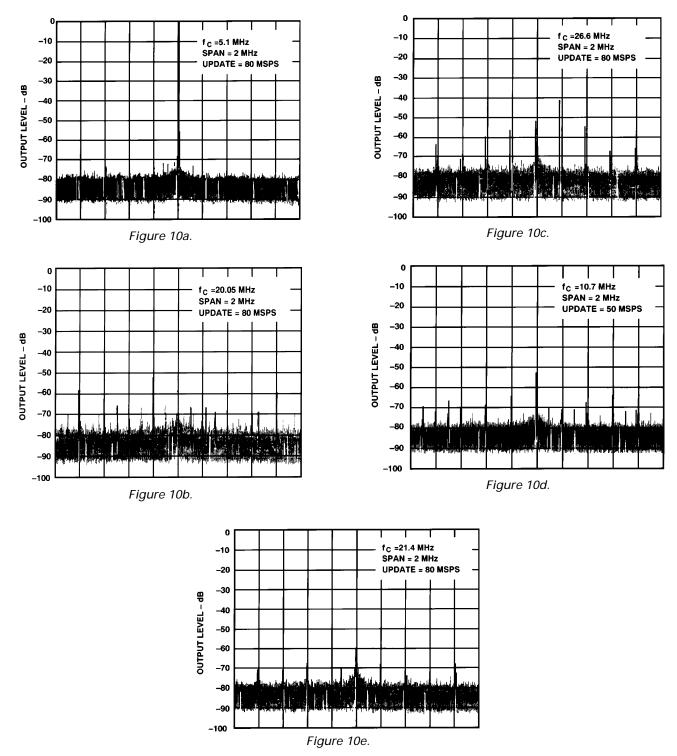

| AC LINEARITY <sup>12</sup>                                             |          |       |       |                       |       |       |                       |           |        |

| Spurious-Free Dynamic Range (SFDR)                                     |          |       |       |                       |       |       |                       |           |        |

| 1.23 MHz; 10 MSPS; 2 MHz Span                                          | +25°C    | V     |       | 70                    |       |       | 70                    |           | dB     |

| 5.055 MHz; 20 MSPS; 2 MHz Span                                         | +25°C    | V     |       | 72                    |       |       | 72                    |           | dB     |

| 10.1 MHz; 50 MSPS; 2 MHz Span                                          | +25°C    | V     |       | 68                    |       |       | 68                    |           | dB     |

| 16 MHz; 40 MSPS; 10 MHz Span                                           | +25°C    | V     |       | 68                    |       |       | 68                    |           | dB     |

| Demonster (Conditions)                            | <b>T</b> | Test  |     | AD9712B<br>All Grades | Mar |     | AD9713B<br>All Grades | 5   | Timita |

|---------------------------------------------------|----------|-------|-----|-----------------------|-----|-----|-----------------------|-----|--------|

| Parameter (Conditions)                            | Temp     | Level | Min | Тур                   | Max | Min | Тур                   | Max | Units  |

| POWER SUPPLY <sup>13</sup>                        |          |       |     |                       |     |     |                       |     |        |

| Positive Supply Current (+5.0 V)                  | +25°C    | I     |     |                       |     |     | 6                     | 12  | mA     |

|                                                   | Full     | VI    |     |                       |     |     |                       | 14  | mA     |

| Negative Supply Current (-5.2 V) <sup>14</sup>    | +25°C    | Ι     |     | 140                   | 178 |     | 145                   | 184 | mA     |

| 0 11 5                                            | Full     | VI    |     |                       | 183 |     |                       | 188 | mA     |

| Nominal Power Dissipation                         | +25°C    | V     |     | 728                   |     |     | 784                   |     | mW     |

| Power Supply Rejection Radio (PSRR) <sup>15</sup> | +25°C    | Ι     |     | 30                    | 100 |     | 30                    | 100 | μA/V   |

NOTES

$^{1}$ Measured as error in ratio of full-scale current to current through  $R_{SET}$  (160  $\mu$ A nominal); ratio is nominally 128.

<sup>2</sup>Full-scale variations among devices are higher when driving REFERENCE INPUT directly.

<sup>3</sup>Frequency at which the gain is flat  $\pm 0.5$  dB;  $R_L = 50 \Omega$ ; 50% modulation at midscale.

<sup>4</sup>Based on  $I_{FS} = 128$  ( $V_{REF}/R_{SET}$ ) when using internal amplifier.

<sup>5</sup>Data registered into DAC accurately at this rate; does not imply settling to 12-bit accuracy.

$^6Measured$  as voltage settling at midscale transition to  $\pm 0.024\%,~R_L$  = 50  $\Omega.$

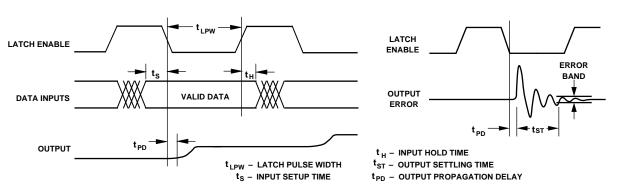

<sup>7</sup>Measured as the time between the 50% point of the falling edge of LATCH ENABLE and the point where the output signal has left a 1 LSB error band around its previous value.

<sup>8</sup>Peak glitch impulse is measured as the largest area under a single positive or negative transient.

<sup>9</sup>Measured with  $R_L = 50 \Omega$  and DAC operating in latched mode.

<sup>10</sup>Data must remain stable for specified time prior to falling edge of LATCH ENABLE signal.

<sup>11</sup>Data must remain stable for specified time after rising edge of LATCH ENABLE signal.

<sup>12</sup>SFDR is defined as the difference in signal energy between the fundamental and worst case spurious frequencies in the output spectrum window, which is centered at the fundamental frequency and covers the indicated span.

<sup>13</sup>Supply voltages should remain stable within  $\pm 5\%$  for normal operation.

$^{14}108$  mA typ on Digital –V<sub>S</sub>, 37 mA typ on Analog –V<sub>S</sub>.

$^{15}$  Measured at  $\pm5\%$  of +V\_S (AD9713B only) and -V\_S (AD9712B or AD9713B) using external reference.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Positive Supply Voltage (+V <sub>S</sub> ) (AD9713B Only) +6 V           |

|--------------------------------------------------------------------------|

| Negative Supply Voltage (-V <sub>S</sub> )7 V                            |

| Analog-to-Digital Ground Voltage Differential 0.5 V                      |

| Digital Input Voltages (D <sub>1</sub> -D <sub>12</sub> , LATCH ENABLE)  |

| $AD9712B$ $O$ V to $-V_S$                                                |

| AD9713B0.5 V to +V <sub>s</sub>                                          |

| Internal Reference Output Current                                        |

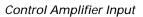

| Control Amplifier Input Voltage Range 0 V to -4 V                        |

| Control Amplifier Output Current ±2.5 mA                                 |

| Reference Input Voltage Range (V <sub>REF</sub> ) 0 V to -V <sub>S</sub> |

| Analog Output Current                                                    |

| Operating Temperature Range                                              |

| AD9712B/AD9713BAN/AP/BN/BP25°C to +85°C                                  |

| AD9712B/AD9713BSE/SQ/TE/TQ55°C to +125°C                                 |

| Maximum Junction Temperature <sup>2</sup>                                |

| AD9712B/AD9713BAN/AP/BN/BP +150°C                                        |

| AD9712B/AD9713BSE/SQ/TE/TQ +175°C                                        |

| Lead Temperature (Soldering, 10 sec) +300°C                              |

| Storage Temperature Range65°C to +150°C                                  |

#### NOTES

<sup>1</sup>Absolute maximum ratings are limiting values to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability is not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

<sup>2</sup>Typical thermal impedances with parts soldered in place: 28-pin plastic DIP:  $\theta_{JA} = 37^{\circ}C/W$ ,  $\theta_{JC} = 10^{\circ}C/W$ ; 28-pin PLCC:  $\theta_{JA} = 44^{\circ}C/W$ ,  $\theta_{JC} = 14^{\circ}C/W$ ; Cerdip:  $\theta_{JA} = 32^{\circ}C/W$ ,  $\theta_{JC} = 10^{\circ}C/W$ ; LCC:  $\theta_{JA} = 41^{\circ}C/W$ ,  $\theta_{JC} = 13^{\circ}C/W$ . No air flow.

#### **ORDERING GUIDE**

| Model          | Temperature<br>Range | Package<br>Description | Package<br>Option |

|----------------|----------------------|------------------------|-------------------|

| AD9712BAN      | -25°C to +85°C       | 28-Pin PDIP            | N-28              |

| AD9712BBN      | -25°C to +85°C       | 28-Pin PDIP            | N-28              |

| AD9712BAP      | -25°C to +85°C       | 28-Pin PLCC            | P-28A             |

| AD9712BBP      | -25°C to +85°C       | 28-Pin PLCC            | P-28A             |

| AD9712BSQ/883B | -55°C to +125°C      | 28-Pin Cerdip          | Q-28              |

| AD9712BSE/883B | -55°C to +125°C      | 28-Pin LCC             | E-28A             |

| AD9712BTQ/883B | -55°C to +125°C      | 28-Pin Cerdip          | Q-28              |

| AD9712BTE/883B | -55°C to +125°C      | 28-Pin LCC             | E-28A             |

| AD9713BAN      | -25°C to +85°C       | 28-Pin PDIP            | N-28              |

| AD9713BBN      | -25°C to +85°C       | 28-Pin PDIP            | N-28              |

| AD9713BAP      | -25°C to +85°C       | 28-Pin PLCC            | P-28A             |

| AD9713BBP      | -25°C to +85°C       | 28-Pin PLCC            | P-28A             |

| AD9713BSQ/883B | -55°C to +125°C      | 28-Pin Cerdip          | Q-28              |

| AD9713BSE/883B | -55°C to +125°C      | 28-Pin LCC             | E-28A             |

| AD9713BTQ/883B | -55°C to +125°C      | 28-Pin Cerdip          | Q-28              |

| AD9713BTE/883B | -55°C to +125°C      | 28-Pin LCC             | E-28A             |

#### EXPLANATION OF TEST LEVELS

#### **Test Level**

- I 100% production tested.

- II 100% production tested at +25°C, and sample tested at specified temperatures.

- III Sample tested only.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI All devices are 100% tested at +25°C. 100% production tested at temperature extremes for extended temperature devices; sample tested at temperature extremes for commercial/industrial devices.

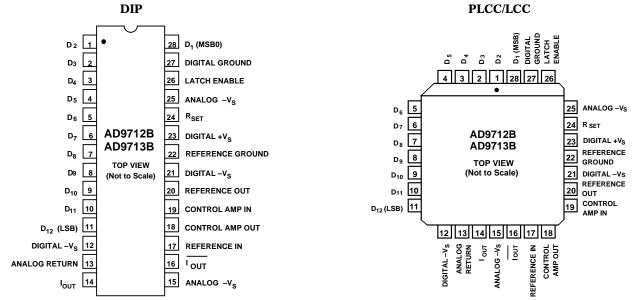

| Pin # | Name                            | Function                                                                                                                                                                                                                                                                                     |                       |                                          |  |  |  |  |

|-------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------|--|--|--|--|

| 1-10  | D <sub>2</sub> -D <sub>11</sub> | Ten bits of twelve-bit digital input word.                                                                                                                                                                                                                                                   |                       |                                          |  |  |  |  |

| 11    | $D_{12}$ (LSB)                  | Least Significant Bit (LSB) of digital input word.                                                                                                                                                                                                                                           |                       |                                          |  |  |  |  |

|       |                                 | Input Coding vs. Current Output                                                                                                                                                                                                                                                              |                       |                                          |  |  |  |  |

|       |                                 | Input Code D <sub>1</sub> -D <sub>12</sub>                                                                                                                                                                                                                                                   | I <sub>OUT</sub> (mA) | I <sub>OUT</sub> (mA)                    |  |  |  |  |

|       |                                 | 111111111<br>0000000000                                                                                                                                                                                                                                                                      | -20.475<br>0          | 0<br>-20.475                             |  |  |  |  |

| 12    | DIGITAL –Vs                     | One of two negative digital supply pins; nominally -5.2 V.                                                                                                                                                                                                                                   |                       |                                          |  |  |  |  |

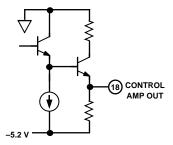

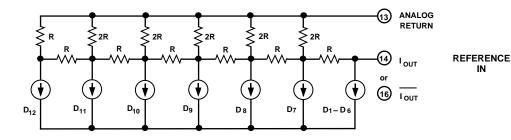

| 13    | ANALOG RETURN                   | Analog ground return. This point and the reference side of the DAC load resistors should be connected to the same potential (nominally ground).                                                                                                                                              |                       |                                          |  |  |  |  |

| 14    | I <sub>OUT</sub>                | Analog current output; full-scale output occurs with digital inputs at all "1."                                                                                                                                                                                                              |                       |                                          |  |  |  |  |

| 15    | ANALOG –Vs                      | One of two negative analog supply pins; nominally -5.2 V.                                                                                                                                                                                                                                    |                       |                                          |  |  |  |  |

| 16    | I <sub>OUT</sub>                | Complementary analog current output; zero scale output occurs with digital inputs at all "1."                                                                                                                                                                                                |                       |                                          |  |  |  |  |

| 17    | REFERENCE IN                    | Normally connected to CONTROL AMP OUT (Pin 18). Direct line to DAC current source network. Voltage changes at this point have a direct effect on the full-scale output value of unit. Full-scale current output = $128$ (Reference voltage/R <sub>SET</sub> ) when using internal amplifier. |                       |                                          |  |  |  |  |

| 18    | CONTROL AMP OUT                 | Normally connected to REFERENCE INPUT (Pin 17). Output of internal control amplifier, which provides a temperature-compensated drive level to the current switch network.                                                                                                                    |                       |                                          |  |  |  |  |

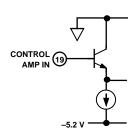

| 19    | CONTROL AMP IN                  | Normally connected to REFERENCE OUT (Pin 20) if not connected to external reference.                                                                                                                                                                                                         |                       |                                          |  |  |  |  |

| 20    | REFERENCE OUT                   | Normally connected to CONTROL AMP IN (Pin 19). Internal voltage reference, nominally -1.18 V.                                                                                                                                                                                                |                       |                                          |  |  |  |  |

| 21    | DIGITAL -Vs                     | One of two negative digital supply pins; nominally –5.2 V.                                                                                                                                                                                                                                   |                       |                                          |  |  |  |  |

| 22    | REFERENCE GROUND                | Ground return for the                                                                                                                                                                                                                                                                        | internal voltage re   | eference and amplifier.                  |  |  |  |  |

| 23    | DIGITAL +V <sub>S</sub>         | Positive digital supply pin, used only on the AD9713B; nominally +5 V. No connection to this pin on AD9712B.                                                                                                                                                                                 |                       |                                          |  |  |  |  |

| 24    | R <sub>SET</sub>                | Connection for external resistance reference. Full-scale current out = 128 (Reference voltage/ $R_{SET}$ ) when using internal amplifier. Nominally 7.5 k $\Omega$ .                                                                                                                         |                       |                                          |  |  |  |  |

| 25    | ANALOG –Vs                      | One of two negative an                                                                                                                                                                                                                                                                       | alog supply pins;     | nominally -5.2 V.                        |  |  |  |  |

| 26    | LATCH ENABLE                    | Transparent latch cont                                                                                                                                                                                                                                                                       | rol line. Register i  | is transparent when LATCH ENABLE is LOW. |  |  |  |  |

| 27    | DIGITAL GROUND                  | Digital ground return.                                                                                                                                                                                                                                                                       |                       |                                          |  |  |  |  |

| 28    | D <sub>1</sub> (MSB)            | Most Significant Bit (MSB) of digital input word.                                                                                                                                                                                                                                            |                       |                                          |  |  |  |  |

### **PIN DESCRIPTIONS**

#### **PIN CONFIGURATIONS**

DIP

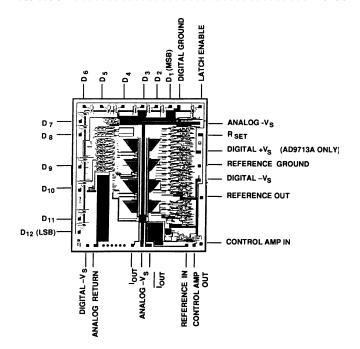

#### DIE LAYOUT AND METALIZATION INFORMATION

| Die Dimensions      | $220 \times 196 \times 15 \ (\pm 2)$ mils |

|---------------------|-------------------------------------------|

| Pad Dimensions      | $\ldots \ldots 4 \times 4$ mils           |

| Metalization        | Aluminum                                  |

| Backing             | None                                      |

| Substrate Potential |                                           |

| Passivation         | Nitride                                   |

#### THEORY AND APPLICATIONS

The AD9712B and AD9713B high speed digital-to-analog converters utilize Most Significant Bit (MSB) decoding and segmentation techniques to reduce glitch impulse and maintain 12-bit linearity without trimming.

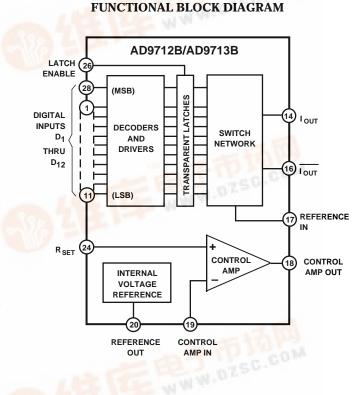

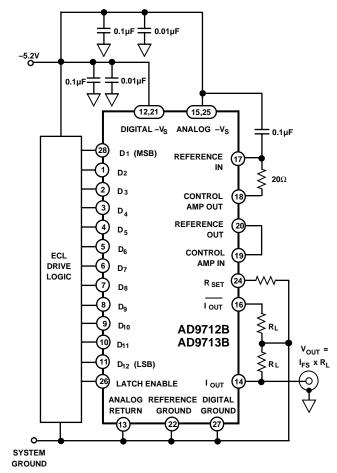

As shown in the functional block diagram, the design is based on four main subsections: the Decoder/Driver circuits, the Transparent Latches, the Switch Network, and the Control Amplifier. An internal bandgap reference is also included to allow operation with a minimum of external components.

#### **Digital Inputs/Timing**

The AD9712B employs single-ended ECL-compatible inputs for data inputs  $D_1-D_{12}$  and LATCH ENABLE. The internal ECL midpoint reference is designed to match 10K ECL device thresholds. On the AD9713B, a TTL translator is added at each input; with this exception, the AD9712B and AD9713B are identical.

In the Decoder/Driver section, the four MSBs  $(D_1-D_4)$  are decoded to 15 "thermometer code" lines. An equalizing delay is included for the eight Least Significant Bits (LSBs) and LATCH ENABLE. This delay minimizes data skew, and data setup and hold times at the latch inputs; this is important when operating the latches in the transparent mode. Without the delay, skew caused by the decoding circuits would degrade glitch impulse.

The latches operate in their transparent mode when LATCH ENABLE (Pin 26) is at logic level "0." The latches should be used to synchronize data to the current switches by applying a narrow LATCH ENABLE pulse with proper data setup and hold times as shown in the Timing Diagram. An external latch at each data input, clocked out of phase with the Latch Enable, operates the AD9712B/AD9713B in a master slave (edgetriggered) mode. This is the optimum way to operate the DAC because data is always stable at the DAC input. An external latch eases timing constraints when using the converter.

Although the AD9712B/AD9713B chip is designed to provide isolation from digital inputs to the outputs, some coupling of digital transitions is inevitable, especially with TTL or CMOS inputs applied to the AD9713B. Digital feedthrough can be reduced by forming a low-pass filter using a (200  $\Omega$ ) series resistor in series with the capacitance of each digital input; this rolls off the slew rate of the digital inputs.

#### References

As shown in the functional block diagram, the internal bandgap reference, control amplifier, and reference input are pinned out for maximum user flexibility when setting the reference.

When using the internal reference, REFERENCE OUT (Pin 20) should be connected to CONTROL AMP IN (Pin 19). CONTROL AMP OUT (Pin 18) should be connected to REFERENCE IN (Pin 17) through a 20  $\Omega$  resistor. A 0.1  $\mu$ F ceramic capacitor from Pin 17 to  $-V_S$  (Pin 15) improves settling by decoupling switching noise from the current sink base line. A reference current cell provides feedback to the control amp by sinking current through R<sub>SET</sub> (Pin 24).

Timing Diagram

Full-scale output current is determined by CONTROL AMP IN and  $R_{SET}$  according to the equation:

$I_{OUT}(FS) = (CONTROL AMP IN/R_{SET}) \times 128$

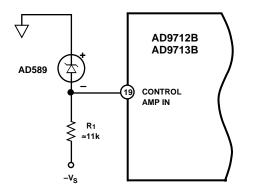

The internal reference is nominally -1.18 V with a tolerance of  $\pm 3.5\%$  and typical drift over temperature of 50 ppm/°C. If greater accuracy or better temperature stability is required, an external reference can be utilized. The AD589 reference shown in Figure 1 features  $\pm 10$  ppm/°C drift over temperatures from 0°C to +70°C.

Figure 1. Use of AD589 as External Reference

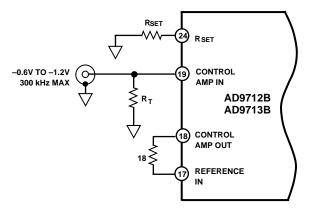

Two modes of multiplying operation are possible with the AD9712B/AD9713B. Signals with small signal bandwidths up to 300 kHz and input swings of 100 mV, or dc signals from -0.6 V to -1.2 V can be applied to the CONTROL AMP input as shown in Figure 2. Because the control amplifier is internally compensated, the 0.1  $\mu$ F capacitor at Pin 17 can be reduced to 0.01  $\mu$ F to maximize the multiplying bandwidth. However, it should be noted that settling time for changes to the digital inputs will be degraded.

Figure 2. Low Frequency Multiplying Circuit

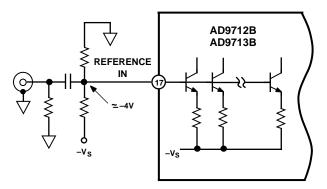

The REFERENCE IN pin can also be driven directly for wider bandwidth multiplying operation. The analog signal for this mode of operation must have a signal swing in the range of -3.75 V to -4.25 V. This can be implemented by capacitively coupling into REFERENCE IN a signal with a dc bias of -3.75 V to -4.25 V, as shown in Figure 3; or by driving REFERENCE IN with a low impedance op amp whose signal swing is limited to the stated range.

#### Outputs

As indicated earlier,  $D_1$ - $D_4$  (four MSBs) are decoded and drive 15 discrete current sinks. D5 and D6 are binarily weighted; and  $D_7$ - $D_{12}$  are applied to the R-2R network. This segmented architecture reduces frequency domain errors due to glitch impulse.

Figure 3. Wideband Multiplying Circuit

The Switch Network provides complementary current outputs  $I_{OUT}$  and  $\overline{I_{OUT}}$ . These current outputs are based on statistical current source matching which provides 12-bit linearity without trim. Current is steered to either  $I_{OUT}$  or  $\overline{I_{OUT}}$  in proportion to the digital input code. The sum of the two currents is always equal to the full-scale output current minus one LSB.

The current output can be converted to a voltage by resistive loading as shown in Figure 4. Both  $I_{OUT}$  and  $\overline{I}_{OUT}$  should be loaded equally for best overall performance. The voltage which is developed is the product of the output current and the value of the load resistor.

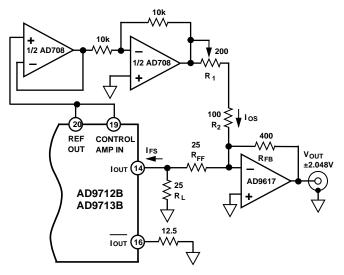

DAC current across feedback resistor  $R_{FB}$  determines the AD9617 output swing. A current divider formed by  $R_L$  and  $R_{FF}$  limits the current used in the I-to-V conversion, and provides an output voltage swing within the specifications of the AD9617. Current through  $R_2$  provides dc offset at the output of the AD9617. Adjusting the value of  $R_1$  adjusts the value of offset current. This offset current is based on the reference of the AD9712B/AD9713B, to avoid coupling noise into the output signal.

The resistor values in Figure 5 provide a 4.096 V swing, centered at ground, at the output of the AD9617 amplifier.

#### Power and Grounding

Maintaining low noise on power supplies and ground is critical for obtaining optimum results with the AD9712B or AD9713B. DACs are most often used in circuits which are predominantly digital. To preserve 12-bit performance, especially at conversion speeds up to 100 MSPS, special precautions are necessary for power supplies and grounding.

Ideally, the DAC should have a separate analog ground plane. All ground pins of the DAC, as well as reference and analog output components, should be tied directly to this analog ground plane. The DAC's ground plane should be connected to the system ground plane at a single point.

Ferrite beads such as the Stackpole 57-1392 or Amidon FB-43B-101, along with high frequency, low-inductance decoupling capacitors, should be used for the supply connections to isolate digital switching currents from the DAC supply pins. Separate isolation networks for the digital and analog supply connections will further reduce supply noise coupling to the output.

Molded socket assemblies should be avoided even when prototyping circuits with the AD9712B or AD9713B. When the DAC cannot be directly soldered into the board, individual pin sockets such as AMP #6-330808-0 (knock-out end), or #60330808-3 (open end) should be used. These have much less effect on inter-lead capacitance than do molded assemblies.

#### **DDS Applications**

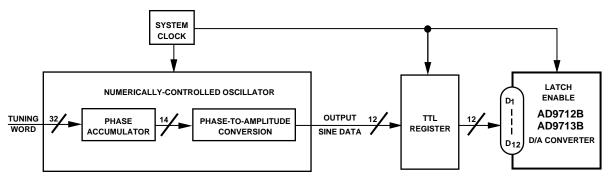

Numerically controlled oscillators (NCOs) are digital devices which generate samples of a sine wave. When the NCO is combined with a high performance D/A converter (DAC), the combination system is referred to as a Direct Digital Synthesizer (DDS).

The digital samples generated by the NCO are reconstructed by the DAC and the resulting sine wave is usable in any system which requires a stable, spectrally pure, frequency-agile reference. The DAC is often the limiting factor in DDS applications, since it is the only analog function in the circuit. The AD9712B/ AD9713B D/A converters offer the highest level of performance available for DDS applications.

DC linearity errors of a DAC are the dominant effect in lowfrequency applications and can affect both noise and harmonic content in the output waveform. Differential Nonlinearity (DNL) errors determine the quantization error between adjacent codes, while Integral Nonlinearity (INL) is a measure of how closely the overall transfer function of the DAC compares with an ideal device. Together, these errors establish the limits of phase and amplitude accuracy in the output waveform.

Figure 4. Typical Resistive Load Connection

An operational amplifier can also be used to perform the I to V conversion of the DAC output. Figure 5 shows an example of a circuit which uses the AD9617, a high speed, current feedback amplifier.

Figure 5. I/VConversion Using Current Feedback

Figure 6. Direct Digital Synthesizer Block Diagram

When the analog frequency  $(f_A)$  is exactly  $f_C/N$  and N is an even integer, the DDS continually uses a small subset of the available DAC codes. The DNL of the converter is effectively the DNL error of the codes used, and is typically worse than the error measured against all available DAC codes. This increase in DNL is translated into higher harmonic and noise levels at the output.

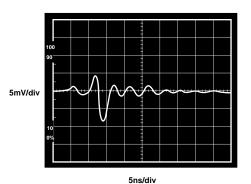

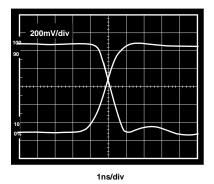

Glitch impulse, often considered a figure of merit in DDS applications, is simply the initial transient response of the DAC as it moves between two output levels. This nonlinearity is commonly associated with external data skew, but this effect is minimized by using the on-board registers of the AD9712B/AD9713B converters (see Digital Inputs/Timing section). The majority of the glitch impulse, shown below, is produced as the current in the R-2R ladder network settles, and is fairly constant over the full-scale range of the DAC. The fast transients which form the glitch impulse appear as high-frequency spurs in the output spectrum.

While it is difficult to predict the effects of glitch on the output waveform, slew rate limitations translate directly into harmonics. This makes slew rate the dominant effect in ac linearity of the DAC. Applications in which the ratio of analog frequency ( $f_A$ ) to clock frequency ( $f_C$ ) is relatively high will benefit from the high slew rate and low output capacitance of the AD9712B/AD9713B devices.

Another concern in DDS applications is the presence of aliased harmonics in the output spectrum. Aliased harmonics appear as spurs in the output spectrum at frequencies which are determined by:

$$MfA \pm Nf_C$$

where M and N are integers.

The effects of these spurs are most easily observed in applications where  $f_A$  is nearly equal to an integer fraction of the clock rate. This condition causes the aliased harmonics to fold near the fundamental output frequency (see Performance Curves.)

Figure 7. AD9712B/AD9713B Glitch Impulse

Figure 8. Rise and Fall Characteristics

Figure 9. Typical Spectral Performance

Figure 10. Typical Spectral Performance

ECL V<sub>MID</sub>

O V<sub>BIAS</sub>

138 CURRENT SOURCES

Control Amp Output

R-2R DAC (for 6 LSBs)

ECL IN

–5.2 V

ECL Input Buffer

(17

REFERENCE

IN

Ş

–5.2 V

+5V O

TTL O

**≷** 10 kΩ

TTL Input Buffer

(24) R SET

+ CONTROL

AMP

Full-Scale Current Control Loop

CONTROL

AMP OUT

ウ

REFERENCE 20 OUT

AMP IN

Ş

**2.5k**Ω

–5.2 V

(17

Reference Input

Output Circuit

Figure 11. Equivalent Circuits

$\downarrow$ 20 REFERENCE OUT –5.2 V

Reference Output

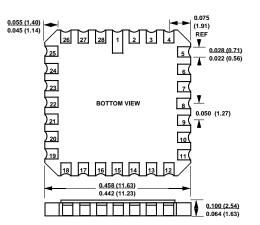

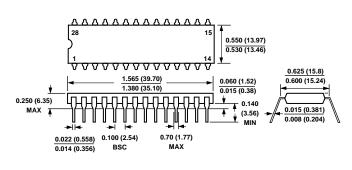

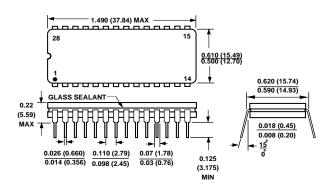

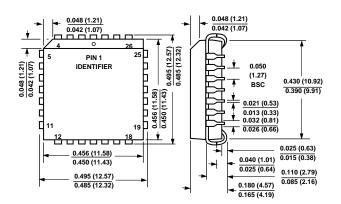

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 28-Pin Plastic DIP (Suffix N)

28-Pin Cerdip (Suffix Q)

#### 28-Pin Plastic Leaded Chip Carrier (Suffix P)

28-Pin LCC Package (Suffix E)