FUJITSU SEMICONDUCTOR DATA SHEET

DS05-20867-3E

WWW.DZSC.COM

# FLASH MEMORY

**CMOS**

# 2M (256K × 8/128K × 16) BIT

# MBM29F200TC-55/-70/-90/MBM29F200BC-55/-70/-90

#### ■ FEATURES

- Single 5.0 V read, write, and erase

Minimizes system level power requirements

- Compatible with JEDEC-standard commands Uses same software commands as E<sup>2</sup>PROMs

- Compatible with JEDEC-standard world-wide pinouts

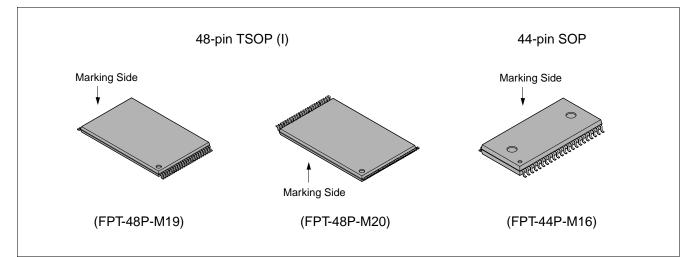

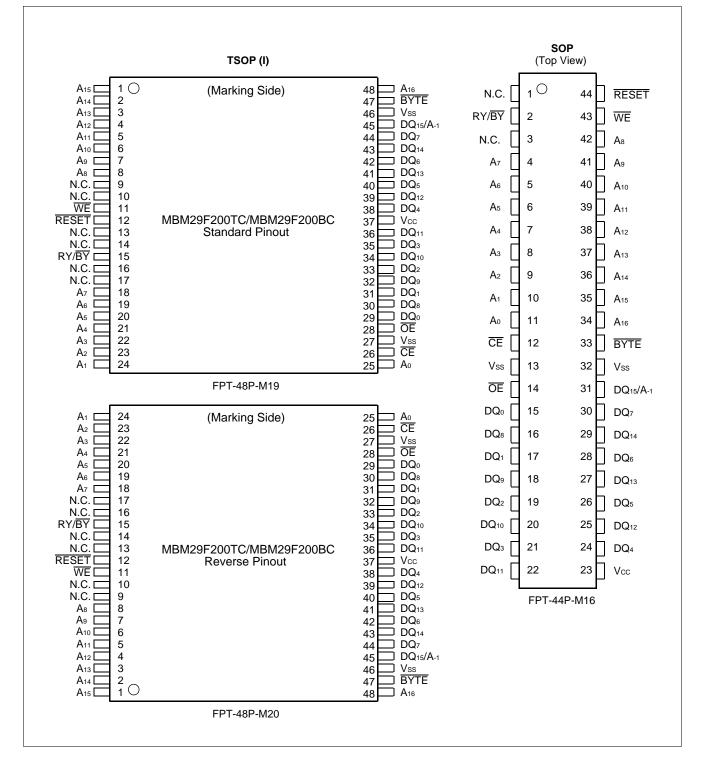

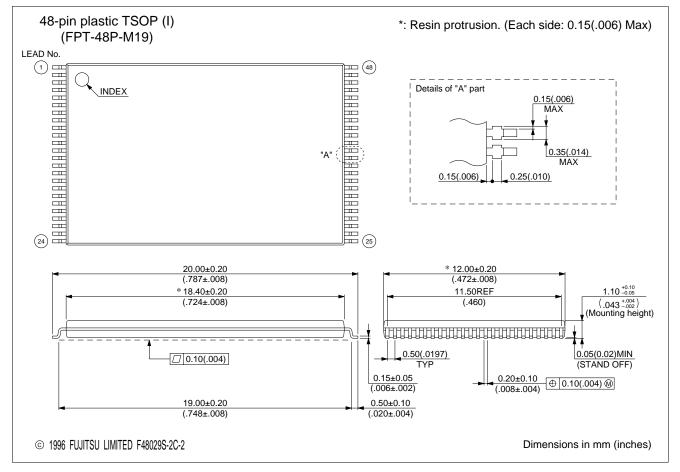

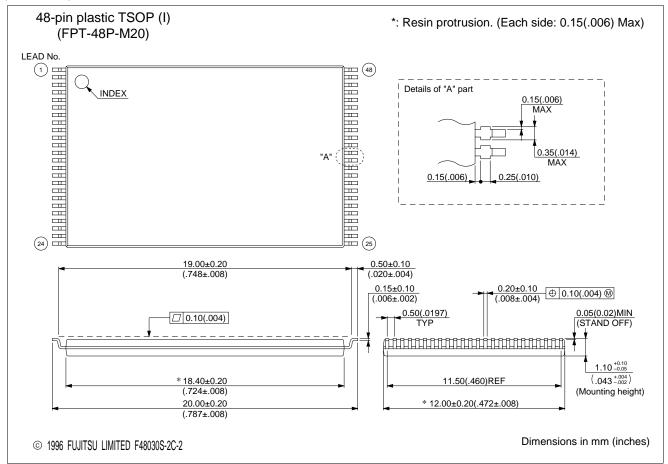

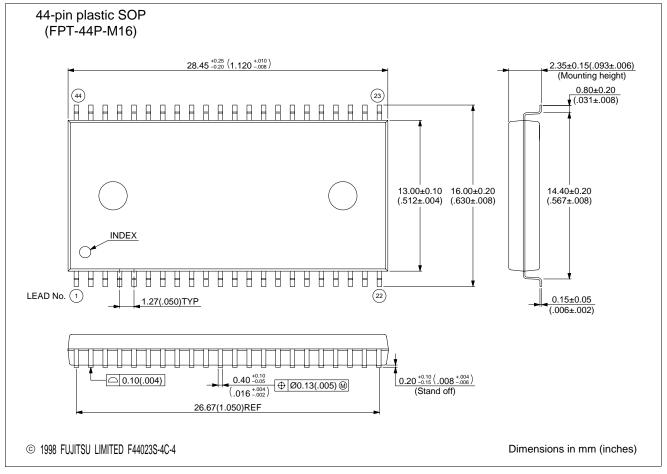

48-pin TSOP (Package suffix: PFTN Normal Bend Type, PFTR Reversed Bend Type)

44-pin SOP (Package suffix: PF)

- Minimum 100,000 write/erase cycles

- High performance 55 ns maximum access time

- Sector erase architecture One 16K byte, two 8K bytes, one 32K byte, and three 64K bytes. Any combination of sectors can be concurrently erased. Also supports full chip erase.

- Boot Code Sector Architecture T = Top sector

- B = Bottom sector

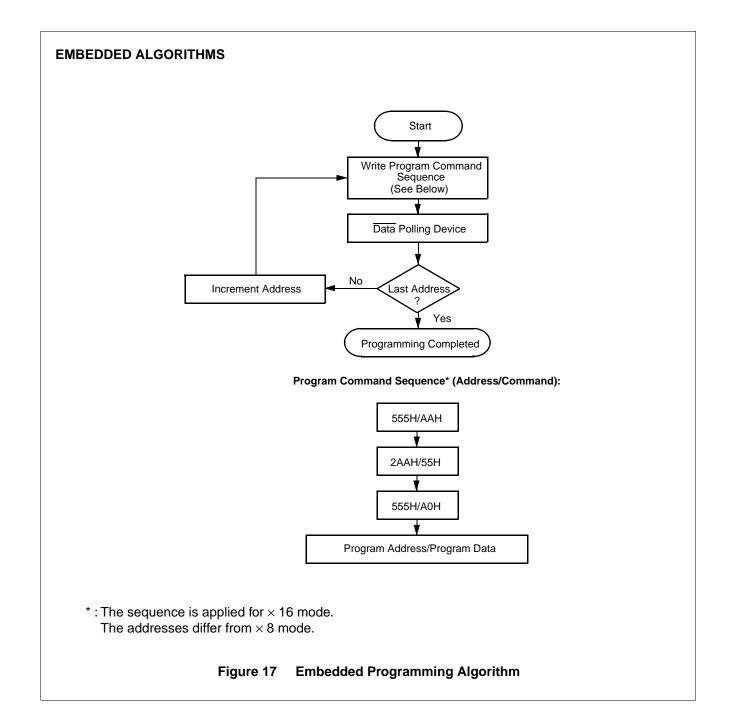

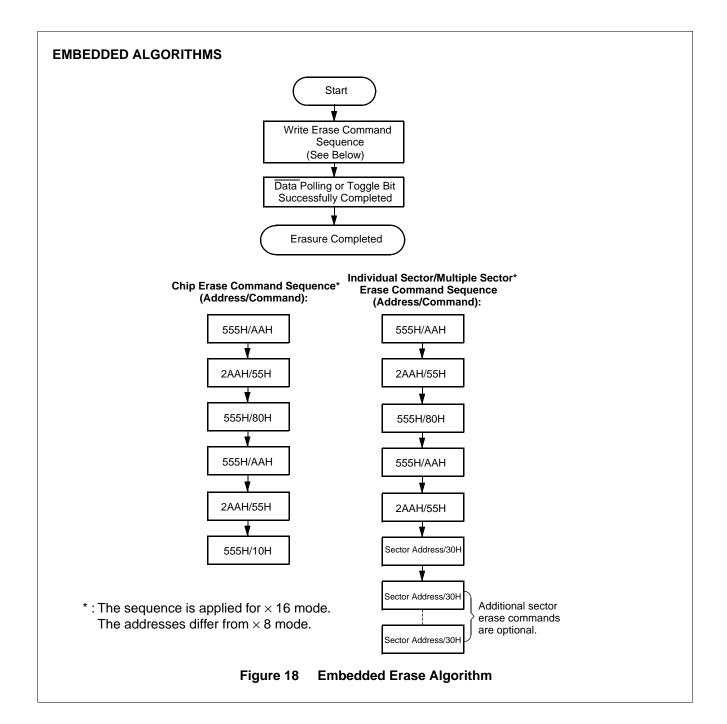

- Embedded Erase<sup>™</sup> Algorithms Automatically pre-programs and erases the chip or any sector

- Embedded Program<sup>™</sup> Algorithms Automatically writes and verifies data at specified address

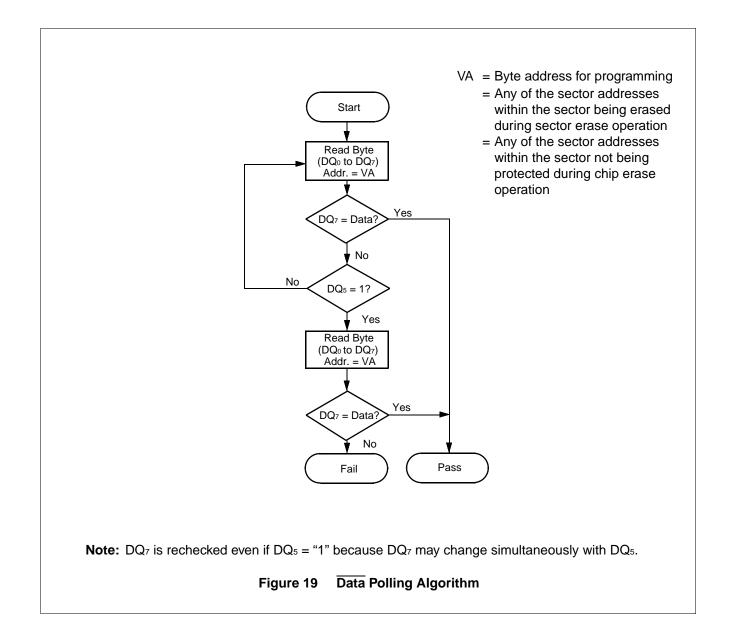

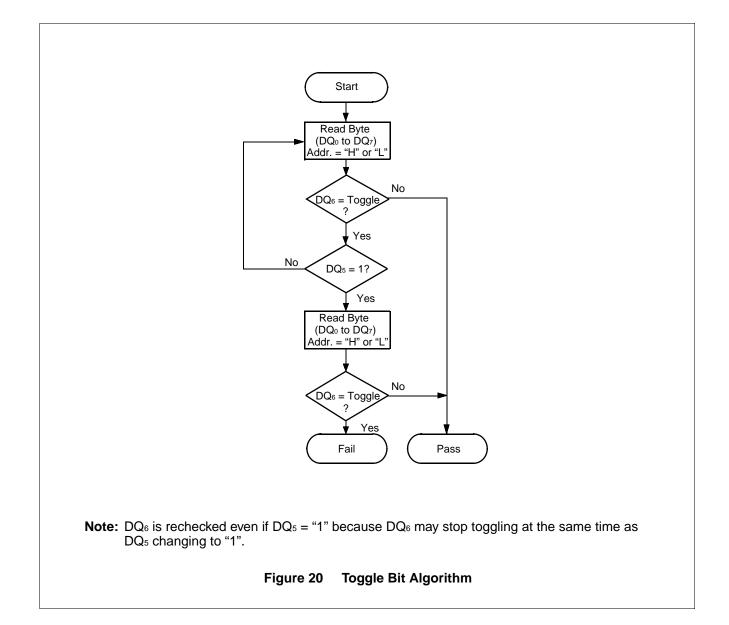

- Data Polling and Toggle Bit feature for detection of program or erase cycle completion

- Ready/Busy output (RY/BY)

Hardware method for detection of program or erase cycle completion

- Low Vcc write inhibit ≤ 3.2 V

- Erase Suspend/Resume Suspends the erase operation to allow a read in another sector within the same device

- Hardware RESET pin

Resets internal state machine to the read mode

- Sector protection Hardware method disables any combination of sectors from write or erase operations

- Temporary sector unprotection

Hardware method temporarily enables any combination of sectors from write on erase operations.

Embedded Erase<sup>™</sup> and Embedded Program<sup>™</sup> are trademarks of Advanced Micro Devices, Inc.

■ PACKAGE

#### GENERAL DESCRIPTION

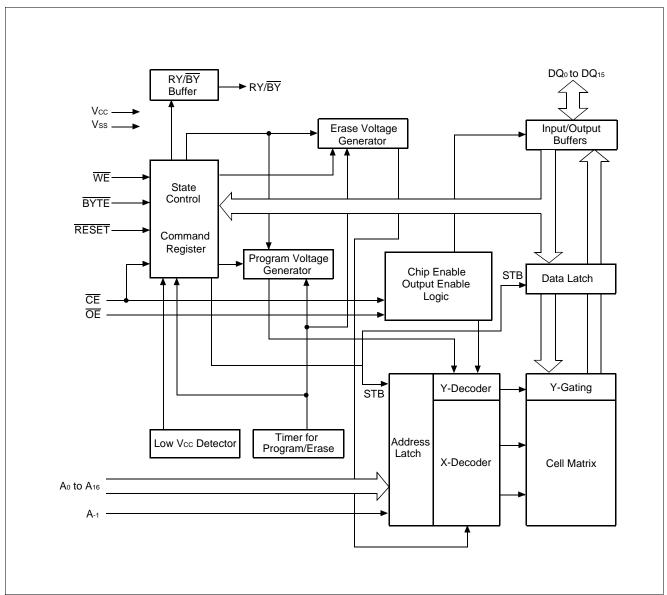

The MBM29F200TC/BC is a 2M-bit, 5.0 V-only Flash memory organized as 256K bytes of 8 bits each or 128K words of 16 bits each. The MBM29F200TC/BC is offered in a 48-pin TSOP and 44-pin SOP packages. This device is designed to be programmed in-system with the standard system 5.0 V V<sub>CC</sub> supply. 12.0 V V<sub>PP</sub> is not required for write or erase operations. The devices can also be reprogrammed in standard EPROM programmers. The standard MBM29F200TC/BC offers access times 55 ns and 90 ns allowing operation of high-speed microprocessors without wait states. To eliminate bus contention the device has separate chip enable ( $\overline{CE}$ ), write enable ( $\overline{WE}$ ), and output enable ( $\overline{OE}$ ) controls.

The MBM29F200TC/BC is pin and command set compatible with JEDEC standard. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state-machine which controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the devices is similar to reading from12.0 V Flash or EPROM devices.

The MBM29F200TC/BC is programmed by executing the program command sequence. This will invoke the Embedded Program Algorithm which is an internal algorithm that automatically times the program pulse widths and verifies proper cell margin. Typically, each sector can be programmed and verified in less than 0.5 seconds. Erase is accomplished by executing the erase command sequence. This will invoke the Embedded Erase Algorithm which is an internal algorithm that automatically preprograms the array if it is not already programmed before executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.

A sector is typically erased and verified in 1.0 second (if already completely preprogrammed.).

The devices also features a sector erase architecture. The sector mode allows each sector to be erased and reprogrammed without affecting other sectors. The MBM29F200TC/BC is erased when shipped from the factory.

The devices features single 5.0 V power supply operation for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations. A low V<sub>CC</sub> detector automatically inhibits write operations on the loss of power. The end of program or erase is detected by Data Polling of DQ<sub>7</sub>, by the Toggle Bit feature on DQ<sub>6</sub>, or the RY/BY output pin. Once the end of a program or erase cycle has been completed, the device internally resets to the read mode.

Fujitsu's Flash technology combines years of EPROM and E<sup>2</sup>PROM experience to produce the highest levels of quality, reliability, and cost effectiveness. The MBM29F200TC/BC memory electrically erase the entire chip or all bits within a sector simultaneously via Fowler-Nordhiem tunneling. The bytes/words are programmed one byte/word at a time using the EPROM programming mechanism of hot electron injection.

#### ■ FLEXIBLE SECTOR-ERASE ARCHITECTURE

- One 16K byte, two 8K bytes, one 32K byte, and three 64K bytes

- Individual-sector, multiple-sector, or bulk-erase capability

- Individual or multiple-sector protection is user definable.

|          | (×8)<br>- 3FFFFH | (×16)<br>1FFFFH |

|----------|------------------|-----------------|

| 16K byte |                  |                 |

| 8K byte  | 3BFFFH           | 1DFFFH          |

| 8K byte  | 39FFFH           | 1CFFFH          |

| 32K byte | 37FFFH           | 1BFFFH          |

| 64K byte | 2FFFFH           | 17FFFH          |

| 64K byte | 1FFFFH           | 0FFFFH          |

|          | OFFFFH           | 07FFFH          |

| 64K byte | 00000H           | 00000H          |

|          | (×8)   | (×16)  |

|----------|--------|--------|

| 64K byte | 3FFFFH | 1FFFFH |

|          | 2FFFFH | 17FFFH |

| 64K byte | 1FFFFH | 0FFFFH |

| 64K byte | 0FFFFH | 07FFFH |

| 32K byte | 07FFFH | 03FFFH |

| 8K byte  | •••••  |        |

| 8K byte  | 05FFFH | 02FFFH |

| 16K byte | 03FFFH | 01FFFH |

|          | 00000H | 00000H |

MBM29F200TC Sector Architecture

MBM29F200BC Sector Architecture

#### ■ PRODUCT LINE UP

| Par                | t No.                         | MBN | 129F200TC/MBM29F20 | 00BC |  |  |

|--------------------|-------------------------------|-----|--------------------|------|--|--|

| Ordering Part No.  | $Vcc = 5.0 \text{ V} \pm 5\%$ | -55 | —                  | —    |  |  |

| Ordening Part No.  | Vcc = 5.0 V ± 10%             | _   | -70                | -90  |  |  |

| Max. Address Acces | s Time (ns)                   | 55  | 55 70              |      |  |  |

| Max. CE Access Tin | ne (ns)                       | 55  | 70                 | 90   |  |  |

| Max. OE Access Tin | ne (ns)                       | 30  | 30                 | 35   |  |  |

#### BLOCK DIAGRAM

#### CONNECTION DIAGRAMS

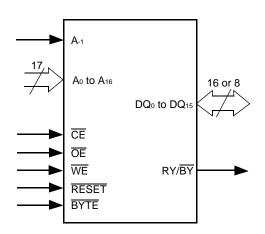

#### ■ LOGIC SYMBOL

| Pin            | Function                                             |

|----------------|------------------------------------------------------|

| A-1, A0 to A16 | Address Inputs                                       |

| DQ0 to DQ15    | Data Inputs/Outputs                                  |

| CE             | Chip Enable                                          |

| ŌE             | Output Enable                                        |

| WE             | Write Enable                                         |

| RY/BY          | Ready-Busy Output                                    |

| RESET          | Hardware Reset Pin/<br>Temporary Sector Unprotection |

| BYTE           | Selects 8-bit or 16-bit mode                         |

| N.C.           | No Internal Connection                               |

| Vss            | Device Ground                                        |

| Vcc            | Device Power Supply                                  |

#### Table 1 MBM29F200TC/BC Pin Configuration

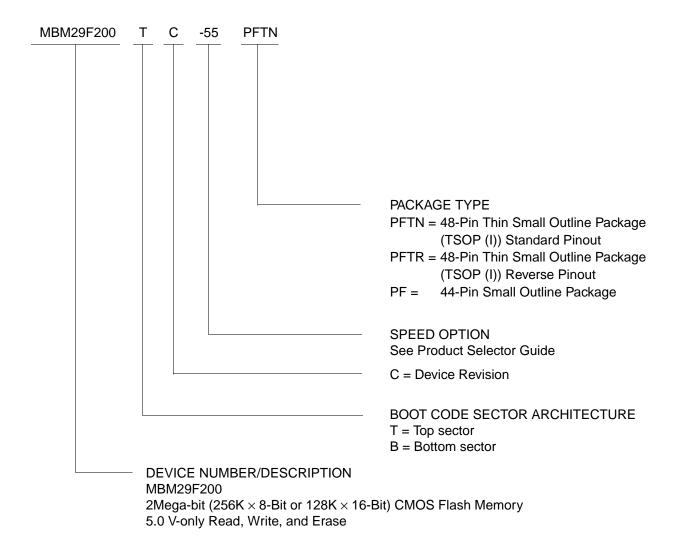

#### ORDERING INFORMATION

#### **Standard Products**

Fujitsu standard products are available in several packages. The order number is formed by a combination of:

| Operation                         | CE | ŌĒ  | WE | Ao | <b>A</b> 1     | A <sub>6</sub> | A۹  | DQ₀ to<br>DQ15 | RESET |

|-----------------------------------|----|-----|----|----|----------------|----------------|-----|----------------|-------|

| Auto-Select Manufacturer Code (1) | L  | L   | Н  | L  | L              | L              | Vid | Code           | Н     |

| Auto-Select Device Code (1)       | L  | L   | Н  | Н  | L              | L              | Vid | Code           | Н     |

| Read (3)                          | L  | L   | Н  | Ao | A <sub>1</sub> | A <sub>6</sub> | A9  | Dout           | Н     |

| Standby                           | Н  | Х   | Х  | Х  | Х              | Х              | Х   | HIGH-Z         | Н     |

| Output Disable                    | L  | Н   | Н  | Х  | Х              | Х              | Х   | HIGH-Z         | Н     |

| Write                             | L  | Н   | L  | Ao | <b>A</b> 1     | A <sub>6</sub> | A9  | DIN            | Н     |

| Enable Sector Protection (2)      | L  | Vid | T  | L  | Н              | L              | Vid | Х              | Н     |

| Verify Sector Protection (2)      | L  | L   | Н  | L  | Н              | L              | Vid | Code           | Н     |

| Temporary Sector Unprotection     | Х  | Х   | Х  | Х  | Х              | Х              | Х   | Х              | Vid   |

| Reset (Hardware)/Standby          | Х  | Х   | Х  | Х  | Х              | Х              | Х   | HIGH-Z         | L     |

#### Table 2 MBM29F200TC/BC User Bus Operation (BYTE = VIH)

Table 3 MBM29F200TC/BC User Bus Operation (BYTE = VIL)

| Operation                         | CE | ŌE  | WE | DQ15<br>/A-1 | A٥ | <b>A</b> 1     | A <sub>6</sub> | A۹  | DQ <sub>0</sub> to DQ <sub>7</sub> | RESET |

|-----------------------------------|----|-----|----|--------------|----|----------------|----------------|-----|------------------------------------|-------|

| Auto-Select Manufacturer Code (1) | L  | L   | Н  | L            | L  | L              | L              | Vid | Code                               | Н     |

| Auto-Select Device Code (1)       | L  | L   | Н  | L            | Н  | L              | L              | Vid | Code                               | Н     |

| Read (3)                          | L  | L   | Н  | <b>A</b> -1  | Ao | A <sub>1</sub> | A <sub>6</sub> | A9  | Dout                               | Н     |

| Standby                           | н  | Х   | Х  | Х            | Х  | Х              | Х              | Х   | HIGH-Z                             | Н     |

| Output Disable                    | L  | н   | Н  | Х            | Х  | Х              | Х              | Х   | HIGH-Z                             | Н     |

| Write                             | L  | н   | L  | <b>A</b> -1  | Ao | A <sub>1</sub> | A <sub>6</sub> | A9  | DIN                                | Н     |

| Enable Sector Protection (2)      | L  | Vid |    | L            | L  | Н              | L              | Vid | Х                                  | Н     |

| Verify Sector Protection (2)      | L  | L   | Н  | L            | L  | Н              | L              | Vid | Code                               | Н     |

| Temporary Sector Unprotection     | Х  | Х   | Х  | Х            | Х  | Х              | Х              | Х   | Х                                  | Vid   |

| Reset (Hardware)/Standby          | Х  | Х   | Х  | Х            | Х  | Х              | Х              | Х   | HIGH-Z                             | L     |

**Legend:**  $L = V_{IL}$ ,  $H = V_{IH}$ ,  $X = V_{IL}$  or  $V_{IH}$ ,  $\neg\_ r$  = Pulse input. See DC Characteristics for voltage levels.

- **Notes:** 1. Manufacturer and device codes may also be accessed via a command register write sequence. Refer to Table 7.

- 2. Refer to the section on Sector Protection.

- 3. WE can be V<sub>IL</sub> if  $\overline{OE}$  is V<sub>IL</sub>,  $\overline{OE}$  at V<sub>IH</sub> initiates the write operations.

#### FUNCTIONAL DESCRIPTION

#### **Read Mode**

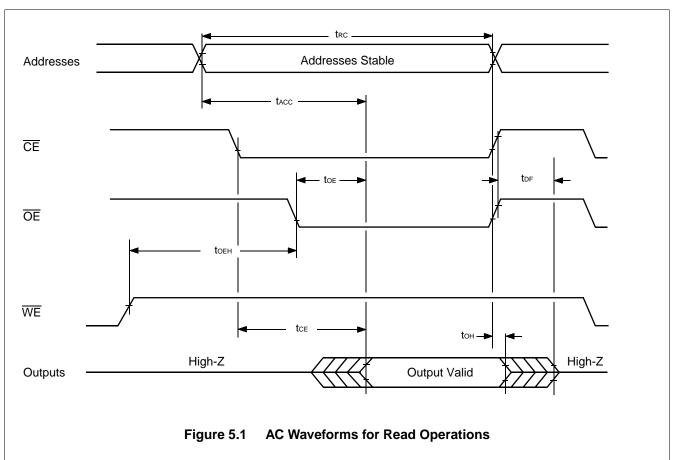

The MBM29F200TC/BC has two control functions which must be satisfied in order to obtain data at the outputs.  $\overline{CE}$  is the power control and should be used for a device selection.  $\overline{OE}$  is the output control and should be used to gate data to the output pins if a device is selected.

Address access time (t<sub>ACC</sub>) is equal to the delay from stable addresses to valid output data. The chip enable access time (t<sub>CE</sub>) is the delay from stable addresses and stable  $\overline{CE}$  to valid data at the output pins. The output enable access time is the delay from the falling edge of  $\overline{OE}$  to valid data at the output pins (Assuming the addresses have been stable for at least t<sub>ACC</sub> - t<sub>CE</sub> time).

#### Standby Mode

There are two ways to implement the standby mode on the MBM29F200TC/BC devices, one using both the  $\overline{CE}$  and  $\overline{RESET}$  pins; the other via the  $\overline{RESET}$  pin only.

When using both pins, a CMOS standby mode is achieved with  $\overline{CE}$  and  $\overline{RESET}$  inputs both held at  $V_{CC} \pm 0.3$  V. Under this condition the current consumed is less than 5  $\mu$ A max. A TTL standby mode is achieved with  $\overline{CE}$  and  $\overline{RESET}$  pins held at V<sub>IH</sub>. Under this condition the current is reduced to approximately 1mA. During Embedded Algorithm operation, V<sub>CC</sub> Active current (I<sub>CC2</sub>) is required even  $\overline{CE} = V_{IH}$ . The device can be read with standard access time (t<sub>CE</sub>) from either of these standby modes.

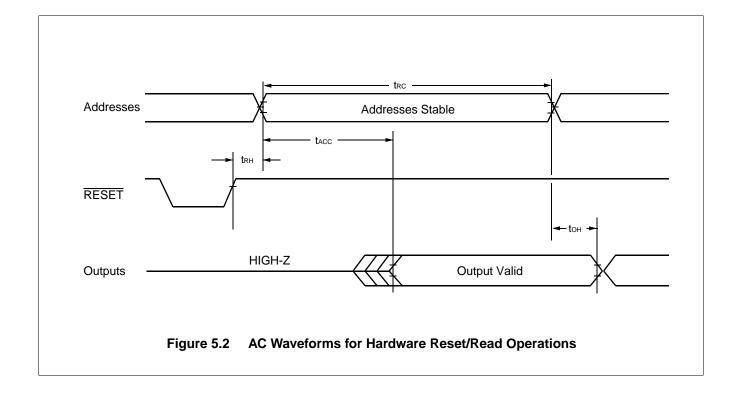

When using the RESET pin only, a CMOS standby mode is achieved with RESET input held at Vss  $\pm$  0.3 V ( $\overline{CE}$  = "H" or "L"). Under this condition the current is consumed is less than 5  $\mu$ A max. A TTL standby mode is achieved with RESET pin held at V<sub>IL</sub>, ( $\overline{CE}$ = "H" or "L"). Under this condition the current required is reduced to approximately 1mA. Once the RESET pin is taken high, the device requires t<sub>RH</sub> of wake up time before outputs are valid for read access.

In the standby mode the outputs are in the high impedance state, independent of the  $\overline{OE}$  input.

#### **Output Disable**

With the  $\overline{OE}$  input at a logic high level (V<sub>H</sub>), output from the device is disabled. This will cause the output pins to be in a high impedance state.

#### Autoselect

The autoselect mode allows the reading out of a binary code from the device and will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the devices to be programmed with its corresponding programming algorithm. This mode is functional over the entire temperature range of the device.

To activate this mode, the programming equipment must force  $V_{ID}$  (11.5 V to 12.5 V) on address pin A<sub>9</sub>. Two identifier bytes may then be sequenced from the devices outputs by toggling address A<sub>0</sub> from  $V_{IL}$  to  $V_{IH}$ . All addresses are don't cares except A<sub>0</sub>, A<sub>1</sub> and A<sub>6</sub> (A<sub>-1</sub>) (See Tables 4.1).

The manufacturer and device codes may also be read via the command register, for instances when the MBM29F200TC/BC is erased or programmed in a system without access to high voltage on the  $A_9$  pin. The command sequence is illustrated in Table 7 (refer to Autoselect Command section).

$A_0 = V_{IL}$  represents the manufacturer's code (Fujitsu = 04H) and  $A_0 = V_{IH}$  the device identifier code (MBM29F200TC =51H and MBM29F200BC = 57H for ×8 mode; MBM29F200TC = 2251H and MBM29F200BC = 2257H for ×16 mode). These two bytes/words are given in the tables 4.1 and 4.2. All identifiers for manufacturer and device will exhibit odd parity with DQ<sub>7</sub> defined as the parity bit. In order to read the proper device codes when executing the autoselect, A<sub>1</sub> must be V<sub>IL</sub> (See Tables 4.1 and 4.2).

|                 | Туре            |                     | A12 to A16 | A <sub>6</sub> | <b>A</b> 1 | A٥    | <b>A</b> -1*1 | Code<br>(HEX) |

|-----------------|-----------------|---------------------|------------|----------------|------------|-------|---------------|---------------|

| Manufacturer's  | Code            |                     | Х          | VIL            | VIL        | VIL   | VIL           | 04H           |

|                 | MBM29F200TC     | Byte                | х          | VIL            | VIL        | Mar   | VIL           | 51H           |

| Device Code     | IVIDIVI29F2001C | Word                | ^          | VIL            | VIL        | Vін   | Х             | 2251H         |

| Device Code     | MBM29F200BC     | Byte                | х          | Ma             | VIL        | Maria | VIL           | 57H           |

|                 | WIDIVI29F200BC  | Word                | ^          | VIL            | VIL        | Vін   | Х             | 2257H         |

| Sector Protecti | on              | Sector<br>Addresses | VIL        | Vін            | VIL        | VIL   | 01H*2         |               |

#### Table 4 .1 MBM29F200TC/BC Sector Protection Verify Autoselect Codes

\*1: A<sub>-1</sub> is for Byte mode.

\*2: Outputs 01H at protected sector addresses and outputs 00H at unprotected sector addresses.

|                     | Туре                      | Code             | <b>DQ</b> 15 | <b>DQ</b> 14 | <b>DQ</b> 13 | <b>DQ</b> 12 | <b>DQ</b> 11 | <b>DQ</b> 10 | DQ∍       | DQ8       | DQ<br>7 | $\mathbf{DQ}_{_{6}}$ | $\mathbf{DQ}_{5}$ | DQ<br>4 | DQ<br>3 |        | <b>DQ</b><br>1 | $\mathbf{DQ}_{_{0}}$ |

|---------------------|---------------------------|------------------|--------------|--------------|--------------|--------------|--------------|--------------|-----------|-----------|---------|----------------------|-------------------|---------|---------|--------|----------------|----------------------|

| Manufacturer's Code |                           | 04H              | A-1/0        | 0            | 0            | 0            | 0            | 0            | 0         | 0         | 0       | 0                    | 0                 | 0       | 0       | 1      | 0              | 0                    |

| Device              | MBM29F200TC<br>(B)<br>(W) | 51H<br>2251<br>H | A-1<br>0     | HI-Z<br>0    | HI-Z<br>1    | HI-Z<br>0    | HI-Z<br>0    | HI-Z<br>0    | HI-Z<br>1 | HI-Z<br>0 | 0<br>0  | 1<br>1               | 0<br>0            | 1<br>1  | 0<br>0  | 0<br>0 | 0<br>0         | 1<br>1               |

| Code                | MBM29F200BC<br>(B)<br>(W) | 57H<br>2257<br>H | A-1<br>0     | HI-Z<br>0    | HI-Z<br>1    | HI-Z<br>0    | HI-Z<br>0    | HI-Z<br>0    | HI-Z<br>1 | HI-Z<br>0 | 0<br>0  | 1<br>1               | 0<br>0            | 1       | 0<br>0  | 1<br>1 | 1<br>1         | 1<br>1               |

| Sector Protection   |                           | 01H              | A-1/0        | 0            | 0            | 0            | 0            | 0            | 0         | 0         | 0       | 0                    | 0                 | 0       | 0       | 0      | 0              | 1                    |

Table 4 .2

Expanded Autoselect Code Table

(B): Byte mode

(W): Word mode

#### Write

Device erasure and programming are accomplished via the command register. The contents of the register serve as inputs to the internal state machine. The state machine outputs dictate the function of the device.

The command register itself does not occupy any addressable memory location. The register is a latch used to store the commands, along with the address and data information needed to execute the command. The command register is written by bringing  $\overline{WE}$  to  $V_{IL}$ , while  $\overline{CE}$  is at  $V_{IL}$  and  $\overline{OE}$  is at  $V_{IH}$ . Addresses are latched on the falling edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever happens later; while data is latched on the rising edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever happens first. Standard microprocessor write timings are used.

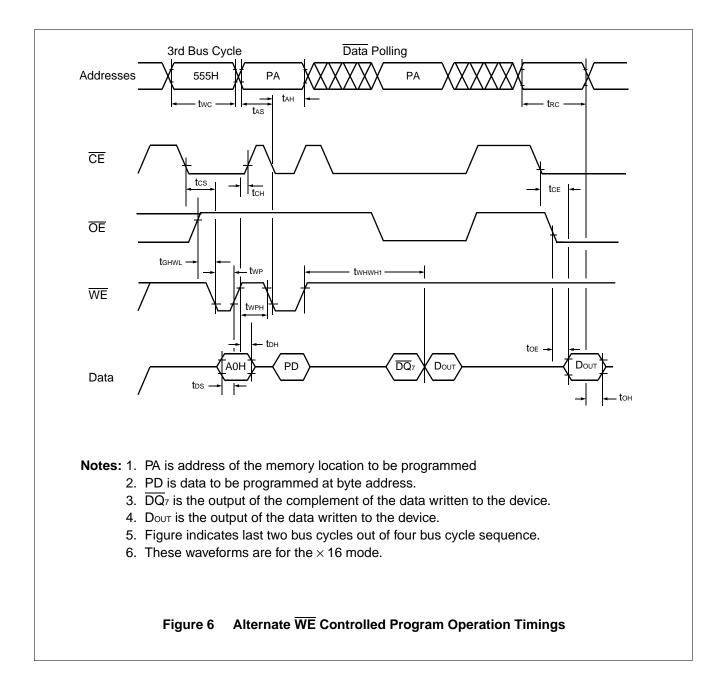

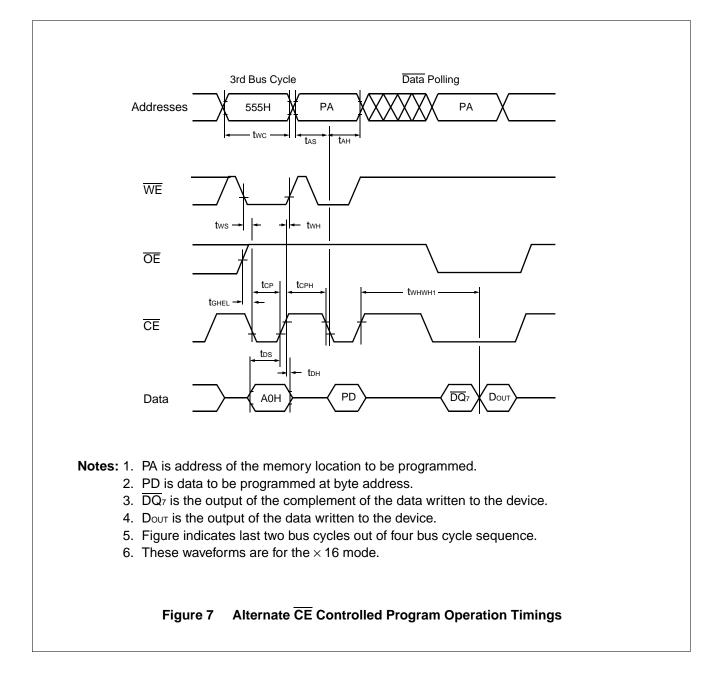

Refer to AC Write Characteristics and the Erase/Programming Waveforms for specific timing parameters.

#### **Sector Protection**

The MBM29F200TC/BC features hardware sector protection. This feature will disable both program and erase operations in any number of sectors (0 through 6). The sector protection feature is enabled using programming equipment at the user's site. The device is shipped with all sectors unprotected.

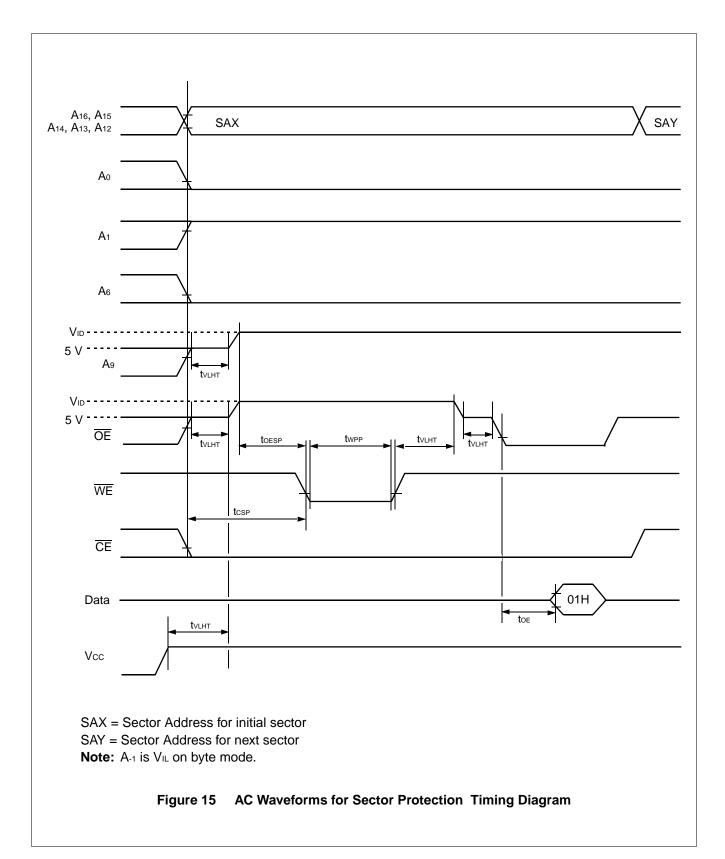

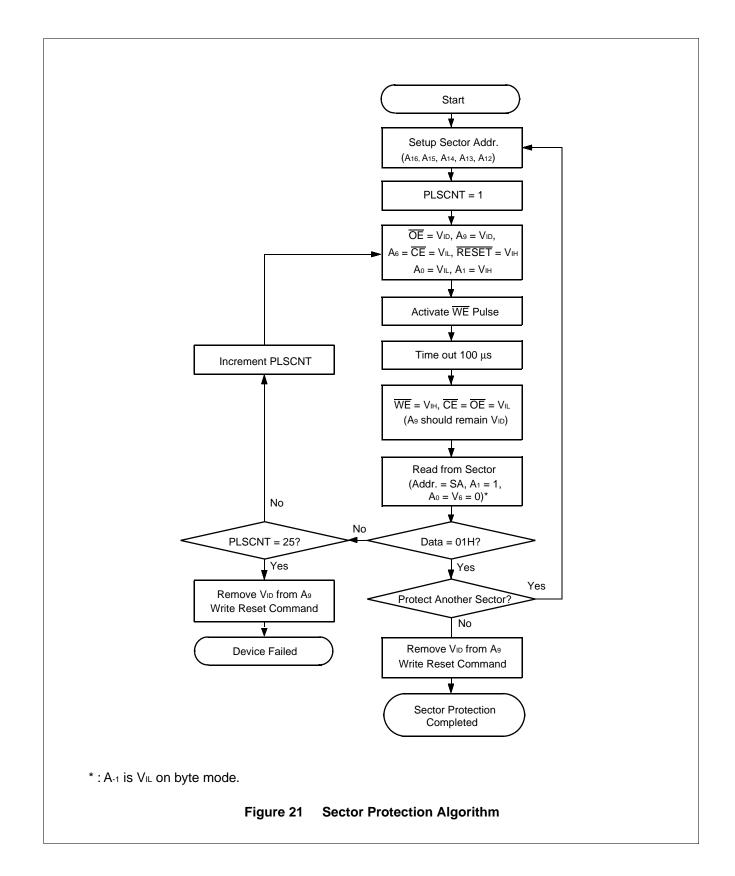

To activate this mode, the programming equipment must force V<sub>ID</sub> on address pin A<sub>9</sub> and control pin  $\overline{OE}$ , (suggest V<sub>ID</sub> = 11.5V),  $\overline{CE} = V_{IL}$ , and A<sub>6</sub> = V<sub>IL</sub>. The sector addresses (A<sub>16</sub>, A<sub>15</sub>, A<sub>14</sub>, A<sub>13</sub>, and A<sub>12</sub>) should be set to the sector to be protected. Tables 5 and 6 define the sector address for each of the seven (7) individual sectors. Programming of the protection circuitry begins on the falling edge of the  $\overline{WE}$  pulse and is terminated with the rising edge of the same. Sector addresses must be held constant during the  $\overline{WE}$  pulse. Refer to Figures 16 and 23 for sector protection waveforms and algorithm.

To verify programming of the protection circuitry, the programming equipment must force  $V_{ID}$  on address pin  $A_9$  with  $\overline{CE}$  and  $\overline{OE}$  at  $V_{IL}$  and  $\overline{WE}$  at  $V_{IH}$ . Scanning the sector addresses (A<sub>16</sub>, A<sub>15</sub>, A<sub>14</sub>, A<sub>13</sub>, and A<sub>12</sub>) while (A<sub>6</sub>, A<sub>1</sub>, A<sub>0</sub>) = (0, 1, 0) will produce a logical "1" code at device output DQ<sub>0</sub> for a protected sector. Otherwise the devices will produce 00H for unprotected sector. In this mode, the lower order addresses, except for A<sub>0</sub>, A<sub>1</sub>, and A<sub>6</sub> are don't care. Address locations with A<sub>1</sub> =  $V_{IL}$  are reserved for Autoselect manufacturer and device codes. A<sub>-1</sub> requires to apply to  $V_{IL}$  on byte mode.

It is also possible to determine if a sector is protected in the system by writing an Autoselect command. Performing a read operation at the address location XX02H, where the higher order addresses ( $A_{16}$ ,  $A_{15}$ ,  $A_{14}$ ,  $A_{13}$ , and  $A_{12}$ ) are the desired sector address will produce a logical "1" at DQ<sub>0</sub> for a protected sector. See Tables 4.1 and 4.2 for Autoselect codes.

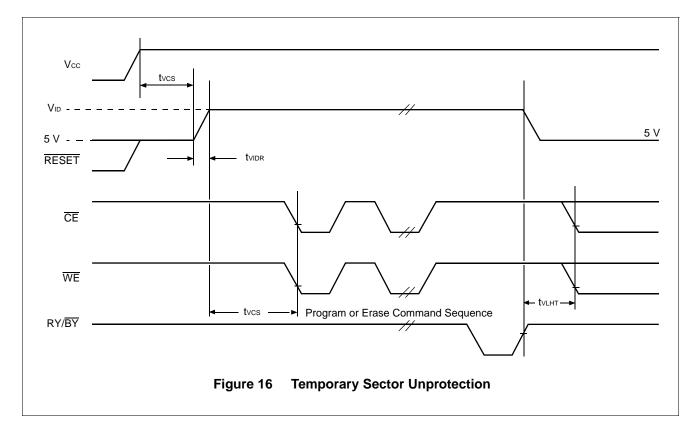

#### **Temporary Sector Unprotection**

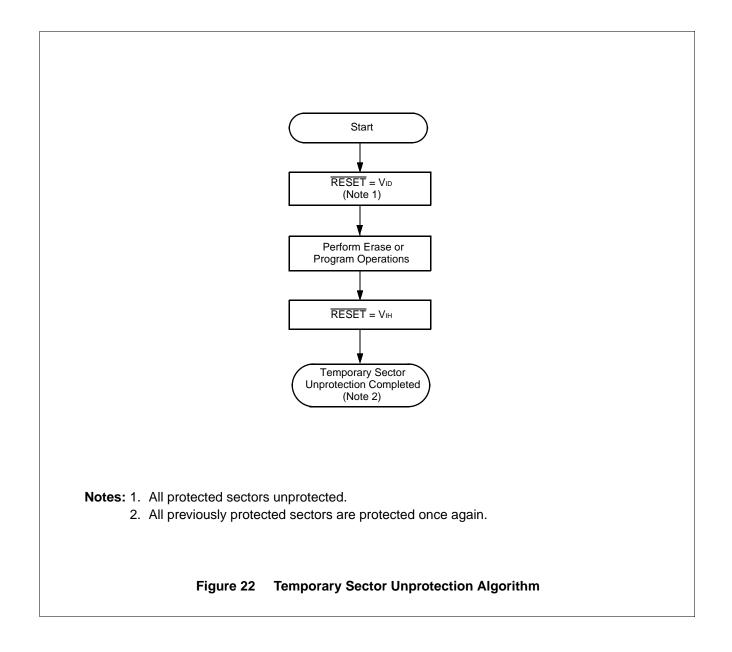

This feature allows temporary unprotection of previously protected sectors of the MBM29F200TC/BC device in order to change data. The Sector Unprotection mode is activated by setting the RESET pin to high voltage (12 V). During this mode, formerly protected sectors can be programmed or erased by selecting the sector addresses. Once the 12 V is taken away from the RESET pin, all the previously protected sectors will be protected again. Refer to Figures 17 and 24.

| Sector<br>Address | <b>A</b> 16 | <b>A</b> 15 | <b>A</b> 14 | <b>A</b> 13 | <b>A</b> 12 | Address Range    |

|-------------------|-------------|-------------|-------------|-------------|-------------|------------------|

| SA0               | 0           | 0           | Х           | Х           | Х           | 00000h to 0FFFFh |

| SA1               | 0           | 1           | Х           | Х           | Х           | 10000h to 1FFFFh |

| SA2               | 1           | 0           | Х           | Х           | Х           | 20000h to 2FFFFh |

| SA3               | 1           | 1           | 0           | Х           | Х           | 30000h to 37FFFh |

| SA4               | 1           | 1           | 1           | 0           | 0           | 38000h to 39FFFh |

| SA5               | 1           | 1           | 1           | 0           | 1           | 3A000h to 3BFFFh |

| SA6               | 1           | 1           | 1           | 1           | Х           | 3C000h to 3FFFFh |

#### Table 5 Sector Address Tables (MBM29F200TC)

|                   |             |             |             | •           |                        | •                |

|-------------------|-------------|-------------|-------------|-------------|------------------------|------------------|

| Sector<br>Address | <b>A</b> 16 | <b>A</b> 15 | <b>A</b> 14 | <b>A</b> 13 | <b>A</b> <sub>12</sub> | Address Range    |

| SA0               | 0           | 0           | 0           | 0           | Х                      | 00000h to 03FFFh |

| SA1               | 0           | 0           | 0           | 1           | 0                      | 04000h to 05FFFh |

| SA2               | 0           | 0           | 0           | 1           | 1                      | 06000h to 07FFFh |

| SA3               | 0           | 0           | 1           | Х           | Х                      | 08000h to 0FFFFh |

| SA4               | 0           | 1           | Х           | Х           | Х                      | 10000h to 1FFFFh |

| SA5               | 1           | 0           | Х           | Х           | Х                      | 20000h to 2FFFFh |

| SA6               | 1           | 1           | Х           | Х           | Х                      | 30000h to 3FFFFh |

#### Table 6 Sector Address Tables (MBM29F200BC)

| Command W<br>Sequence C                                                                   |       | Bus<br>Write<br>Cycles<br>Req'd | First<br>Write | Bus<br>Cycle | Seco<br>Bu<br>Write | IS     | Third<br>Write | Third Bus<br>Write Cycle |          | Fourth Bus<br>Read/Write<br>Cycle |           | Fifth Bus<br>Write Cycle |          | Bus<br>Cycle |

|-------------------------------------------------------------------------------------------|-------|---------------------------------|----------------|--------------|---------------------|--------|----------------|--------------------------|----------|-----------------------------------|-----------|--------------------------|----------|--------------|

| -                                                                                         |       |                                 | Addr           | Data         | Addr                | Data   | Addr           | Data                     | Addr     | Data                              | Addr      | Data                     | Addr     | Data         |

| Read/Reset                                                                                | Word  | 1                               | хххн           | F0H          |                     |        |                |                          |          |                                   |           |                          |          |              |

| Reau/Resei                                                                                | Byte  |                                 | лллп           | гоп          |                     |        | _              |                          |          | _                                 |           |                          |          | _            |

| Read/Reset                                                                                | Word  | 3                               | 555H           | ААН          | 2AAH                | 55H    | 555H           | F0H                      | RA       | RD                                |           |                          |          |              |

| Reau/Reset                                                                                | Byte  | 5                               | AAAH           | AAH          | 555H                | 5511   | AAAH           | гоп                      | ΓA       | ΝD                                |           |                          |          | _            |

| Autoselect                                                                                | Word  | 3                               | 555H           | AAH          | 2AAH                | 55H    | 555H           | 90H                      |          |                                   |           |                          |          |              |

| Autoselect                                                                                | Byte  | 5                               | AAAH           | AAH          | 555H                | 5511   | AAAH           | 0011                     |          |                                   |           |                          |          |              |

| Program                                                                                   | Word  | 4                               | 555H           | AAH          | 2AAH                | 55H    | 555H           | A0H                      | PA       | PD                                |           |                          |          |              |

| Filogram                                                                                  | Byte  | -                               | AAAH           |              | 555H                | 5511   | AAAH           | AULI                     |          | FD                                |           |                          |          |              |

| Chip Erase                                                                                | Word  | 6                               | 555H           | AAH          | 2AAH                | 55H    | 555H           | 80H                      | 555H     | ААН                               | 2AAH      | 55H                      | 555H     | 10H          |

| Chip Elase                                                                                | Byte  | 0                               | AAAH           | AAH          | 555H                | 5511   | AAAH           | 0011                     | AAAH     | AAH                               | 555H      | 5511                     | AAAH     | TUL          |

| Sector                                                                                    | Word  | 6                               | 555H           | AAH          | 2AAH                | 55H    | 555H           | 80H                      | 555H     | ААН                               | 2AAH      | 55H                      | SA       | 30H          |

| Erase                                                                                     | Byte  | 0                               | AAAH           | AAH          | 555H                | 5511   | AAAH           | 0011                     | AAAH     | AAH                               | 555H      | 5511                     | SA       | 3011         |

| Sector Erase                                                                              | Suspe | end                             | Erase          | can be       | suspen              | ded du | uring se       | ctor er                  | ase with | Addr                              | ("H" or ' | 'L"). Da                 | ata (B0F | I)           |

| Sector Erase Resume Erase can be resumed after suspend with Addr ("H" or "L"). Data (30H) |       |                                 |                |              |                     |        |                | )                        |          |                                   |           |                          |          |              |

#### Table 7 MBM29F200TC/BC Command Definitions

- **Notes:** 1. Address bits A<sub>16</sub> to A<sub>11</sub> = X = "H" or "L" for all address commands except or Program Address (PA) and Sector Address (SA).

- 2. Bus operations are defined in Tables 2 and 3.

- 3. RA = Address of the memory location to be read.

- PA = Address of the memory location to be programmed. Addresses are latched on the falling edge of the WE pulse.

- SA = Address of the sector to be erased. The combination of A<sub>16</sub>, A<sub>15</sub>, A<sub>14</sub>, A<sub>13</sub>, and A<sub>12</sub> will uniquely select any sector.

- 4. RD = Data read from location RA during read operation.

- PD = Data to be programmed at location PA. Data is latched on the falling edge of  $\overline{WE}$ .

- 5. The system should generate the following address patterns: Word Mode: 555H or 2AAH to addresses A<sub>0</sub> to A<sub>10</sub>

Byte Mode: AAAH or 555H to addresses A-1 to A10

6. Both Read/Reset commands are functionally equivalent, resetting the device to the read mode.

#### **Command Definitions**

Device operations are selected by writing specific address and data sequences into the command register. Writing incorrect address and data values or writing them in the improper sequence will reset the device to the read mode. Table 7 defines the valid register command sequences. Note that the Erase Suspend (BOH) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress. Moreover both Read/Reset commands are functionally equivalent, resetting the device to the read mode. Please note that commands are always written at DQ<sub>0</sub> to DQ<sub>7</sub> and DQ<sub>8</sub> to DQ<sub>15</sub> bits are ignored.

#### **Read/Reset Command**

The read or eset operation is initiated by writing the read/reset command sequence into the command register. Microprocessor read cycles retrieve array data from the memory. The devices remain enabled for reads until the command register contents are altered. The device will automatically power-up in the read/reset state. In this case, a command sequence is not required to read data. Standard microprocessor read cycles will retrieve array data. This default value ensures that no spurious alteration of the memory content occurs during the power transition. Refer to the AC Read Characteristics and Waveforms for the specific timing parameters.

#### **Autoselect Command**

Flash memories are intended for use in applications where the local CPU alters memory contents. As such, manufacture and device codes must be accessible while the devices reside in the target system. PROM programmers typically access the signature codes by raising A<sub>9</sub> to a high voltage. However, multiplexing high voltage onto the address lines is not generally desired system design practice.

The device contains an autoselect command operation to supplement traditional PROM programming methodology. The operation is initiated by writing the autoselect command sequence into the command register. Following the command write, a read cycle from address XX00H retrieves the manufacture code of 04H. A read cycle from address XX01H for ×16 (XX02H for ×8) returns the device code (MBM29F200TC = 51H and MBM29F200BC = 57H for ×8 mode; MBM29F200TC = 2251H and MBM29F200BC = 2257H for ×16 mode). (See Tables 4.1 and 4.2.)

All manufacturer and device codes will exhibit odd parity with  $DQ_7$  defined as the parity bit. Scanning the sector addresses (A<sub>16</sub>, A<sub>15</sub>, A<sub>14</sub>, A<sub>13</sub>, and A<sub>12</sub>) while (A<sub>6</sub>, A<sub>1</sub>, A<sub>0</sub>) = (0, 1, 0) will produce a logical "1" at device output  $DQ_0$  for a protected sector. The programming verification should be perform margin mode on the protected sector (See Tables 2 and 3).

To terminate the operation, it is necessary to write the read/reset command sequence into the register and also to write the autoselect command during the operation, execute it after writing read/reset command sequence.

#### **Byte/Word Programming**

The device is programmed on a byte-by-byte (or word-by-word) basis. Programming is a four bus cycle operation. There are two "unlock" write cycles. These are followed by the program set-up command and data write cycles. Addresses are latched on the falling edge of  $\overline{CE}$  or  $\overline{WE}$ , whichever happens later and the data is latched on the rising edge of  $\overline{CE}$  or  $\overline{WE}$ , whichever happens later and the data is latched on the rising edge of  $\overline{CE}$  or  $\overline{WE}$ , whichever happens first) begins programming. Upon executing the Embedded Program<sup>TM</sup> Algorithm command sequence the system is not required to provide further controls or timings. The device will automatically provide adequate internally generated program pulses and verify the programmed cell margin.

The automatic programming operation is completed when the data on DQ<sub>7</sub> is equivalent to data written to this bit at which time the devices return to the read mode and addresses are no longer latched (see Table 8, Hardware Sequence Flags) Therefore, the devices require that a valid address to the devices be supplied by the system at this particular instance of time. Hence, Data Polling must be performed at the memory location which is being programmed.

Any commands written to the chip during this period will be ignored. If hardware reset occurs during the programming operation, it is impossible to guarantee the data are being written.

Programming is allowed in any sequence and across sector boundaries. Beware that a data "0" cannot be programmed back to a "1". Attempting to do so may either hang up the device or result in an apparent success according to the data polling algorithm but a read from read/reset mode will show that the data is still "0". Only erase operations can convert "0"s to "1"s.

Figure 19 illustrates the Embedded Programming Algorithm using typical command strings and bus operations.

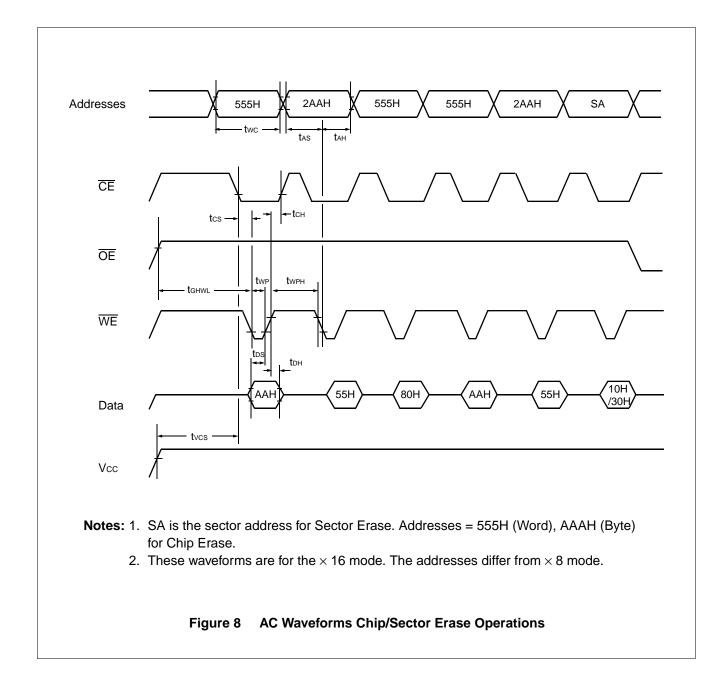

#### Chip Erase

Chip erase is a six bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command. Two more "unlock" write cycles are then followed by the chip erase command.

Chip erase does not require the user to program the device prior to erase. Upon executing the Embedded Erase<sup>™</sup> Algorithm command sequence the device will automatically program and verify the entire memory for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or timings during these operations.

The automatic erase begins on the rising edge of the last  $\overline{WE}$  pulse in the command sequence and terminates when the data on DQ<sub>7</sub> is "1" (see Write Operation Status section) at which time the device returns to read the mode.

Figure 20 illustrates the Embedded Erase Algorithm using typical command strings and bus operations.

#### Sector Erase

Sector erase is a six bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command. Two more "unlock" write cycles are then followed by the sector erase command. The sector address (any address location within the desired sector) is latched on the falling edge of  $\overline{WE}$ , while the command (Data = 30H) is latched on the rising edge of  $\overline{WE}$ . After time-out of 50 µs from the rising edge of the last sector erase command, the sector erase operation will begin.

Multiple sectors may be erased concurrently by writing the six bus cycle operations on Table 7. This sequence is followed with writes of the Sector Erase command to addresses in other sectors desired to be concurrently erased. The time between writes must be less than 50  $\mu$ s otherwise that command will not be accepted and erasure will start. It is recommended that processor interrupts be disabled during this time to guarantee this condition. The interrupts can be re-enabled after the last Sector Erase command is written. A time-out of 50  $\mu$ s from the rising edge of the last  $\overline{WE}$  will initiate the execution of the Sector Erase command(s). If another falling edge of the  $\overline{WE}$  occurs within the 50  $\mu$ s time-out window the timer is reset. (Monitor DQ<sub>3</sub> to determine if the sector erase timer window is still open, see section DQ<sub>3</sub>, Sector Erase Timer.) Any command other than Sector Erase or Erase Suspend during this time-out period will reset the devices to the read mode, ignoring the previous command string. Resetting the device once execution has begun will corrupt the data in that sector. In that case, restart the erase on those sectors and allow them to complete. (Refer to the Write Operation Status section for Sector Erase Timer operation.) Loading the sector erase buffer may be done in any sequence and with any number of sectors (0 to 6).

Sector erase does not require the user to program the devices prior to erase. The device automatically programs all memory locations in the sector(s) to be erased prior to electrical erase. When erasing a sector or sectors the remaining unselected sectors are not affected. The system is not required to provide any controls or timings during these operations.

The automatic sector erase begins after the 50  $\mu$ s time out from the rising edge of the WE pulse for the last sector erase command pulse and terminates when the data on DQ<sub>7</sub> is "1" (see Write Operation Status section) at which time the device returns to the read mode. Data polling must be performed at an address within any of the sectors being erased.

Figure 20 illustrates the Embedded Erase Algorithm using typical command strings and bus operations.

#### Erase Suspend

The Erase Suspend command allows the user to interrupt a Sector Erase operation and then perform data reads from or programs to a sector not being erased. This command is applicable ONLY during the Sector Erase operation which includes the time-out period for sector erase. The Erase Suspend command will be ignored if written during the Chip Erase operation or Embedded Program Algorithm. Writting the Erase Suspend command during the Sector Erase time-out results in immediate termination of the time-out period and suspension of the erase operation.

Writing the Erase Resume command resumes the erase operation. The addresses are "don't cares" when writing the Erase Suspend or Erase Resume command.

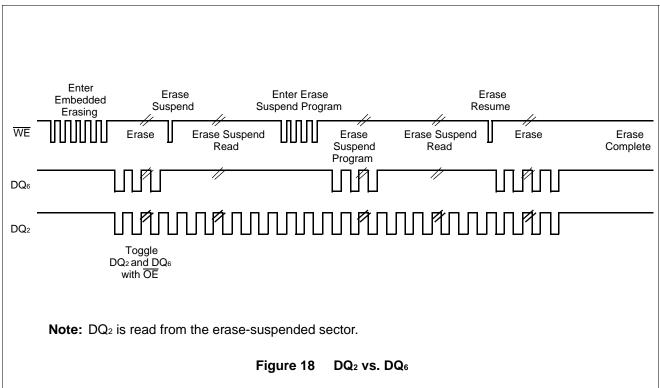

When the Erase Suspend command is written during the Sector Erase operation, the device will take a maximum of 20  $\mu$ s to suspend the erase operation. When the device has entered the erase-suspended mode, the RY/BY output pin and the DQ7 bit will be at logic "1", and DQ6 will stop toggling. The user must use the address of the erasing sector for reading DQ6 and DQ7 to determine if the erase operation has been suspended. Further writes of the Erase Suspend command are ignored.

When the erase operation has been suspended, the device defaults to the erase-suspend-read mode. Reading data in this mode is the same as reading from the standard read mode except that the data must be read from sectors that have not been erase-suspended. Successively reading from the erase-suspended sector while the device is in the erase-suspend-read mode will cause DQ<sub>2</sub> to toggle. (See the section on DQ<sub>2</sub>).

After entering the erase-suspend-read mode, the user can program the device by writing the appropriate command sequence for Program. This program mode is known as the erase-suspend-program mode. Again, programming in this mode is the same as programming in the regular Program mode except that the data must be programmed to sectors that are not erase-suspended. Successively reading from the erase-suspended sector while the device is in the erase-suspend-program mode will cause DQ<sub>2</sub> to toggle. The end of the erase-suspended program operation is detected by the RY/BY output pin, Data polling of DQ<sub>7</sub>, or by the Toggle Bit I (DQ<sub>6</sub>) which is the same as the regular Program operation. Note that DQ<sub>7</sub> must be read from the program address while DQ<sub>6</sub> can be read from any address.

To resume the operation of Sector Erase, the Resume command (30H) should be written. Any further writes of the Resume command at this point will be ignored. Another Erase Suspend command can be written after the chip has resumed erasing.

#### Write Operation Status

|                |                            | Status                                                | DQ7               | $DQ_6$             | DQ₅  | DQ₃  | DQ <sub>2</sub> |

|----------------|----------------------------|-------------------------------------------------------|-------------------|--------------------|------|------|-----------------|

|                | Embedded P                 | rogram Algorithm                                      | DQ <sub>7</sub>   | Toggle             | 0    | 0    | 1               |

|                | Embedded E                 | rase Algorithm                                        | 0                 | Toggle             | 0    | 1    | Toggle          |

| In             |                            | Erase Suspend Read (Erase Suspended Sector)           | 1                 | 1                  | 0    | 0    | Toggle          |

| Progress       | Erase<br>Suspended<br>Mode | Erase Suspend Read (Non-Erase<br>Suspended Sector)    | Data              | Data               | Data | Data | Data            |

|                |                            | Erase Suspend Program (Non-Erase<br>Suspended Sector) | $\overline{DQ}_7$ | Toggle<br>(Note 1) | 0    | 0    | 1<br>(Note 2)   |

|                | Embedded P                 | rogram Algorithm                                      | DQ <sub>7</sub>   | Toggle             | 1    | 0    | 1               |

| Exceeded       | Embedded E                 | rase Algorithm                                        | 0                 | Toggle             | 1    | 1    | N/A             |

| Time<br>Limits | Erase<br>Suspended<br>Mode | Erase Suspend Program (Non-Erase<br>Suspended Sector) | DQ7               | Toggle             | 1    | 0    | N/A             |

#### Table 8 Hardware Sequence Flags

Notes: 1. Performing successive read operations from any address will cause DQ6 to toggle.

- Reading the byte address being programmed while in the erase-suspend program mode will indicate logic "1" at the DQ<sub>2</sub> bit. However, successive reads from the erase-suspended sector will cause DQ<sub>2</sub> to toggle.

- 3.  $DQ_0$  and  $DQ_1$  are reserve pins for future use.  $DQ_4$  is Fujitsu internal use only.

- 4. DQ<sub>8</sub> to DQ<sub>15</sub> are "DON'T CARES" because there is for  $\times$  16 mode.

#### DQ7

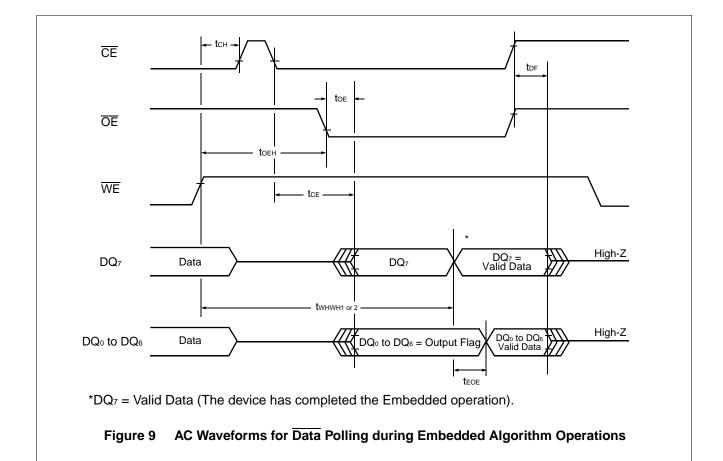

#### Data Polling

The MBM29F200TC/BC device feature Data Polling as a method to indicate to the host that the Embedded Algorithms are in progress or completed. During the Embedded Program Algorithm an attempt to read the device will produce the complement of the data last written to DQ<sub>7</sub>. Upon completion of the Embedded Program Algorithm, an attempt to read the device will produce the true data last written to DQ<sub>7</sub>. During the Embedded Erase Algorithm, an attempt to read the device will produce a "0" at the DQ<sub>7</sub> output. Upon completion of the Embedded Erase Algorithm an attempt to read the device will produce a "1" at the DQ<sub>7</sub> output. The flowchart for Data Polling (DQ<sub>7</sub>) is shown in Figure 21.

For Programing, the Data Polling is valid after the rising edge of fourth write pulse in the four write pulse sequence.

For chip erase and sector erase, the Data Polling is valid after the rising edge of the sixth write pulse in the six write pulse sequence. Data Polling must be performed at sector address within any of the sectors being erased and not a protected sector. Otherwise, the status may not be valid. Once the Embedded Algorithm operation is close to being completed, the MBM29F200TC/BC data pins (DQ<sub>7</sub>) may change asynchronously while the output enable ( $\overline{OE}$ ) is asserted low. This means that the device is driving status information on DQ<sub>7</sub> at one instant of time and then that byte's valid data at the next instant of time. Depending on when the system samples the DQ<sub>7</sub> output, it may read the status or valid data. Even if the device has completed the Embedded Algorithm operation and DQ<sub>7</sub> has a valid data, the data outputs on DQ<sub>0</sub> to DQ<sub>6</sub> may be still invalid. The valid data on DQ<sub>0</sub> to DQ<sub>7</sub> will be read on the successive read attempts.

The Data Polling feature is only active during the Embedded Programming Algorithm, Embedded Erase Algorithm or sector erase time-out (See Table 8).

See Figure 9 for the Data Polling timing specifications and diagrams.

#### DQ<sub>6</sub>

#### Toggle Bit I

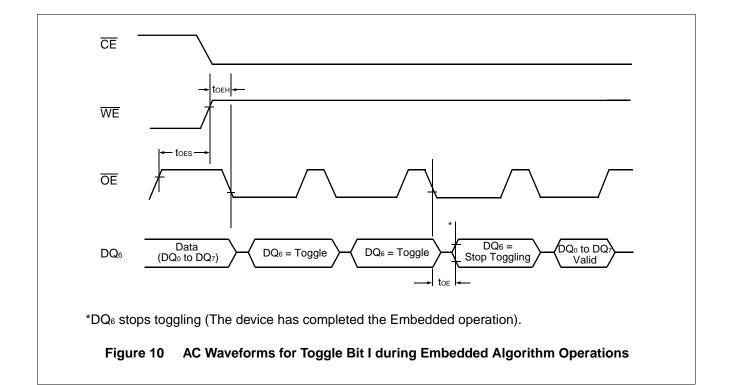

The MBM29F200TC/BC also feature the "Toggle Bit I" as a method to indicate to the host system that the Embedded Algorithms are in progress or completed.

During an Embedded Program or Erase Algorithm cycle, successive attempts to read ( $\overline{OE}$  toggling) data from the device will result in DQ<sub>6</sub> toggling between one and zero. Once the Embedded Program or Erase Algorithm cycle is completed, DQ<sub>6</sub> will stop toggling and valid data will be read on the next successive attempts. During programming, the Toggle Bit I is valid after the rising edge of the fourth write pulse in the four write pulse sequence. For chip erase and sector erase, the Toggle Bit I is valid after the rising edge of the sixth write pulse in the six write pulse sequence. The Toggle Bit I is active during the sector time out.

In programming, if the sector being written to is protected, the toggle bit I will toggle for about 2  $\mu$ s and then stop toggling without the data having changed. In erase, the device will erase all the selected sectors except for the ones that are protected. If all selected sectors are protected, the chip will toggle the toggle bit for about 100  $\mu$ s and then drop back into read mode, having changed none of the data.

Either  $\overline{CE}$  or  $\overline{OE}$  toggling will cause the DQ<sub>6</sub> to toggle. In addition, an Erase Suspend/Resume command will cause DQ<sub>6</sub> to toggle.

See Figure 10 for the Toggle Bit I timing specifications and diagrams.

#### DQ₅

#### **Exceeded Timing Limits**

$DQ_5$  will indicate if the program or erase time has exceeded the specified limits (internal pulse count). Under these conditions  $DQ_5$  will produce a "1". This is a failure condition which indicates that the program or erase cycle was not successfully completed. Data Polling is the only operating function of the devices under this condition. The  $\overline{CE}$  circuit will partially power down the device under these conditions (to approximately 2 mA). The  $\overline{OE}$  and  $\overline{WE}$  pins will control the output disable functions as described in Tables 2 and 3. The DQ<sub>5</sub> failure condition may also appear if a user tries to program a non blank location without erasing. In this case the device locks out and never complete the Embedded Algorithm operation. Hence, the system never reads a valid data on DQ<sub>7</sub> bit and DQ<sub>6</sub> never stops toggling. Once the device has exceeded timing limits, the DQ<sub>5</sub> bit will indicate a "1." Please note that this is not a device failure condition since the device was incorrectly used.

#### DQ₃

#### Sector Erase Timer

After the completion of the initial sector erase command sequence the sector erase time-out will begin. DQ<sub>3</sub> will remain low until the time-out is complete. Data Polling and Toggle Bit are valid after the initial sector erase command sequence.

If Data Polling or the Toggle Bit I indicates the device has been written with a valid erase command,  $DQ_3$  may be used to determine if the sector erase timer window is still open. If  $DQ_3$  is high ("1") the internally controlled erase cycle has begun; attempts to write subsequent commands to the device will be ignored until the erase operation is completed as indicated by Data Polling or Toggle Bit I. If  $DQ_3$  is low ("0"), the device will accept additional sector erase commands. To insure the command has been accepted, the system software should check the status of  $DQ_3$  prior to and following each subsequent sector erase command. If  $DQ_3$  were high on the second status check, the command may not have been accepted.

Refer to Table 8: Hardware Sequence Flags.

#### DQ<sub>2</sub>

#### Toggle Bit II

This toggle bit II, along with DQ<sub>6</sub>, can be used to determine whether the device is in the Embedded Erase Algorithm or in Erase Suspend.

Successive reads from the erasing sector will cause  $DQ_2$  to toggle during the Embedded Erase Algorithm. If the device is in the erase-suspended-read mode, successive reads from the erase-suspended sector will cause  $DQ_2$  to toggle. When the device is in the erase-suspended-program mode, successive reads from the byte address of the non-erase suspended sector will indicate a logic "1" at the  $DQ_2$  bit.

$DQ_6$  is different from  $DQ_2$  in that  $DQ_6$  toggles only when the standard program or Erase, or Erase Suspend Program operation is in progress. The behavior of these two status bits, along with that of  $DQ_7$ , is summarized as follows:

| Mode                                                       | DQ7             | DQ <sub>6</sub> | DQ <sub>2</sub> |

|------------------------------------------------------------|-----------------|-----------------|-----------------|

| Program                                                    | DQ <sub>7</sub> | toggles         | 1               |

| Erase                                                      | 0               | toggles         | toggles         |

| Erase Suspend Read<br>(Erase-Suspended Sector)<br>(Note 1) | 1               | 1               | toggles         |

| Erase Suspend Program                                      | DQ7 (Note 2)    | toggles         | 1 (Note 2)      |

**Notes:** 1. These status flags apply when outputs are read from a sector that has been erase-suspended.

2. These status flags apply when outputs are read from the byte address of the non-erase suspended sector. For example,  $DQ_2$  and  $DQ_6$  can be used together to determine the erase-suspend-read mode ( $DQ_2$  toggles while  $DQ_6$  does not). See also Table 8 and Figure 22.

Furthermore,  $DQ_2$  can also be used to determine which sector is being erased. When the device is in the erase mode,  $DQ_2$  toggles if this bit is read from the erasing sector.

#### RY/BY

#### Ready/Busy

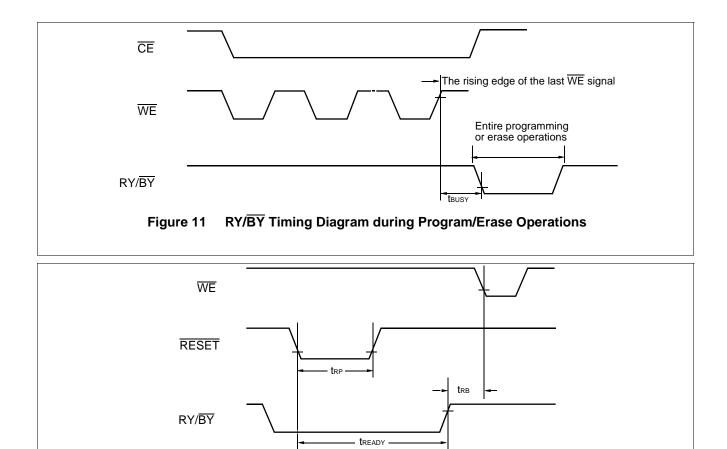

The MBM29F200TC/BC provides a RY/BY open-drain output pin as a way to indicate to the host system that the Embedded<sup>™</sup> Algorithms are either in progress or completed. If the output is low, the device is busy with either a program or erase operation. If the output is high, the device is ready to accept any read/write or erase operation. When the RY/BY pin is low, the device will not accept any additional program or erase commands. If the MBM29F200TC/BC is placed in an Erase Suspend mode, the RY/BY output will be high. Also, since this is an open drain output, many RY/BY pins can be tied together in parallel with a pull up resistor to Vcc.

During programming, the RY/BY pin is driven low after the rising edge of the fourth write pulse. During an erase operation, the RY/BY pin is driven low after the rising edge of the sixth write pulse. The RY/BY pin will indicate a busy condition during the RESET pulse. Refer to Figure 11 and 12 for a detailed timing diagram.

Since this is an open-drain output, several RY/BY pins can be tied together in parallel with a pull-up resistor to Vcc.

#### RESET

#### Hardware Reset

The MBM29F200TC/BC device may be reset by driving the RESET pin to V<sub>IL</sub>. The RESET pin has a pulse requirement and has to be kept low (V<sub>IL</sub>) for at least 500 ns in order to properly reset the internal state machine. Any operation in the process of being executed will be terminated and the internal state machine will be reset to the read mode 20  $\mu$ s after the RESET pin is driven low. Furthermore, once the RESET pin goes high, the device requires time of t<sub>RH</sub> before it will allow read access. When the RESET pin is low, the device will be in the standby mode for the duration of the pulse and all the data output pins will be tri-stated. If a hardware reset occurs during a program or erase operation, the data at that particular location will be corrupted. Please note that the RY/BY output signal should be ignored during the RESET pulse. Refer to Figure 12 for the timing diagram. Refer to Temporary Sector Unprotection for additional functionality.

If hardware reset occurs during Embedded Erase Algorithm, there is a possibility that the erasing sector(s) cannot be used.

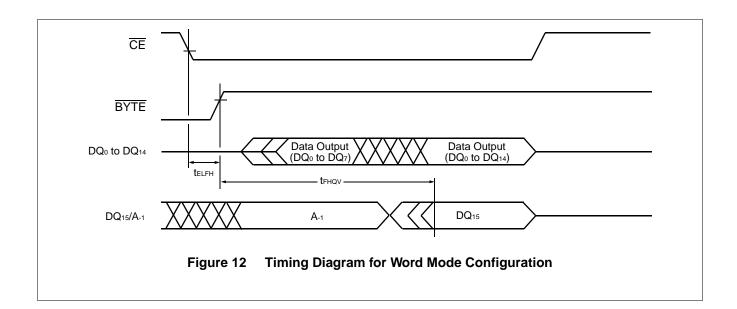

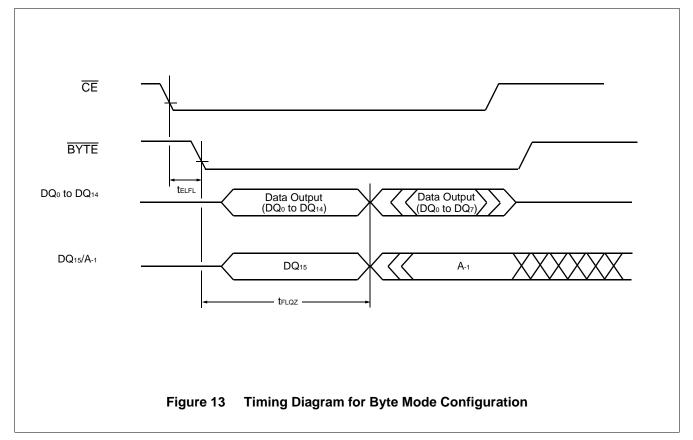

#### **Byte/Word Configuration**

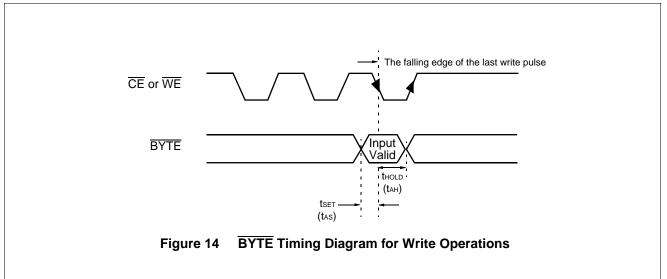

The BYTE pin selects the byte (8-bit) mode or word (16-bit) mode for the MBM29F200TC/BC device. When this pin is driven high, the device operates in the word (16-bit) mode. The data is read and programmed at DQ<sub>0</sub> to DQ<sub>15</sub>. When this pin is driven low, the device operates in byte (8-bit) mode. Under this mode, the DQ<sub>15</sub>/A-1 pin becomes the lowest address bit and DQ<sub>8</sub> to DQ<sub>14</sub> bits are tri-stated. However, the command bus cycle is always an 8-bit operation and hence commands are written at DQ<sub>0</sub> to DQ<sub>7</sub> and the DQ<sub>8</sub> to DQ<sub>15</sub> bits are ignored. Refer to Figures 13, 14 and 15 for the timing diagram.

#### **Data Protection**

The MBM29F200TC/BC are designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transitions. During power up the device automatically resets the internal state machine in the read mode. Also, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific multi-bus cycle command sequences.

The device also incorporate several features to prevent inadvertent write cycles resulting form Vcc power-up and power-down transitions or system noise.

#### Low Vcc Write Inhibit

To avoid initiation of a write cycle during Vcc power-up and power-down, a write cycle is locked out for Vcc less than 3.2 V (typically 3.7 V). If Vcc < VLKO, the command register is disabled and all internal program/erase circuits are disabled. Under this condition the device will reset to the read mode. Subsequent writes will be ignored until the Vcc level is greater than VLKO. It is the users responsibility to ensure that the control pins are logically correct to prevent unintentional writes when Vcc is above 3.2 V.

If Embedded Erase Algorithm is interrupted, there is possibility that the erasing sector(s) cannot be used.

#### Write Pulse "Glitch" Protection

Noise pulses of less than 5 ns (typical) on OE, CE, or WE will not initiate a write cycle.

#### **Logical Inhibit**

Writing is inhibited by holding any one of  $\overline{OE} = V_{\mathbb{H}}$ ,  $\overline{CE} = V_{\mathbb{H}}$ , or  $\overline{WE} = V_{\mathbb{H}}$ . To initiate a write cycle  $\overline{CE}$  and  $\overline{WE}$  must be a logical zero while  $\overline{OE}$  is a logical one.

#### **Power-Up Write Inhibit**

Power-up of the device with  $\overline{WE} = \overline{CE} = V_{IL}$  and  $\overline{OE} = V_{IH}$  will not accept commands on the rising edge of  $\overline{WE}$ . The internal state machine is automatically reset to the read mode on power-up.

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                                                                | –55°C to +125°C   |

|------------------------------------------------------------------------------------|-------------------|

| Ambient Temperature with Power Applied                                             | –40°C to +85°C    |

| Voltage with respect to Ground All pins except A <sub>9</sub> , OE, RESET (Note 1) | –2.0 V to +7.0 V  |

| Vcc (Note 1)                                                                       | –2.0 V to +7.0 V  |

| A9, OE, RESET (Note 2)                                                             | –2.0 V to +13.5 V |

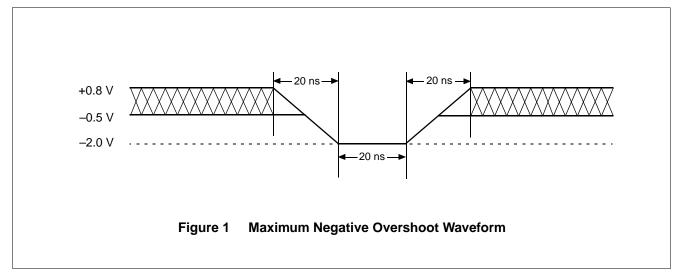

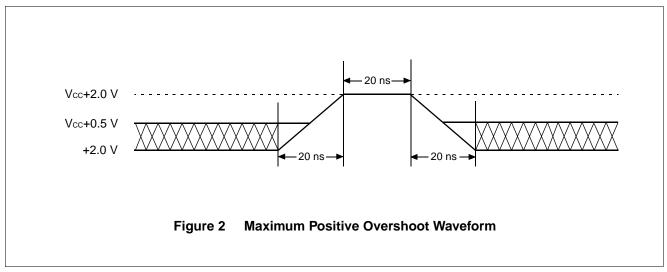

- Notes: 1. Minimum DC voltage on input or I/O pins are -0.5 V. During voltage transitions, inputs may negative overshoot Vss to -2.0 V for periods of up to 20 ns. Maximum DC voltage on output and I/O pins are Vcc +0.5 V. During voltage transitions, outputs may positive overshoot to Vcc +2.0 V for periods of up to 20 ns.

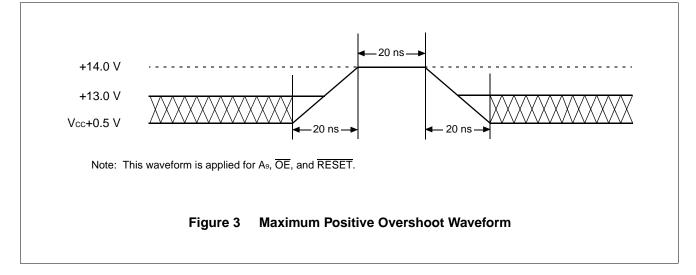

- Minimum DC input voltage on A<sub>9</sub>, OE, RESET pins are –0.5 V. During voltage transitions, A<sub>9</sub>, OE, RESET pins may negative overshoot Vss to –2.0 V for periods of up to 20 ns. Maximum DC input voltage on A<sub>9</sub>, OE, RESET pins are +13.0 V which may positive overshoot to 13.5 V for periods of up to 20 ns. Voltage difference between input voltage and power supply. (V<sub>IN</sub> V<sub>CC</sub>) do not exceed 9 V.

- **WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### RECOMMENDED OPERATING RANGES

. . .

| Commercial Devices    |                    |

|-----------------------|--------------------|

| Ambient Temperatue    | –40°C to +85°C     |

| Vcc Supply Voltages   |                    |

| MBM29F200TC/BC-55     | +4.75 V to +5.25 V |

| MBM29F200TC/BC-70/-90 | +4.50 V to +5.50 V |

|                       |                    |

Operating ranges define those limits between which the functionality of the devices are guaranteed.

**WARNING:** The recommended operating conditions are required in order to ensure the normal operating ranges for the semiconductor device. All of the device's electrical characteristics are warranted whent the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

#### MAXIMUM OVERSHOOT

#### ■ DC CHARACTERISTICS

| Parameter<br>Symbol | Parameter Description                                                                                           | Test Conditions                                                                                                                                               | Min.   | Max.    | Unit      |    |

|---------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-----------|----|

| lu                  | Input Leakage Current                                                                                           | VIN = Vss to Vcc, Vcc = Vcc                                                                                                                                   | -1.0   | +1.0    | μA        |    |

| Ilo                 | Output Leakage Current                                                                                          | Vout = Vss to Vcc, Vcc = Vc                                                                                                                                   | c Max. | -1.0    | +1.0      | μA |

| Ιιπ                 | A₃, OE, RESET Inputs Leakage<br>Current                                                                         | Vcc <u>= Vcc Max.</u><br>A <sub>9</sub> , OE, RESET = 12.5 V                                                                                                  |        | _       | 50        | μA |

| l                   | Ver Active Current (Note 1)                                                                                     | $\overline{CE} = V_{IL}, \overline{OE} = V_{IH}$                                                                                                              | Byte   |         | 35        | mA |

| Icc1                | Vcc Active Current (Note 1)                                                                                     | CE = VIL, OE = VIH                                                                                                                                            | Word   |         | 40        |    |

| Icc2                | Vcc Active Current (Note 2)                                                                                     | $\overline{CE} = V_{IL}, \overline{OE} = V_{IH}$                                                                                                              |        | —       | 50        | mA |

| 1                   |                                                                                                                 | $\frac{V_{CC} = V_{CC} \text{ Max., } \overline{CE} = V_{IH},}{\overline{RESET} = V_{IH}}$                                                                    |        | _       | 1         | mA |

| Іссз                | Vcc Current (Standby)                                                                                           | $\frac{V_{\text{CC}} = V_{\text{CC}} \text{ Max., } \overline{\text{CE}} = V_{\text{CC}} \pm 0.3 \text{ V,}}{\text{RESET} = V_{\text{CC}} \pm 0.3 \text{ V}}$ |        | _       | 5         | μA |

|                     |                                                                                                                 | Vcc = Vcc Max.,<br>RESET = Vi∟                                                                                                                                |        | _       | 1         | mA |

| Icc4                | Vcc Current (Standby, Reset)                                                                                    | Vcc = Vcc Max.,<br>RESET = Vss±0.3 V                                                                                                                          | _      | 5       | μA        |    |

| VIL                 | Input Low Level                                                                                                 | _                                                                                                                                                             |        | -0.5    | 0.8       | V  |

| Vih                 | Input High Level                                                                                                | _                                                                                                                                                             | _      |         | Vcc + 0.5 | V  |

| Vid                 | Voltage for Autoselect and<br>Sector Protection<br>(A $_9$ , $\overline{OE}$ , $\overline{RESET}$ ) (Note 3, 4) |                                                                                                                                                               |        | 11.5    | 12.5      | V  |

| Vol                 | Output Low Voltage Level                                                                                        | Io∟ = 5.8mA, Vcc = Vcc Min.                                                                                                                                   |        |         | 0.45      | V  |

| Vон1                |                                                                                                                 | Іон = –2.5 mA, Vcc = Vcc Min.                                                                                                                                 |        | 2.4     | _         | V  |

| Vон2                | Output High Voltage Level                                                                                       | Іон = –100 µА                                                                                                                                                 |        | Vcc-0.4 | _         | V  |

| Vlko                | Low Vcc Lock-Out Voltage                                                                                        | _                                                                                                                                                             | 3.2    | 4.2     | V         |    |

Notes: 1. The Icc current listed includes both the DC operating current and the frequency dependent component (at 6 MHz). The frequency component typically is 2 mA/MHz, with OE at V<sub>H</sub>.

2. Icc active while Embedded Algorithm (program or erase) is in progress.

3. Applicable to sector protection function.

4. (VID - VCC) do not exceed 9 V.

#### ■ AC CHARACTERISTICS

#### • Read Only Operations Characteristics

| Parameter<br>Symbols |                | Description                                                          | Test Setup                          |      | -55<br>(Note1) | -70<br>(Note2) | -90     | Unit |

|----------------------|----------------|----------------------------------------------------------------------|-------------------------------------|------|----------------|----------------|---------|------|

| JEDEC                | Standard       |                                                                      |                                     |      | (NOLET)        | (NOLEZ)        | (Note2) |      |

| <b>t</b> avav        | <b>t</b> RC    | Read Cycle Time                                                      | —                                   | Min. | 55             | 70             | 90      | ns   |

| <b>t</b> avqv        | tacc           | Address to Output Delay                                              | $\frac{\overline{CE}}{OE} = V_{IL}$ | Max. | 55             | 70             | 90      | ns   |

| <b>t</b> elqv        | <b>t</b> CE    | Chip Enable to Output Delay                                          | $\overline{OE} = V_{IL}$            | Max. | 55             | 70             | 90      | ns   |

| <b>t</b> glqv        | <b>t</b> OE    | Output Enable to Output Delay                                        | —                                   | Max. | 30             | 30             | 35      | ns   |

| <b>t</b> ehqz        | tdf            | Chip Enable to Output High-Z                                         | —                                   | Max. | 15             | 20             | 20      | ns   |

| t <sub>GHQZ</sub>    | tdf            | Output Enable to Output High-Z                                       | —                                   | Max. | 15             | 20             | 20      | ns   |

| taxqx                | tон            | Output Hold Time From Addresses,<br>CE or OE, Whichever Occurs First | _                                   | Min. | 0              | 0              | 0       | ns   |

| —                    | <b>t</b> ready | RESET Pin Low to Read Mode                                           | —                                   | Max. | 20             | 20             | 20      | μs   |

| _                    | telfl<br>telfh | CE or BYTE Switching Low or High                                     |                                     | Max. | 5              | 5              | 5       | ns   |

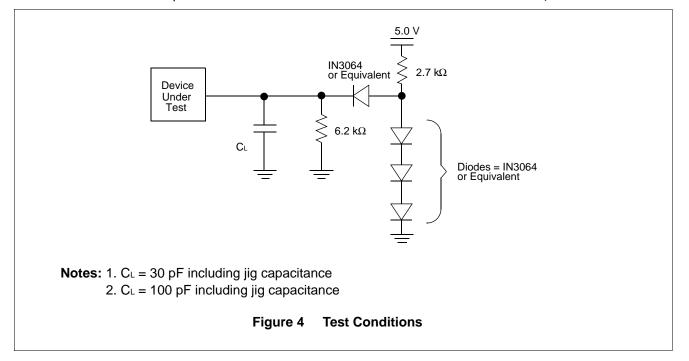

Note: 1. Test Conditions: Output Load: 1 TTL gate and 30 pF Input rise and fall times: 5 ns Input pulse levels: 0.0 V to 3.0 V Timing measurement reference level Input: 1.5 V Output: 1.5 V Note: 2. Test Conditions:

Output Load: 1 TTL gate and 100 pF Input rise and fall times: 5 ns Input pulse levels: 0.45 V to 2.4 V Timing measurement reference level Input: 0.8 V and 2.0 V Output: 0.8 V and 2.0 V

#### • Write/Erase/Program Operations

| Parameter Symbols |                 | Description           |                                              |      | MB  | 11  |     |        |

|-------------------|-----------------|-----------------------|----------------------------------------------|------|-----|-----|-----|--------|

| JEDEC             | Standard        | Description           |                                              |      | -55 | -70 | -90 | – Unit |

| <b>t</b> avav     | twc             | Write Cycle Time Min. |                                              | Min. | 55  | 70  | 90  | ns     |

| <b>t</b> avwl     | tas             | Address Setu          | p Time                                       | Min. | 0   | 0   | 0   | ns     |

| twlax             | tан             | Address Hold          | Time                                         | Min. | 40  | 45  | 45  | ns     |

| tovwн             | tos             | Data Setup Ti         | me                                           | Min. | 25  | 30  | 45  | ns     |

| <b>t</b> whdx     | tон             | Data Hold Tin         | ne                                           | Min. | 0   | 0   | 0   | ns     |

| _                 | toes            | Output Enable         | e Setup Time                                 | Min. | 0   | 0   | 0   | ns     |

|                   |                 | Output                | Read                                         | Min. | 0   | 0   | 0   | ns     |

| —                 | tоен            | Enable Hold<br>Time   | Toggle and Data Polling                      | Min. | 10  | 10  | 10  | ns     |

| <b>t</b> GHWL     | <b>t</b> GHWL   | Read Recove           | r Time Before Write                          | Min. | 0   | 0   | 0   | ns     |

| <b>t</b> GHEL     | <b>t</b> GHEL   | Read Recove           | r Time Before Write                          | Min. | 0   | 0   | 0   | ns     |

| telwl             | tcs             | CE Setup Tim          | CE Setup Time                                |      | 0   | 0   | 0   | ns     |

| twlel             | tws             | WE Setup Tin          | WE Setup Time                                |      | 0   | 0   | 0   | ns     |

| twнен             | tсн             | CE Hold Time          |                                              | Min. | 0   | 0   | 0   | ns     |

| <b>t</b> ehwh     | twн             | WE Hold Time          |                                              | Min. | 0   | 0   | 0   | ns     |

| twlwн             | twp             | Write Pulse W         | Write Pulse Width                            |      | 30  | 35  | 45  | ns     |

| <b>t</b> eleh     | t <sub>CP</sub> | CE Pulse Wid          | CE Pulse Width                               |      | 30  | 35  | 45  | ns     |

| twnw∟             | twpн            | Write Pulse W         | /idth High                                   | Min. | 20  | 20  | 20  | ns     |

| <b>t</b> ehel     | tсрн            | CE Pulse Width High   |                                              | Min. | 20  | 20  | 20  | ns     |

| <b>t</b> whwh1    | twhwh1          | Byte Program          | Byte Programming Operation                   |      | 8   | 8   | 8   | μs     |

| 4                 | 4               | Sector Frees          | Operation (Note 1)                           | Тур. | 1   | 1   | 1   | sec    |

| <b>t</b> whwh2    | twhwh2          | Seciol Elase          | Operation (Note 1)                           | Max. | 8   | 8   | 8   | sec    |

| _                 | tvcs            | Vcc Setup Tin         | ne                                           | Min. | 50  | 50  | 50  | μs     |

| _                 | tvidr           | RiseTime to \         | / <sub>ID</sub>                              | Min. | 500 | 500 | 500 | ns     |

| _                 | <b>t</b> ∨LHT   | Voltage Trans         | ition Time (Note 2)                          | Min. | 4   | 4   | 4   | μs     |

| —                 | twpp            | Write Pulse W         | /idth (Note 2)                               | Min. | 100 | 100 | 100 | μs     |

| —                 | toesp           | OE Setup Tim          | ne to $\overline{\text{WE}}$ Active (Note 2) | Min. | 4   | 4   | 4   | μs     |

| —                 | <b>t</b> CSP    | CE Setup Tim          | te to $\overline{\text{WE}}$ Active (Note 2) | Min. | 4   | 4   | 4   | μs     |

| _                 | t <sub>RB</sub> | Recover Time          | from RY/BY                                   | Min. | 0   | 0   | 0   | ns     |

(Continued)

#### (Continued)

| Parameter Symbols |               | Description                            |      | MBM29F200TC/BC |     |     |        |

|-------------------|---------------|----------------------------------------|------|----------------|-----|-----|--------|

| JEDEC             | Standard      | Description                            |      | -55            | -70 | -90 | - Unit |

|                   | <b>t</b> RP   | RESET Pulse Width                      | Min. | 500            | 500 | 500 | ns     |

|                   | <b>t</b> RH   | RESET Hold Time Before Read            | Min. | 50             | 50  | 50  | ns     |

| —                 | <b>t</b> FLQZ | BYTE Switching Low to Output High-Z    | Max. | 30             | 20  | 30  | ns     |

| —                 | <b>t</b> fhqv | BYTE Switching High to Output Active   | Min. | 30             | 20  | 30  | ns     |

| —                 | <b>t</b> BUSY | Program/Erase Valid to RY/BY Delay     | Max. | 55             | 70  | 90  | ns     |

| —                 | <b>t</b> EOE  | Delay Time from Embedded Output Enable | Max. | 30             | 30  | 35  | ns     |