#### 查询SN65LBC031QD供应商

## <u>共应商</u> HIGH-SPEED CONTROLLER AREA NETWORK (CAN) TRANSCEIVERS

- SN65LBC031Q Meets Standard ISO/DIS 11898 (up to 500 k Baud)

- Driver Output Capability at 50 mA

- Wide Positive and Negative Input/output Bus Voltage Range

- Bus Outputs Short-Circuit-Protected to Battery Voltage and Ground

- Thermal Shutdown

- Available in Q-Temp Automotive

- High Reliability Automotive Applications

- Configuration Control/Print Support

- Qualification to Automotive Standards

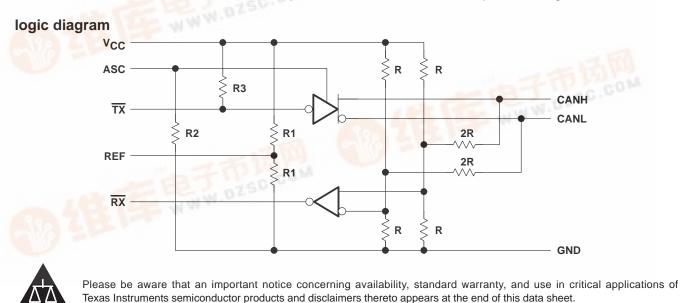

#### description

The SN65LBC031Q is a CAN transceiver used as an interface between a CAN controller and the physical bus for high speed applications of up to 500 k Baud. The device provides transmit capability to the differential bus and differential receive capability to the controller. The transmitter outputs (CANH and CANL), feature internal transition regulation to provide controlled symmetry resulting in low EMI emissions. Both

| D PACKAGE<br>(TOP VIEW)                                              |                              |  |  |  |  |  |

|----------------------------------------------------------------------|------------------------------|--|--|--|--|--|

| TX 1 8 ASC<br>GND 2 7 CANH<br>V <sub>CC</sub> 3 6 CANL<br>RX 4 5 REF |                              |  |  |  |  |  |

| TERMINAL DESCRIPTION                                                 |                              |  |  |  |  |  |

| ТХ                                                                   | Transmitter input            |  |  |  |  |  |

| GND                                                                  | Ground                       |  |  |  |  |  |

| VCC                                                                  | Supply voltage               |  |  |  |  |  |

| RX                                                                   | Receiver output              |  |  |  |  |  |

| REF                                                                  | Reference output             |  |  |  |  |  |

| CANL                                                                 | Low side bus output driver   |  |  |  |  |  |

| CANH                                                                 | High side bus output driver  |  |  |  |  |  |

| ASC                                                                  | ASC Adjustable slope control |  |  |  |  |  |

| FUNCTION TABLE                                                       |                              |  |  |  |  |  |

SLRS048B - MAY 1998 - REVISED MAY 2000

#### FUNCTION TABL TX CANH CANL **BUS STATE** RX Н Т Dominant L L High or floating Floating Floating Recessive Н L = low.H = high

transmitter outputs are fully protected against battery short circuits and electrical transients that can occur on the bus lines. In the event of excessive device power dissipation the output drivers are disabled by the thermal shutdown circuitry at a junction temperature of approximately 160°C. The inclusion of an internal pullup resistor on the transmitter input ensures a defined output during power up and protocol controller reset. For normal operation at 500 k Baud the ASC terminal is open or tied to GND. For slower speed operation at 125 k Baud the bus output transition times can be increased to reduce EMI by connecting the ASC terminal to V<sub>CC</sub>. The receiver includes an integrated filter that suppresses the signal into pulses less than 30 ns wide.

The SN65LBC031Q is characterized for operation over the automotive temperature range of -40°C to 125°C.

RCDUCTION DATA information is current as of publication date. roducts conform to specifications per the terms of Texas instruments randard vargarnly. Production processing does not necessarily include esting of all parameters.

SLRS048B - MAY 1998 - REVISED MAY 2000

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Logic supply voltage, V <sub>CC</sub> (see Note 1)                                  |                         |

|-------------------------------------------------------------------------------------|-------------------------|

| Bus terminal vol <u>tag</u> e                                                       |                         |

| Input current at $\overline{TX}$ and ASC terminal, I <sub>1</sub>                   |                         |

| Input voltage at $\overline{TX}$ and ASC terminal, V <sub>1</sub>                   | $\dots 2 \times V_{CC}$ |

| Operating free-air temperature range, T <sub>A</sub>                                |                         |

| Operating junction temperature range, T <sub>J</sub>                                | –40°C to 150°C          |

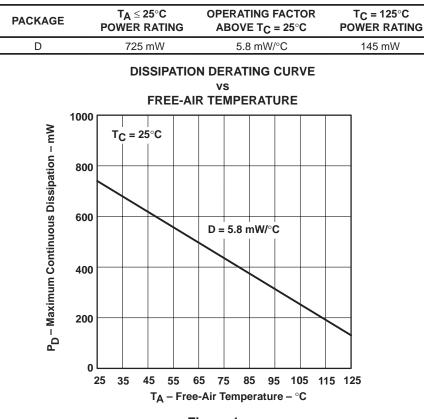

| Continuous total power dissipation at (or below) 25°C free-air temperature See Diss | ipation Rating Table    |

| Storage temperature range, T <sub>stg</sub>                                         | 65°C to 150°C           |

| Case temperature for 10 sec $T_{C}$ , D package                                     | 260°C                   |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

**DISSIPATION RATING TABLE**

NOTE 1: All voltage values, except differential bus voltage, are measured with respect to GND.

Figure 1

SLRS048B - MAY 1998 - REVISED MAY 2000

#### recommended operating conditions

|                                       |                                               | MIN                                                            | NOM  | MAX | UNIT       |

|---------------------------------------|-----------------------------------------------|----------------------------------------------------------------|------|-----|------------|

| Logic supply voltage, V <sub>CC</sub> |                                               | 4.5                                                            | 5    | 5.5 | V          |

| Voltage at any bus terminal (separa   | ately or common mode), VI or VIC (see Note 3) | -2                                                             |      | 7   | V          |

| High-level input voltage, VIH         | TX                                            | 2                                                              |      | VCC | V          |

| Low-level input voltage, VIL          | TX                                            | 0                                                              |      | 0.8 | V          |

| Ligh lovel output ourrent love        | Transmitter                                   |                                                                |      | -50 | mA         |

| High-level output current, IOH        | Receiver                                      | 3)<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2 | -400 | μA  |            |

|                                       | Transmitter                                   |                                                                |      | 50  | <b>~</b> ^ |

| Low-level output current, IOL         | Receiver                                      |                                                                |      | 1   | mA         |

| Operating free-air temperature, TA    |                                               | -40                                                            |      | 125 | °C         |

NOTES: 2. All voltage values, except differential bus voltage, are measured with respect to the ground terminal.

3. For bus voltages from -5 V to -2 V and 7 V to 20 V the receiver output is stable.

| STMBOL DEFINITION    |                                                   |  |  |  |  |  |

|----------------------|---------------------------------------------------|--|--|--|--|--|

| DATA SHEET PARAMETER | DEFINITION                                        |  |  |  |  |  |

| VO(CANHR)            | CANH bus output voltage (recessive state)         |  |  |  |  |  |

| VO(CANLR)            | CANL bus output voltage (recessive state)         |  |  |  |  |  |

| VO(CANHD)            | CANH bus output voltage (dominant state)          |  |  |  |  |  |

| VO(CANLD)            | CANL bus output voltage (dominant state)          |  |  |  |  |  |

| VO(DIFFR)            | Bus differential output voltage (recessive state) |  |  |  |  |  |

| VO(DIFFD)            | Bus differential output voltage (dominant state)  |  |  |  |  |  |

| VI(ASC)              | Adjustable slope control input voltage            |  |  |  |  |  |

#### SYMBOL DEFINITION

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER           |                                       | TEST CONDITIONS            | MIN                  | TYP | MAX                 | UNIT |

|---------------------|---------------------------------------|----------------------------|----------------------|-----|---------------------|------|

| V <sub>O(REF)</sub> | Reference source output voltage       | $I_{REF} = \pm 20 \ \mu A$ | 0.45 V <sub>CC</sub> |     | 0.55V <sub>CC</sub> | V    |

| R <sub>O(REF)</sub> | Reference source output resistance    |                            | 5                    |     | 10                  | kΩ   |

| ICC(REC)            | Logic supply current, recessive state | See Figure 2, S1 closed    |                      | 12  | 20                  | mA   |

| ICC(DOM)            | Logic supply current, dominant state  | See Figure 2, ST Closed    |                      | 55  | 80                  | ШA   |

SLRS048B - MAY 1998 - REVISED MAY 2000

# transmitter electrical characteristics over recommended ranges of supply and operating free-air temperature (unless otherwise noted)

|                        | PARAMETER                                     | TEST CONDITIONS                       | MIN  | TYP    | MAX  | UNIT |  |

|------------------------|-----------------------------------------------|---------------------------------------|------|--------|------|------|--|

| VO(CANHR)<br>VO(CANLR) | Output voltage (recessive state)              | See Figure 2, S1 open                 | 2    | 0.5VCC | 3    | V    |  |

| VO(DIFFR)              | Differential output voltage (recessive state) |                                       | -500 | 0      | 50   | mV   |  |

| VO(CANHD)              | Output voltage (dominant state)               |                                       | 2.75 | 3.5    | 4.5  |      |  |

| VO(CANLD)              | Output voltage (dominant state)               | See Figure 2, S1 closed               | 0.5  | 1.5    | 2.25 | V    |  |

| VO(DIFFD)              | Differential output voltage (dominant state)  |                                       | 1.5  | 2      | 3    |      |  |

| IIH(TX)                | High lovel input current (TV)                 | V <sub>IH</sub> = 2.4 V               |      | -100   | -185 | A    |  |

|                        | High-level input current (TX)                 | $V_{IH} = V_{CC}$                     |      |        | ±2   | μΑ   |  |

|                        | Ligh lovel input ourrest (ACC)                | V <sub>IH</sub> = 2.4 V               |      | 100    | 165  | A    |  |

| IIH(ASC)               | High-level input current (ASC)                | VIH = VCC                             |      | 200    | 340  | μA   |  |

| IIL(TX)                | Low-level input current (TX)                  | V <sub>IL</sub> = 0.4 V               |      | -180   | -400 | μA   |  |

| IIL(ASC)               | Low-level input current (ASC)                 | V <sub>IL</sub> = 0.4 V               |      | 15     | 25   | μA   |  |

| C <sub>I(TX)</sub>     | TX input capacitance                          |                                       |      | 8      |      | pF   |  |

| I <sub>O(ssH)</sub>    | CANH short circuit output current             | $V_{O(CANH)} = -2 V \text{ to } 20 V$ |      | -95    | -200 | mA   |  |

| IO(ssL)                | CANL short circuit output current             | V <sub>O(CANL)</sub> = 20 V to -2 V   |      | 140    | 250  | mA   |  |

NOTE 2: All voltage values, except differential bus voltage, are measured with respect to the ground terminal.

# transceiver dynamic characteristics over recommended operating free-air temperature range and $V_{CC}$ = 5 V

|                        | PARAMETER                                             | TEST                               | CONDITIONS                                          | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------------|------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| + <i>a</i> .           | Loop time                                             | See Figures 2 and 3,<br>S1 closed, | VI(ASC) = 0 V or open circuit,<br>S2 open           |     |     | 280 | ns   |

| t(loop)                | Loop time                                             | See Figures 2 and 3,<br>S1 closed, | VI(ASC) = V <sub>CC</sub> ,<br>S2 closed            |     |     | 400 | ns   |

|                        | Differential-output slew rate (recessive to dominant) | See Figures 2 and 4,<br>S1 closed, | V <sub>I(ASC)</sub> = 0 or open circuit,<br>S2 open |     | 35  |     | V/µs |

| SR(RD)                 |                                                       | See Figures 2 and 4,<br>S1 closed, | VI(ASC) = V <sub>CC</sub> ,<br>S2 closed            |     | 10  |     | V/µs |

|                        | Differential-output slew rate                         | See Figures 2 and 4,<br>S1 closed, | V <sub>I(ASC)</sub> = 0 or open circuit,<br>S2 open |     | 10  |     | V/µs |

| SR(DR)                 | (dominant to recessive)                               | See Figures 2 and 4,<br>S1 closed, | VI(ASC) = V <sub>CC</sub> ,<br>S2 closed            |     | 10  |     | V/µs |

| <sup>t</sup> d(RD)     | Differential output delay time                        |                                    | S1 alagad                                           |     | 55  |     | ns   |

| <sup>t</sup> d(DR)     | Differential-output delay time                        | See Figure 2,                      | S1 closed                                           |     | 160 |     | ns   |

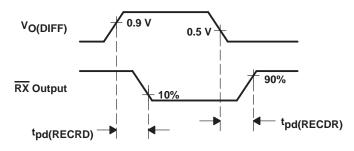

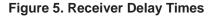

| <sup>t</sup> pd(RECRD) | Receiver propagation delay                            | See Figures 2 and 5                |                                                     |     | 90  |     | ns   |

| <sup>t</sup> pd(RECDR) | time                                                  | See Figures 2 and 5                |                                                     |     | 55  |     | ns   |

NOTE 4: Receiver input pulse width should be >50 ns. Input pulses of <30 ns are suppressed.

SLRS048B - MAY 1998 - REVISED MAY 2000

#### receiver electrical characteristics over recommended ranges of common-mode input voltage, supply voltage, and operating free-air temperature (unless otherwise noted)

|                      | PARAMETER                                                      | TEST CONDITIONS                                 | MIN                    | TYP | MAX | UNIT |

|----------------------|----------------------------------------------------------------|-------------------------------------------------|------------------------|-----|-----|------|

| VIT(REC)             | Differential input threshold voltage for recessive state       | $V_{IC} = -2 V \text{ to } 7 V$                 |                        |     | 500 | mV   |

| VIT(DOM)             | Differential input threshold voltage for dominant state        | $V_{\rm IC} = -2  v  10  V  v$                  | 900                    |     |     | IIIV |

| V <sub>hys</sub>     | Recessive-dominant input hysteresis                            |                                                 | 100                    | 180 |     | mV   |

| VOH(RX)              | High-level output voltage                                      | VO(DIFF) = 500 mV,<br>I <sub>OH</sub> = -400 μA | V <sub>CC</sub> -0.5 V |     | VCC | V    |

| VOL(RX)              | Low-level output voltage                                       | VO(DIFF) = 900 mV,<br>I <sub>OL</sub> = 1 mA    | 0                      |     | 0.5 | V    |

| <sup>r</sup> I(REC)  | CANH and CANL input resistance in recessive state              | dc, no load                                     | 5                      |     | 50  | kΩ   |

| <sup>r</sup> l(DIFF) | Differential CANH and CANL input resistance in recessive state | dc, no load                                     | 10                     |     | 100 | kΩ   |

| Ci                   | CANH and CANL input capacitance                                |                                                 |                        | 20  |     | pF   |

| C <sub>i(DHL)</sub>  | Differential CANH and CANL input capacitance                   |                                                 |                        | 10  |     | pF   |

NOTE 2: All voltage values, except differential bus voltage, are measured with respect to the ground terminal.

#### S2 Vcc C > **60** Ω **60** Ω ASC CANH **S**1 TX Input VDIFF Ō CANL Generator 56 pF ≶ **60** Ω Ś **60** Ω 📥 56 pF ≶ R (see Note A) **RX** Output < 15 pF ÷

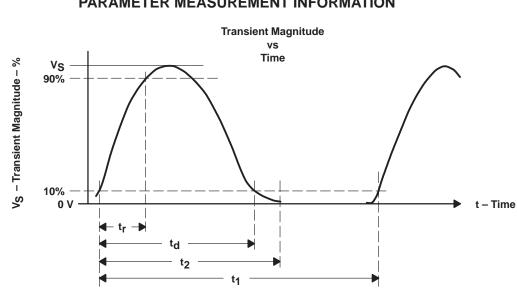

## PARAMETER MEASUREMENT INFORMATION

NOTE A: The input pulse is supplied to  $\overline{TX}$  by a generator having a t<sub>r</sub> and t<sub>f</sub> = 5 ns.

#### Figure 2. Test Circuit

SLRS048B - MAY 1998 - REVISED MAY 2000

NOTE A: The input pulse is supplied to  $\overline{TX}$  by a generator having a t<sub>r</sub> and t<sub>f</sub> = 5 ns.

NOTE A: The input pulse is supplied as VDIFF using CANH and CANL respectively by a generator having a  $t_f$  and  $t_f = 5$  ns.

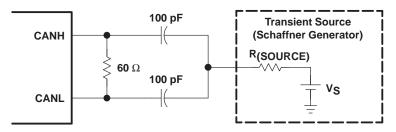

Figure 6. Transient Stress Capability Test Circuit

SLRS048B - MAY 1998 - REVISED MAY 2000

#### PARAMETER MEASUREMENT INFORMATION

Figure 7. Transient Stress Capability Waveform

| TEST PULSE | TRANSIENT<br>MAGNITUDE<br><sup>V</sup> S | SOURCE<br>IMPEDANCE<br><sup>R</sup> SOURCE | PULSE WIDTH<br><sup>t</sup> d<br>(see Note 5) | PULSE RISE<br>TIME, t <sub>r</sub><br>(see Note 6) | PULSE TIME,<br><sup>t</sup> 2<br>(see Figure 7) | REPETITION<br>PERIOD, t <sub>1</sub><br>(see Figure 7) | NUMBER OF<br>PULSES |

|------------|------------------------------------------|--------------------------------------------|-----------------------------------------------|----------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|---------------------|

| 1          | –100 V                                   | 10 Ω                                       | 2 ms                                          | 1 μs                                               | 200 ms                                          | 5 s                                                    | 5000                |

| 2          | 100 V                                    | 10 Ω                                       | 50 μs                                         | 1 μs                                               | 200 ms                                          | 5 s                                                    | 5000                |

| 3a         | –150 V                                   | 50 Ω                                       | 0.1 μs                                        | 5 ns                                               | 100 μs                                          | 100 μs                                                 | See Note 7          |

| 3b         | 100 V                                    | 50 Ω                                       | 0.1 μs                                        | 5 ns                                               | 100 μs                                          | 100 μs                                                 | See Note 7          |

| 5          | 60 V                                     | 1 Ω                                        | 400 ms                                        | 5 ms                                               | _                                               | _                                                      | 1                   |

Table 1. Test Circuit Results According to DIN 40839

NOTES: 5. Measured from 10% on rising edge to 10% on falling edge

6. Measured from 10% to 90% of pulse

7. Pulse package for a period of 3600 s, 10 ms pulse time, 90 ms stop time

SLRS048B - MAY 1998 - REVISED MAY 2000

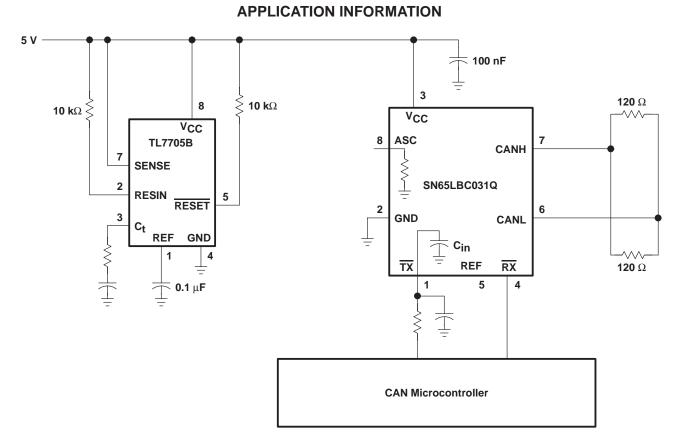

Figure 8. Typical SN65LBC031Q Application

SLRS048B - MAY 1998 - REVISED MAY 2000

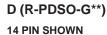

#### **MECHANICAL DATA**

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated