## **Document Title**

256Kx16 Bit High Speed Static RAM(5.0V Operating).

Operated at Commercial and Industrial Temperature Ranges.

## **Revision History**

| Rev No.  | <u>History</u>                       | Draft Data          | Remark      |

|----------|--------------------------------------|---------------------|-------------|

| Rev. 0.0 | Initial release with Preliminary.    | September. 7. 2001  | Preliminary |

| Rev. 0.1 | Package dimension modify on page 11. | Septermber.28. 2001 | Preliminary |

| Rev. 0.2 | Change Icc, Isb and Isb1             | November, 3, 2001   | Preliminary |

| Item            | THE PARTY OF | Previous | Current |

|-----------------|--------------|----------|---------|

|                 | 10ns         | 90mA     | 65mA    |

| ICC(Commercial) | 12ns         | 80mA     | 55mA    |

|                 | 15ns         | 70mA     | 45mA    |

|                 | 10ns         | 115mA    | 85mA    |

| ICC(Industrial) | 12ns         | 100mA    | 75mA    |

| ľ               | 15ns         | 85mA     | 65mA    |

| ISB             |              | 30mA     | 20mA    |

| ISB1(Normal)    |              | 10mA     | 5mA     |

Rev. 0.3 1. Correct AC parameters : Read & Write Cycle

2. Corrrect Power part : Delete "P-Industrial,Low Power" part

3. Delete Data Retention Characteristics

Rev. 0.4 1. Delete 15ns speed bin.

2. Change Icc for Industrial mode.

| Change icc for industrial mode. |      |          |         |  |  |  |  |

|---------------------------------|------|----------|---------|--|--|--|--|

| Ite                             | m    | Previous | Current |  |  |  |  |

| ICC(Industrial)                 | 10ns | 85mA     | 75mA    |  |  |  |  |

| 100(iiidustilai)                | 12ns | 75mA     | 65mA    |  |  |  |  |

Rev. 1.0 1. Final datasheet release.

2. Delete 12ns speed bin.

Rev. 2.0 1. Add the Lead Free Package type.

November, 23, 2001

Preliminary

December, 18, 2001

Preliminary

July, 09, 2002

Final

June. 20, 2003

Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any questions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

## 4Mb Async. Fast SRAM Ordering Information

|          |                                        | -      | <b>=</b>     | -                                                  | =                                                                     |  |

|----------|----------------------------------------|--------|--------------|----------------------------------------------------|-----------------------------------------------------------------------|--|

| Org.     | Part Number                            | VDD(V) | Speed ( ns ) | PKG                                                | Temp. & Power                                                         |  |

| 1M x4    | K6R4004C1D-J(K)C(I) 10 5 10 J : 32-SOJ |        |              |                                                    |                                                                       |  |

| TIVI X4  | K6R4004V1D-J(K)C(I) 08/10              | 3.3    | 8/10         | K : 32-SOJ(LF)                                     | C : Commercial Temperature<br>,Normal Power Range                     |  |

|          | K6R4008C1D-J(K,T,U)C(I) 10             | 5      | 10           | J:36-SOJ                                           | I : Industrial Temperature                                            |  |

| 512K x8  | K6R4008V1D-J(K,T,U)C(I) 08/10          | 3.3    | 8/10         | K : 36-SOJ(LF)<br>T : 44-TSOP2<br>U : 44-TSOP2(LF) | ,Normal Power Range<br>L : Commercial Temperature<br>,Low Power Range |  |

|          | K6R4016C1D-J(K,T,U,E)C(I) 10           | 5      | 10           | J : 44-SOJ<br>K : 44-SOJ(LF)                       | P : Industrial Temperature                                            |  |

| 256K x16 | K6R4016V1D-J(K,T,U,E)C(I,L,P) 08/10    | 3.3    | 8/10         | T : 44-TSOP2<br>U: 44-TSOP2(LF)<br>E : 48-TBGA     | ,Low Power Range                                                      |  |

## 256K x 16 Bit High-Speed CMOS Static RAM

#### **FEATURES**

• Fast Access Time 10ns(Max.)

• Low Power Dissipation

Standby (TTL) : 20mA(Max.) (CMOS) : 5mA(Max.)

Operating K6R4016C1D-10:65mA(Max.)

• Single 5.0V±10% Power Supply

· TTL Compatible Inputs and Outputs

• Fully Static Operation

- No Clock or Refresh required

· Three State Outputs

• Center Power/Ground Pin Configuration

• Data Byte Control : LB : I/O1~ I/O8, UB : I/O9~ I/O16

• Standard Pin Configuration

K6R4016C1D-J: 44-SOJ-400

K6R4016C1D-K: 44-SOJ-400(Lead-Free) K6R4016C1D-T: 44-TSOP2-400BF

K6R4016C1D-U: 44-TSOP2-400BF (Lead-Free) K6R4016C1D-E: 48-TBGA with 0.75 Ball pitch (7mm X 9mm)

Operating in Commercial and Industrial Temperature range.

#### **GENERAL DESCRIPTION**

The K6R4016C1D is a 4,194,304-bit high-speed Static Random Access Memory organized as 262,144 words by 16 bits. The K6R4016C1D uses 16 common input and output lines and has an output enable pin which operates faster than address access time at read cycle. Also it allows that lower and upper byte access by data byte control(UB, LB). The device is fabricated using SAMSUNG's advanced CMOS process and designed for high-speed circuit technology. It is particularly well suited for use in high-density high-speed system applications. The K6R4016C1D is packaged in a 400mil 44-pin plastic SOJ or TSOP(II) forward or 48 T BGA.

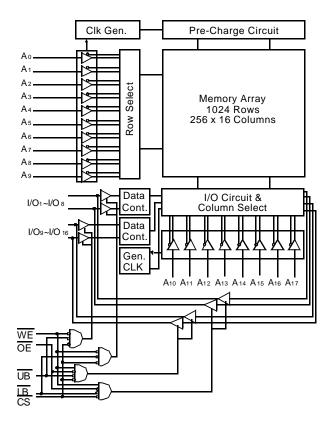

#### **FUNCTIONAL BLOCK DIAGRAM**

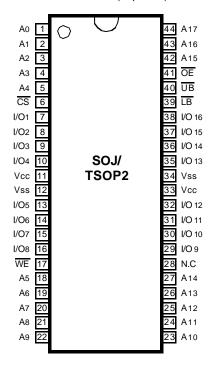

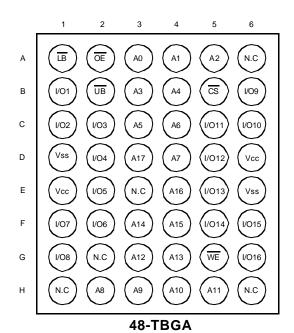

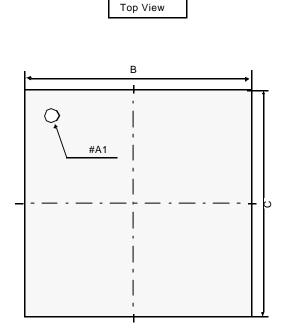

## PIN CONFIGURATION (Top View)

### **PIN FUNCTION**

|              | -                              |

|--------------|--------------------------------|

| Pin Name     | Pin Function                   |

| A0 - A17     | Address Inputs                 |

| WE           | Write Enable                   |

| CS           | Chip Select                    |

| ŌĒ           | Output Enable                  |

| LB           | Lower-byte Control(I/O1~I/O8)  |

| UB           | Upper-byte Control(I/O9~I/O16) |

| I/O1 ~ I/O16 | Data Inputs/Outputs            |

| Vcc          | Power(+5.0V)                   |

| Vss          | Ground                         |

| N.C          | No Connection                  |

## **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                             |            | Symbol    | Rating          | Unit |

|---------------------------------------|------------|-----------|-----------------|------|

| Voltage on Any Pin Relative to Vss    |            | VIN, VOUT | -0.5 to VCC+0.5 | V    |

| Voltage on Vcc Supply Relative to Vss |            | Vcc       | -0.5 to 7.0     | V    |

| Power Dissipation                     |            | PD        | 1.0             | W    |

| Storage Temperature                   |            | Tstg      | -65 to 150      | °C   |

| Operating Temperature                 | Commercial | TA        | 0 to 70         | °C   |

|                                       | Industrial | TA        | -40 to 85       | °C   |

<sup>\*</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **RECOMMENDED DC OPERATING CONDITIONS\***(TA=0 to 70°C)

| Parameter          | Symbol | Min    | Тур | Max        | Unit |

|--------------------|--------|--------|-----|------------|------|

| Supply Voltage     | Vcc    | 4.5    | 5.0 | 5.5        | V    |

| Ground             | Vss    | 0      | 0   | 0          | V    |

| Input High Voltage | ViH    | 2.2    | -   | Vcc+0.5*** | V    |

| Input Low Voltage  | VIL    | -0.5** | -   | 0.8        | V    |

The above parameters are also guaranteed at industrial temperature range.

## DC AND OPERATING CHARACTERISTICS\*(TA=0 to 70°C, Vcc=5.0V±10%, unless otherwise specified)

| Parameter                 | Symbol | Test Conditions                                                    |      |      | Min | Max | Unit |

|---------------------------|--------|--------------------------------------------------------------------|------|------|-----|-----|------|

| Input Leakage Current     | lu     | VIN=VSS to VCC                                                     |      |      | -2  | 2   | μΑ   |

| Output Leakage Current    | ILO    | CS=VIH or OE=VIH or WE=VIL VOUT=VSS to VCC                         |      |      | -2  | 2   | μΑ   |

| Operating Current         | Icc    | Min. Cycle, 100% Duty                                              | Com. | 10ns | -   | 65  | mA   |

|                           | С      | CS=VIL, VIN=VIH or VIL, IOUT=0mA                                   | Ind. | 10ns | -   | 75  |      |

| Standby Current           | ISB    | Min. Cycle, CS=VIH  f=0MHz, CS≥Vcc-0.2V,  VIN≥Vcc-0.2V or VIN≤0.2V |      | -    | 20  | mA  |      |

|                           | ISB1   |                                                                    |      | -    | 5   |     |      |

| Output Low Voltage Level  | Vol    | IoL=8mA                                                            |      |      | -   | 0.4 | V    |

| Output High Voltage Level | Voн    | IOH=-4mA                                                           |      |      | 2.4 | -   | V    |

<sup>\*</sup> The above parameters are also guaranteed at industrial temperature range.

## **CAPACITANCE\***(TA=25°C, f=1.0MHz)

| Item                     | Symbol | Test Conditions | TYP | Max | Unit |

|--------------------------|--------|-----------------|-----|-----|------|

| Input/Output Capacitance | CI/O   | VI/0=0V         | -   | 8   | pF   |

| Input Capacitance        | CIN    | VIN=0V          | -   | 6   | pF   |

<sup>\*</sup> Capacitance is sampled and not 100% tested.

<sup>\*\*\*</sup>  $V_{IL}(Min) = -2.0V$  a.c(Pulse Width  $\leq 8ns$ ) for  $I \leq 20mA$  \*\*\*  $V_{IH}(Max) = V_{CC} + 2.0V$  a.c (Pulse Width  $\leq 8ns$ ) for  $I \leq 20mA$ .

## AC CHARACTERISTICS (TA=0 to 70°C, Vcc=5.0V±10%, unless otherwise noted.)

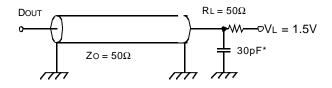

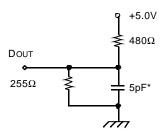

#### **TEST CONDITIONS\***

| Parameter                                | Value     |

|------------------------------------------|-----------|

| Input Pulse Levels                       | 0V to 3V  |

| Input Rise and Fall Times                | 3ns       |

| Input and Output timing Reference Levels | 1.5V      |

| Output Loads                             | See below |

<sup>\*</sup> The above test conditions are also applied at industrial temperature range.

Output Loads(A)

Output Loads(B) for tHz, tLz, tWHz, tOW, tOLz & tOHz

#### **READ CYCLE\***

| Barranatan                       | 0      | K6R4016C1D-10 |     |      |

|----------------------------------|--------|---------------|-----|------|

| Parameter                        | Symbol | Min           | Max | Unit |

| Read Cycle Time                  | trc    | 10            | -   | ns   |

| Address Access Time              | tAA    | -             | 10  | ns   |

| Chip Select to Output            | tco    | -             | 10  | ns   |

| Output Enable to Valid Output    | tOE    | -             | 5   | ns   |

| Chip Enable to Low-Z Output      | tız    | 3             | -   | ns   |

| Output Enable to Low-Z Output    | tOLZ   | 0             | -   | ns   |

| Chip Disable to High-Z Output    | tHZ    | 0             | 5   | ns   |

| Output Disable to High-Z Output  | tonz   | 0             | 5   | ns   |

| Output Hold from Address Change  | tон    | 3             | -   | ns   |

| Chip Selection to Power Up Time  | tpu    | 0             | -   | ns   |

| Chip Selection to Power DownTime | tPD    | -             | 10  | ns   |

<sup>\*</sup> The above parameters are also guaranteed at industrial temperature range.

<sup>\*</sup> Capacitive Load consists of all components of the test environment.

<sup>\*</sup> Including Scope and Jig Capacitance

## WRITE CYCLE\*

| Danamatan                     | 0      | K6R401 | 6C1D-10 | I I m i t |

|-------------------------------|--------|--------|---------|-----------|

| Parameter                     | Symbol | Min    | Max     | Unit      |

| Write Cycle Time              | twc    | 10     | -       | ns        |

| Chip Select to End of Write   | tcw    | 7      | -       | ns        |

| Address Set-up Time           | tas    | 0      | -       | ns        |

| Address Valid to End of Write | tAW    | 7      | -       | ns        |

| Write Pulse Width(OE High)    | twp    | 7      | -       | ns        |

| Write Pulse Width(OE Low)     | tWP1   | 10     | -       | ns        |

| Write Recovery Time           | twr    | 0      | -       | ns        |

| Write to Output High-Z        | twHZ   | 0      | 5       | ns        |

| Data to Write Time Overlap    | tDW    | 5      | -       | ns        |

| Data Hold from Write Time     | tDH    | 0      | -       | ns        |

| End of Write to Output Low-Z  | tow    | 3      | -       | ns        |

$<sup>^{\</sup>star}$  The above parameters are also guaranteed at industrial temperature range.

### **TIMING DIAGRAMS**

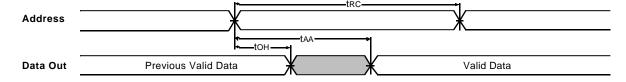

$\textbf{TIMING WAVEFORM OF READ CYCLE(1)} \ (\text{Address Controlled}, \ \overline{\text{CS}} = \overline{\text{OE}} = \text{VIL}, \ \overline{\text{WE}} = \text{VIH}, \ \overline{\text{UB}}, \ \overline{\text{LB}} = \text{VIL})$

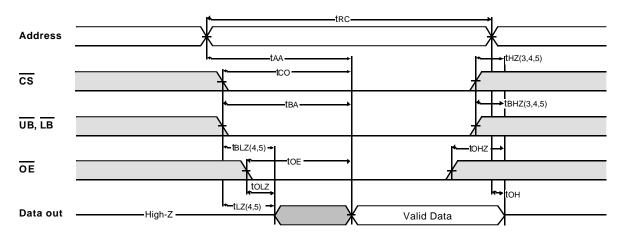

## TIMING WAVEFORM OF READ CYCLE(2) (WE=ViH)

#### NOTES (READ CYCLE)

- 1.  $\overline{\text{WE}}$  is high for read cycle.

- 2. All read cycle timing is referenced from the last valid address to the first transition address.

- 3. tHz and toHz are defined as the time at which the outputs achieve the open circuit condition and are not referenced to VoH or VoL

- 4. At any given temperature and voltage condition, thz(Max.) is less than tz(Min.) both for a given device and from device to device.

- 5. Transition is measured  $\pm 200$ mV from steady state voltage with Load(B). This parameter is sampled and not 100% tested. 6. Device is continuously selected with  $\overline{\text{CS}} = \text{V}_{\text{IL}}$

- 7. Address valid prior to coincident with CS transition low.

- 8. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

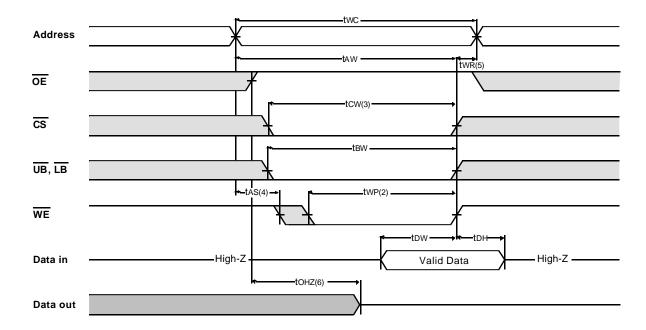

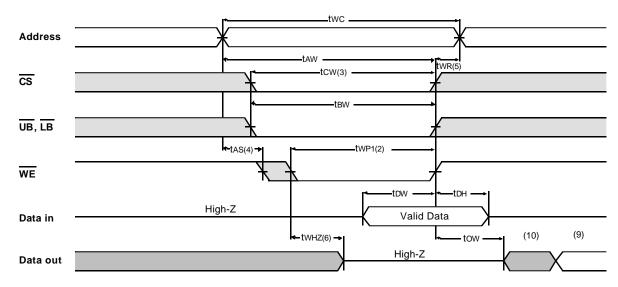

## TIMING WAVEFORM OF WRITE CYCLE(1) (OEClock)

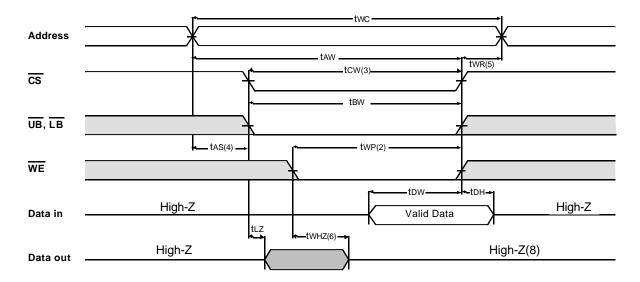

## TIMING WAVEFORM OF WRITE CYCLE(2) (OE=Low fixed)

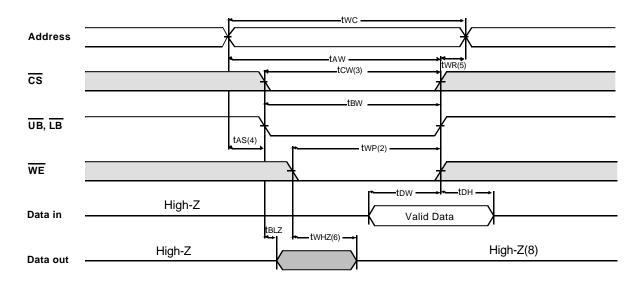

#### TIMING WAVEFORM OF WRITE CYCLE(3) (CS=Controlled)

### TIMING WAVEFORM OF WRITE CYCLE(4) (UB, LBControlled)

#### NOTES(WRITE CYCLE)

- 1. All write cycle timing is referenced from the <u>last valid address</u> to the first transition address.

2. A write occurs during the overlap of a low CS, WE, LB and UB. A write begins at the latest transition CS going low and WE going low; A write ends at the earliest transition  $\overline{CS}$  going high or  $\overline{WE}$  going high. twp is measured from the beginning of write to the end of write.

- 3. tcw is measured from the later of  $\overline{\text{CS}}$  going low to end of write.

- 4. tas is measured from the address valid to the beginning of write.

- 5. twn is measured from the end of write to the address change. twn applied in case a write ends as  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going high.

- 6. If  $\overline{OE}$ ,  $\overline{CS}$  and  $\overline{WE}$  are in the Read Mode during this period, the I/O pins are in the output low-Z state. Inputs of opposite phase of the output must not . be applied because bus contention can occur.

7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

- 8. If  $\overline{CS}$  goes low simultaneously with  $\overline{WE}$  going or after  $\overline{WE}$  going low, the outputs remain high impedance state.

- 9. Dout is the read data of the new address.

10. When CS is low: I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be applied.

## **FUNCTIONAL DESCRIPTION**

| cs | WE | OE | LB | UB | Mode           | I/O Pin   |            | Supply Current |

|----|----|----|----|----|----------------|-----------|------------|----------------|

| 03 | WL | OL | LB | ОВ | Wode           | I/O1~I/O8 | I/O9~I/O16 | Supply Current |

| Н  | Х  | X* | Х  | X  | Not Select     | High-Z    | High-Z     | ISB, ISB1      |

| L  | Н  | Н  | X  | Х  | Output Disable | High-Z    | High-Z     | Icc            |

| L  | Х  | Х  | Н  | Η  |                |           |            |                |

| L  | Н  | L  | L  | Н  | Read           | Dout      | High-Z     | Icc            |

|    |    |    | Н  | L  |                | High-Z    | Dout       |                |

|    |    |    | L  | L  |                | Dout      | Douт       |                |

| L  | L  | Х  | L  | Н  | Write          | DIN       | High-Z     | Icc            |

|    |    |    | Н  | L  |                | High-Z    | DIN        |                |

|    |    |    | L  | L  |                | DIN       | DIN        |                |

<sup>\*</sup> X means Don't Care.

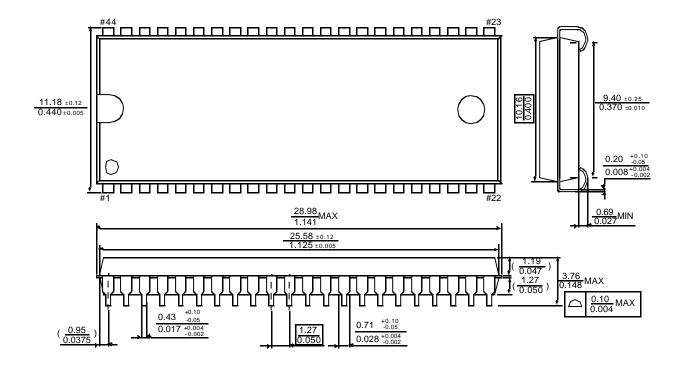

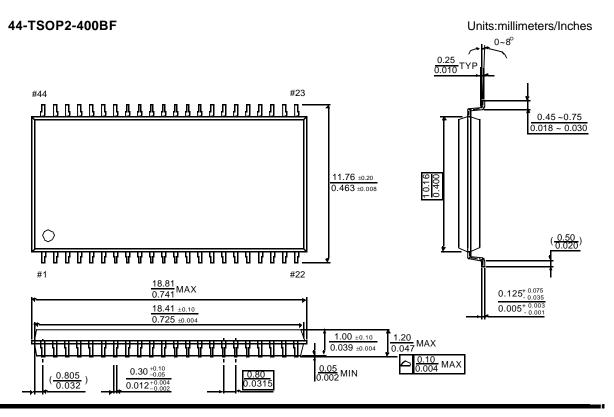

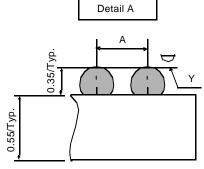

### **PACKAGE DIMENSIONS**

Units:millimeters/Inches

#### 44-SOJ-400

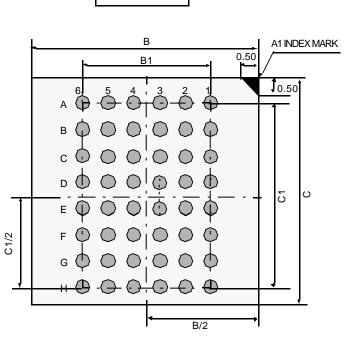

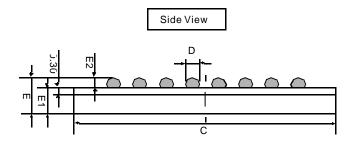

## **PACKAGE DIMENSIONS**

Units: millimeter.

**Bottom View**

|    | Min  | Тур  | Max  |

|----|------|------|------|

| Α  | -    | 0.75 | -    |

| В  | 6.90 | 7.00 | 7.10 |

| B1 | -    | 3.75 | -    |

| С  | 8.90 | 9.00 | 9.10 |

| C1 | -    | 5.25 | -    |

| D  | 0.40 | 0.45 | 0.50 |

| E  | 0.80 | 0.90 | 1.00 |

| E1 | -    | 0.55 | -    |

| E2 | 0.30 | 0.35 | 0.40 |

| Y  | -    | -    | 0.08 |

### Notes.

- 1. Bump counts: 48(8row x 6column)

- 2. Bump pitch :  $(x,y)=(0.75 \times 0.75)(typ.)$

- 3. All tolerence are +/-0.050 unless otherwise specified.

- 4. Typ: Typical

- 5. Y is coplanarity: 0.08(Max)