#### **FAIRCHILD** SEMICONDUCTOR®

April 2000 Revised January 2003 NC7WZ00 TinyLogic® UHS Dual 2-Input NAND Gate

## NC7WZ00

## TinyLogic® UHS Dual 2-Input NAND Gate

#### **General Description**

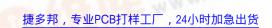

The NC7WZ00 is a dual 2-Input NAND Gate from Fairchild's Ultra High Speed Series of TinyLogic®. The device is fabricated with advanced CMOS technology to achieve ultra high speed with high output drive while maintaining low static power dissipation over a broad V<sub>CC</sub> operating range. The device is specified to operate over the 1.65V to 5.5V V<sub>CC</sub> operating range. The inputs and output are high impedance when V<sub>CC</sub> is 0V. Inputs tolerate voltages up to 7V independent of V<sub>CC</sub> operating voltage.

#### **Features**

- Space saving US8 surface mount package

- MicroPak<sup>™</sup> leadless package

- Ultra High Speed; t<sub>PD</sub> 2.4 ns typ into 50 pF at 5V V<sub>CC</sub>

- High Output Drive; ±24 mA at 3V V<sub>CC</sub>

- Broad V<sub>CC</sub> Operating Range; 1.65V–5.5V

- Matches the performance of LCX when operated at 3.3V V<sub>CC</sub>

- Power down high impedance inputs/output

- Overvoltage tolerant inputs facilitate 5V to 3V translation

- Patented noise/EMI reduction circuitry implemented

## Ordering Code:

|                             |         | Product  |                                                   |                           |  |  |

|-----------------------------|---------|----------|---------------------------------------------------|---------------------------|--|--|

| Order                       | Package | Code     | Package Description                               | Supplied As               |  |  |

| Number                      | Number  | Top Mark |                                                   | - 1                       |  |  |

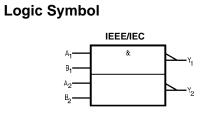

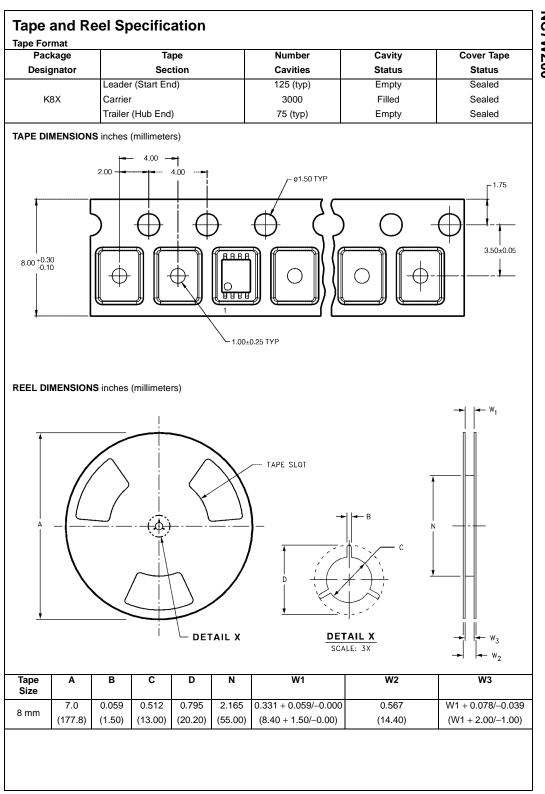

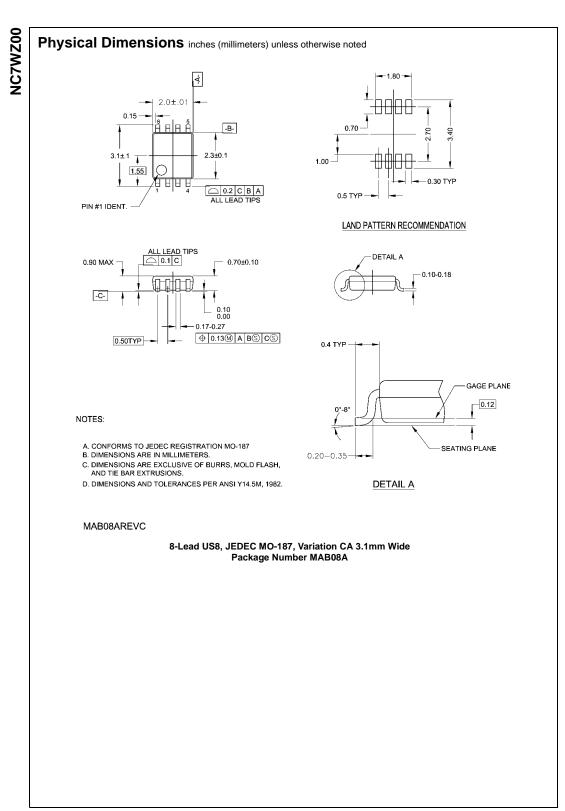

| NC7WZ00K8X                  | MAB08A  | WZ00     | 8-Lead US8, JEDEC MO-187, Variation CA 3.1mm Wide | 3k Units on Tape and Reel |  |  |

| NC7WZ00L8X<br>(Preliminary) | MAC08A  | N6       | 8-Lead MicroPak, 1.6 mm Wide                      | 5k Units on Tape and Reel |  |  |

TinyLogic® is a registered trademark and MicroPak™ is a trademark of Fairchild Semiconductor Corporation.

# NC7WZ00

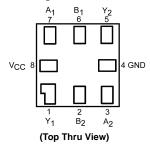

#### **Pin Descriptions**

| Pin Names                       | Description |  |  |  |  |

|---------------------------------|-------------|--|--|--|--|

| A <sub>n</sub> , B <sub>n</sub> | Inputs      |  |  |  |  |

| Y <sub>n</sub>                  | Output      |  |  |  |  |

#### **Function Table**

|     | $\mathbf{Y} = \overline{\mathbf{AE}}$ | 5      |

|-----|---------------------------------------|--------|

| Inp | uts                                   | Output |

| Α   | В                                     | Y      |

| L   | L                                     | Н      |

| L   | н                                     | Н      |

| н   | L                                     | Н      |

| н   | Н                                     | L      |

H = HIGH Logic Level L = LOW Logic Level

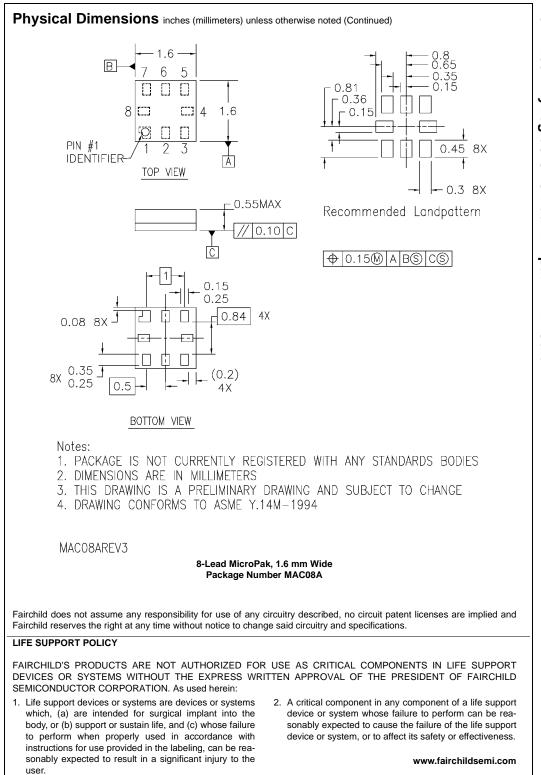

AAA represents Product Code Top Mark - see ordering code **Note:** Orientation of Top Mark determines Pin One location. Read the top product code mark left to right, Pin One is the lower left pin (see diagram).

Pin One

#### Pad Assignments for MicroPak

www.fairchildsemi.com

#### Absolute Maximum Ratings(Note 1)

| Supply Voltage (V <sub>CC</sub> )                                    | -0.5V to +7V    |

|----------------------------------------------------------------------|-----------------|

| DC Input Voltage (V <sub>IN</sub> )                                  | -0.5V to +7V    |

| DC Output Voltage (V <sub>OUT</sub> )                                | -0.5V to +7V    |

| DC Input Diode Current (IIK)                                         |                 |

| $@V_{IN} < -0.5V$                                                    | –50 mA          |

| DC Output Diode Current (I <sub>OK</sub> )                           |                 |

| $@V_{OUT} < -0.5V$                                                   | –50 mA          |

| DC Output Current (I <sub>OUT</sub> )                                | $\pm$ 50 mA     |

| DC V <sub>CC</sub> /GND Current (I <sub>CC</sub> /I <sub>GND</sub> ) | $\pm100~mA$     |

| Storage Temperature (T <sub>STG</sub> )                              | –65°C to +150°C |

| Junction Temperature under Bias $(T_J)$                              | 150°C           |

| Junction Lead Temperature (TL);                                      |                 |

| (Soldering, 10 seconds)                                              | 260°C           |

| Power Dissipation (P <sub>D</sub> ) @ +85°C                          | 250 mW          |

|                                                                      |                 |

# Recommended Operating Conditions (Note 2)

| Supply Voltage Operating ( $V_{CC}$ )         | 1.65V to 5.5V                    |

|-----------------------------------------------|----------------------------------|

| Supply Voltage Data Retention ( $V_{CC}$ )    | 1.5V to 5.5V                     |

| Input Voltage (V <sub>IN</sub> )              | 0V to 5.5V                       |

| Output Voltage (V <sub>OUT</sub> )            | 0V to $V_{CC}$                   |

| Operating Temperature (T <sub>A</sub> )       | $-40^{\circ}C$ to $+85^{\circ}C$ |

| Input Rise and Fall Time $(t_r, t_f)$         |                                  |

| $V_{CC}$ @ 1.65V $\pm$ 0.15V, 2.5V $\pm$ 0.2V | 0 ns/V to 20 ns/V                |

| $V_{CC} @ 3.3V \pm 0.3V$                      | 0 ns/V to 10 ns/V                |

| $V_{CC} @ 5.0V \pm 0.5V$                      | 0 ns/V to 5 ns/V                 |

| Thermal Resistance ( $\theta_{JA}$ )          | 250°C/W                          |

Note 1: Absolute maximum ratings are DC values beyond which the device may be damaged or have its useful life impaired. The datasheet specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation outside datasheet specifications.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

Units

V

V

V

V

V

v

μA

μΑ

μΑ

$V_{IN} = V_{IL}$

Conditions

$I_{OH} = -100 \ \mu A$

$I_{OH} = -4 \text{ mA}$

$I_{OH} = -8 \text{ mA}$

$I_{OH} = -16 \text{ mA}$

$I_{OH} = -24 \text{ mA}$  $I_{OH} = -32 \text{ mA}$

$I_{OL} = 4 \text{ mA}$

$I_{OL} = 8 \text{ mA}$

I<sub>OL</sub> = 16 mA

I<sub>OL</sub> = 24 mA I<sub>OL</sub> = 32 mA

$V_{IN} = V_{IH}$   $I_{OL} = 100 \ \mu A$

$V_{IN} = 5.5V, GND$

V<sub>IN</sub> = 5.5V, GND

V<sub>IN</sub> or V<sub>OUT</sub> = 5.5V

#### Vcc $T_A = +25^{\circ}C$ $T_A = -40^{\circ}C$ to $+85^{\circ}C$ Symbol Parameter (V) Min Тур Max Min Max VIH HIGH Level Input Voltage 1.65-1.95 0.75 V<sub>CC</sub> 0.75 V<sub>CC</sub> 2.3-5.5 0.70 V<sub>CC</sub> 0.70 V<sub>CC</sub> 0.25 V<sub>CC</sub> 0.25 V<sub>CC</sub> $V_{\text{IL}}$ LOW Level Input Voltage 1.65-1.95 0.30 V<sub>CC</sub> 0.30 V<sub>CC</sub> 2.3-5.5 HIGH Level Output Voltage V<sub>ОН</sub> 1.65 1.55 1.65 1.55 2.3 2.2 2.3 2.2 3.0 2.9 3.0 2.9 4.5 4.5 4.4 4.4 1.65 1.29 1.52 1.69 2.3 1.9 2.15 1.9 3.0 2.4 2.80 2.4 3.0 2.3 2.68 2.3

3.8

4.20

0.0

0.0

0.0

0.0

0.08

0.10

0.15

0.22

0.22

3

0.1

0.1

0.1

0.1

0.24

0.3

0.4

0.55

0.55

±0.1

1

1

4.5

1.65

2.3

3.0

4.5

1.65

2.3

3.0

3.0

4.5

0-5.5

0.0

1.65-5.5

#### 260°C 250 mW Note 1: Absolute maximum ra may be damaged or have its

3.8

0.1

0.1

0.1

0.1

0.24

0.3

0.4

0.55

0.55

±1.0

10

10

### **DC Electrical Characteristics**

LOW Level Output Voltage

Input Leakage Current

Power Off Leakage Current

Quiescent Supply Current

V<sub>OL</sub>

I<sub>IN</sub>

**I**OFF

lcc

| 0 |

|---|

| 0 |

| Ñ |

| > |

| 5 |

| Ň |

| C |

| Z |

### **AC Electrical Characteristics**

| Symbol             | Parameter                     | V <sub>cc</sub>               | T <sub>A</sub> = +25°C |     |     | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |     | Units | Conditions               | Fig. No.        |

|--------------------|-------------------------------|-------------------------------|------------------------|-----|-----|----------------------------------------|-----|-------|--------------------------|-----------------|

|                    | Faranieter                    | (V)                           | Min                    | Тур | Max | Min                                    | Max | Units | conultions               | Fig. NO.        |

| t <sub>PLH</sub> , | Propagation Delay             | $1.8\pm0.15$                  | 2.0                    | 5.3 | 9.6 | 2.0                                    | 9.8 |       |                          |                 |

| t <sub>PHL</sub>   |                               | $2.5\pm0.2$                   | 1.2                    | 3.2 | 5.3 | 1.2                                    | 5.7 | ns    | $C_{L} = 15 \text{ pF},$ | Figures         |

|                    |                               | $3.3\pm0.3$                   | 0.8                    | 2.4 | 3.7 | 0.8                                    | 4.0 | 115   | $R_L = 1 M\Omega$        | 1, 3            |

|                    |                               | $5.0\pm0.5$                   | 0.5                    | 1.9 | 2.9 | 0.5                                    | 3.2 |       |                          |                 |

| t <sub>PLH,</sub>  | Propagation Delay             | $\textbf{3.3}\pm\textbf{0.3}$ | 1.2                    | 3.0 | 4.6 | 1.2                                    | 4.9 | ns    | $C_{L} = 50 \text{ pF},$ | Figures<br>1, 3 |

| t <sub>PHL</sub>   |                               | $5.0\pm0.5$                   | 0.8                    | 2.4 | 3.6 | 0.8                                    | 3.9 |       | $R_L = 500\Omega$        |                 |

| CIN                | Input Capacitance             | 0                             |                        | 2.5 |     |                                        |     | pF    |                          |                 |

| C <sub>PD</sub>    | Power Dissipation Capacitance | 3.3                           |                        | 13  |     |                                        |     | pF    | (Note 3)                 | Figure 2        |

|                    |                               | 5.0                           |                        | 17  |     |                                        |     | PΓ    | (14018-3)                | r igule z       |

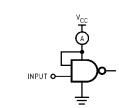

Note 3:  $C_{PD}$  is defined as the value of the internal equivalent capacitance which is derived from dynamic operating current consumption ( $I_{CCD}$ ) at no output loading and operating at 50% duty cycle. (See Figure 2.)  $C_{PD}$  is related to  $I_{CCD}$  dynamic operating current by the expression:  $I_{CCD} = (C_{PD})(V_{CC})(f_{|N}) + (I_{CC}$ static).

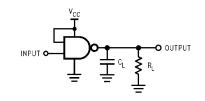

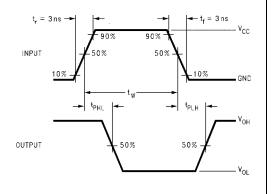

#### **AC Loading and Waveforms**

$C_L$  includes load and stray capacitance Input PRR = 1.0 MHz;  $t_w = 500$  ns

FIGURE 1. AC Test Circuit

Input = AC Waveform;  $t_r = t_f = 1.8$  ns; PRR = 10 MHz; Duty Cycle = 50% FIGURE 2. I<sub>CCD</sub> Test Circuit

#### FIGURE 3. AC Waveforms

www.fairchildsemi.com

NC7WZ00

www.fairchildsemi.com