CMOS LSI

Ordering number :

查询LC897194供应商

\*EN5572

# LC897194

# CD-ROM Decoder with Built-In ATAPI (IDE) and DVD ECC Interfaces

## Preliminary

## **Overview**

The LC897194 provides CD-ROM functionality and includes built-in DVD ECC and ATAPI (IDE) interfaces.

## **Function**

• CD-ROM ECC functionality, an ATAPI (IDE) interface (the register and other blocks), and a DVD ECC interface

## **Features**

- ATAPI (IDE) interface

- DVD ECC interface

- Supports up to 12×-speed playback (when using 70-ns 16-bit data path DRAM)

- Transfer rate: 16.6 MB/s (when using 60-ns 16-bit data path DRAM)

- Transfer rate: 8.33 MB/s (when using 70-ns 8-bit data path DRAM)

- Between 1 and 32 Mbits of DRAM can be used as buffer RAM.

- The user can freely set up the CD main channel and the C2 flags in buffer RAM.

- Built-in batch transfer function (function for transferring the CD main channel and the C2 flags in one operation)

- Built-in multiple transfer function (function for automatically transferring multiple blocks in a single operation)

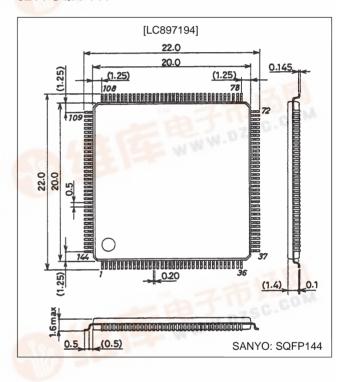

# Package Dimensions

unit: mm 3214-SQFP144

## **Specifications**

Absolute Maximum Ratings at  $V_{SS} = 0 V$

| Parameter                             | Symbol                              | Conditions              | Ratings                      | Unit |

|---------------------------------------|-------------------------------------|-------------------------|------------------------------|------|

| Maximum supply voltage                | V <sub>DD</sub> max                 | Ta = 2 <mark>5°C</mark> | -0.3 to +7.0                 | V    |

| I/O voltages                          | V <sub>I</sub> , V <sub>O</sub>     | Ta = 25°C               | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation           | Pd max                              | Ta ≤ 70°C               | 550                          | mW   |

| Operating temperature                 | Topr                                |                         | -30 to +70                   | °C   |

| Storage temperature                   | Tstg                                | COM                     | -55 to +125                  | °C   |

| Soldering heat resistance (pins only) |                                     | 10 seconds              | 235                          | °C   |

| Maximum I/O power                     | I <sub>I</sub> , I <sub>O</sub> max |                         | ±20*                         | mA   |

Note: Per basic I/O cell.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

#### Allowable Operating Ranges at Ta = -30 to $+70^{\circ}$ C, V<sub>SS</sub> = 0 V

| Parameter           | Symbol          | Conditions |     | Unit |                 |      |

|---------------------|-----------------|------------|-----|------|-----------------|------|

| Falameter           | Symbol          | Conditions | min | typ  | max             | Unit |

| Supply voltage      | V <sub>DD</sub> |            | 4.5 | 5.0  | 5.5             | V    |

| Input voltage range | V <sub>IN</sub> |            | 0   |      | V <sub>DD</sub> | V    |

## DC Characteristics at Ta = –30 to +70°C, $V_{SS}$ = 0 V, $V_{DD}$ = 4.5 to 5.5 V

| Devenuetor                | O mah al         |                                                                      |                       | Unit |                     |      |  |

|---------------------------|------------------|----------------------------------------------------------------------|-----------------------|------|---------------------|------|--|

| Parameter                 | Symbol           | Applicable pins (see below)                                          | min                   | typ  | max                 | Unit |  |

| Input high-level voltage  | V <sub>IH1</sub> | TTL compatible: (1)                                                  | 2.2                   |      |                     | V    |  |

| Input low-level voltage   | V <sub>IL1</sub> | TTL compatible: (1)                                                  |                       |      | 0.8                 | V    |  |

| Input high-level voltage  | V <sub>IH2</sub> | TTL compatible, with pull-up resistor: (12)                          | 2.2                   |      |                     | V    |  |

| Input low-level voltage   | V <sub>IL2</sub> | TTL compatible, with pull-up resistor: (12)                          |                       |      | 0.8                 | V    |  |

| Input high-level voltage  | V <sub>IH3</sub> | TTL compatible, with pull-down resistor: (2)                         | 2.2                   |      |                     | V    |  |

| Input low-level voltage   | V <sub>IL3</sub> | TTL compatible, with pull-down resistor: (2)                         |                       |      | 0.8                 | V    |  |

| Input high-level voltage  | V <sub>IH4</sub> | TTL compatible, Schmitt characteristics: (3), (5), (13), (14)        | 2.5                   |      |                     | v    |  |

| Input low-level voltage   | V <sub>IL4</sub> | TTL compatible, Schmitt characteristics: (3), (5), (13), (14)        |                       |      | 0.6                 | v    |  |

| Input high-level voltage  | V <sub>IH5</sub> | CMOS compatible, Schmitt characteristics: (4)                        | 0.8 V <sub>DD</sub>   |      |                     | V    |  |

| Input low-level voltage   | V <sub>IL5</sub> | CMOS compatible, Schmitt characteristics: (4)                        |                       |      | 0.2 V <sub>DD</sub> | V    |  |

| Output high-level voltage | V <sub>OH1</sub> | I <sub>OH</sub> = -2 mA : (7), (10), (12)                            | V <sub>DD</sub> – 2.1 |      |                     | V    |  |

| Output low-level voltage  | V <sub>OL1</sub> | I <sub>OL</sub> = 2 mA : (7), (10), (12)                             |                       |      | 0.4                 | V    |  |

| Output high-level voltage | V <sub>OH2</sub> | I <sub>OH</sub> = -8 mA : (6)                                        | V <sub>DD</sub> – 2.1 |      |                     | V    |  |

| Output low-level voltage  | V <sub>OL2</sub> | I <sub>OL</sub> = 8 mA : (6)                                         |                       |      | 0.4                 | V    |  |

| Output high-level voltage | V <sub>OH3</sub> | I <sub>OH</sub> = -4 mA : (8), (13)                                  | V <sub>DD</sub> – 2.1 |      |                     | V    |  |

| Output low-level voltage  | V <sub>OL3</sub> | I <sub>OL</sub> = 24 mA : (8), (13)                                  |                       |      | 0.4                 | V    |  |

| Output high-level voltage | V <sub>OH4</sub> | I <sub>OL</sub> = 24 mA : (9), (14)                                  |                       |      | 0.4                 | V    |  |

| Output low-level voltage  | V <sub>OL5</sub> | I <sub>OL</sub> = 2 mA : (11)                                        |                       |      | 0.4                 | V    |  |

| Input leakage current     | I <sub>IL</sub>  | $V_{I} = V_{SS}, V_{DD}$ : (1), (2), (3), (4), (5), (12), (13), (14) | -10                   |      | +10                 | μA   |  |

| Output leakage current    | I <sub>OZ</sub>  | When the output is high impedance: (9), (11), (13), (14)             | -10                   |      | +10                 | μA   |  |

| Pull-up resistance        | R <sub>UP</sub>  | (12)                                                                 | 40                    | 80   | 160                 | kΩ   |  |

| Pull-down resistance      | R <sub>DN</sub>  | (2)                                                                  | 40                    | 80   | 160                 | kΩ   |  |

|                           |                  |                                                                      |                       |      |                     |      |  |

Note: The applicable pins are as follows:

INPUT

(1) CSCTRL, RSSEL, HDB0 to 7, SUA0 to 6

(2) TEST0 to 4

(3) ZDMACK, ZHRST, ZRESET, BCK, C2PO, LRCK, SDATA, DA0 to 2, ZCS1FX, ZCS3FX

(4) ZCS, ZRD, ZWR

(5) ZDIOR, ZDIOW, DRESP, WFCK, SCOR

OUTPUT

(6) MCK, MCK2

(7) ZINTO, ZINT1

(8) DMARQ, HINTRQ

(9) IORDY, ZIOCS16

(10) RA0 to 9, ZCAS0 to 1, ZRAS0 to 1, ZLWE, ZUWE, ZOE, DREQ

(11) ZRSTCPU, ZRSTIC, ZSWAIT

INOUT

(12) D0 to 7, IO0 to 15

(13) DD0 to 15

(14) ZDASP, ZPDIAG

$\ast:$  The DC characteristics do not apply to the XTAL and XTALCK pins.

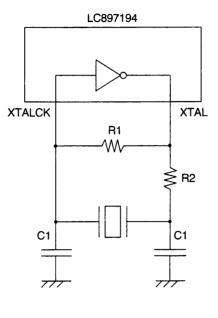

#### **Recommended Oscillator Circuit Example**

A06532

$R1 = 120 \ k\Omega$

$\begin{aligned} R2 &= 47 \ \Omega \\ C1 &= 30 \ pF \end{aligned}$

CI = 50 pr

With a crystal with a resonant frequency of 16.9344 MHz, or:

$R1=3.3\;k\Omega$

R2 = None

$C1 = 5 \ pF$

With a crystal with a resonant frequency of 33.8688 MHz.

If third harmonics are a problem in the 33.8688-MHz recommended circuit, consult with the manufacturer of the crystal for exact component values, since those values will be influenced by the printed circuit board used.

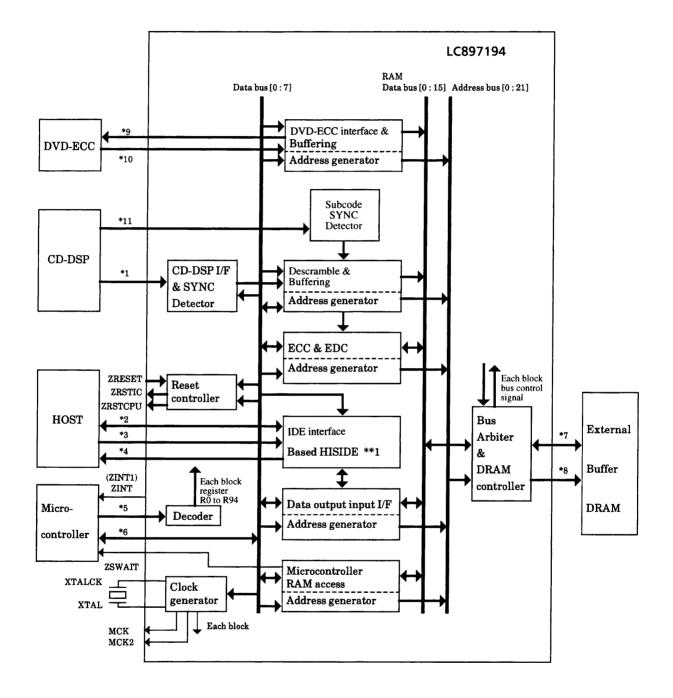

#### **Block Diagram**

- \*1 BCK, SDATA, LRCK, C2PO

- \*2 DD0 to DD15, ZDASP, ZPDIAG

- \*3 ZCS1FX, ZCS3FX, DA0 to DA2, ZDIOR, ZDIOW, ZDMACK

- \*4 DMARQ, HINTRQ, ZIOCS16, IORDY, ZHRST

- \*5 ZRD, ZWR, SUA0 to SUA6, ZCS, CSCTRL

- \*6 D0 to D7

- \*7 IO0 to IO15

- \*8 RA0 to RA9, ZRAS0, ZRAS1, ZCAS0, ZCAS1, ZOE, ZUWE, ZLWE

- \*9 DREQ

- \*10 HDB0 to HDB7, DRESP

- \*11 WFCK, SCOR

- \*\*1 HISIDE (WD25C32) is made by WESTERN DIGITAL.

#### **Pin Functions**

|   |        |   | typ         |    |               |

|---|--------|---|-------------|----|---------------|

| I | Input  | В | Bidirection | NC | Not connected |

| 0 | Output | Р | Power       |    |               |

| 1         V <sub>S80</sub> P           2         ZRAS0         0         RAS signal output 0 to the buffer DRAM (Output 0 is normally used.)           4         V <sub>S80</sub> P           5         ZCAS0         0         CAS signal output 1 to the buffer DRAM (Output 0 is normally used.)           6         ZCAS0         0         CAS signal output 1 to the buffer DRAM (Output 0 is normally used.)           7         V <sub>S80</sub> P            8         ZOE         0         Buffer RAM output enable           9         ZUWE         0         Buffer RAM output enable           10         ZLWE         0         Buffer RAM lower write enable           11         RA0         0         RA0 to RA9 are used for the data buffer DRAM address.           12         RA1         0             14         RA3         0             15         RA4         0             16         RA5         0             17         RA6         0             20         RA7         0             21         RA8         0 <td< th=""><th>Pin No.</th><th>Symbol</th><th>Туре</th><th>Function</th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin No. | Symbol           | Туре | Function                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|------|---------------------------------------------------------------------|

| 2         ZRAS0         O         RAS signal output 0 to the buffer DRAM (Output 0 is normally used.)           3         ZRAS1         O         RAS signal output 1 to the buffer DRAM           4         V <sub>SS0</sub> P           5         ZCAS0         O         CAS signal output 0 to the buffer DRAM (Output 0 is normally used.)           6         ZCAS1         O         CAS signal output 1 to the buffer DRAM           7         V <sub>SS0</sub> P           8         ZOE         O         Buffer RAM output enable           9         ZUWE         O         Buffer RAM lower write enable           10         ZLWE         O         Buffer RAM lower write enable           11         RA0         O         RA0 to RA9 are used for the data buffer DRAM address.           12         RA1         O         Image: State Sta | 1       | V <sub>SS0</sub> | Р    |                                                                     |

| 4         V <sub>SS0</sub> P         Constraint           5         ZCAS0         0         CAS signal output 0 to the buffer DRAM (Output 0 is normally used.)           6         ZCAS1         0         CAS signal output 1 to the buffer DRAM           7         V <sub>SS0</sub> P           8         ZOE         0         Buffer RAM output enable           9         ZUWE         0         Buffer RAM upper write enable           10         ZUWE         0         Buffer RAM upper write enable           11         RA0         0         RAP re used for the data buffer DRAM address.           12         RA1         0           13         RA2         0           14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         VDD         P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST3         NC           25         TEST4         NC                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2       | ZRAS0            | 0    | RAS signal output 0 to the buffer DRAM (Output 0 is normally used.) |

| 5         ZCAS0         O         CAS signal output 0 to the buffer DRAM (Output 0 is normally used.)           6         ZCAS1         O         CAS signal output 1 to the buffer DRAM           7         V <sub>SS0</sub> P           8         ZOE         O         Buffer RAM output enable           9         ZUWE         O         Buffer RAM output enable           10         ZUWE         O         Buffer RAM output enable           11         RA0         O         RA1           12         RA1         O           13         RA2         O           14         RA3         O           15         RA4         O           16         RA5         O           17         RA6         O           18         V <sub>DD</sub> P           19         V <sub>SSO</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST4         NC <td>3</td> <td>ZRAS1</td> <td>0</td> <td>RAS signal output 1 to the buffer DRAM</td>                                                                                                                                                                                                                                                                                                                                                                                                | 3       | ZRAS1            | 0    | RAS signal output 1 to the buffer DRAM                              |

| 5         ZCAS0         O         CAS signal output 0 to the buffer DRAM (Output 0 is normally used.)           6         ZCAS1         O         CAS signal output 1 to the buffer DRAM           7         V <sub>SS0</sub> P           8         ZOE         O         Buffer RAM output enable           9         ZUWE         O         Buffer RAM output enable           10         ZUWE         O         Buffer RAM output enable           11         RA0         O         RA1           12         RA1         O           13         RA2         O           14         RA3         O           15         RA4         O           16         RA5         O           17         RA6         O           18         V <sub>DD</sub> P           19         V <sub>SSO</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST4         NC <td>4</td> <td>V<sub>SS0</sub></td> <td>Р</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                            | 4       | V <sub>SS0</sub> | Р    |                                                                     |

| 7         V <sub>SS0</sub> P         O           8         ZOE         0         Buffer RAM output enable           9         ZUWE         0         Buffer RAM output enable           10         ZUWE         0         Buffer RAM lower write enable           11         RA0         0         RA0 to RA9 are used for the data buffer DRAM address.           12         RA1         0         RA2 to RA9 are used for the data buffer DRAM address.           14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         V <sub>DD</sub> P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           28         IO0         B           33         IO5         B           34         IO6         B           33         IO5         B           34         IO6         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5       |                  | 0    | CAS signal output 0 to the buffer DRAM (Output 0 is normally used.) |

| B         ZOE         O         Buffer RAM output enable           9         ZUWE         O         Buffer RAM upper write enable           10         ZUWE         O         Buffer RAM lower write enable           11         RA0         O         RA0 to RA9 are used for the data buffer DRAM address.           12         RA1         O         RA0 to RA9 are used for the data buffer DRAM address.           14         RA3         O         RA4         O           16         RA5         O         P           17         RA6         O         P           19         V <sub>SS0</sub> P         P           20         RA7         O         RA0 to RA9 are used for the data buffer DRAM address.           21         RA8         O         P           22         RA9         O         P           23         TEST0         NC         Used for testing. There should be no connections to these pins.           24         TEST1         NC         P           27         TEST4         NC           28         IOO         B         Data I/O to/from data buffer DRAM           29         IO1         B         B           31                                                                                                                                                                                                                                                                                                                                                                                         | 6       | ZCAS1            | 0    | CAS signal output 1 to the buffer DRAM                              |

| 9         ZUWE         0         Buffer RAM upper write enable           10         ZUWE         0         Buffer RAM lower write enable           11         RA0         0         RA1 to RA9 are used for the data buffer DRAM address.           12         RA1         0         Rave to RA9 are used for the data buffer DRAM address.           13         RA2         0         0         14           14         RA3         0         0           15         RA4         0         0           16         RA5         0           17         RA6         0           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           31         IO3         B           32         IO4         B          33         IO5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7       | V <sub>SS0</sub> | Р    |                                                                     |

| 10         ZLWE         0         Buffer RAM lower write enable           11         RA0         0         RA0 to RA9 are used for the data buffer DRAM address.           12         RA1         0           13         RA2         0           14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         100         B           31         103         B           32         104         B           33         105         B           34         106         B           34         106         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8       | ZOE              | 0    | Buffer RAM output enable                                            |

| 11         RA0         0         RA0 to RA9 are used for the data buffer DRAM address.           12         RA1         0           13         RA2         0           14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         V <sub>DD</sub> P           19         V <sub>S30</sub> P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           31         IO3         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9       | ZUWE             | 0    | Buffer RAM upper write enable                                       |

| 12         RA1         0           13         RA2         0           14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         Vpp         P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         100         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10      | ZLWE             | 0    | Buffer RAM lower write enable                                       |

| 13         RA2         0           14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11      | RA0              | 0    | RA0 to RA9 are used for the data buffer DRAM address.               |

| 14         RA3         0           15         RA4         0           16         RA5         0           17         RA6         0           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         0           21         RA8         0           22         RA9         0           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           26         TEST3         NC           27         TEST3         NC           28         IO0         B           24         ICST4         NC           28         IO0         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12      | RA1              | 0    |                                                                     |

| 15         RA4         O           16         RA5         O           17         RA6         O           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IOO         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13      | RA2              | 0    |                                                                     |

| 16         RA5         O           17         RA6         O           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         OO         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14      | RA3              | 0    |                                                                     |

| 17         RA6         O           18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>S80</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15      | RA4              | 0    |                                                                     |

| 18         V <sub>DD</sub> P           19         V <sub>SS0</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC           24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IOO         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16      | RA5              | 0    |                                                                     |

| 19         V <sub>SS0</sub> P           20         RA7         O           21         RA8         O           22         RA9         O           23         TEST0         NC         Used for testing. There should be no connections to these pins.           24         TEST1         NC         Used for testing. There should be no connections to these pins.           24         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17      | RA6              | 0    |                                                                     |

| Solution         RA7         O         RA0 to RA9 are used for the data buffer DRAM address.           21         RA8         O         Particular Stresson         Particular Stresson           23         TEST0         NC         Used for testing. There should be no connections to these pins.           24         TEST1         NC         Particular Stresson         Particular Stresson           26         TEST3         NC         Particular Stresson         Particular Stresson           27         TEST4         NC         Particular Stresson         Particular Stresson           28         IOO         B         Data I/O to/from data buffer DRAM         Pull-up resistors are built in.           30         IO2         B         Pull-up resistors are built in.         Pull-up resistors are built in.           33         IO5         B         Pull         Pull         Pull         Pull           34         IO6         B         Pull         Pull         Pull         Pull           36         V <sub>SS0</sub> P         Pull         Pull         Pull         Pull                                                                                                                                                                                                                                                                                                                                                                                                                                | 18      | V <sub>DD</sub>  | Р    |                                                                     |

| 21       RA8       O         22       RA9       O         23       TEST0       NC         24       TEST1       NC         25       TEST2       NC         26       TEST3       NC         27       TEST4       NC         28       IOO       B         29       IO1       B         30       IO2       B         31       IO3       B         32       IO4       B         33       IO5       B         34       IO6       B         35       IO7       B         36       V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19      | V <sub>SS0</sub> | Р    |                                                                     |

| 22         RA9         O           23         TEST0         NC         Used for testing. There should be no connections to these pins.           24         TEST1         NC         These pins must be left open.           25         TEST3         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           29         IO1         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20      | RA7              | 0    | RA0 to RA9 are used for the data buffer DRAM address.               |

| 23         TEST0         NC         Used for testing. There should be no connections to these pins.           24         TEST1         NC         These pins must be left open.           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B         Data I/O to/from data buffer DRAM           29         IO1         B         Pull-up resistors are built in.           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21      | RA8              | 0    |                                                                     |

| 24         TEST1         NC           25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           29         IO1         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22      | RA9              | 0    |                                                                     |

| 25         TEST2         NC           26         TEST3         NC           27         TEST4         NC           28         IO0         B           29         IO1         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23      | TEST0            | NC   | Used for testing. There should be no connections to these pins.     |

| 26         TEST3         NC           27         TEST4         NC           28         IO0         B           29         IO1         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24      | TEST1            | NC   | These pins must be left open.                                       |

| 27         TEST4         NC           28         IO0         B           29         IO1         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25      | TEST2            | NC   |                                                                     |

| 28         IO0         B         Data I/O to/from data buffer DRAM           29         IO1         B         Pull-up resistors are built in.           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26      | TEST3            | NC   |                                                                     |

| 29         IO1         B           30         IO2         B           31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27      | TEST4            | NC   |                                                                     |

| 30     IO2     B       31     IO3     B       32     IO4     B       33     IO5     B       34     IO6     B       35     IO7     B       36     V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28      | IO0              | В    | Data I/O to/from data buffer DRAM                                   |

| 31         IO3         B           32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29      | IO1              | В    | Pull-up resistors are built in.                                     |

| 32         IO4         B           33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30      | IO2              | В    |                                                                     |

| 33         IO5         B           34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31      | IO3              | В    |                                                                     |

| 34         IO6         B           35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32      | IO4              | В    |                                                                     |

| 35         IO7         B           36         V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33      | IO5              | В    |                                                                     |

| 36 V <sub>SS0</sub> P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34      | IO6              | В    |                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35      | 107              | В    |                                                                     |

| 37 Vpp P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36      | V <sub>SS0</sub> | Р    |                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37      | V <sub>DD</sub>  | Р    |                                                                     |

Continued on next page.

#### Continued from preceding page.

| Pin No. | Symbol           | Туре | Function                                                        |

|---------|------------------|------|-----------------------------------------------------------------|

| 38      | IO8              | В    | Data I/O to/from data buffer DRAM                               |

| 39      | 109              | В    | Pull-up resistors are built in.                                 |

| 40      | IO10             | В    |                                                                 |

| 41      | IO11             | В    |                                                                 |

| 42      | IO12             | В    |                                                                 |

| 43      | IO13             | В    |                                                                 |

| 44      | IO14             | В    |                                                                 |

| 45      | IO15             | В    |                                                                 |

| 46      | V <sub>SS0</sub> | Р    |                                                                 |

| 47      | WFCK             | 1    | Subcode input                                                   |

| 48      | SCOR             | 1    | Subcode input                                                   |

| 49      | V <sub>SS0</sub> | Р    |                                                                 |

| 50      | DREQ             | 0    | DVD ECC data request output                                     |

| 51      | DRESP            | 1    | DVD ECC data latch signal input                                 |

| 52      | HDB7             | 1    | DVD ECC data input                                              |

| 53      | HDB6             | 1    |                                                                 |

| 54      | V <sub>DD</sub>  | Р    |                                                                 |

| 55      | V <sub>SS0</sub> | Р    |                                                                 |

| 56      | HDB5             | 1    | DVD ECC data input                                              |

| 57      | HDB4             | I    |                                                                 |

| 58      | HDB3             | I    |                                                                 |

| 59      | HDB2             | I    |                                                                 |

| 60      | HDB1             | I    |                                                                 |

| 61      | HDB0             | I    |                                                                 |

| 62      | SDATA            | I    | Interface with the CD digital signal processor                  |

| 63      | BCK              | I    |                                                                 |

| 64      | LRCK             | I    |                                                                 |

| 65      | C2PO             | I    |                                                                 |

| 66      | MCK2             | 0    | Outputs the XTALCK signal times 1/1, 1/2, or 1/512, or stopped. |

| 67      | CSCTRL           | I    | Microcontroller chip select signal active high or low selection |

| 68      | RSSEL            | I    | Direct or indirect addressing selection                         |

| 69      | V <sub>SS0</sub> | Р    |                                                                 |

| 70      | XTALCK           | I    | Crystal oscillator circuit input                                |

| 71      | XTAL             | 0    | Crystal oscillator circuit output                               |

| 72      | V <sub>SS0</sub> | Р    |                                                                 |

| 73      | V <sub>DD</sub>  | Р    |                                                                 |

| 74      | MCK              | 0    | Outputs the XTALCK signal times 1/1 or 1/2, or stopped.         |

| 75      | V <sub>SS0</sub> | Р    |                                                                 |

| 76      | ZRSTIC           | 0    | Reset output to the driver reset IC                             |

| 77      | ZRESET           | I    | LSI reset input                                                 |

| 78      | ZRD              | I    | Microcontroller data read signal input                          |

| 79      | ZWR              | I    | Microcontroller data write signal input                         |

| 80      | ZCS              | I    | Register chip select signal input from the microcontroller      |

| 81      | ZINT1            | 0    | ATAPI block interrupt output (selected by a register)           |

| 82      | ZINT0            | 0    | Interrupt request signal output to the microcontroller          |

|         |                  |      | Continued on next page                                          |

Continued on next page.

## Continued from preceding page.

| Pin No. | Symbol           | Туре | Function                                               |

|---------|------------------|------|--------------------------------------------------------|

| 83      | SUA0             | I    | Microcontroller register selection signals             |

| 84      | SUA1             | I    | The SUA0 pin functions as RS in indirect address mode. |

| 85      | SUA2             | I    |                                                        |

| 86      | SUA3             | I    |                                                        |

| 87      | SUA4             | I    |                                                        |

| 88      | SUA5             | I    |                                                        |

| 89      | SUA6             | I    |                                                        |

| 90      | V <sub>DD</sub>  | Р    |                                                        |

| 91      | V <sub>SS0</sub> | Р    |                                                        |

| 92      | D0               | В    | Microcontroller data signals                           |

| 93      | D1               | В    | Pull-up resistors are built in.                        |

| 94      | D2               | В    |                                                        |

| 95      | D3               | В    |                                                        |

| 96      | D4               | В    |                                                        |

| 97      | D5               | В    |                                                        |

| 98      | D6               | В    |                                                        |

| 99      | D7               | В    |                                                        |

| 100     | V <sub>SS0</sub> | Р    |                                                        |

| 101     | ZRSTCPU          | 0    | Reset signal output to the CPU                         |

| 102     | ZSWAIT           | 0    | WAIT signal output to the microcontroller              |

| 103     | ZHRST            | I    | ATAPI control signals                                  |