# DATA SHEET

## 80C552/83C552

Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

Product data Supersedes data of 1998 Aug 13

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

#### **DESCRIPTION**

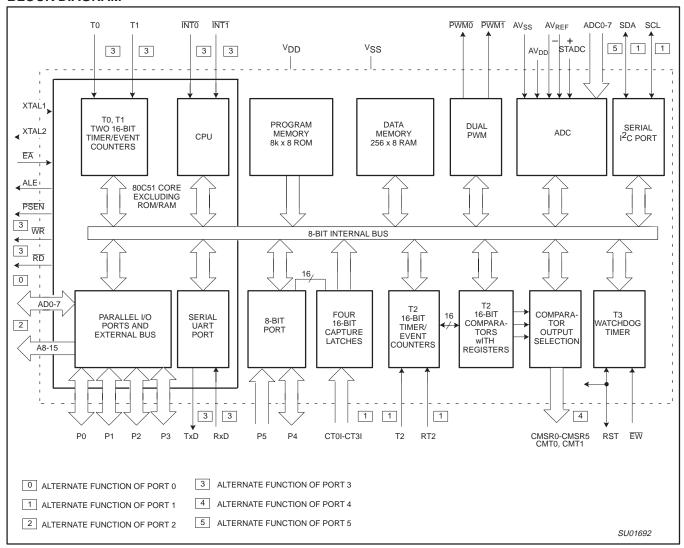

The 80C552/83C552 (hereafter generically referred to as 8XC552) Single-Chip 8-Bit Microcontroller is manufactured in an advanced CMOS process and is a derivative of the 80C51 microcontroller family. The 8XC552 has the same instruction set as the 80C51. Three versions of the derivative exist:

- 83C552—8 kbytes mask programmable ROM

- 80C552—ROMless version of the 83C552

- 87C552—8 kbytes EPROM (described in a separate chapter)

The 8XC552 contains a non-volatile  $8k \times 8$  read-only program memory (83C552), a volatile  $256 \times 8$  read/write data memory, five 8-bit I/O ports, one 8-bit input port, two 16-bit timer/event counters (identical to the timers of the 80C51), an additional 16-bit timer coupled to capture and compare latches, a 15-source, two-priority-level, nested interrupt structure, an 8-input ADC, a dual DAC pulse width modulated interface, two serial interfaces (UART and I²C-bus), a "watchdog" timer and on-chip oscillator and timing circuits. For systems that require extra capability, the 8XC552 can be expanded using standard TTL compatible memories and logic.

In addition, the 8XC552 has two software selectable modes of power reduction—idle mode and power-down mode. The idle mode freezes the CPU while allowing the RAM, timers, serial ports, and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative.

The device also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities. The instruction set consists of over 100 instructions: 49 one-byte, 45 two-byte, and 17 three-byte. With a 16 MHz (24 MHz) crystal, 58% of the instructions are executed in 0.75  $\mu s$  (0.5  $\mu s$ ) and 40% in 1.5  $\mu s$  (1  $\mu s$ ). Multiply and divide instructions require 3  $\mu s$  (2  $\mu s$ ).

#### **FEATURES**

- 80C51 central processing unit

- 8k × 8 ROM expandable externally to 64 kbytes

- ROM code protection

- An additional 16-bit timer/counter coupled to four capture registers and three compare registers

- Two standard 16-bit timer/counters

- 256 × 8 RAM, expandable externally to 64 kbytes

- · Capable of producing eight synchronized, timed outputs

- A 10-bit ADC with eight multiplexed analog inputs

- Two 8-bit resolution, pulse width modulation outputs

- Five 8-bit I/O ports plus one 8-bit input port shared with analog inputs

- I<sup>2</sup>C-bus serial I/O port with byte oriented master and slave functions

- Full-duplex UART compatible with the standard 80C51

- On-chip watchdog timer

- Three speed ranges:

- 3.5 to 16 MHz

- 3.5 to 24 MHz (ROM, ROMless only)

- Three operating ambient temperature ranges:

- P83C552xBx: 0 °C to +70 °C

- P83C552xFx: -40 °C to +85 °C (XTAL frequency max. 24 MHz)

- P83C552xHx: -40 °C to +125 °C (XTAL frequency max. 16 MHz)

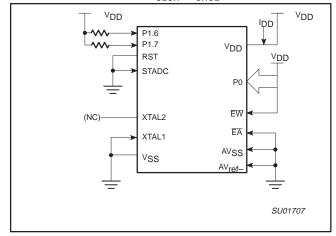

#### **LOGIC SYMBOL**

Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

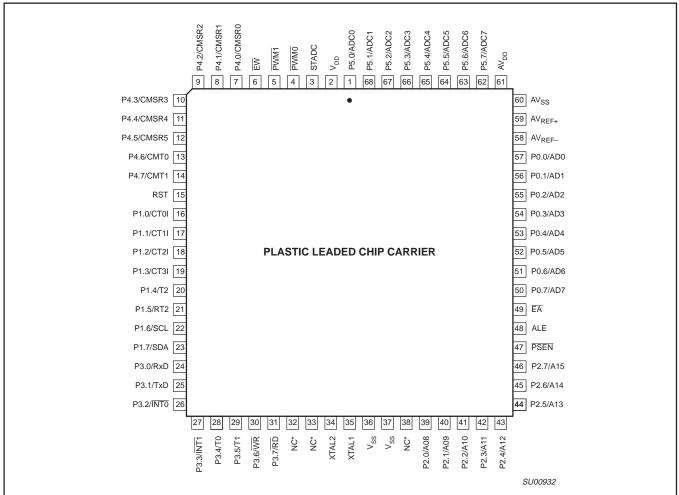

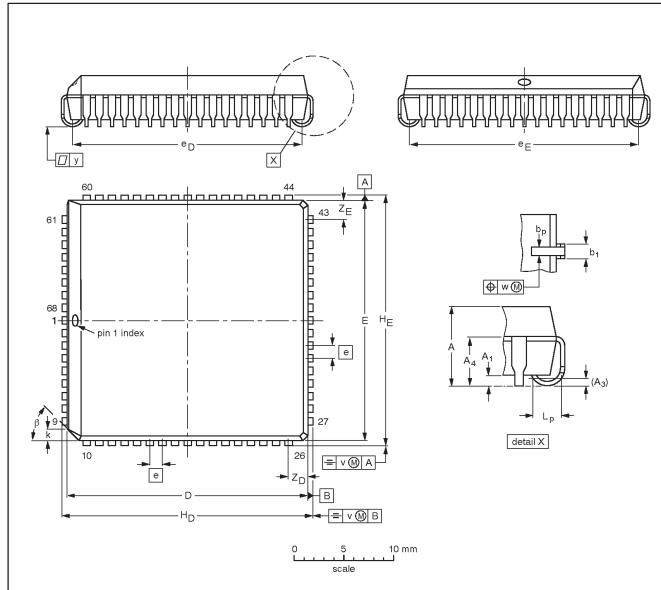

#### PIN CONFIGURATIONS

### **Plastic Leaded Chip Carrier**

<sup>\*</sup> Do not connect.

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

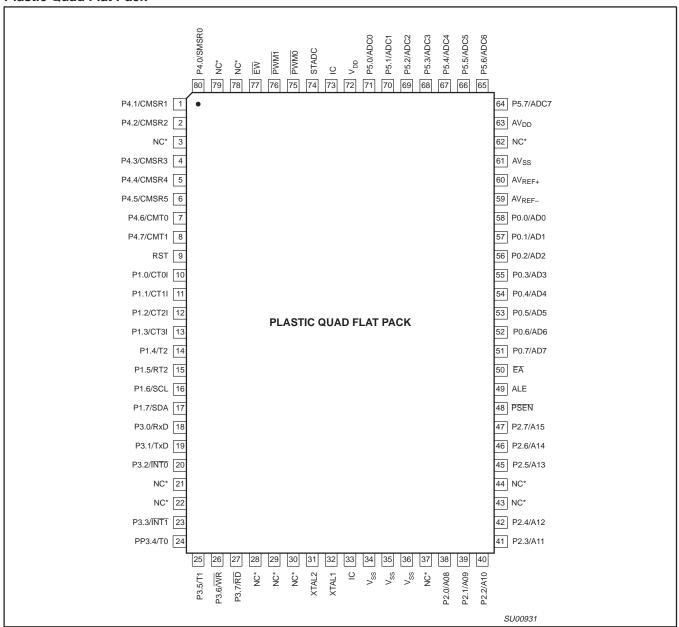

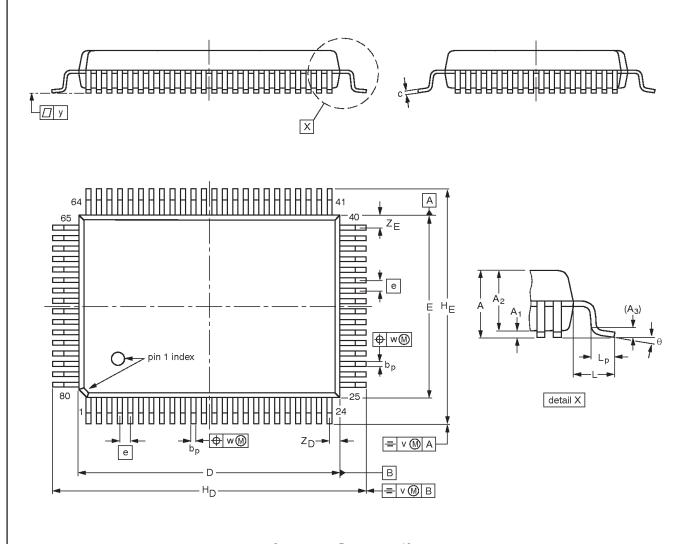

#### **Plastic Quad Flat Pack**

<sup>\*</sup> Do not connect.

IC = Internally connected (do not use).

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

### **BLOCK DIAGRAM**

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

#### **ORDERING INFORMATION**

| PHILIPS PART ORDER NUMBER PART MARKING |                  | DRAWING<br>NUMBER | TEMPERATURE (°C) AND PACKAGE                | FREQ<br>(MHz) |

|----------------------------------------|------------------|-------------------|---------------------------------------------|---------------|

| ROMIess                                | ROM <sup>1</sup> |                   |                                             |               |

| P80C552EBA                             | P83C552EBA/xxx   | SOT188-2          | 0 to +70,<br>Plastic Leaded Chip Carrier    | 16            |

| P80C552EBB                             | P83C552EBB/xxx   | SOT318-2          | 0 to +70,<br>Plastic Quad Flat Pack         | 16            |

| P80C552EFA                             | P83C552EFA/xxx   | SOT188-2          | −40 to +85,<br>Plastic Leaded Chip Carrier  | 16            |

| P80C552EFB                             | P83C552EFB/xxx   | SOT318-2          | -40 to +85,<br>Plastic Quad Flat Pack       | 16            |

| P80C552EHA                             | P83C552EHA/xxx   | SOT188-2          | −40 to +125,<br>Plastic Leaded Chip Carrier | 16            |

| P80C552EHB                             | P83C552EHB/xxx   | SOT318-2          | −40 to +125,<br>Plastic Quad Flat Pack      | 16            |

| P80C552IBA                             | P83C552IBA/xxx   | SOT188-2          | 0 to +70,<br>Plastic Leaded Chip Carrier    | 24            |

| P80C552IBB                             | P83C552IBB/xxx   | SOT318-2          | 0 to +70,<br>Plastic Quad Flat Pack         | 24            |

| P80C552IFA                             | P83C552IFA/xxx   | SOT188-2          | −40 to +85,<br>Plastic Leaded Chip Carrier  | 24            |

| P80C552IFB                             | P83C552IFB/xxx   | SOT318-2          | -40 to +85,<br>Plastic Quad Flat Pack       | 24            |

xxx denotes the ROM code number.

For EPROM device specification, refer to 87C552 datasheet.

# Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

### **PIN DESCRIPTION**

| PIN NO.   |             |                 |      |                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------|-------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MNEMONIC  | PLCC        | QFP             | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                       |  |

| $V_{DD}$  | 2           | 72              | ı    | <b>Digital Power Supply:</b> +5 V power supply pin during normal operation, idle and power-down mode.                                                                                                                                                                                                                                                   |  |

| STADC     | 3           | 74              | ı    | Start ADC Operation: Input starting analog to digital conversion (ADC operation can also be started by software). This pin must not float.                                                                                                                                                                                                              |  |

| PWM0      | 4           | 75              | 0    | Pulse Width Modulation: Output 0.                                                                                                                                                                                                                                                                                                                       |  |

| PWM1      | 5           | 76              | 0    | Pulse Width Modulation: Output 1.                                                                                                                                                                                                                                                                                                                       |  |

| EW        | 6           | 77              | ı    | <b>Enable Watchdog Timer:</b> Enable for T3 watchdog timer and disable power-down mode. This pin must not float.                                                                                                                                                                                                                                        |  |

| P0.0-P0.7 | 57-50       | 58-51           | I/O  | <b>Port 0:</b> Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application it uses strong internal pull-ups when emitting 1s. |  |

| P1.0-P1.7 | 16-23       | 10-17           | I/O  | Port 1: 8-bit I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                    |  |

|           | 16-21       | 10-15           | I/O  | (P1.0-P1.5): Quasi-bidirectional port pins.                                                                                                                                                                                                                                                                                                             |  |

|           | 22-23       | 16-17           | I/O  | (P1.6, P1.7): Open drain port pins.                                                                                                                                                                                                                                                                                                                     |  |

|           | 16-19       | 10-13           |      | CT0I-CT3I (P1.0-P1.3): Capture timer input signals for timer T2.                                                                                                                                                                                                                                                                                        |  |

|           | 20          | 14              |      | T2 (P1.4): T2 event input.                                                                                                                                                                                                                                                                                                                              |  |

|           | 21          | 15              |      | RT2 (P1.5): T2 timer reset signal. Rising edge triggered.                                                                                                                                                                                                                                                                                               |  |

|           | 22          | 16              | 1/0  | SCL (P1.6): Serial port clock line l <sup>2</sup> C-bus.                                                                                                                                                                                                                                                                                                |  |

|           | 23          | 17              | I/O  | SDA (P1.7): Serial port data line I <sup>2</sup> C-bus.  Port 1 is also used to input the lower order address byte during EPROM programming and verification. A0 is on P1.0, etc.                                                                                                                                                                       |  |

| P2.0-P2.7 | 39-46       | 38-42,<br>45-47 | I/O  | Port 2: 8-bit quasi-bidirectional I/O port. Alternate function: High-order address byte for external memory (A08-A15).                                                                                                                                                                                                                                  |  |

| P3.0-P3.7 | 24-31       | 18-20,<br>23-27 | I/O  | Port 3: 8-bit quasi-bidirectional I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                |  |

|           | 24          | 18              |      | RxD(P3.0): Serial input port.                                                                                                                                                                                                                                                                                                                           |  |

|           | 25          | 19              | 1    | TxD (P3.1): Serial output port.                                                                                                                                                                                                                                                                                                                         |  |

|           | 26          | 20              | l    | INTO (P3.2): External interrupt.                                                                                                                                                                                                                                                                                                                        |  |

|           | 27          | 23              | l    | INT1 (P3.3): External interrupt.                                                                                                                                                                                                                                                                                                                        |  |

|           | 28          | 24              | l    | T0 (P3.4): Timer 0 external input.                                                                                                                                                                                                                                                                                                                      |  |

|           | 29          | 25              |      | T1 (P3.5): Timer 1 external input.                                                                                                                                                                                                                                                                                                                      |  |

|           | 30          | 26              | l    | WR (P3.6): External data memory write strobe.                                                                                                                                                                                                                                                                                                           |  |

|           | 31          | 27              |      | RD (P3.7): External data memory read strobe.                                                                                                                                                                                                                                                                                                            |  |

| P4.0-P4.7 | 7-14        | 80, 1-2<br>4-8  | I/O  | Port 4: 8-bit quasi-bidirectional I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                |  |

|           | 7-12        | 80, 1-2<br>4-6  | 0    | CMSR0-CMSR5 (P4.0-P4.5): Timer T2 compare and set/reset outputs on a match with timer T2.                                                                                                                                                                                                                                                               |  |

|           | 13, 14      | 7, 8            | 0    | CMT0, CMT1 (P4.6, P4.7): Timer T2 compare and toggle outputs on a match with timer T2.                                                                                                                                                                                                                                                                  |  |

| P5.0-P5.7 | 68-62,<br>1 | 71-64,          | ı    | Port 5: 8-bit input port.  ADC0-ADC7 (P5.0-P5.7): Alternate function: Eight input channels to ADC.                                                                                                                                                                                                                                                      |  |

| RST       | 15          | 9               | I/O  | Reset: Input to reset the 8XC552. It also provides a reset pulse as output when timer T3 overflows.                                                                                                                                                                                                                                                     |  |

| XTAL1     | 35          | 32              | ı    | <b>Crystal Input 1:</b> Input to the inverting amplifier that forms the oscillator, and input to the internal clock generator. Receives the external clock signal when an external oscillator is used.                                                                                                                                                  |  |

| XTAL2     | 34          | 31              | 0    | Crystal Input 2: Output of the inverting amplifier that forms the oscillator. Left open-circuit when an external clock is used.                                                                                                                                                                                                                         |  |

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

#### PIN DESCRIPTION (Continued)

|                    | PIN    | NO.   |      |                                                                                                                                                                                                                                                                                                           |

|--------------------|--------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | PLCC   | QFP   | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub>    | 36, 37 | 34-36 | ı    | Two Digital ground pins.                                                                                                                                                                                                                                                                                  |

| PSEN               | 47     | 48    | 0    | Program Store Enable: Active-low read strobe to external program memory.                                                                                                                                                                                                                                  |

| ALE                | 48     | 49    | 0    | Address Latch Enable: Latches the low byte of the address during accesses to external memory. It is activated every six oscillator periods. During an external data memory access, one ALE pulse is skipped. ALE can drive up to eight LS TTL inputs and handles CMOS inputs without an external pull-up. |

| EA                 | 49     | 50    | I    | External Access: When EA is held at TTL level high, the CPU executes out of the internal program ROM provided the program counter is less than 8192. When EA is held at TTL low level, the CPU executes out of external program memory. EA is not allowed to float.                                       |

| AV <sub>REF</sub>  | 58     | 59    | ı    | Analog to Digital Conversion Reference Resistor: Low-end.                                                                                                                                                                                                                                                 |

| AV <sub>REF+</sub> | 59     | 60    | 1    | Analog to Digital Conversion Reference Resistor: High-end.                                                                                                                                                                                                                                                |

| AV <sub>SS</sub>   | 60     | 61    | 1    | Analog Ground                                                                                                                                                                                                                                                                                             |

| $AV_{DD}$          | 61     | 63    | I    | Analog Power Supply                                                                                                                                                                                                                                                                                       |

#### NOTE:

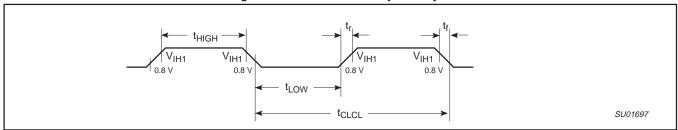

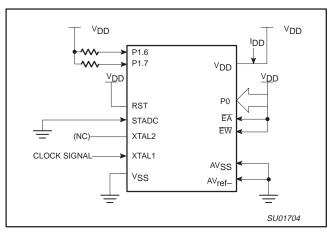

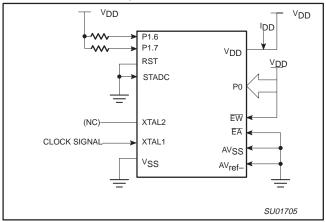

#### OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol, page 2.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

#### **RESET**

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-on reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. At power-on, the voltage on  $V_{DD}$  and RST must come up at the same time for a proper start-up.

#### **IDLE MODE**

In the idle mode, the CPU puts itself to sleep while some of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt

service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

#### **POWER-DOWN MODE**

In the power-down mode, the oscillator is stopped and the instruction to invoke power-down is the last instruction executed. Only the contents of the on-chip RAM are preserved. A hardware reset is the only way to terminate the power-down mode. The control bits for the reduced power modes are in the special function register PCON. Table 1 shows the state of the I/O ports during low current operating modes.

#### **ROM CODE PROTECTION (83C552)**

The 83C552 has an additional security feature. ROM code protection may be selected by setting a mask–programmable security bit (i.e., user dependent). This feature may be requested during ROM code submission. When selected, the ROM code is protected and cannot be read out at any time by any test mode or by any instruction in the external program memory space.

The MOVC instructions are the only instructions that have access to program code in the internal or external program memory. The  $\overline{\text{EA}}$  input is latched during RESET and is "don't care" after RESET (also if the security bit is not set). This implementation prevents reading internal program code by switching from external program memory to internal program memory during a MOVC instruction or any other instruction that uses immediate data.

Table 1. External Pin Status During Idle and Power-Down Modes

| MODE       | PROGRAM<br>MEMORY | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 | PORT 4 | PWM0/<br>PWM1 |

|------------|-------------------|-----|------|--------|--------|---------|--------|--------|---------------|

| Idle       | Internal          | 1   | 1    | Data   | Data   | Data    | Data   | Data   | 1             |

| Idle       | External          | 1   | 1    | Float  | Data   | Address | Data   | Data   | 1             |

| Power-down | Internal          | 0   | 0    | Data   | Data   | Data    | Data   | Data   | 1             |

| Power-down | External          | 0   | 0    | Float  | Data   | Data    | Data   | Data   | 1             |

To avoid "latch-up" effect at power-on, the voltage on any pin at any time must not be higher or lower than V<sub>DD</sub> + 0.5 V or V<sub>SS</sub> – 0.5 V, respectively.

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

Serial Control Register (S1CON) – See Table 2

S1CON (D8H) CR2 ENS1 STA STO SI AA CR1 CR0

Bits CR0, CR1 and CR2 determine the serial clock frequency that is generated in the master mode of operation.

#### **Table 2. Serial Clock Rates**

|     |     |     | BIT FREQUENCY (kHz) AT f <sub>OSC</sub> |             |                  |                     |                                            |

|-----|-----|-----|-----------------------------------------|-------------|------------------|---------------------|--------------------------------------------|

| CR2 | CR1 | CR0 | 6 MHZ                                   | 12 MHz      | 16 MHz           | 24 MHz <sup>2</sup> | f <sub>OSC</sub> DIVIDED BY                |

| 0   | 0   | 0   | 23                                      | 47          | 62.5             | 94                  | 256                                        |

| 0   | 0   | 1   | 27                                      | 54          | 71               | 107 <sup>1</sup>    | 224                                        |

| 0   | 1   | 0   | 31                                      | 63          | 83.3             | 125 <sup>1</sup>    | 192                                        |

| 0   | 1   | 1   | 37                                      | 75          | 100              | 150 <sup>1</sup>    | 160                                        |

| 1   | 0   | 0   | 6.25                                    | 12.5        | 17               | 25                  | 960                                        |

| 1   | 0   | 1   | 50                                      | 100         | 133 <sup>1</sup> | 200 1               | 120                                        |

| 1   | 1   | 0   | 100                                     | 200         | 267 <sup>1</sup> | 400 <sup>1</sup>    | 60                                         |

| 1   | 1   | 1   | 0.24 < 62.5                             | 0.49 < 62.5 | 0.65 < 55.6      | 0.98 < 50.0         | $96 \times (256 - (reload value Timer 1))$ |

|     |     |     | 0 < 255                                 | 0 < 254     | 0 < 253          | 0 <251              | reload value Timer 1 in Mode 2.            |

#### NOTES:

1. These frequencies exceed the upper limit of 100kHz of the I<sup>2</sup>C-bus specification and cannot be used in an I<sup>2</sup>C-bus application.

2. At f<sub>OSC</sub> = 24 MHz the maximum I<sup>2</sup>C bus rate of 100kHz cannot be realized due to the fixed divider rates.

### **ABSOLUTE MAXIMUM RATINGS**1, 2, 3

| PARAMETER                                                                                    | RATING       | UNIT |

|----------------------------------------------------------------------------------------------|--------------|------|

| Storage temperature range                                                                    | -65 to +150  | °C   |

| Voltage on any other pin to V <sub>SS</sub>                                                  | -0.5 to +6.5 | V    |

| Input, output DC current on any single I/O pin                                               | 5.0          | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.0          | W    |

#### NOTES:

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

- 2. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

- 3. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted

#### **DEVICE SPECIFICATIONS**

|               | SUPPLY VO | SUPPLY VOLTAGE (V) |     | ICY (MHz) |                        |

|---------------|-----------|--------------------|-----|-----------|------------------------|

| TYPE          | MIN       | MAX                | MIN | MAX       | TEMPERATURE RANGE (°C) |

| P83(0)C552EBx | 4.5       | 5.5                | 3.5 | 16        | 0 to +70               |

| P83(0)C552EFx | 4.5       | 5.5                | 3.5 | 16        | -40 to +85             |

| P83(0)C552EHx | 4.5       | 5.5                | 3.5 | 16        | -40 to +125            |

| P83(0)C552IBx | 4.5       | 5.5                | 3.5 | 24        | 0 to +70               |

| P83(0)C552IFx | 4.5       | 5.5                | 3.5 | 24        | -40 to +85             |

# Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

#### DC ELECTRICAL CHARACTERISTICS

$V_{SS}$ ,  $AV_{SS} = 0 \text{ V}$ ;  $V_{DD}$ ,  $AV_{DD} = 5 \text{ V} \pm 10\%$

|                   |                                                                                                                        | TEST                                                                                                                                                               | LIM                                              | IITS                          |                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------|----------------------|

| SYMBOL            | PARAMETER                                                                                                              | CONDITIONS                                                                                                                                                         | MIN                                              | MAX                           | UNIT                 |

| I <sub>DD</sub>   | Supply current operating:  P83(0)C552EBx  P83(0)C552EFx  P83(0)C552EHx  P83(0)C552IBx  P83(0)C552IFx                   | See notes 1 and 2<br>f <sub>OSC</sub> = 16 MHz<br>f <sub>OSC</sub> = 16 MHz<br>f <sub>OSC</sub> = 16 MHz<br>f <sub>OSC</sub> = 24 MHz<br>f <sub>OSC</sub> = 24 MHz |                                                  | 45<br>45<br>40<br>55<br>55    | mA<br>mA<br>mA<br>mA |

| I <sub>ID</sub>   | Idle mode:     P83(0)C552EBx     P83(0)C552EFx     P83(0)C552EHx     P83(0)C552EHx     P83(0)C552IBx     P83(0)C552IFx | See notes 1 and 3<br>fosc = 16 MHz<br>fosc = 16 MHz<br>fosc = 16 MHz<br>fosc = 24 MHz<br>fosc = 24 MHz                                                             |                                                  | 10<br>10<br>9<br>12.5<br>12.5 | mA<br>mA<br>mA<br>mA |

| I <sub>PD</sub>   | Power-down current:  P83(0)C552xBx  P83(0)C552xFx  P83(0)C552xHx                                                       | See notes 1 and 4;<br>2 V < V <sub>PD</sub> < V <sub>DD</sub> max                                                                                                  |                                                  | 50<br>50<br>150               | μΑ<br>μΑ<br>μΑ       |

| Inputs            |                                                                                                                        |                                                                                                                                                                    |                                                  |                               |                      |

| $V_{IL}$          | Input low voltage, except EA, P1.6, P1.7                                                                               |                                                                                                                                                                    | -0.5                                             | 0.2V <sub>DD</sub> -0.1       | V                    |

| $V_{IL1}$         | Input low voltage to EA                                                                                                |                                                                                                                                                                    | -0.5                                             | 0.2V <sub>DD</sub> -0.3       | V                    |

| $V_{IL2}$         | Input low voltage to P1.6/SCL, P1.7/SDA <sup>5</sup>                                                                   |                                                                                                                                                                    | -0.5                                             | 0.3V <sub>DD</sub>            | V                    |

| V <sub>IH</sub>   | Input high voltage, except XTAL1, RST, P1.6/SCL, P1.7/SDA                                                              |                                                                                                                                                                    | 0.2V <sub>DD</sub> +0.9                          | V <sub>DD</sub> +0.5          | V                    |

| V <sub>IH1</sub>  | Input high voltage, XTAL1, RST                                                                                         |                                                                                                                                                                    | 0.7V <sub>DD</sub>                               | V <sub>DD</sub> +0.5          | V                    |

| $V_{\text{IH2}}$  | Input high voltage, P1.6/SCL, P1.7/SDA <sup>5</sup>                                                                    |                                                                                                                                                                    | 0.7V <sub>DD</sub>                               | 6.0                           | V                    |

| I <sub>IL</sub>   | Logical 0 input current, ports 1, 2, 3, 4, except P1.6, P1.7                                                           | V <sub>IN</sub> = 0.45 V                                                                                                                                           |                                                  | <b>-</b> 50                   | μΑ                   |

| $I_{TL}$          | Logical 1-to-0 transition current, ports 1, 2, 3, 4, except P1.6, P1.7                                                 | See note 6                                                                                                                                                         |                                                  | -650                          | μΑ                   |

| ±I <sub>IL1</sub> | Input leakage current, port 0, EA, STADC, EW                                                                           | $0.45 \text{ V} < \text{V}_{\text{I}} < \text{V}_{\text{DD}}$                                                                                                      |                                                  | 10                            | μΑ                   |

| ±l <sub>IL2</sub> | Input leakage current, P1.6/SCL, P1.7/SDA                                                                              | 0 V < V <sub>I</sub> < 6 V<br>0 V < V <sub>DD</sub> < 5.5 V                                                                                                        |                                                  | 10                            | μΑ                   |

| $\pm I_{IL3}$     | Input leakage current, port 5                                                                                          | 0.45 V < V <sub>I</sub> < V <sub>DD</sub>                                                                                                                          |                                                  | 1                             | μΑ                   |

| Outputs           |                                                                                                                        |                                                                                                                                                                    |                                                  |                               |                      |

| $V_{OL}$          | Output low voltage, ports 1, 2, 3, 4, except P1.6, P1.7                                                                | $I_{OL} = 1.6 \text{mA}^7$                                                                                                                                         |                                                  | 0.45                          | V                    |

| $V_{OL1}$         | Output low voltage, port 0, ALE, PSEN, PWM0, PWM1                                                                      | $I_{OL} = 3.2 \text{mA}^7$                                                                                                                                         |                                                  | 0.45                          | V                    |

| $V_{OL2}$         | Output low voltage, P1.6/SCL, P1.7/SDA                                                                                 | $I_{OL} = 3.0 \text{mA}^7$                                                                                                                                         |                                                  | 0.4                           | V                    |

| V <sub>OH</sub>   | Output high voltage, ports 1, 2, 3, 4, except P1.6/SCL, P1.7/SDA                                                       | -l <sub>OH</sub> = 60μA<br>-l <sub>OH</sub> = 25μA<br>-l <sub>OH</sub> = 10μA                                                                                      | 2.4<br>0.75V <sub>DD</sub><br>0.9V <sub>DD</sub> |                               | V<br>V<br>V          |

| V <sub>OH1</sub>  | Output high voltage (port 0 in external bus mode, ALE, PSEN, PWM0, PWM1)8                                              | -I <sub>OH</sub> = 400μA<br>-I <sub>OH</sub> = 150μA<br>-I <sub>OH</sub> = 40μA                                                                                    | 2.4<br>0.75V <sub>DD</sub><br>0.9V <sub>DD</sub> |                               | V<br>V<br>V          |

| V <sub>OH2</sub>  | Output high voltage (RST)                                                                                              | −l <sub>OH</sub> = 400μA<br>−l <sub>OH</sub> = 120μA                                                                                                               | 2.4<br>0.8V <sub>DD</sub>                        |                               | V<br>V               |

| R <sub>RST</sub>  | Internal reset pull-down resistor                                                                                      |                                                                                                                                                                    | 50                                               | 150                           | kΩ                   |

| C <sub>IO</sub>   | Pin capacitance                                                                                                        | Test freq = 1 MHz,<br>T <sub>amb</sub> = 25 °C                                                                                                                     |                                                  | 10                            | pF                   |

### Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

#### DC ELECTRICAL CHARACTERISTICS (Continued)

|                   |                                                                                          | TEST                                                   | LIN                   | IITS                        | ]                    |  |

|-------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------|-----------------------------|----------------------|--|

| SYMBOL            | PARAMETER                                                                                | CONDITIONS                                             | MIN                   | MAX                         | UNIT                 |  |

| Analog In         | outs                                                                                     | -                                                      |                       |                             |                      |  |

| Al <sub>DD</sub>  | Analog supply current: operating: (16 MHz)<br>Analog supply current: operating: (24 MHz) | Port $5 = 0$ to $AV_{DD}$<br>Port $5 = 0$ to $AV_{DD}$ |                       | 1.2<br>1.0                  | mA<br>mA             |  |

| Al <sub>ID</sub>  | Idle mode: P83(0)C552EBx P83(0)C552EFx P83(0)C552EHx P83(0)C552IBx P83(0)C552IFx         |                                                        |                       | 50<br>50<br>100<br>50<br>50 | µА<br>µА<br>µА<br>µА |  |

| Al <sub>PD</sub>  | Power-down mode:  P83(0)C552xBx P83(0)C552xFx P83(0)C552xHx                              | 2 V < AV <sub>PD</sub> < AV <sub>DD</sub><br>max       |                       | 50<br>50<br>100             | μΑ<br>μΑ<br>μΑ       |  |

| AV <sub>IN</sub>  | Analog input voltage                                                                     |                                                        | AV <sub>SS</sub> -0.2 | AV <sub>DD</sub> +0.2       | V                    |  |

| AV <sub>REF</sub> | Reference voltage:  AV <sub>REF</sub> -  AV <sub>REF+</sub>                              |                                                        | AV <sub>SS</sub> -0.2 | AV <sub>DD</sub> +0.2       | V                    |  |

| R <sub>REF</sub>  | Resistance between AV <sub>REF+</sub> and AV <sub>REF-</sub>                             |                                                        | 10                    | 50                          | kΩ                   |  |

| C <sub>IA</sub>   | Analog input capacitance                                                                 |                                                        |                       | 15                          | pF                   |  |

| t <sub>ADS</sub>  | Sampling time                                                                            |                                                        |                       | 8t <sub>CY</sub>            | μs                   |  |

| t <sub>ADC</sub>  | Conversion time (including sampling time)                                                |                                                        |                       | 50t <sub>CY</sub>           | μs                   |  |

| DL <sub>e</sub>   | Differential non-linearity <sup>10, 11, 12</sup>                                         |                                                        |                       | ±1                          | LSB                  |  |

| ILe               | Integral non-linearity <sup>10, 13</sup>                                                 |                                                        |                       | ±2                          | LSB                  |  |

| OS <sub>e</sub>   | Offset error <sup>10, 14</sup>                                                           |                                                        |                       | ±2                          | LSB                  |  |

| G <sub>e</sub>    | Gain error <sup>10, 15</sup>                                                             |                                                        |                       | ±0.4                        | %                    |  |

| A <sub>e</sub>    | Absolute voltage error <sup>10, 16</sup>                                                 |                                                        |                       | ±3                          | LSB                  |  |

| M <sub>CTC</sub>  | Channel to channel matching                                                              |                                                        |                       | ±1                          | LSB                  |  |

| Ct                | Crosstalk between inputs of port 5 <sup>17</sup>                                         | 0-100kHz                                               |                       | -60                         | dB                   |  |

#### NOTES FOR DC ELECTRICAL CHARACTERISTICS:

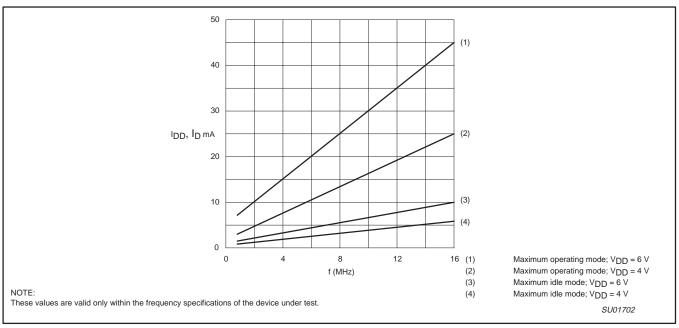

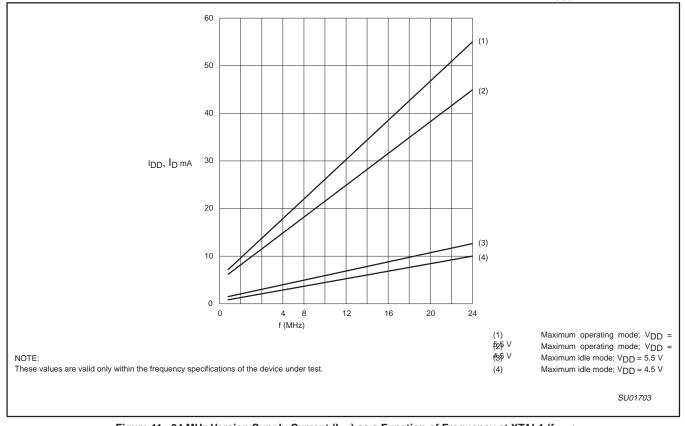

- See Figures 10 through 15 for I<sub>DD</sub> test conditions.

- 2. The operating supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r = t_f = 10$  ns;  $V_{IL} = V_{SS} + 0.5$  V;  $V_{IH} = V_{DD} - 0.5 \text{ V}$ ; XTAL2 not connected;  $\overline{EA} = RST = Port 0 = \overline{EW} = V_{DD}$ ; STADC =  $V_{SS}$ .

- The idle mode supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r = t_f = 10$  ns;  $V_{IL} = V_{SS} + 0.5$  V;  $V_{IH} = V_{DD} - 0.5 \text{ V}$ ; XTAL2 not connected; Port  $0 = \overline{EW} = V_{DD}$ ;  $\overline{EA} = RST = STADC = V_{SS}$ .

- The power-down current is measured with all output pins disconnected; XTAL2 not connected; Port  $0 = \overline{EW} = V_{DD}$ ;

- EA = RST = STADC = XTAL1 = V<sub>SS</sub>.

5. The input threshold voltage of P1.6 and P1.7 (SIO1) meets the I<sup>2</sup>C specification, so an input voltage below 1.5 V will be recognized as a logic 0 while an input voltage above 3.0 V will be recognized as a logic 1.

- Pins of ports 1 (except P1.6, P1.7), 2, 3, and 4 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2 V.

- Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the V<sub>OL</sub>s of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8 V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. I<sub>OL</sub> can exceed these conditions provided that no single output sinks more than 5mA and no more than two outputs exceed the test conditions.

8. Capacitive loading on ports 0 and 2 may cause the V<sub>OH</sub> on ALE and PSEN to momentarily fall below the 0.9 V<sub>DD</sub> specification when the

- address bits are stabilizing.

- The following condition must not be exceeded:  $V_{DD} 0.2 \text{ V} < AV_{DD} < V_{DD} + 0.2 \text{ V}$ .

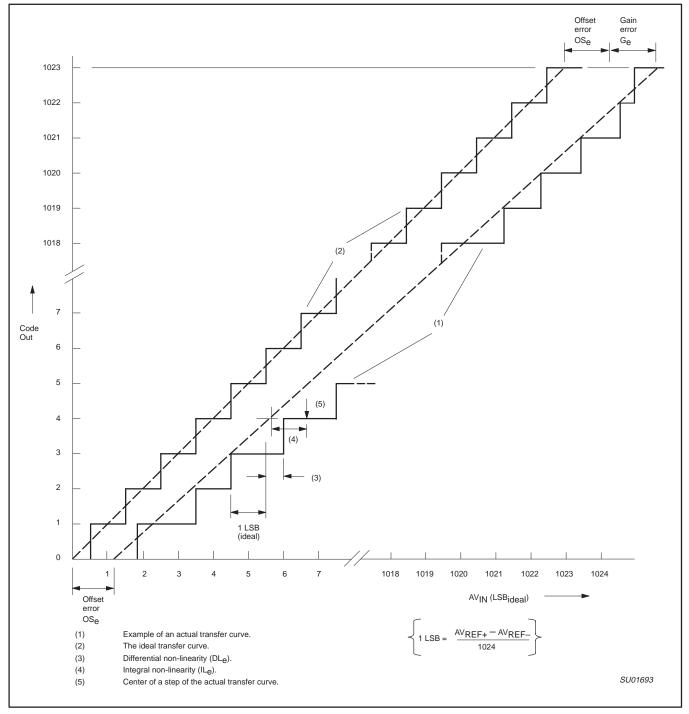

- 10. Conditions: AV<sub>REF</sub> = 0 V; AV<sub>DD</sub> = 5.0 V, AV<sub>REF</sub> (80C552, 83C552) = 5.12 V. ADC is monotonic with no missing codes. Measurement by continuous conversion of AV<sub>IN</sub> = -20 mV to 5.12 V in steps of 0.5 mV.

11. The differential non-linearity (DL<sub>e</sub>) is the difference between the actual step width and the ideal step width. (See Figure 1.)

- 12. The ADC is monotonic; there are no missing codes.

- 13. The integral non-linearity (ILe) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset error. (See Figure 1.)

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

- 14. The offset error (OS<sub>e</sub>) is the absolute difference between the straight line which fits the actual transfer curve (after removing gain error), and a straight line which fits the ideal transfer curve. (See Figure 1.)

- 15. The gain error (G<sub>e</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve (after removing offset error), and the straight line which fits the ideal transfer curve. Gain error is constant at every point on the transfer curve. (See Figure 1.)

- 16. The absolute voltage error (A<sub>e</sub>) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve.

- 17. This should be considered when both analog and digital signals are simultaneously input to port 5.

Figure 1. ADC Conversion Characteristic

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

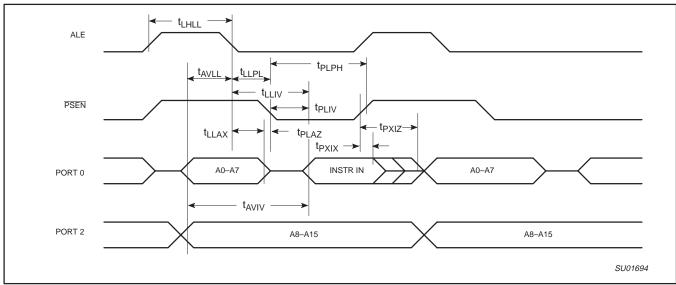

#### AC ELECTRICAL CHARACTERISTICS<sup>1, 2</sup>

16 MHz version

|                     |              |                                                                  | 16 MH:                       | z CLOCK            | VARIABL                  | E CLOCK                  |      |

|---------------------|--------------|------------------------------------------------------------------|------------------------------|--------------------|--------------------------|--------------------------|------|

| SYMBOL              | FIGURE       | PARAMETER                                                        | MIN                          | MAX                | MIN                      | MAX                      | UNIT |

| 1/t <sub>CLCL</sub> | 2            | Oscillator frequency                                             |                              |                    | 3.5                      | 16                       | MHz  |

| t <sub>LHLL</sub>   | 2            | ALE pulse width                                                  | 85                           |                    | 2t <sub>CLCL</sub> -40   |                          | ns   |

| t <sub>AVLL</sub>   | 2            | Address valid to ALE low                                         | 8                            |                    | t <sub>CLCL</sub> -55    |                          | ns   |

| t <sub>LLAX</sub>   | 2            | Address hold after ALE low                                       | 28                           |                    | t <sub>CLCL</sub> -35    |                          | ns   |

| t <sub>LLIV</sub>   | 2            | ALE low to valid instruction in                                  |                              | 150                |                          | 4t <sub>CLCL</sub> -100  | ns   |

| t <sub>LLPL</sub>   | 2            | ALE low to PSEN low                                              | 23                           |                    | t <sub>CLCL</sub> -40    |                          | ns   |

| t <sub>PLPH</sub>   | 2            | PSEN pulse width                                                 | 143                          |                    | 3t <sub>CLCL</sub> -45   |                          | ns   |

| t <sub>PLIV</sub>   | 2            | PSEN low to valid instruction in                                 |                              | 83                 |                          | 3t <sub>CLCL</sub> -105  | ns   |

| t <sub>PXIX</sub>   | 2            | Input instruction hold after PSEN                                | 0                            |                    | 0                        |                          | ns   |

| t <sub>PXIZ</sub>   | 2            | Input instruction float after PSEN                               |                              | 38                 |                          | t <sub>CLCL</sub> -25    | ns   |

| t <sub>AVIV</sub>   | 2            | Address to valid instruction in                                  |                              | 208                |                          | 5t <sub>CLCL</sub> -105  | ns   |

| t <sub>PLAZ</sub>   | 2            | PSEN low to address float                                        |                              | 10                 |                          | 10                       | ns   |

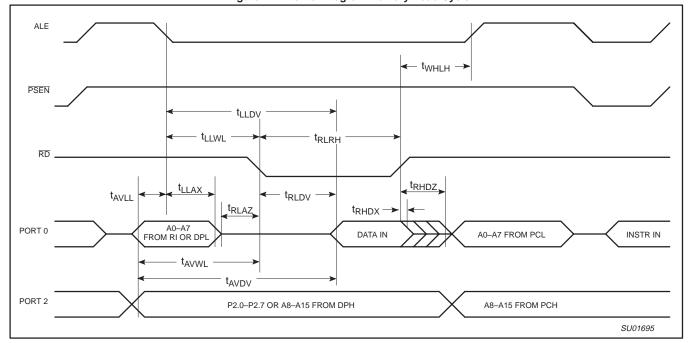

| Data Memo           | ory          |                                                                  |                              | •                  |                          |                          |      |

| t <sub>RLRH</sub>   | 3            | RD pulse width                                                   | 275                          |                    | 6t <sub>CLCL</sub> -100  |                          | ns   |

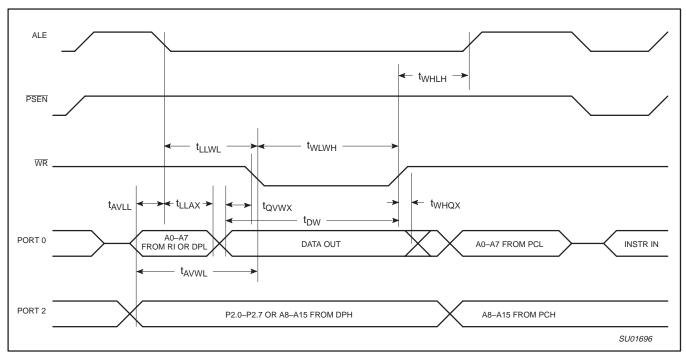

| t <sub>WLWH</sub>   | 4            | WR pulse width                                                   | 275                          |                    | 6t <sub>CLCL</sub> -100  |                          | ns   |

| t <sub>RLDV</sub>   | 3            | RD low to valid data in                                          |                              | 148                | 0202                     | 5t <sub>CLCL</sub> -165  | ns   |

| t <sub>RHDX</sub>   | 3            | Data hold after RD                                               | 0                            |                    | 0                        | 0202                     | ns   |

| t <sub>RHDZ</sub>   | 3            | Data float after RD                                              |                              | 55                 |                          | 2t <sub>CLCL</sub> -70   | ns   |

| t <sub>LLDV</sub>   | 3            | ALE low to valid data in                                         |                              | 350                |                          | 8t <sub>CLCL</sub> -150  | ns   |

| t <sub>AVDV</sub>   | 3            | Address to valid data in                                         |                              | 398                |                          | 9t <sub>CLCL</sub> -165  | ns   |

| t <sub>LLWL</sub>   | 3, 4         | ALE low to RD or WR low                                          | 138                          | 238                | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50   | ns   |

| t <sub>AVWL</sub>   | 3, 4         | Address valid to WR low or RD low                                | 120                          |                    | 4t <sub>CLCL</sub> -130  |                          | ns   |

| t <sub>QVWX</sub>   | 4            | Data valid to WR transition                                      | 3                            |                    | t <sub>CLCL</sub> -60    |                          | ns   |

| t <sub>DW</sub>     | 4            | Data before WR                                                   | 288                          |                    | 7t <sub>CLCL</sub> -150  |                          | ns   |

| twhqx               | 4            | Data hold after WR                                               | 13                           |                    | t <sub>CLCL</sub> -50    |                          | ns   |

| t <sub>RLAZ</sub>   | 3            | RD low to address float                                          |                              | 0                  |                          | 0                        | ns   |

| twhlh               | 3, 4         | RD or WR high to ALE high                                        | 23                           | 103                | t <sub>CLCL</sub> -40    | t <sub>CLCL</sub> +40    | ns   |

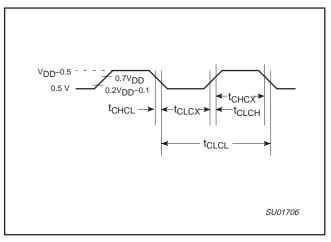

| External Cl         | ock          |                                                                  |                              | •                  |                          |                          |      |

| t <sub>CHCX</sub>   | 5            | High time <sup>4</sup>                                           | 20                           |                    | 20                       |                          | ns   |

| t <sub>CLCX</sub>   | 5            | Low time <sup>4</sup>                                            | 20                           |                    | 20                       |                          | ns   |

| tCLCH               | 5            | Rise time <sup>4</sup>                                           |                              | 20                 |                          | 20                       | ns   |

| t <sub>CHCL</sub>   | 5            | Fall time <sup>4</sup>                                           |                              | 20                 |                          | 20                       | ns   |

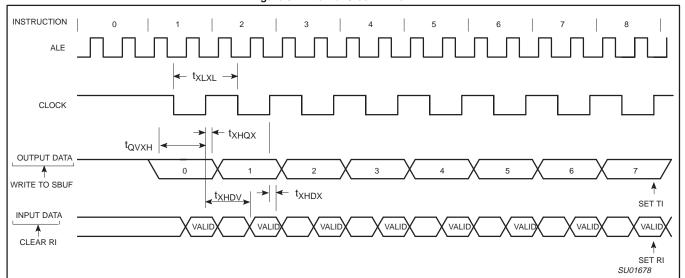

|                     | ng – Shift R | egister Mode <sup>4</sup> (Test Conditions: T <sub>amb</sub> = 0 | °C to +70 °C; V <sub>S</sub> | S = 0 V; Load Capa | acitance = 80 pF)        |                          |      |

| t <sub>XLXL</sub>   | 6            | Serial port clock cycle time                                     | 0.75                         | Ì                  | 12t <sub>CLCL</sub>      |                          | μs   |

| t <sub>QVXH</sub>   | 6            | Output data setup to clock rising edge                           | 492                          |                    | 10t <sub>CLCL</sub> -133 |                          | ns   |

| t <sub>XHQX</sub>   | 6            | Output data hold after clock rising edge                         | 8                            |                    | 2t <sub>CLCL</sub> -117  |                          | ns   |

| t <sub>XHDX</sub>   | 6            | Input data hold after clock rising edge                          | 0                            |                    | 0                        |                          | ns   |

| t <sub>XHDV</sub>   | 6            | Clock rising edge to input data valid                            |                              | 492                | 1                        | 10t <sub>CLCL</sub> -133 | ns   |

- Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

3. t<sub>CLCL</sub> = 1/f<sub>OSC</sub> = one oscillator clock period. t<sub>CLCL</sub> = 83.3ns at f<sub>OSC</sub> = 12 MHz. t<sub>CLCL</sub> = 62.5ns at f<sub>OSC</sub> = 16 MHz.

4. These values are characterized but not 100% production tested.

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

### AC ELECTRICAL CHARACTERISTICS (Continued)1, 2

24 MHz version

|                     |                                              |                                                                        | 24 MHz                 | CLOCK       | VARIABL                  | E CLOCK                  |      |

|---------------------|----------------------------------------------|------------------------------------------------------------------------|------------------------|-------------|--------------------------|--------------------------|------|

| SYMBOL              | FIGURE                                       | PARAMETER                                                              | MIN                    | MAX         | MIN                      | MAX                      | UNIT |

| 1/t <sub>CLCL</sub> | 2                                            | Oscillator frequency                                                   |                        |             | 3.5                      | 24                       | MHz  |

| LHLL                | 2                                            | ALE pulse width                                                        | 43                     |             | 2t <sub>CLCL</sub> -40   |                          | ns   |

| t <sub>AVLL</sub>   | 2                                            | Address valid to ALE low                                               | 17                     |             | t <sub>CLCL</sub> -25    |                          | ns   |

| t <sub>LLAX</sub>   | 2                                            | Address hold after ALE low                                             | 17                     |             | t <sub>CLCL</sub> -25    |                          | ns   |

| t <sub>LLIV</sub>   | 2                                            | ALE low to valid instruction in                                        |                        | 102         |                          | 4t <sub>CLCL</sub> -65   | ns   |

| LLPL                | 2                                            | ALE low to PSEN low                                                    | 17                     |             | t <sub>CLCL</sub> -25    |                          | ns   |

| t <sub>PLPH</sub>   | 2                                            | PSEN pulse width                                                       | 80                     |             | 3t <sub>CLCL</sub> -45   |                          | ns   |

| t <sub>PLIV</sub>   | 2                                            | PSEN low to valid instruction in                                       |                        | 65          |                          | 3t <sub>CLCL</sub> -60   | ns   |

| t <sub>PXIX</sub>   | 2                                            | Input instruction hold after PSEN                                      | 0                      |             | 0                        |                          | ns   |

| t <sub>PXIZ</sub>   | 2                                            | Input instruction float after PSEN                                     |                        | 17          |                          | t <sub>CLCL</sub> -25    | ns   |

| t <sub>AVIV</sub>   | 2                                            | Address to valid instruction in                                        |                        | 128         |                          | 5t <sub>CLCL</sub> -80   | ns   |

| t <sub>PLAZ</sub>   | 2                                            | PSEN low to address float                                              |                        | 10          |                          | 10                       | ns   |

| Data Memory         | <u>.                                    </u> | •                                                                      |                        |             |                          |                          |      |

| t <sub>RLRH</sub>   | 3                                            | RD pulse width                                                         | 150                    |             | 6t <sub>CLCL</sub> -100  |                          | ns   |

| t <sub>WLWH</sub>   | 4                                            | WR pulse width                                                         | 150                    |             | 6t <sub>CLCL</sub> -100  |                          | ns   |

| t <sub>RLDV</sub>   | 3                                            | RD low to valid data in                                                |                        | 118         |                          | 5t <sub>CLCL</sub> -90   | ns   |

| t <sub>RHDX</sub>   | 3                                            | Data hold after RD                                                     | 0                      |             | 0                        |                          | ns   |

| t <sub>RHDZ</sub>   | 3                                            | Data float after RDxs                                                  |                        | 55          |                          | 2t <sub>CLCL</sub> -28   | ns   |

| t <sub>LLDV</sub>   | 3                                            | ALE low to valid data in                                               |                        | 183         |                          | 8t <sub>CLCL</sub> -150  | ns   |

| t <sub>AVDV</sub>   | 3                                            | Address to valid data in                                               |                        | 210         |                          | 9t <sub>CLCL</sub> -165  | ns   |

| t <sub>LLWL</sub>   | 3, 4                                         | ALE low to RD or WR low                                                | 75                     | 175         | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50   | ns   |

| t <sub>AVWL</sub>   | 3, 4                                         | Address valid to WR low or RD low                                      | 92                     |             | 4t <sub>CLCL</sub> -75   |                          | ns   |

| t <sub>QVWX</sub>   | 4                                            | Data valid to WR transition                                            | 12                     |             | t <sub>CLCL</sub> -30    |                          | ns   |

| t <sub>DW</sub>     | 4                                            | Data before WR                                                         | 162                    |             | 7t <sub>CLCL</sub> -130  |                          | ns   |

| t <sub>WHQX</sub>   | 4                                            | Data hold after WR                                                     | 17                     |             | t <sub>CLCL</sub> -25    |                          | ns   |

| t <sub>RLAZ</sub>   | 3                                            | RD low to address float                                                |                        | 0           |                          | 0                        | ns   |

| t <sub>WHLH</sub>   | 3, 4                                         | RD or WR high to ALE high                                              | 17                     | 67          | t <sub>CLCL</sub> -25    | t <sub>CLCL</sub> +25    | ns   |

| External Clo        | ck                                           |                                                                        |                        |             |                          |                          |      |

| t <sub>CHCX</sub>   | 5                                            | High time <sup>3</sup>                                                 | 17                     |             | 17                       |                          | ns   |

| t <sub>CLCX</sub>   | 5                                            | Low time <sup>3</sup>                                                  | 17                     |             | 17                       |                          | ns   |

| t <sub>CLCH</sub>   | 5                                            | Rise time <sup>3</sup>                                                 | 1                      | 5           |                          | 20                       | ns   |

| tchcl               | 5                                            | Fall time <sup>3</sup>                                                 | 1                      | 5           |                          | 20                       | ns   |

|                     | g – Shift Reg                                | ister Mode <sup>3</sup> (Test Conditions: T <sub>amb</sub> = 0 °C to - | 70 °C; V <sub>SS</sub> | = 0 V; Load | d Capacitance = 8        | 0 pF)                    |      |

| t <sub>XLXL</sub>   | 6                                            | Serial port clock cycle time                                           | 0.5                    |             | 12t <sub>CLCL</sub>      |                          | μs   |

| t <sub>QVXH</sub>   | 6                                            | Output data setup to clock rising edge                                 | 283                    |             | 10t <sub>CLCL</sub> -133 |                          | ns   |

| XHQX                | 6                                            | Output data hold after clock rising edge                               | 23                     |             | 2t <sub>CLCL</sub> -60   |                          | ns   |

| XHDX                | 6                                            | Input data hold after clock rising edge                                | 0                      |             | 0                        |                          | ns   |

| t <sub>XHDV</sub>   | 6                                            | Clock rising edge to input data valid                                  | 1                      | 283         |                          | 10t <sub>CLCL</sub> -133 | ns   |

- NOTES:

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

These values are characterized but not 100% production tested.

t<sub>CLCL</sub> = 1/f<sub>OSC</sub> = one oscillator clock period. t<sub>CLCL</sub> = 41.7ns at f<sub>OSC</sub> = 24 MHz.

### Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

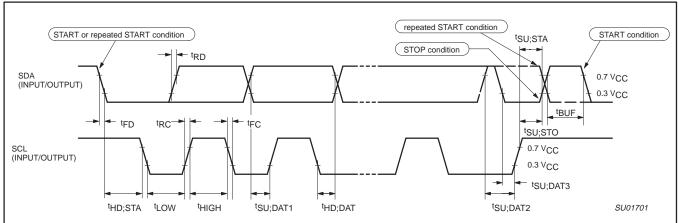

#### AC ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL                   | PARAMETER                                 | INPUT                  | ОИТРИТ                                   |

|--------------------------|-------------------------------------------|------------------------|------------------------------------------|

| I <sup>2</sup> C Interfa | L<br>ce (Refer to Figure 9)               |                        |                                          |

| t <sub>HD;STA</sub>      | START condition hold time                 | ≥ 14 t <sub>CLCL</sub> | > 4.0 μs <sup>1</sup>                    |

| t <sub>LOW</sub>         | SCL low time                              | ≥ 16 t <sub>CLCL</sub> | > 4.7 μs <sup>1</sup>                    |

| t <sub>HIGH</sub>        | SCL high time                             | ≥ 14 t <sub>CLCL</sub> | > 4.0 µs <sup>1</sup>                    |

| t <sub>RC</sub>          | SCL rise time                             | ≤ 1 μs                 | _2                                       |

| t <sub>FC</sub>          | SCL fall time                             | ≤ 0.3 μs               | < 0.3 μs <sup>3</sup>                    |

| t <sub>SU;DAT1</sub>     | Data set-up time                          | ≥ 250ns                | > 20 t <sub>CLCL</sub> – t <sub>RD</sub> |

| t <sub>SU;DAT2</sub>     | SDA set-up time (before rep. START cond.) | ≥ 250ns                | > 1 μs <sup>1</sup>                      |

| t <sub>SU;DAT3</sub>     | SDA set-up time (before STOP cond.)       | ≥ 250ns                | > 8 t <sub>CLCL</sub>                    |

| t <sub>HD;DAT</sub>      | Data hold time                            | ≥ 0ns                  | > 8 t <sub>CLCL</sub> - t <sub>FC</sub>  |

| t <sub>SU;STA</sub>      | Repeated START set-up time                | ≥ 14 t <sub>CLCL</sub> | > 4.7 μs <sup>1</sup>                    |

| t <sub>SU;STO</sub>      | STOP condition set-up time                | ≥ 14 t <sub>CLCL</sub> | > 4.0 µs <sup>1</sup>                    |

| t <sub>BUF</sub>         | Bus free time                             | ≥ 14 t <sub>CLCL</sub> | > 4.7 μs <sup>1</sup>                    |

| t <sub>RD</sub>          | SDA rise time                             | ≤ 1 μs                 | _2                                       |

| t <sub>FD</sub>          | SDA fall time                             | ≤ 0.3 μs               | < 0.3 μs <sup>3</sup>                    |

- At 100 kbit/s. At other bit rates this value is inversely proportional to the bit-rate of 100 kbit/s.

Determined by the external bus-line capacitance and the external bus-line pull-resistor, this must be < 1 μs.</li>

Spikes on the SDA and SCL lines with a duration of less than 3 t<sub>CLCL</sub> will be filtered out. Maximum capacitance on bus-lines SDA and

- 4. t<sub>CLCL</sub> = 1/f<sub>OSC</sub> = one oscillator clock period at pin XTAL1. For 62 ns, 42 ns < t<sub>CLCL</sub> < 285 ns (16 MHz, 24 MHz > f<sub>OSC</sub> > 3.5 MHz) the SI01 interface meets the I<sup>2</sup>C-bus specification for bit-rates up to 100 kbit/s.

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

80C552/83C552

#### **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

A - Address

C - Clock

D - Input data

H - Logic level high

I - Instruction (program memory contents)

L - Logic level low, or ALE

P - PSEN

Q - Output data

R - RD signal

t - Time

V - Valid

W - WR signal

X - No longer a valid logic level

Z - Float

**Examples:**  $t_{AVLL} = Time for address valid to$

ALE low.

$t_{LLPL}$  = Time for ALE low to

PSEN low.

Figure 2. External Program Memory Read Cycle

Figure 3. External Data Memory Read Cycle

Figure 4. External Data Memory Write Cycle

Figure 5. External Clock Drive XTAL1

Figure 6. Shift Register Mode Timing

## Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

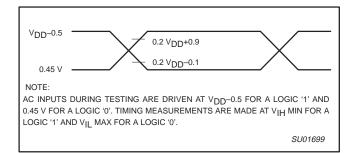

Figure 7. AC Testing Input/Output

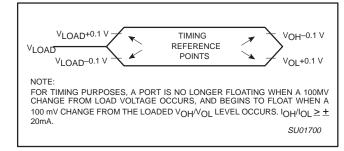

Figure 8. Float Waveform

Figure 9. Timing SIO1 (I<sup>2</sup>C) Interface

# Single-chip 8-bit microcontroller with 10-bit A/D, capture/compare timer, high-speed outputs, PWM

### 80C552/83C552

Figure 10. 16 MHz Version Supply Current (I<sub>DD</sub>) as a Function of Frequency at XTAL1 (f<sub>OSC</sub>)