# DATA SHEET

# FB2041

7-bit Futurebus+ transceiver

**Product specification**

1995 May 25

IC19 Data Handbook

# 7-bit Futurebus+ transceiver

FB2041

### **DESCRIPTION**

The FB2041 is a 7-bit bidirectional BTL transceiver and is intended to provide the electrical interface to a high performance wired-OR bus. The FB2041 is an inverting transceiver.

The B-port drivers are Low-capacitance open collectors with controlled ramp and are designed to sink 100mA. Precision band gap references on the B-port insure very good noise margins by limiting the switching threshold to a narrow region centered at 1.55V.

### **FEATURES**

- 7-bit BTL transceiver

- Separate I/O on TTL A-port

- Inverting

- Three separate pairs of driver enables in a 1 bit, 3 bit, 3 bit arrangement

- Drives heavily loaded backplanes with equivalent load impedances down to 10 $\Omega$ .

- High drive 100mA BTL open collector drivers on B-port

- Allows incident wave switching in heavily loaded backplane buses

- Reduced BTL voltage swing produces less noise and reduces power consumption

- Built-in precision band-gap reference provides accurate receiver thresholds and improved noise immunity

- Compatible with IEEE Futurebus+ or proprietary BTL backplanes

- Controlled output ramp and multiple GND pins minimize ground bounce

- Each BTL driver has a dedicated Bus GND for a signal return

- Glitch-free power up/power down operation

- Low I<sub>CC</sub> current

- Tight output skew

- Supports live insertion

- Pins for the optional JTAG boundary scan function are provided

- High density packaging in plastic Quad Flatpack

# **QUICK REFERENCE DATA**

| SYMBOL           | PARA                              | METER                             | TYPICAL | UNIT |

|------------------|-----------------------------------|-----------------------------------|---------|------|

| t <sub>PLH</sub> | Propagation delay                 |                                   | 3.7     | ns   |

| t <sub>PHL</sub> | Aln to Bn                         | Aln to Bn                         |         |      |

| t <sub>PLH</sub> | Propagation delay                 |                                   | 3.4     | ns   |

| t <sub>PHL</sub> | Bn to AOn                         | Bn to AOn                         |         |      |

| C <sub>OB</sub>  | Output capacitance (B0 - B6 only) | Output capacitance (B0 - B6 only) |         |      |

| I <sub>OL</sub>  | Output current (B0 - B6 only)     |                                   | 100     | mA   |

|                  |                                   | Standby                           | 19      |      |

| l .              | Supply Current                    | Aln to Bn (outputs Low or High)   | 40      |      |

| Icc              | Supply Current                    | Bn to AOn (outputs Low)           | 22      | mA   |

|                  |                                   | Bn to AOn (outputs High)          | 19      |      |

## ORDERING INFORMATION

| PACKAGE                      | COMMERCIAL RANGE                                        | INDUSTRIAL RANGE                                          | DWG      |

|------------------------------|---------------------------------------------------------|-----------------------------------------------------------|----------|

|                              | V <sub>CC</sub> = 5V±10%; T <sub>amb</sub> = 0 to +70°C | V <sub>CC</sub> = 5V±10%; T <sub>amb</sub> = -40 to +85°C | No.      |

| 52-pin Plastic Quad Flatpack | FB2041BB                                                | CD3207BB                                                  | SOT379-1 |

# 7-bit Futurebus+ transceiver

FB2041

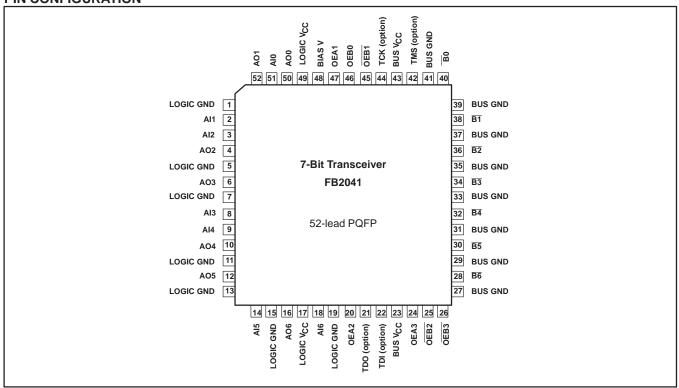

### **PIN CONFIGURATION**

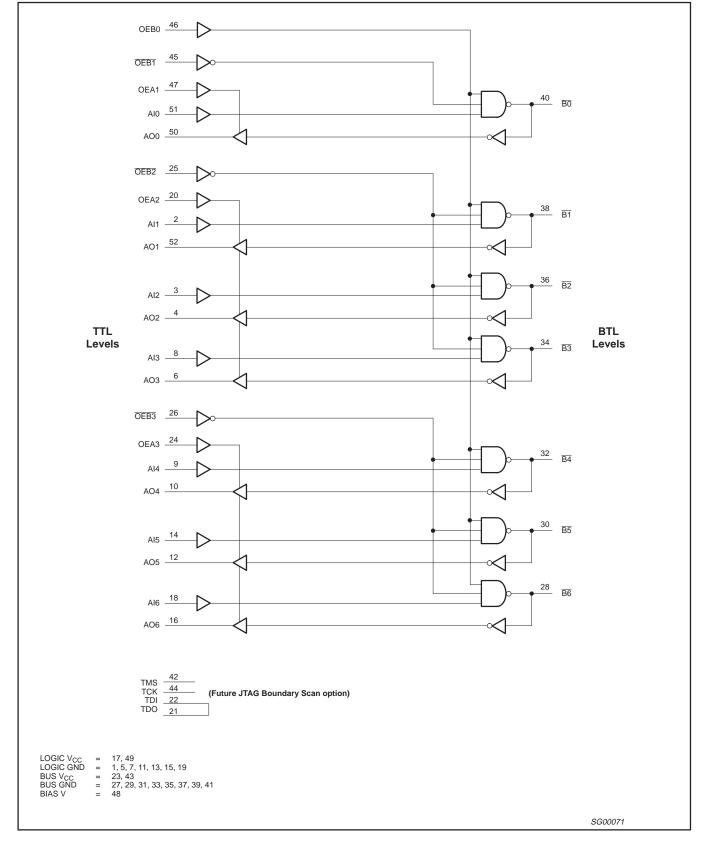

The B-port interfaces to "Backplane Transceiver Logic" (See the IEEE 1194.1 BTL standard). BTL features low power consumption by reducing voltage swing (1Vp-p, between 1V and 2V) and reduced capacitive loading by placing an internal series diode on the drivers. BTL also provides incident wave switching, a necessity for high performance backplanes.

There are three separate pairs of driver enables in a 1 bit, 3 bit, 3 bit arrangement. The TTL/BTL output drivers for bit 0 are enabled with OEA1/OEB1, output drivers for bits 1–2–3 are enabled with OEA2/OEB2 and output drivers for bits 4–5–6 are enabled with OEA3/OEB3.

The A-port operates at TTL levels with separate I/O. The 3-state A-port drivers are enabled when OEAn goes High after an extra 6ns delay which is built in to provide a break-before-make function. When OEAn goes Low, A-port drivers become High impedance without any extra delay. During power on/off cycles, the A-port drivers are held in a High impedance state when V<sub>CC</sub> is below 2.5V.

The B-port has an output enable, OEB0, which affects all seven drivers. When OEB0 is High and OEBn is Low the output driver will be enabled. When OEB0 is Low or if OEBn is High, the B-port drivers will be inactive and at the level of the backplane signal.

To support live insertion, OEB0 is held Low during power on/off cycles to insure glitch free B port drivers. Proper bias for B port drivers during live insertion is provided by the BIAS V pin when at a 5V level while  $V_{CC}$  is Low. If live insertion is not a requirement, the BIAS V pin should be tied to a  $V_{CC}$  pin.

The LOGIC GND and BUS GND pins are isolated in the package to minimize noise coupling between the BTL and TTL sides. These pins should be tied to a common ground external to the package.

Each BTL driver has an associated BUS GND pin that acts as a signal return path and these BUS GND pins are internally isolated from each other. In the event of a ground return fault, a "hard" signal failure occurs instead of a pattern dependent error that may be very infrequent and impossible to trouble-shoot.

The LOGIC  $V_{CC}$  and BUS  $V_{CC}$  pins are also isolated internally to minimize noise and may be externally decoupled separately or simply tied together.

JTAG boundary scan functionality is provided as an option with signals TMS, TCK, TDI and TDO. When this option is not present, TMS and TCK are no-connects (no bond wires) and TDI and TDO are shorted together internally.

# 7-bit Futurebus+ transceiver

FB2041

# **PIN DESCRIPTION**

| SYMBOL                | PIN NUMBER                     | TYPE   | NAME AND FUNCTION                                            |

|-----------------------|--------------------------------|--------|--------------------------------------------------------------|

| AI0 – AI6             | 51, 2, 3, 8, 9, 14, 18         | Input  | Data inputs (TTL)                                            |

| AO0 – AO6             | 50, 52, 4, 6, 10, 12, 16       | Output | 3-state outputs (TTL)                                        |

| B0 – B6               | 40, 38, 36, 34, 32, 30, 28     | I/O    | Data inputs/Open Collector outputs, High current drive (BTL) |

| OEB0                  | 46                             | Input  | Enables the Bn outputs when High                             |

| OEB1                  | 45                             | Input  | Enables the B0 output when Low                               |

| OEB2                  | 25                             | Input  | Enables the B1 – B3 outputs when Low                         |

| OEB3                  | 26                             | Input  | Enables the B4 – B6 outputs when Low                         |

| OEA1                  | 47                             | Input  | Enables the A0 outputs when High                             |

| OEA2                  | 20                             | Input  | Enables the A1 – A3 outputs when High                        |

| OEA3                  | 24                             | Input  | Enables the A4 – A6 outputs when High                        |

| BUS GND               | 41, 39, 37, 35, 33, 31, 29, 27 | GND    | Bus ground (0V)                                              |

| LOGIC GND             | 1, 5, 7, 11, 13, 15, 19        | GND    | Logic ground (0V)                                            |

| BUS V <sub>CC</sub>   | 23, 43                         | Power  | Positive supply voltage                                      |

| LOGIC V <sub>CC</sub> | 17, 49                         | Power  | Positive supply voltage                                      |

| BIAS V                | 48                             | Power  | Positive supply voltage                                      |

| TMS                   | 42                             | Input  | Test Mode Select (no-connect)                                |

| TCK                   | 44                             | Input  | Test Clock (no-connect)                                      |

| TDI                   | 22                             | Input  | Test Data In (shorted to TDO)                                |

| TDO                   | 21                             | Output | Test Data Out (TDI)                                          |

# **ABSOLUTE MAXIMUM RATINGS**

Operation beyond the limits set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the operating free-air temperature range.

| SYMBOL                        | PARA                                  | PARAMETER                   |                          |    |

|-------------------------------|---------------------------------------|-----------------------------|--------------------------|----|

| V <sub>CC</sub>               | Supply voltage                        |                             | -0.5 to +7.0             | V  |

| \/                            | Input voltage                         | AIO – AI6, OEBO, OEBn, OEAn |                          | V  |

| V <sub>IN</sub> Input voltage | Input voltage                         | <u>B0 – B6</u>              | -1.2 to +5.5             | 7  |

| I <sub>IN</sub>               | Input current                         | -                           | -18 to +5.0              | mA |

| V <sub>OUT</sub>              | Voltage applied to output in High out | out state                   | -0.5 to +V <sub>CC</sub> | V  |

| la                            | Current applied to output in          | AO0 – AO6                   | 48                       | mA |

| IOUT                          | Low output state                      | B0 – B6                     | 200                      | 7  |

| T <sub>STG</sub>              | Storage temperature                   |                             | -65 to +150              | °C |

# **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL                          | PARAMETER                               |           | PARAMETER COMMERCIAL LIMITS $V_{CC} = 5V\pm10\%;$ $T_{amb} = 0 \text{ to } +70^{\circ}\text{C}$ |     |      |      | INDUSTRIAL LIMITS  V <sub>CC</sub> = 5V±10%;  T <sub>amb</sub> = -40 to +85°C |      |     |

|---------------------------------|-----------------------------------------|-----------|-------------------------------------------------------------------------------------------------|-----|------|------|-------------------------------------------------------------------------------|------|-----|

|                                 |                                         |           | MIN                                                                                             | TYP | MAX  | MIN  | TYP                                                                           | MAX  |     |

| V <sub>CC</sub>                 | Supply voltage                          |           | 4.5                                                                                             | 5.0 | 5.5  | 4.5  | 5.0                                                                           | 5.5  | V   |

| V <sub>IH</sub>                 | High-level input voltage                |           | 2.0                                                                                             |     |      | 2.0  |                                                                               |      | V   |

| VIH I light-level input voltage | B0 – B6                                 | 1.62      | 1.55                                                                                            |     | 1.62 | 1.55 |                                                                               |      |     |

| V <sub>IL</sub>                 | V <sub>II</sub> Low-level input voltage |           |                                                                                                 |     | 0.8  |      |                                                                               | 0.8  | V   |

| VIL                             | Low-level input voltage                 | B0 – B6   |                                                                                                 |     | 1.47 |      |                                                                               | 1.47 | 1 1 |

| I <sub>IK</sub>                 | Input clamp current                     |           |                                                                                                 |     | -18  |      |                                                                               | -18  | mA  |

| I <sub>OH</sub>                 | High-level output current               | AO0 – AO6 |                                                                                                 |     | -3   |      |                                                                               | -3   | mA  |

| 1                               | Low-level output current                | AO0 – AO6 |                                                                                                 |     | 24   |      |                                                                               | 24   | mA  |

| IOL L                           | Low-level output current                | B0 – B6   |                                                                                                 |     | 100  |      |                                                                               | 100  | 1   |

| C <sub>OB</sub>                 | Output capacitance on B port            |           |                                                                                                 | 6   | 7    |      | 6                                                                             | 7    | pF  |

| T <sub>amb</sub>                | Operating free-air temperature re       | ange      | 0                                                                                               |     | +70  | -40  |                                                                               | +85  | °C  |

FB2041

### **FUNCTION TABLE**

| MODE                                           |     |          |      |      | INPUTS |      |      |      |      | OUTPUTS |       |

|------------------------------------------------|-----|----------|------|------|--------|------|------|------|------|---------|-------|

|                                                | Aln | Bn*      | OEB0 | OEB1 | OEB2   | OEB3 | OEA1 | OEA2 | OEA3 | AOn     | Bn*   |

|                                                | L   | _        | Н    | L    | L      | L    | L    | L    | L    | Z       | H**   |

| Aln to Bn                                      | Н   | <u> </u> | Н    | L    | L      | L    | L    | L    | L    | Z       | L     |

|                                                | L   | <u> </u> | Н    | L    | L      | L    | Н    | Н    | Н    | L       | H**   |

|                                                | Н   | <u> </u> | Н    | L    | L      | L    | Н    | Н    | Н    | Н       | L     |

|                                                | L   | <u> </u> | Н    | L    | Х      | Х    | L    | L    | L    | Z       | H**   |

| Al0 to BO                                      | Н   | _        | Н    | L    | Х      | Х    | L    | L    | L    | Z       | L     |

|                                                | L   | <u> </u> | Н    | L    | Х      | Х    | Н    | Н    | Н    | L       | H**   |

|                                                | Н   | _        | Н    | L    | Х      | Х    | Н    | Н    | Н    | Н       | L     |

|                                                | L   | <u> </u> | Н    | Х    | L      | Х    | L    | L    | L    | Z       | H**   |

| Al1 – Al3 to $\overline{B1}$ – $\overline{B3}$ | Н   | <u> </u> | Н    | Х    | L      | Х    | L    | L    | L    | Z       | L     |

|                                                | L   | <u> </u> | Н    | Х    | L      | Х    | Н    | Н    | Н    | L       | H**   |

|                                                | Н   | <u> </u> | Н    | Х    | L      | Х    | Н    | Н    | Н    | Н       | L     |

|                                                | L   |          | Н    | Х    | Х      | L    | L    | L    | L    | Z       | H**   |

| $AI4 - AI6$ to $\overline{B4} - \overline{B6}$ | Н   | <u> </u> | Н    | Х    | Х      | L    | L    | L    | L    | Z       | L     |

|                                                | L   | <u> </u> | Н    | Х    | Х      | L    | Н    | Н    | Н    | L       | H**   |

|                                                | Н   | <u> </u> | Н    | Х    | Х      | L    | Н    | Н    | Н    | Н       | L     |

| Disable Bn outputs                             | Х   | Х        | L    | Х    | Х      | Х    | Х    | Х    | Х    | Х       | H**   |

|                                                | Х   | Х        | Х    | Н    | Н      | Н    | Х    | Х    | Х    | Х       | H**   |

| Disable B0 outputs                             | Х   | Х        | Н    | Н    | Х      | Х    | Х    | Х    | Х    | Х       | H**   |

| Disable B1 – B3 outputs                        | Х   | Х        | Н    | Х    | Н      | Х    | Х    | Х    | Х    | Х       | H**   |

| Disable B4 – B6 outputs                        | Х   | Х        | Н    | Х    | Х      | Н    | Х    | Х    | Х    | Х       | H**   |

|                                                | Х   | L        | L    | Х    | Х      | Х    | Н    | Н    | Н    | Н       | Input |

| Bn to AOn                                      | Х   | Н        | L    | Х    | Х      | Х    | Н    | Н    | Н    | L       | Input |

|                                                | Х   | L        | Х    | Н    | Н      | Н    | Н    | Н    | Н    | Н       | Input |

|                                                | Х   | Н        | Х    | Н    | Н      | Н    | Н    | Н    | Н    | L       | Input |

|                                                | Х   | L        | L    | Х    | Х      | Х    | Н    | Х    | Х    | Н       | Input |

| B0 to AO0                                      | Х   | Н        | L    | Х    | Х      | Х    | Н    | Х    | Х    | L       | Input |

|                                                | Х   | L        | Х    | Н    | Н      | Н    | Н    | Х    | Х    | Н       | Input |

|                                                | Х   | Н        | Х    | Н    | Н      | Н    | Н    | Х    | Х    | L       | Input |

|                                                | Х   | L        | L    | Х    | Х      | Х    | Х    | Н    | Х    | Н       | Input |

| $\overline{B1} - \overline{B3}$ to AO1 – AO3   | Х   | Н        | L    | Х    | Х      | Х    | Х    | Н    | Х    | L       | Input |

|                                                | Х   | L        | Х    | Н    | Н      | Н    | Х    | Н    | Х    | Н       | Input |

|                                                | Х   | Н        | Х    | Н    | Н      | Н    | Х    | Н    | Х    | L       | Input |

|                                                | Х   | L        | L    | Х    | Х      | Х    | Х    | Х    | Н    | Н       | Input |

| B4 – B6 to AO4 – AO6                           | Х   | Н        | L    | Х    | Х      | Х    | Х    | Х    | Н    | L       | Input |

|                                                | Х   | L        | Х    | Н    | Н      | Н    | Х    | Х    | Н    | Н       | Input |

|                                                | Х   | Н        | Х    | Н    | Н      | Н    | Х    | Х    | Н    | L       | Input |

| Disable AOn outputs                            | Х   | Х        | Х    | Х    | Х      | Х    | L    | L    | L    | Z       | X     |

| Disable AO0 outputs                            | Х   | Х        | Х    | Х    | Х      | Х    | L    | Х    | Х    | Z       | Х     |

| Disable AO1 – AO3 outputs                      | Х   | Х        | Х    | Х    | Х      | Х    | Х    | L    | Х    | Z       | Х     |

| Disable AO4 – AO6 outputs                      | X   | X        | X    | X    | Х      | X    | Х    | X    | L    | Z       | Х     |

# NOTES:

H = High voltage level

L = Low voltage level

X = Don't care

Z = High-impedance (OFF) state

— = Input not externally driven

H\*\* = Goes to level of pull-up voltage

B\* = Precaution should be taken to ensure B inputs do not float.

If they do, they are equal to Low state.

Z = High-impedance (OFF) state

— = Input not externally driven

H\*\* = Goes to level of pull-up voltage

$B^*$  = Precaution should be taken to ensure B inputs do not float.

If they do, they are equal to Low state.

FB2041

# **LOGIC DIAGRAM**

# 7-bit Futurebus+ transceiver

FB2041

# LIVE INSERTION SPECIFICATIONS

| CVMDOL              |                                   | DADAMETED                                                                                                              |      | LIMITS |     | UNIT |  |

|---------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------|------|--------|-----|------|--|

| SYMBOL              |                                   | PARAMETER                                                                                                              | MIN  | TYP    | MAX | UNII |  |

| V <sub>BIASV</sub>  | Bias pin voltage                  | $V_{CC} = 0 \text{ to } 5.25V, \overline{Bn} = 0 \text{ to } 2.0V$                                                     | 4.5  |        | 5.5 | V    |  |

|                     | Diag pin DC gurrent               | $V_{CC} = 0$ to 4.75V, $\overline{Bn} = 0$ to 2.0V,<br>Bias V = 4.5 to 5.5V                                            |      |        | 1   | mA   |  |

| IBIASV              | Bias pin DC current               | $V_{CC} = 4.5 \text{ to } 5.5 \text{V}, \overline{Bn} = 0 \text{ to } 2.0 \text{V},$<br>Bias V = 4.5 to 5.5 V          |      |        | 10  | μΑ   |  |

| V <sub>Bn</sub>     | Bus voltage during prebias        | $\overline{B0} - \overline{B8} = 0$ V, Bias V = 5.0V                                                                   | 1.62 |        | 2.1 | V    |  |

| I <sub>LM</sub>     | Fall current during prebias       | $\overline{B0} - \overline{B8} = 2V$ , Bias $V = 4.5$ to $5.5V$                                                        | 1    |        |     | μΑ   |  |

| I <sub>HM</sub>     | Rise current during prebias       | $\overline{B0} - \overline{B8} = 1V$ , Bias $V = 4.5$ to $5.5V$                                                        | -1   |        |     | μΑ   |  |

| I <u>m</u> PEAK     | Peak bus current during insertion | $V_{CC} = 0$ to 5.25V, $\overline{B0} - \overline{B8} = 0$ to 2.0V,<br>Bias V = 4.5 to 5.5V, OEB0 = 0.8V, $t_r = 2$ ns |      |        | 10  | mA   |  |

| I OFF               | Dower up ourront                  | $V_{CC} = 0$ to 5.25V, OEB0 = 0.8V                                                                                     |      |        | 100 |      |  |

| I <sub>OL</sub> OFF | Power up current                  | $V_{CC} = 0$ to 2.2V, OEB0 = 0 to 5V                                                                                   |      |        | 100 | μΑ   |  |

| t <sub>GR</sub>     | Input glitch rejection            | V <sub>CC</sub> = 5.0V                                                                                                 | 1.0  | 1.35   |     | ns   |  |

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating free-air temperature range unless otherwise noted.

| CVMDOL           | PARAMETER                              |                                            | TEST CONDITIONS                                                                             |     | UNIT             |       |      |

|------------------|----------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|-----|------------------|-------|------|

| SYMBOL           | PARAME                                 | IER                                        | TEST CONDITIONS <sup>1</sup>                                                                | MIN | TYP <sup>2</sup> | MAX   | UNII |

| I <sub>OH</sub>  | High level output current              | B0 – B6                                    | $V_{CC} = MAX$ , $V_{IL} = MAX$ , $V_{IH} = MIN$ , $V_{OH} = 2.1V$                          |     |                  | 100   | μΑ   |

| I <sub>OFF</sub> | Power-off output current               | B0 – B6                                    | $V_{CC} = 0.0V, V_{IL} = MAX, V_{IH} = MIN, V_{OH} = 2.1V$                                  |     |                  | 100   | μΑ   |

| V <sub>OH</sub>  | High-level output voltage              | AO0 – AO6 <sup>3</sup>                     | V <sub>CC</sub> = MIN, V <sub>IL</sub> = MAX, V <sub>IH</sub> = MIN, I <sub>OH</sub> = -3mA | 2.5 | 2.85             |       | V    |

|                  |                                        | AO0 – AO6 <sup>3</sup>                     | $V_{CC} = MIN, V_{IL} = MAX, V_{IH} = MIN, I_{OL} = 24mA$                                   |     | 0.33             | 0.5   |      |

| $V_{OL}$         | Low-level output voltage               | B0 – B6                                    | $V_{CC} = MIN, V_{IL} = MAX, V_{IH} = MIN, I_{OL} = 80mA$                                   | .75 | 1.0              | 1.10  | V    |

|                  |                                        |                                            | $V_{CC} = MIN, V_{IL} = MAX, V_{IH} = MIN, I_{OL} = 100mA$                                  |     |                  | 1.15  |      |

| $V_{IK}$         | Input clamp voltage                    |                                            | $V_{CC} = MIN, I_I = I_{IK}$                                                                |     |                  | -1.2  | V    |

| II               | Input current at maximum input voltage | OEB0, <del>OEBn</del> ,<br>OEAn, Al0 – Al6 | $V_{CC} = MAX, V_I = GND \text{ or } 5.5V$                                                  |     |                  | ±50   | μΑ   |

| I <sub>IH</sub>  | High-level input current               | OEB0, OEBn,<br>OEAn, Al0 – Al6             | $V_{CC} = MAX, V_I = 2.7V$                                                                  |     |                  | 20    | μА   |

|                  |                                        | B0 – B6                                    | $V_{CC} = MAX, V_I = 2.1V$                                                                  |     |                  | 100   |      |

| I <sub>IL</sub>  | Low-level input current                | OEB0, <del>OEBn</del> ,<br>OEAn, Al0 – Al6 | $V_{CC} = MAX, V_I = 0.5V$                                                                  |     |                  | -20   | μА   |

|                  |                                        | B0 – B6                                    | $V_{CC} = MAX, V_I = 0.75V$                                                                 |     |                  | -100  | '    |

| I <sub>OZH</sub> | Off-state output current               | AO0 – AO6                                  | $V_{CC} = MAX, V_O = 2.7V$                                                                  |     |                  | 50    | μА   |

| I <sub>OZL</sub> | Off-state output current               | AO0 – AO6                                  | $V_{CC} = MAX, V_O = 0.5V$                                                                  |     |                  | -50   | μΑ   |

| Io               | Output current                         | AO0 – AO6 only                             | V <sub>CC</sub> = MAX                                                                       | -30 | -55              | -150  | mA   |

|                  |                                        | I <sub>CCZ</sub> (standby)                 | V <sub>CC</sub> = MAX                                                                       |     | 19               | 30    |      |

|                  | Cumply ourrent (total)                 | I <sub>CCB,</sub> Aln to Bn                | V <sub>CC</sub> = MAX, outputs Low or High                                                  |     | 40               | 60    | mA   |

| Icc              | Supply current (total)                 | I <sub>CCA,</sub> Bn to AOn                | V <sub>CC</sub> = MAX, outputs Low                                                          |     | 22               | 22 35 |      |

|                  |                                        | I <sub>CCA,</sub> Bn to AOn                | V <sub>CC</sub> = MAX, outputs High                                                         |     | 19               | 35    | 1    |

- For conditions shown as MIN or MAX, use the appropriate value specified under recommended operation conditions for the applicable type.

All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

Due to test equipment limitations, actual test conditions are V<sub>IH</sub> = 1.8V and V<sub>IL</sub> = 1.3V for the B side.

# 7-bit Futurebus+ transceiver

FB2041

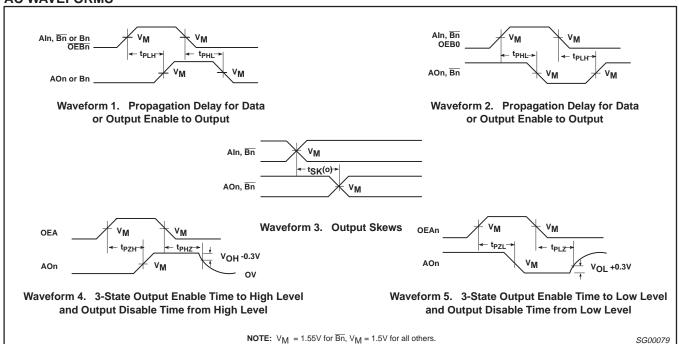

# AC ELECTRICAL CHARACTERISTICS (Commercial)

|                                      |                                                            |                               | A PORT LIMITS                                                      |                                                 |                                         |                  |                                             |      |

|--------------------------------------|------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------|------------------|---------------------------------------------|------|

| SYMBOL                               | PARAMETER                                                  | TEST<br>CONDITION             |                                                                    | +25°C, V <sub>C</sub><br>50pF, R <sub>L</sub> = |                                         | $V_{CC} = 5$     | to 70°C,<br>V±10%,<br>R <sub>L</sub> = 500Ω | UNIT |

|                                      |                                                            |                               | MIN                                                                | TYP                                             | MAX                                     | MIN              | MAX                                         |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay,<br>Bn to AOn                            | Waveform 1, 2                 | 1.8<br>1.6                                                         | 3.4<br>3.2                                      | 5.0<br>4.9                              | 1.6<br>1.6       | 5.5<br>5.0                                  | ns   |

| $t_{PZH}$                            | Output enable time,<br>OEA to AOn                          | Waveform 4, 5                 | 2.2<br>2.0                                                         | 5.0<br>4.0                                      | 6.5<br>6.5                              | 2.0<br>1.8       | 10.0<br>8.0                                 | ns   |

| $t_{PHZ}$                            | Output disable time,<br>OEA to AOn                         | Waveform 4, 5                 | 1.5<br>1.8                                                         | 3.3<br>3.0                                      | 4.8<br>5.0                              | 1.2<br>1.5       | 5.0<br>5.5                                  | ns   |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition time, AOn Port (10% to 90% or 90% to 10%)       | Test Circuit and<br>Waveforms | 1.5<br>1.5                                                         | 2.2<br>2.4                                      | 3.0<br>3.0                              | 1.5<br>1.5       | 3.5<br>3.5                                  | ns   |

| t <sub>SK</sub> (o)                  | Output skew between receivers in same package <sup>1</sup> | Waveform 3                    |                                                                    | 0.4                                             | 1.0                                     |                  | 1.0                                         | ns   |

|                                      |                                                            |                               |                                                                    | E                                               | PORT LIN                                | IITS             |                                             |      |

| SYMBOL                               | PARAMETER                                                  | TEST CONDITION                | $T_{amb}$ = +25°C, $V_{CC}$ = 5V, $C_D$ = 30pF, $R_U$ = 9 $\Omega$ |                                                 | $T_{amb} = 0$ $V_{CC} = 5$ $C_D = 30pI$ | UNIT             |                                             |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay,<br>Aln to Bn                            | Waveform 1, 2                 | 2.4<br>1.5                                                         | 3.7<br>2.7                                      | 4.9<br>4.4                              | 1.9<br>1.5       | 5.7<br>5.0                                  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB0 to Bn                         | Waveform 2                    | 2.4<br>1.9                                                         | 3.7<br>3.5                                      | 4.9<br>4.9                              | 1.9<br>1.8       | 6.4<br>5.4                                  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB1 to Bn                         | Waveform 1                    | 2.4<br>1.9                                                         | 4.0<br>3.6                                      | 5.5<br>5.5                              | 1.9<br>2.5       | 5.9<br>5.9                                  | ns   |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition time, Bn Port (1.3V to 1.8V)                    | Test Circuit and<br>Waveforms | 1.0<br>0.5                                                         | 1.4<br>1.1                                      | 3.0<br>3.0                              | 1.0<br>0.5       | 3.0<br>3.0                                  | ns   |

| t <sub>SK</sub> (o)                  | Output skew between drivers in same package <sup>1</sup>   | Waveform 3                    |                                                                    | 0.3                                             | 1.0                                     |                  | 1.0                                         | ns   |

| SYMBOL                               | PARAMETER                                                  | TEST CONDITION                |                                                                    | $R_U = 16.5\Omega$                              | 1                                       | R <sub>U</sub> = | 16.5Ω                                       | UNIT |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay,<br>Aln to Bn                            | Waveform 1, 2                 | 2.5<br>1.6                                                         | 3.8<br>2.8                                      | 5.0<br>4.5                              | 2.0<br>1.6       | 5.8<br>5.1                                  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB0 to Bn                         | Waveform 2                    | 2.5<br>2.0                                                         | 3.8<br>3.6                                      | 5.0<br>5.0                              | 2.0<br>1.9       | 6.5<br>5.5                                  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB1 to Bn                         | Waveform 1                    | 2.5<br>2.0                                                         | 4.1<br>3.7                                      | 5.6<br>5.6                              | 2.0<br>2.6       | 6.0<br>6.0                                  | ns   |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition time, Bn Port (1.3V to 1.8V)                    | Test Circuit and<br>Waveforms | 1.0<br>0.5                                                         | 1.5<br>1.1                                      | 3.0<br>3.0                              | 1.0<br>0.5       | 3.0<br>3.0                                  | ns   |

| t <sub>SK</sub> (o)                  | Output skew between drivers in same package <sup>1</sup>   | Waveform 3                    |                                                                    | 0.3                                             | 1.0                                     |                  | 1.0                                         | ns   |

It<sub>PN</sub>actual – t<sub>PM</sub>actual | for any data input to output path compared to any other data input to output path where N and M are either LH or HL. Skew times are valid only under same test conditions (temperature, V<sub>CC</sub>, loading, etc.).

# 7-bit Futurebus+ transceiver

FB2041

# AC ELECTRICAL CHARACTERISTICS (Industrial)

|                                      |                                                            |                               | A PORT LIMITS                                                     |                                                   |                                           |                  |                                                |      |

|--------------------------------------|------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------|------------------|------------------------------------------------|------|

| SYMBOL                               | PARAMETER                                                  | TEST<br>CONDITION             | T <sub>amb</sub> =<br>C <sub>L</sub> =                            | = +25°C, V <sub>C</sub><br>50pF, R <sub>L</sub> = | c = 5V,<br>500Ω                           | $V_{CC} = 5$     | 0 to +85°C,<br>V±10%,<br>R <sub>L</sub> = 500Ω | UNIT |

|                                      |                                                            |                               | MIN                                                               | TYP                                               | MAX                                       | MIN              | MAX                                            |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay,<br>Bn to AOn                            | Waveform 1, 2                 | 1.8<br>1.6                                                        | 3.4<br>3.2                                        | 5.0<br>4.9                                | 1.6<br>1.6       | 5.5<br>5.5                                     | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time,<br>OEA to AOn                          | Waveform 4, 5                 | 2.2<br>2.0                                                        | 5.0<br>4.0                                        | 6.5<br>6.5                                | 1.5<br>1.5       | 8.0<br>8.0                                     | ns   |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output disable time,<br>OEA to AOn                         | Waveform 4, 5                 | 1.5<br>1.5                                                        | 3.3<br>3.0                                        | 4.8<br>5.0                                | 0.8<br>1.2       | 6.0<br>6.0                                     | ns   |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition time, AOn Port (10% to 90% or 90% to 10%)       | Test Circuit and<br>Waveforms | 1.5<br>1.5                                                        | 2.2<br>2.4                                        | 3.0<br>3.0                                | 1.5<br>1.5       | 3.5<br>3.5                                     | ns   |

| t <sub>SK</sub> (o)                  | Output skew between receivers in same package <sup>1</sup> | Waveform 3                    |                                                                   | 0.4                                               | 1.0                                       |                  | 1.0                                            | ns   |

|                                      |                                                            |                               |                                                                   | E                                                 | B PORT LIM                                |                  |                                                |      |

| SYMBOL                               | PARAMETER                                                  | TEST CONDITION                | $T_{amb}$ = +25°C, $V_{CC}$ = 5V, $C_D$ = 30pF, $R_U$ = $9\Omega$ |                                                   | $T_{amb} = -40$ $V_{CC} = 5$ $C_D = 30pI$ | UNIT             |                                                |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay,<br>Aln to Bn                            | Waveform 1, 2                 | 2.4<br>1.5                                                        | 3.7<br>2.7                                        | 4.9<br>4.4                                | 1.9<br>1.5       | 5.9<br>5.0                                     | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB0 to Bn                         | Waveform 2                    | 2.4<br>1.9                                                        | 3.7<br>3.5                                        | 4.9<br>4.9                                | 1.9<br>1.8       | 6.4<br>5.9                                     | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time, OEB1 to Bn                            | Waveform 1                    | 2.4<br>1.9                                                        | 4.0<br>3.6                                        | 5.5<br>5.5                                | 1.9<br>1.5       | 6.8<br>6.8                                     | ns   |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition time, Bn Port (1.3V to 1.8V)                    | Test Circuit and<br>Waveforms | 1.0<br>0.5                                                        | 1.4<br>1.1                                        | 3.0<br>3.0                                | 1.0<br>0.5       | 3.0<br>3.0                                     | ns   |

| t <sub>SK</sub> (o)                  | Output skew between drivers in same package <sup>1</sup>   | Waveform 3                    |                                                                   | 0.3                                               | 1.0                                       |                  | 1.0                                            | ns   |

| SYMBOL                               | PARAMETER                                                  | TEST CONDITION                |                                                                   | $R_U = 16.5\Omega$                                | 1                                         | R <sub>U</sub> = | 16.5Ω                                          | UNIT |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay,<br>Aln to Bn                            | Waveform 1, 2                 | 2.5<br>1.6                                                        | 3.8<br>2.8                                        | 5.0<br>4.5                                | 2.0<br>1.6       | 6.0<br>5.1                                     | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB0 to Bn                         | Waveform 2                    | 2.5<br>2.0                                                        | 3.8<br>3.6                                        | 5.0<br>5.0                                | 2.0<br>1.9       | 6.5<br>6.0                                     | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Enable/disable time,<br>OEB1 to Bn                         | Waveform 1                    | 2.5<br>2.0                                                        | 4.1<br>3.7                                        | 5.5<br>5.5                                | 2.0<br>1.6       | 6.9<br>6.9                                     | ns   |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition time, Bn Port (1.3V to 1.8V)                    | Test Circuit and<br>Waveforms | 1.0<br>0.5                                                        | 1.5<br>1.1                                        | 3.0<br>3.0                                | 1.0<br>0.5       | 3.0<br>3.0                                     | ns   |

| t <sub>SK</sub> (o)                  | Output skew between drivers in same package <sup>1</sup>   | Waveform 3                    |                                                                   | 0.3                                               | 1.0                                       |                  | 1.0                                            | ns   |

It<sub>PN</sub>actual – t<sub>PM</sub>actual | for any data input to output path compared to any other data input to output path where N and M are either LH or HL. Skew times are valid only under same test conditions (temperature, V<sub>CC</sub>, loading, etc.).

FB2041

# **AC WAVEFORMS**

FB2041

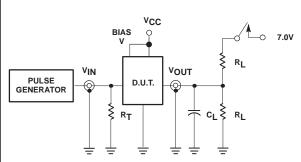

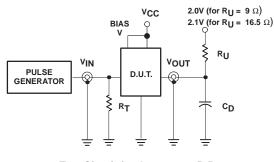

# **TEST CIRCUIT AND WAVEFORMS**

Test Circuit for 3-State Outputs on A Port

### 90% NEGATIVE PULSE ٧M 10% 10% LOW V - t<sub>THL</sub> (t<sub>f</sub>) tTLH (tr) tTLH (tr) - t<sub>THL</sub> (t<sub>f</sub>) $v_{IN}$ 90% 90% POSITIVE PULSE ۷м 10% 10% LOW V

$V_{M} = 1.55V$  for  $\overline{Bn}$ ,  $V_{M} = 1.5V$  for all others. **Input Pulse Definitions**

# **SWITCH POSITION**

| TEST                               | SWITCH |

|------------------------------------|--------|

| t <sub>PLZ,</sub> t <sub>PZL</sub> | closed |

| All other                          | open   |

**Test Circuit for Outputs on B Port**

| Family | INPUT PULSE REQUIREMENTS |       |           |                |                  |                  |  |  |  |

|--------|--------------------------|-------|-----------|----------------|------------------|------------------|--|--|--|

| FB+    | Amplitude                | Low V | Rep. Rate | t <sub>W</sub> | t <sub>TLH</sub> | t <sub>THL</sub> |  |  |  |

| A Port | 3.0V                     | 0.0V  | 1MHz      | 500ns          | 2.5ns            | 2.5ns            |  |  |  |

| B Port | 2.0V                     | 1.0V  | 1MHz      | 500ns          | 2.5ns            | 2.5ns            |  |  |  |

## **DEFINITIONS:**

R<sub>L</sub> = Load Resistor; see AC CHARACTERISTICS for value.

Load capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

$R_T$  = Termination resistance should be equal to  $Z_{OUT}$  of pulse generators.  $C_D$  = Load capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

R<sub>II</sub> = Pull up resistor; see AC CHARACTERISTICS for value.

SG00059

FB2041

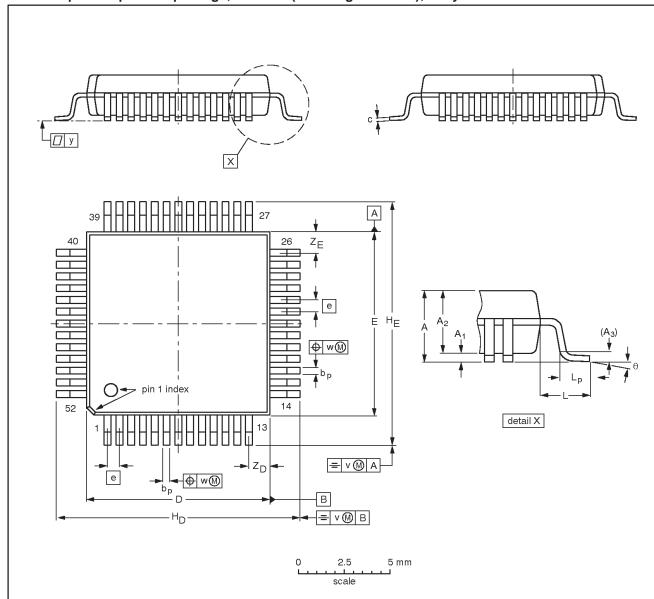

# QFP52: plastic quad flat package; 52 leads (lead length 1.6 mm); body 10 x 10 x 2.0 mm

SOT379-1

# DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | H <sub>D</sub> | HE             | L    | Lp           | v    | w    | у    | Z <sub>D</sub> <sup>(1)</sup> | Z <sub>E</sub> <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|------|--------------|--------------|------------------|------------------|------|----------------|----------------|------|--------------|------|------|------|-------------------------------|-------------------------------|----------|

| mm   | 2.45      | 0.45<br>0.25   | 2.10<br>1.95   | 0.25 | 0.38<br>0.22 | 0.23<br>0.13 | 10.1<br>9.9      | 10.1<br>9.9      | 0.65 | 13.45<br>12.95 | 13.45<br>12.95 | 1.60 | 0.95<br>0.65 | 0.20 | 0.12 | 0.10 | 1.24<br>0.95                  | 1.24<br>0.95                  | 7°<br>0° |

### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | EUROPEAN | ISSUE DATE |            |                                   |

|----------|-----|--------|----------|------------|------------|-----------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ     |            | PROJECTION | ISSUE DATE                        |

| SOT379-1 |     | MO-108 |          |            |            | <del>-95-02-04-</del><br>97-08-04 |

# 7-bit Futurebus+ transceiver

FB2041

# **NOTES**

# 7-bit Futurebus+ transceiver

FB2041

### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development.  Specification may change in any manner without notice.                                                                                                         |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date.  Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code

Date of release: 08-98

Document order number:

Let's make things better.