Data Sheet

April 1999

File Number 4704

# SMBus/I<sup>2</sup>C ACPI Dual Device Bay Controller

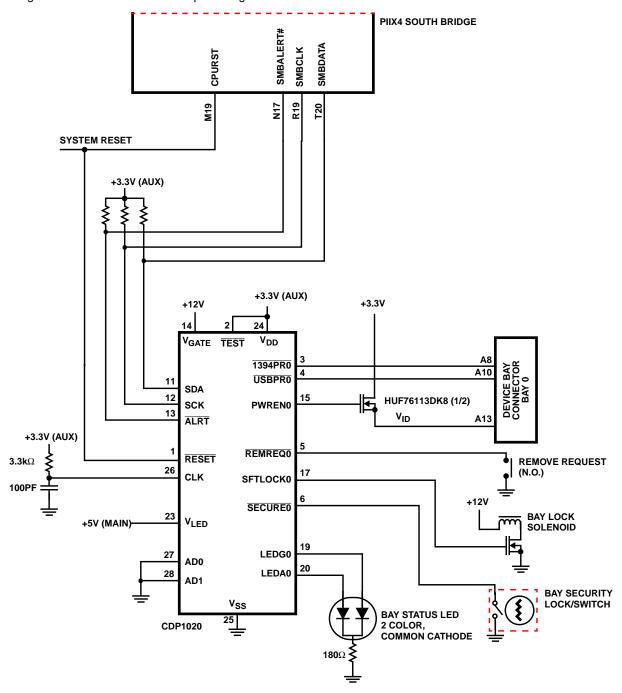

The CDP1020 is an ACPI compliant Device Bay Controller (DBC) that can control two device bays. The controller interfaces to the host system through the industry standard I<sup>2</sup>C or System Management Bus (SMBus) and is fully compliant with Device Bay Specification 0.90. The CDP1020 is designed to be compatible with the integrated SMBus host controller of the PiiX4/PiiX6 in Intel Architecture platforms.

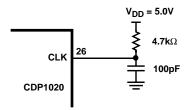

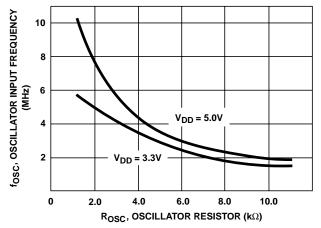

The CDP1020 is designed to be placed on the host motherboard, on a riser, or adjacent to the Device Bay connectors. The required clock source is generated from an internal oscillator on the CLK pin, with an external RC to set the frequency. This lowers the system cost and allows the CDP1020 to remain active during S3-S5 system states where all clock generators have been stopped.

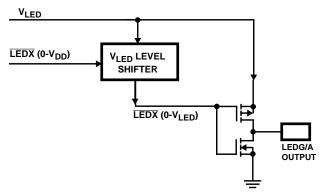

One of the key features of this device is the on-chip level shifters that provide slew rate controlled, direct gate drive for external N-Channel MOSFETs (Intersil HUF76113DK8 recommended) to switch the device bay V<sub>ID</sub> supplies. Switching an N-Channel device as opposed to a P-Channel reduces both device cost and device count, resulting in an overall lower system cost.

Configuration data for the CDP1020, including subsystem vendor ID, subsystem revision, bay size and device bay capabilities are designed to be written into the CDP1020 by the system BIOS at power up. The registers for this data are write-once-only and thus become read-only after the initial BIOS write.

The address selection pins (AD1 and AD0) allow the CDP1020 to occupy any one of four I<sup>2</sup>C/SMBus addresses. This enables up to four CDP1020 devices to coexist in a system.

The CDP1020 implements high current outputs for direct drive (with a limiting resistor) of the optional bay status LEDs. These indicators are two color (green/amber) common anode or anti-parallel LEDs that indicate the device bay status per the Device Bay Specification 0.90.

# Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>(°C) | PACKAGE    | PKG. NO. |

|----------------|---------------------|------------|----------|

| CDP1020        | 0 to 85             | 28 Ld SOIC | M28.3    |

For More Information Contact:

Mike Coletta (714) 433-0600

Fry Pierce (407) 729-5835

dzsc.com

#### Features

- Fully Compliant with Device Bay Specification 0.90 and ACPI Specification 1.0

- Industry Standard SMBus/I<sup>2</sup>C Interface

- Controls for Two Device Bays

- Onboard Level Shifting for Direct Drive of N-Channel MOSFET V<sub>ID</sub> Switches

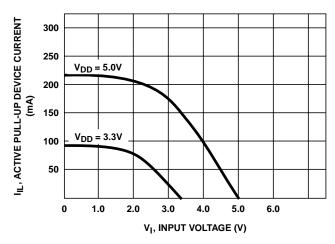

- Integrated Pull-up Resistors on 1394PRx, USBPRx, SECUREx, and REMREQx Inputs

- RC Type Oscillator Low Cost and Low Power Consumption

- Operational Voltage from 3.3 to 5.5\/li>

- "5V Tolerant" Inputs at all Operating Voltages

- Write-Once BIOS/External Configuration

- Removal Request Input for Each Bay

- Security Lock Input for Each Bay

- · High Current Device Bay LED Indicator Drivers With Separate High-Side Power Input

- Configurable Level/Pulse Bay Solenoid Drivers

- Programmable Insertion Time Out Delay

- HCMOS Technology: 28 Lead Plastic SOIC

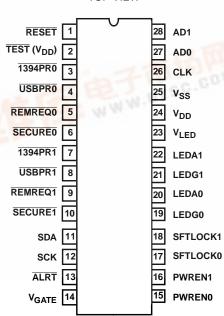

#### **Pinout**

#### CDP1020 (SOIC) TOP VIEW

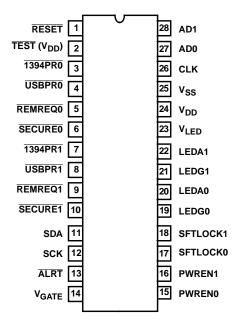

# Pin Descriptions

| PIN NUMBER | PIN NAME          | IN/OUT | PIN DESCRIPTION                                                                     |

|------------|-------------------|--------|-------------------------------------------------------------------------------------|

| 1          | RESET             | IN     | Device Bay Controller Master Reset Schmitt Input                                    |

| 2          | TEST              | -      | Test pin used by manufacturer only. Must be externally connected to V <sub>DD</sub> |

| 3          | 1394PR0           | IN     | Bay 0 1394 Presence Input with Active Pull-up                                       |

| 4          | USBPR0            | IN     | Bay 0 USB Presence Input with Active Pull-up                                        |

| 5          | REMREQ0           | IN     | Bay 0 Remove Request Input with Active Pull-up                                      |

| 6          | SECURE0           | IN     | Bay 0 Security Input with Active Pull-up                                            |

| 7          | 1394PR1           | IN     | Bay 1 1394 Presence Input with Active Pull-up                                       |

| 8          | USBPR1            | IN     | Bay 1 USB Presence Input with Active Pull-up                                        |

| 9          | REMREQ1           | IN     | Bay 1 Remove Request Input with Active Pull-up                                      |

| 10         | SECURE1           | IN     | Bay 1 Security Input with Active Pull-up                                            |

| 11         | SDA               | IN/OUT | SMBus/I <sup>2</sup> C Data Schmitt Input/Open-Drain Output                         |

| 12         | SCK               | IN/OUT | SMBus/I <sup>2</sup> C Clock Schmitt Input/Open-Drain Output                        |

| 13         | ALRT              | OUT    | SMBus Alert Open-Drain Output                                                       |

| 14         | V <sub>GATE</sub> | -      | Power Supply Input for PWREN0/PWREN1 Drivers                                        |

| 15         | PWREN0            | OUT    | Bay 0 Power Enable 12V NMOS Gate Drive Output                                       |

| 16         | PWREN1            | OUT    | Bay 1 Power Enable 12V NMOS Gate Drive Output                                       |

| 17         | SFTLOCK0          | OUT    | Bay 0 Software Controlled Lock Mechanism Driver                                     |

| 18         | SFTLOCK1          | OUT    | Bay 1 Software Controlled Lock Mechanism Driver                                     |

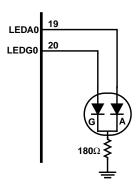

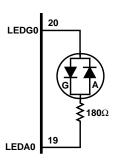

| 19         | LEDG0             | OUT    | Bay 0 Status Indicator (Green LED) Driver                                           |

| 20         | LEDA0             | OUT    | Bay 0 Status Indicator (Amber LED) Driver                                           |

| 21         | LEDG1             | OUT    | Bay 1 Status Indicator (Green LED) Driver                                           |

| 22         | LEDA1             | OUT    | Bay 1 Status Indicator (Amber LED) Driver                                           |

| 23         | V <sub>LED</sub>  | -      | Power Supply Input for LED Driver (LEDAx, LEDGx)                                    |

| 24         | V <sub>DD</sub>   | -      | Power Supply Input (Power)                                                          |

| 25         | V <sub>SS</sub>   | -      | Power Supply Return (Ground or GND)                                                 |

| 26         | CLK               | IN     | External Clock Schmitt Input (for RC oscillator)                                    |

| 27         | AD0               | IN     | SMBus/I <sup>2</sup> C Address Configuration Bit 0                                  |

| 28         | AD1               | IN     | SMBus/I <sup>2</sup> C Address Configuration Bit 1                                  |

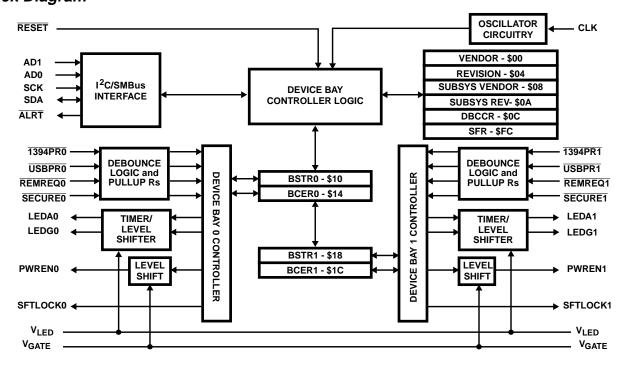

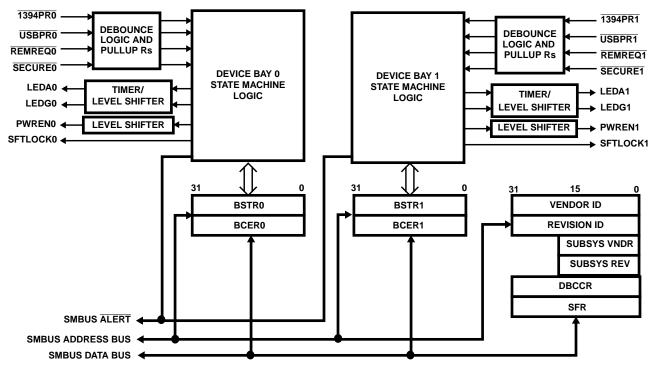

# **Block Diagram**

# **Absolute Maximum Ratings**

#

# **Thermal Information**

| Thermal Resistance (Typical, Note 1)                    | $\theta_{JA}$ (°C/W) |

|---------------------------------------------------------|----------------------|

| 28 Ld SOIC                                              | 60                   |

| Maximum Junction Temperature                            | 150 <sup>o</sup> C   |

| Maximum Storage Temperature Range (T <sub>STG</sub> )65 |                      |

| Maximum Lead Temperature (Soldering 10s)                | 300°C                |

| (SOIC - Lead Tips Only)                                 |                      |

# **Operating Conditions**

| Voltage Range           | +3.0V to +5.0V           |

|-------------------------|--------------------------|

| Temperature Range       | . 0°C to 85°C            |

| Input High Voltage (0.8 | x $V_{DD}$ ) to $V_{DD}$ |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

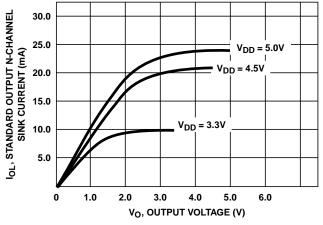

# **DC Electrical Specifications, 5.0V** $V_{DD} = 5.0V \pm 10\%$ , $T_A = 0^{\circ}C$ to $85^{\circ}C$

| PARAMETER                                                                                          | SYMBOL            | CONDITIONS                       | MIN                        | TYP                        | MAX                 | UNITS |

|----------------------------------------------------------------------------------------------------|-------------------|----------------------------------|----------------------------|----------------------------|---------------------|-------|

| Output Voltage                                                                                     |                   | -10μA < I <sub>LOAD</sub> < 10μA |                            |                            |                     |       |

| All Outputs                                                                                        | V <sub>OL</sub>   |                                  | -                          | -                          | 0.1                 | V     |

| SFTLOCK0, SFTLOCK1                                                                                 | V <sub>OH</sub>   |                                  | V <sub>DD</sub> - 0.1      | -                          | -                   | V     |

| Output High Voltage                                                                                |                   |                                  |                            |                            |                     |       |

| LEDA0, LEDG0, LEDA1, LEDG1                                                                         | V <sub>OH</sub>   | $I_{LOAD} = -16.0 \text{mA}$     | V <sub>LED</sub> - 1.0     | -                          | -                   | V     |

| SFTLOCK0, SFTLOCK1                                                                                 | V <sub>OH</sub>   | $I_{LOAD} = -0.7mA$              | V <sub>DD</sub> - 0.3      | -                          | -                   | V     |

| Output Low Voltage                                                                                 |                   |                                  |                            |                            |                     |       |

| SCK, SDA, ALRT, SFTLOCKO, SFTLOCK1,<br>LEDGO, LEDAO, LEDG1, LEDA1                                  | V <sub>OL</sub>   | I <sub>LOAD</sub> = 1.6mA        | -                          | -                          | 0.4                 | V     |

| PWREN0, PWREN1                                                                                     | V <sub>OL</sub>   | I <sub>LOAD</sub> = 60μA         | -                          | -                          | 0.4                 | V     |

| Gate Output High Voltage                                                                           |                   |                                  |                            |                            |                     |       |

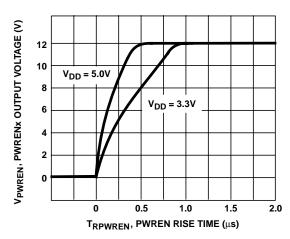

| PWREN0, PWREN1                                                                                     | V <sub>GOH</sub>  | I <sub>LOAD</sub> < 10μΑ         | V <sub>GATE</sub><br>-0.5V | V <sub>GATE</sub><br>-0.3V | V <sub>GATE</sub>   | V     |

| Gate Output Current Source                                                                         |                   |                                  |                            |                            |                     |       |

| PWREN0, PWREN1                                                                                     | I <sub>GATE</sub> |                                  | -15                        | -35                        | -50                 | μΑ    |

| Input High Voltage  1394PR0, USBPR0, REMREQ0, SECURE0, 1394PR1, USBPR1, REMREQ1, SECURE1           | V <sub>IH</sub>   |                                  | 0.7•V <sub>DD</sub>        | -                          | V <sub>DD</sub>     | V     |

| SCK, SDA                                                                                           | V <sub>IH</sub>   |                                  | 0.7•V <sub>DD</sub>        | -                          | V <sub>DD</sub>     | V     |

| RESET, CLK                                                                                         | V <sub>IH</sub>   |                                  | 0.7•V <sub>DD</sub>        | -                          | V <sub>DD</sub>     | V     |

| Input Low Voltage 1394PR0, USBPR0, REMREQ0, SECURE0, 1394PR1, USBPR1, REMREQ1, SECURE1, RESET, CLK | V <sub>IL</sub>   |                                  | V <sub>SS</sub>            | -                          | 0.2•V <sub>DD</sub> | V     |

| SCK, SDA                                                                                           | V <sub>IL</sub>   |                                  | V <sub>SS</sub>            | -                          | 0.2•V <sub>DD</sub> | V     |

| Input/Output Leakage Current: RESET, CLK, AD0, AD1, SCK, SDA, ALRT                                 | l <sub>IOL</sub>  |                                  | -                          | -                          | ±10                 | μА    |

| Input Pullup Current  1394PR0, USBPR0, REMREQ0, SECURE0, 1394PR1, USBPR1, REMREQ1, SECURE1         | I <sub>IN</sub>   |                                  | 50                         | 200                        | 400                 | μА    |

| Input Hysteresis Voltage                                                                           |                   |                                  |                            |                            |                     |       |

| SCK, SDA                                                                                           | V <sub>HYS</sub>  |                                  | 0.02                       | 0.10                       | 0.40                | V     |

| CLK                                                                                                | V <sub>HYS</sub>  |                                  | 0.6                        | 1.0                        | 1.3                 | V     |

| RESET                                                                                              | V <sub>HYS</sub>  |                                  | 0.8                        | 1.1                        | 1.4                 | V     |

# DC Electrical Specifications, 5.0V $V_{DD} = 5.0V \pm 10\%$ , $T_A = 0^{o}C$ to $85^{o}C$ (Continued)

| PARAMETER            | SYMBOL           | CONDITIONS                         | MIN | TYP | MAX | UNITS |

|----------------------|------------------|------------------------------------|-----|-----|-----|-------|

| Capacitance          | C <sub>OUT</sub> |                                    | -   | -   | 12  | pF    |

|                      | C <sub>IN</sub>  |                                    | -   | -   | 8   | pF    |

| Supply Current (RUN) | I <sub>DD</sub>  | f <sub>CLK</sub> = 4.0MHz External | -   | 1.3 | 5.0 | mA    |

# DC Electrical Specifications, 3.3V $V_{DD} = 3.3V \pm 10\%$ , $T_A = 0^{\circ}C$ to $85^{\circ}C$

| PARAMETER                                                                                           | SYMBOL            | CONDITIONS                       | MIN                        | TYP                        | MAX                 | UNITS |

|-----------------------------------------------------------------------------------------------------|-------------------|----------------------------------|----------------------------|----------------------------|---------------------|-------|

| Output Voltage                                                                                      |                   | -10μA < I <sub>LOAD</sub> < 10μA |                            |                            |                     |       |

| All Outputs                                                                                         | V <sub>OL</sub>   |                                  | -                          | -                          | 0.1                 | V     |

| SFTLOCK0, SFTLOCK1                                                                                  | V <sub>OH</sub>   |                                  | V <sub>DD</sub> - 0.1      | -                          | -                   | V     |

| Output High Voltage                                                                                 |                   |                                  |                            |                            |                     |       |

| LEDA0, LEDG0, LEDA1, LEDG1                                                                          | V <sub>OH</sub>   | $I_{LOAD} = -6.0 \text{mA}$      | V <sub>LED</sub> - 1.0     | -                          | -                   | V     |

| SFTLOCK0, SFTLOCK1                                                                                  | V <sub>OH</sub>   | I <sub>LOAD</sub> = -0.4mA       | V <sub>DD</sub> - 0.3      | -                          | -                   | V     |

| Output Low Voltage                                                                                  |                   |                                  |                            |                            |                     |       |

| SCK, SDA, ALRT, SFTLOCKO, SFTLOCK1, LEDG0, LEDA0, LEDG1, LEDA1                                      | V <sub>OL</sub>   | I <sub>LOAD</sub> = 1.6mA        | -                          | -                          | 0.4                 | V     |

| PWREN0, PWREN1                                                                                      | V <sub>OL</sub>   | I <sub>LOAD</sub> = 50μA         | -                          | -                          | 0.4                 | V     |

| Gate Output High Voltage                                                                            |                   |                                  |                            |                            |                     |       |

| PWREN0, PWREN1                                                                                      | V <sub>GOH</sub>  | I <sub>LOAD</sub> < 10μA         | V <sub>GATE</sub><br>-0.5V | V <sub>GATE</sub><br>-0.3V | V <sub>GATE</sub>   | V     |

| Gate Output Current Source                                                                          |                   |                                  |                            |                            |                     |       |

| PWREN0, PWREN1                                                                                      | I <sub>GATE</sub> |                                  | -10                        | -20                        | -30                 | μΑ    |

| Input High Voltage                                                                                  |                   |                                  |                            |                            |                     |       |

| 1394PR0, USBPR0, REMREQ0, SECURE0, 1394PR1, USBPR1, REMREQ1, SECURE1                                | V <sub>IH</sub>   |                                  | 0.7•V <sub>DD</sub>        | -                          | V <sub>DD</sub>     | V     |

| SCK, SDA                                                                                            | V <sub>IH</sub>   |                                  | 0.7•V <sub>DD</sub>        | -                          | V <sub>DD</sub>     | V     |

| RESET, CLK                                                                                          | V <sub>IH</sub>   |                                  | 0.7•V <sub>DD</sub>        | -                          | V <sub>DD</sub>     | V     |

| Input Low Voltage  1394PRŌ, ŪSBPRŌ, REMREQŌ, SECUREŌ, 1394PR1, ŪSBPR1, REMREQ1, SECURE1, RESET, CLK | V <sub>IL</sub>   |                                  | V <sub>SS</sub>            | -                          | 0.2•V <sub>DD</sub> | V     |

| SCK, SDA                                                                                            | V <sub>IL</sub>   |                                  | V <sub>SS</sub>            | -                          | 0.2•V <sub>DD</sub> | V     |

| Input/Output Leakage Current:                                                                       |                   |                                  |                            |                            |                     |       |

| RESET, CLK, AD0, AD1, SCK, SDA, ALRT                                                                | I <sub>IOL</sub>  |                                  | -                          | -                          | ±10                 | μΑ    |

| Input Pullup Current  1394PRŌ, USBPRŌ, REMREQŌ, SECUREŌ, 1394PR1, USBPR1, REMREQ1, SECURE1          | I <sub>IN</sub>   |                                  | 20                         | 80                         | 160                 | μΑ    |

| Input Hysteresis Voltage                                                                            |                   |                                  |                            |                            |                     |       |

| SCK, SDA                                                                                            | V <sub>HYS</sub>  |                                  | 0.05                       | 0.15                       | 0.45                | V     |

| CLK                                                                                                 | V <sub>HYS</sub>  |                                  | 0.4                        | 0.8                        | 1.1                 | V     |

| RESET                                                                                               | V <sub>HYS</sub>  |                                  | 0.3                        | 0.5                        | 0.8                 | V     |

| Capacitance                                                                                         | C <sub>OUT</sub>  |                                  | -                          | -                          | 12                  | pF    |

|                                                                                                     | C <sub>IN</sub>   |                                  | -                          | -                          | 8                   | pF    |

| Supply Current (RUN)                                                                                | I <sub>DD</sub>   |                                  | -                          | 0.9                        | 4.5                 | mA    |

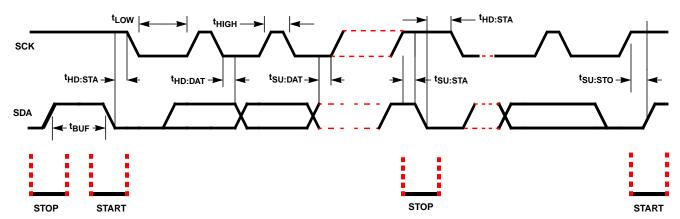

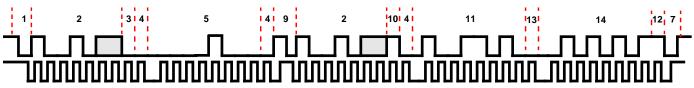

FIGURE 1. CONTROL TIMING

# **Control Timing** $V_{DD} = 3.3V \pm 10\%$ , $T_A = 0^{\circ}C$ to $85^{\circ}C$

| PARAMETER                                                    | SYMBOL                | MIN | MAX  | UNITS |

|--------------------------------------------------------------|-----------------------|-----|------|-------|

| Frequency Of Operation (4.0MHz nominal) (CLK Pin)            | fCLK                  | 2.0 | 4.5  | MHz   |

| Suspend Recovery Start-up Time                               | t <sub>RSUS</sub>     | 0.9 | 1    | ms    |

| RESET Pulse Width (RESET Pin)                                | t <sub>RL</sub>       | 6   | -    | tosc  |

| Input Debounce Time (1394PRx, USBPRx, REMREQx, SECUREx Pins) | t <sub>DB</sub>       | 50  | -    | ms    |

| SMBus SCK and SDA Pins                                       |                       |     |      |       |

| SCK Frequency                                                | f <sub>SMB</sub>      | 10  | 100  | kHz   |

| SMBus Free Time                                              | t <sub>BUF</sub>      | 4.7 | -    | μs    |

| Hold Time After (Repeated) Start Condition                   | t <sub>HD:STA</sub>   | 4.0 | -    | μs    |

| Repeated Start Condition Setup Time                          | t <sub>SU:STA</sub>   | 4.7 | -    | μs    |

| Stop Condition Setup Time                                    | tsu:sto               | 4.0 | -    | μs    |

| Data Hold Time                                               | t <sub>HD:DAT</sub>   | 300 | -    | ns    |

| Data Setup Time                                              | t <sub>SU:DAT</sub>   | 250 | -    | ns    |

| SCK Time-out Period                                          | t <sub>TIMEOUT</sub>  | 25  | 35   | ms    |

| SCK Low Period                                               | t <sub>LOW</sub>      | 4.7 | -    | μs    |

| SCK High Period                                              | tHIGH                 | 4.0 | 50   | μs    |

| Slave SCK Extend Period (cumulative)                         | tLOW:SEXT             | -   | 25   | ms    |

| Master SCK Extend Period (cumulative)                        | t <sub>LOW:MEXT</sub> | -   | 10   | ms    |

| SCK/SMBDAT Fall Time                                         | t <sub>F</sub>        | -   | 300  | ns    |

| SCK/SMBDAT Rise Time                                         | t <sub>R</sub>        | -   | 1000 | ns    |

# **Notational Conventions**

The following conventions are used throughout this document:

- Hexadecimal numbers are denoted with a "\$" symbol preceding the number.

- Binary numbers are represented with a "%" symbol proceeding the number, or a "b" following.

- Because of the large mix of active-low and active-high signals used in connection with the CDP1020, the terms "asserted" and "de-asserted" will be used exclusively. An active low signal is asserted when it is at a logic 0 and deasserted when it is at a logic 1 state. Conversely, an active high signal is at a logic 1 state when asserted and at a logic 0 state when de-asserted. The terms reset, clear,

- and "low" can also mean logic 0; set or "high" can also mean logic 1.

- Active low signals are represented with an overline; active high signals have no overline. For example, REMREQO is active low, PWRENO is active high.

- There are many pins, signals, registers, and software bits common to both Bay 0 and Bay 1; these names may include the Bay number suffix (0 or 1), an "x" to represent either, or no suffix at all. For example, PWREN, PWRENO, or PWRENx may each be used to describe output pin(s).

# Functional Pin Descriptions

This section provides a description of each of the 28 pins of the CDP1020 as shown in Figure 2.

FIGURE 2. PINOUT DIAGRAM FOR THE CDP1020

NOTE: The following pins are "5V Tolerant" Inputs at all Operating Voltages: CLK, RESET, SCK, SDA, ALRT. This means that the input voltages can range up to the maximum allowed (5V typical), regardless of the operating voltage of the IC.

# V<sub>DD</sub>, V<sub>GATE</sub>, V<sub>LED</sub>, and V<sub>SS</sub> (Power Supply)

Power is supplied to the CDP1020 using these pins.  $V_{DD}$  is connected to the positive logic supply (typically either 3.3V or 5V),  $V_{GATE}$  is connected to the positive supply for the PWREN0 and PWREN1 gate drivers (typically 12V),  $V_{LED}$  is connected to the positive power supply for the LED drivers (typically 5V), and  $V_{SS}$  is connected to the negative supply (Ground).

NOTE:  $V_{GATE}$  and  $V_{LED}$  power supplies should never be connected to the CDP1020 without the presence of the  $V_{DD}$  and  $V_{SS}$  supplies. Applying power to these inputs without the presence of the main power supply could result in a condition where all level-shifted outputs (PWRENx, LEDGx and LEDAx) track their power supply input voltage, thus enabling any of their output circuitry.

# RESET (Reset Input)

The RESET input is a low level active input, which resets the CDP1020. Resetting the device forces ALRT high and forces the device to reset the state of each bay (see *Effects Of Reset* for more details). The RESET pin contains an internal Schmitt Trigger to improve noise immunity.

# 1394PR0, 1394PR1, USBPR0, USBPR1

These four pins are the device presence inputs to the device bay controller for both bay 0 ( $\overline{1394PR0}$  and  $\overline{USBPR0}$ ) and bay 1 ( $\overline{1394PR1}$  and  $\overline{USBPR1}$ ). If the (peripheral) device uses the 1394 or USB (or both), that pin(s) on its connector

is tied to GND (active low); when a device is inserted or removed, these pins are monitored to reflect whether a device is present (or not), and which of the two busses it uses. All of these pins are CMOS inputs with internal active pull-ups to  $V_{DD}$ .

## REMREQO. REMREQ1

The  $\overline{REMREQ0}$  and  $\overline{REMREQ1}$  inputs are driven from the "REMOVE REQUEST" buttons for bay 0 and bay 1, respectively. These pins are CMOS inputs, with internal active pull-ups to  $V_{DD}$ .

## SECUREO. SECURE1

SECUREO and SECURE1 are inputs which are integral to the bay security feature; each input should be connected such that it will be asserted when an optional hardware lock is engaged for the related bay. The state of these inputs are observable by the operating system through the SL\_STS bits in the bay status registers. Both of these pins are CMOS inputs with internal active pull-ups to VDD.

# SDA (I<sup>2</sup>C/SMBus Data Input/Output)

The SDA pin is the serial data input to the SMBus interface logic of the CDP1020; it contains an internal Schmitt Trigger to improve noise immunity. When in slave-transmit mode, this pin is an open drain output. Input thresholds for the SDA input are fully compliant with SMBus Specification 1.0 (see **Electrical Specifications**). Refer to the *I*<sup>2</sup>*C/SMBus Interface* text for more details.

# SCK (I<sup>2</sup>C/SMBus Clock Input)

The SCK pin is the serial clock input to the SMBus interface logic of the CDP1020; it contains an internal Schmitt Trigger to improve noise immunity. Since the CDP1020 never acts as a SMBus master, this pin is a dedicated clock input (except for clock-stretching protocol, where it uses an opendrain low-side output). Input thresholds for the SCK input are fully compliant with SMBus Specification 1.0 (see **Electrical Specifications**). Refer to the *I*<sup>2</sup>*C/SMBus Interface* text for more details.

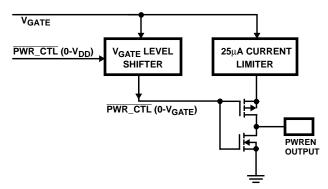

## PWREN0, PWREN1

PWREN0 and PWREN1 are the outputs from the gate drive level-shifter circuitry located on the CDP1020. These pins will output  $V_{GATE}$  (typically 12V) to drive the gates of the  $V_{ID}$  control MOSFETs per Device Bay Specification 0.90.

#### SFTLOCKO, SFTLOCK1

SFTLOCK0 and SFTLOCK1 are CMOS outputs designed to control the software locking mechanism installed in each bay. These outputs are designed to drive solenoid driver circuitry (such as an NFET), not a solenoid directly. The output can be programmed via the Special Function Register (SFR) to be a level or a pulse of a user defined duration. Refer to the *Hardware* text for more details.

#### LEDGO, LEDAO, LEDG1, LEDA1

The LEDGx and LEDAx are the output LED drive pins for the device bay status LED located in each bay. The status indicators should be two color, green/amber, common anode or anti-parallel LEDs. These pins drive the LEDs directly through an external current limiting resistor; no additional buffering is necessary. The high side of these output drivers is powered directly from the  $V_{\text{LED}}$  (typically 5V) power input and is not tied to the  $V_{\text{DD}}$  rail of the device.

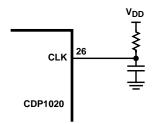

# **CLK (Clock Input)**

The Clock input (CLK) provides the time base reference for operation of the device bay controller logic, including: debounce timing, state sequencing, LED timing, etc. SMBus transfers between the CDP1020 and the SMBus Host controller are not based on the clock input. The clock input of the CDP1020 has the circuitry necessary for oscillating an external resistor-capacitor circuit, as shown in Figure 3. External clock sources (like those from a can oscillator) should **not** be used with the CDP1020.

FIGURE 3. RC OSCILLATOR CONFIGURATION

The CDP1020 is designed to operate optimally with an input frequency of 4MHz. All of the internal timing, including debounce, insertion delay, and solenoid pulse durations are based on a 4MHz input. While the CDP1020 will operate over a wide range of frequency, a nominal input frequency of 4MHz is strongly recommended. Refer to the *Hardware Interface* text at the end of this document for more information on the RC oscillator, including recommended RC values.

# ALRT (I<sup>2</sup>C/SMBus Alert Output)

The  $\overline{\text{ALRT}}$  pin is the used by the CDP1020 to signal the SMBus Host Controller that an interrupt event within the controller has occurred and the device wishes to be read by the operating system. This pin is an open drain output. Refer to the  $I^2$ C/SMBus Interface text for more details.

#### ADO, AD1

AD0 and AD1 are sampled by the CDP1020 immediately after reset and are used as the 2 least significant bits of the  $I^2$ C/SMBus slave address of the CDP1020. These pins are CMOS inputs, and should be tied to the same power plane as the device ( $V_{DD}$  for a logic high;  $V_{SS}$  for a logic low).

Through the use of these pins, up to four devices may be placed on the same bus (addresses \$90, \$92, \$94, \$96).

#### **TEST**

TEST is a CMOS input used only by Intersil for testing, and is not recommended for the user; it **must** be externally connected to V<sub>DD</sub>.

# I<sup>2</sup>C/SMBus Interface

The CDP1020 contains a standard implementation of an  $I^2$ C/SMBus serial interface. The CDP1020 is always an  $I^2$ C/SMBus slave device. Its serial interface supports single or burst mode reads and writes using standard  $I^2$ C/SMBus mechanisms.

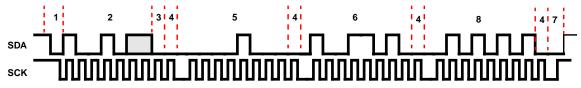

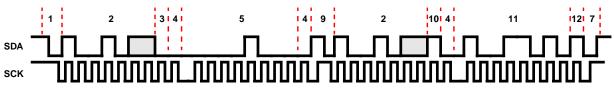

# Reading from and Writing to the CDP1020

The I $^2$ C/SMBus slave address of the CDP1020 is %10010XXY, where the "XX" bits are defined by the AD1:AD0 input pins, and the "Y" is the R/W (Read/Write) bit. Every access of the CDP1020 begins when the I $^2$ C/SMBus master generates a start condition (or repeated start condition) followed by transmitting an address/control byte with the address equal to the CDP1020's slave address and the R/ $\overline{W}$  bit set appropriately. Note that the R/ $\overline{W}$  bit can be considered the 8th (Least Significant Bit) in the address, even though that may not be the standard I $^2$ C/SMBus notation.

A write operation is defined as the condition when the  $I^2C/SMB$ us master transmits the slave address with the  $R/\overline{W}$  bit clear. A read operation is defined as the transmission of the CDP1020 slave address with the  $R/\overline{W}$  bit set. Thus, when looked upon as an 8-bit address, write operations will have even addresses (for example, \$90), while read operations will be odd (\$91).

For write operations, the command byte following the address/control byte is used to set the internal *address pointer* of the CDP1020. An I<sup>2</sup>C/SMBus *send byte* command will therefore behave as a "set the address pointer" command. The address pointer is initialized to \$00 following a reset. The byte written to the CDP1020 immediately following an address/control byte with the R/W bit clear will always be used to set the CDP1020 internal address pointer.

Subsequent bytes written to the CDP1020 in a transmission following the address/command and address pointer bytes are written directly into the register space of the CDP1020. The address pointer of the CDP1020 is auto-incrementing; once a byte is written into the register space, the address pointer increments to the next location. In this way multiple byte writes to adjacent address locations within the CDP1020 may be performed within a single I<sup>2</sup>C/SMBus transmission. Figure 5 shows examples for a single byte and a multiple byte write to the CDP1020.

Read operations are performed when the  $I^2$ C/SMBus master transmits a start condition and the CDP1020 slave address with the  $R/\overline{W}$  bit set. Following the address/command byte

the CDP1020 will transmit data to the master beginning at the CDP1020 register location pointer to by the internal address pointer. In accordance with I<sup>2</sup>C/SMBus protocols, the CDP1020 will continue to transmit data to the master until it receives a negative acknowledge from the master.

NOTE: Due to the nature of the CDP1020  $I^2$ C/SMBus interface module, a master device cannot simply end a read operation by transmitting a stop condition. The master is required to not-acknowledge the last byte of a read operation. Only when the CDP1020 detects this negative acknowledge will it end transmission and wait for another start condition.

As with write operations, the internal address pointer of the CDP1020 will automatically increment after each byte is transmitted during a read operation. In this way multiple bytes can be read from the CDP1020 register space within a single  $I^2$ C/SMBus transmission.

Figure 4 demonstrates single and multiple byte read sequences, both of which begin with a send byte command followed by a restart and read command. This technique forces the address pointer to the desired address prior to the read(s) and, while not strictly necessary, is strongly recommended.

Note that writing to un-implemented registers will be ignored (the data will not be stored anywhere). Reading unimplemented registers will produce undefined results.

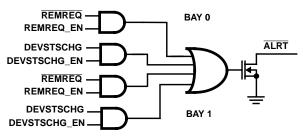

#### I<sup>2</sup>C/SMBus Alert Function

The CDP1020 is a slave only I<sup>2</sup>C/SMBus device. As such, it has no capability to start a transmission on the serial bus to notify the master of an *interrupt event* within the CDP1020 control logic (Interrupt events are described in more detail in the *Device Bay Control Logic* text). To notify the master of such an event, the CDP1020 implements the SMBus alert function as detailed in the SMBus specification.

When an interrupt event (interrupt events are described in the *Device Bay Control Logic* text) within the CDP1020 occurs, it will assert its  $\overline{ALRT}$  signal. The  $\overline{ALRT}$  pin is an active low, open drain output that must have an external pullup resistor. The assertion of this signal is an indication to the master that an interrupt condition within the CDP1020 has occurred and needs service.

FIGURE 4. ALRT OUTPUT LOGIC

The master device may respond in two different ways to the assertion of the  $\overline{ALRT}$  pin - one way using the SMBus Alert

feature of SMBus control modules (such as the PiiX4/PiiX6) and the other way using a general purpose I/O to monitor the ALRT signal of the CDP1020 and I<sup>2</sup>C messaging to service the alert.

In the SMBus method, the ALRT pin of the CDP1020 should be tied to the general purpose SMBus alert signal going into the SMBus controller. This signal may have many other devices connected to it in addition to the CDP1020. When the SMBus alert line is pulled low by any of the SMBus devices, the SMBus controller will send out an Alert Response Address (ARA), %00011001 (\$19, with the  $R/\overline{W}$ bit set). Any slave device that is currently asserting its ALRT signal will respond to the ARA by sending the master its slave address. If there are multiple devices asserting the ALRT signal, they will use standard SMBus arbitration techniques to determine ownership of the bus. Once a slave successfully transmits a response to the ARA, it will deassert its ALRT signal. On the occurrence of any interrupt event, the CDP1020 will assert its ALRT pin. Once this pin is asserted, the CDP1020 will now respond to an SMBus ARA.

NOTE: The present CDP1020 does not support the SMBus ARA response, but a future mask option fully implements it. The same is true for a General Call (\$00 address to broadcast to all devices on bus). Thus, if the SMBus alert signal is used, the SMBus controller should poll the CDP1020 (similar to the description in the next paragraph) to determine if it created the interrupt (it can separately issue the ARA to see if any other device responds to it; the CDP1020 will not).

For  $I^2C$  systems or SMBus systems that do not implement the SMBus alert feature, the  $\overline{ALRT}$  pin of the CDP1020 should be connected to a separate interrupt pin or general purpose input of the  $I^2C$ /SMBus master and monitored. When the master detects that the  $\overline{ALRT}$  signal of the CDP1020 has been asserted, it should perform a read operation on the CDP1020 using the standard read protocol described in the previous section. If multiple devices share the same input to the master, the software will have to check each device to determine which one caused the Alert.

Note that if the  $\overline{\text{ALRT}}$  pin is only monitored in software (instead of using a more immediate interrupt), then the latency needs to be considered, such that there is not a noticeable or objectionable delay in the response time (for example, if the user pushes the  $\overline{\text{REMREQ}}$  button repeatedly, or inserts and removes a device repeatedly because of no apparent response).

As shown in Figure 4, the CDP1020 will only de-assert its ALRT signal when the cause of the interrupt event is cleared (by clearing either the status or enable bit). This is true whether the SMBus ARA or the general purpose I/O method is used.

FIGURE 5B. MULTIPLE BYTE WRITE OPERATION (WRITE \$9A TO CDP1020 REGISTER \$08, \$55 TO REGISTER \$09)

FIGURE 5C. SINGLE BYTE READ OPERATION (READ \$9A FROM CDP1020 REGISTER \$08)

FIGURE 5D. MULTIPLE BYTE READ OPERATION (READ \$9A FROM CDP1020 REGISTER \$08, \$55 FROM REGISTER \$09)

FIGURE 5. CDP1020 I<sup>2</sup>C/SMBUS TRANSMISSION PROTOCOLS

TABLE 1.

| NUMBER | R DESCRIPTION                                                                                                                    |    | DESCRIPTION                                                                                                                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Start Condition, generated by I <sup>2</sup> C/SMBus master (defined as negative edge on SDA while SCK is high).                 | 8  | 2nd data byte written to the CDP1020. This data will be written to the register location set by the command byte, plus one.                                              |

| 2      | CDP1020 I <sup>2</sup> C/SMBus slave address (7 bits)                                                                            | 9  | Repeated start condition                                                                                                                                                 |

| 3      | R/W bit, cleared indicating a write operation                                                                                    |    | R/W bit, set indicating a read operation                                                                                                                                 |

| 4      | Acknowledge from CDP1020 (ack; active low on SDA)                                                                                | 11 | 1st byte of data read from the CDP1020, read from the CDP1020 register location set by the command byte in the write portion of the transmission.                        |

| 5      | Command byte sent from I <sup>2</sup> C/SMBus master. This data will be used to set the internal address pointer of the CDP1020. | 12 | Negative master acknowledge. This signals to the CDP1020 that the master is done reading data and the CDP1020 should end transmission.                                   |

| 6      | 1st data byte written to the CDP1020. This data will be written into the register specified by the command byte.                 | 13 | Master Acknowledge. This is an indication from the master that the read data has been received and the CDP1020 should continue to transmit data.                         |

| 7      | Stop condition, generated by the I <sup>2</sup> C/SMBus master (defined as a positive edge on SDA while SCK is high).            | 14 | 2nd data byte of read transmission. This data is read from the CDP1020 register location set by the command byte during the write portion of the transmission, plus one. |

FIGURE 6. CDP1020 CONTROL LOGIC BLOCK DIAGRAM

# **Device Bay Control Logic**

The Device Bay Control Logic unit of the CDP1020 contains all of the state machine control logic for both device bays, the register set, debounce logic for the presence and remove request inputs, and the timer logic for the Device Bay status LEDs and software lock solenoids. All inputs from the Device Bays are received from the Input/Output Control Block. A block diagram of the Control Logic is shown in Figure 6.

#### **Programming Model**

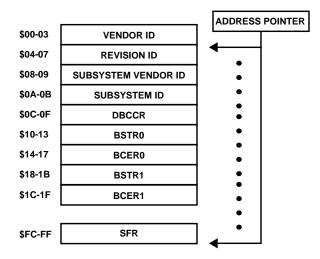

There are ten registers within the CDP1020, all of which may be read by the operating system at any time through the serial interface. The first nine registers implement the ACPI-based register set compliant with Device Bay Specification 0.90. The tenth register (SFR) provides control of other features not explicitly defined in Device Bay Specification 0.90. A memory map of the CDP1020 register space is shown in Figure 7.

The second byte transferred at the beginning of every SMBus write operation defines the address of a byte to access. Once the address is specified, it is stored in the CDP1020's address pointer. Subsequent reads or writes will access the register selected by the address pointer.

The address pointer will be incremented following each access facilitating burst mode accesses of sequential bytes in the CDP1020. Following access of the byte at \$FF the address will increment to \$00. Reading of unimplemented registers will produce undefined results.

Although the CDP1020 memory map is organized into ten multi-byte registers (8 4-byte registers and 2 2-byte

registers), the BIOS/operating system is not required to read or write entire registers. All reads and writes take place at a byte granularity. For example, to write to the DBCCR, the BIOS needs to only write a single byte to address location \$0C. The other three bytes of the DBCCR register (\$0D:\$0F) do not have to be written to.

FIGURE 7. CDP1020 REGISTER SET/MEMORY MAP

NOTE: It is strongly recommended that all write-once-only registers and bits are programmed after a reset operation, even if the bits happen to be reset to the desired state, so that a noise transient during the address of a later write operation doesn't inadvertently write new data to any of those locations.

NOTE: The register set in the CDP1020 is implemented in littleendian format, as specified in Device Bay Specification 0.90. As such, the least significant byte in any register is in the lowest memory address for that register; likewise the most significant byte is in the highest memory address. In the DBCCR, for example, the least significant byte (containing the configuration data) is at address \$0C. The most significant byte (containing all 0's) is at address \$0F. The following subsections describe each of the registers

within the CDP1020.

## Vendor ID Register, \$00

Per Device Bay Specification 0.90, the first register in the CDP1020 register set is the Vendor ID register. The contents of this register identify the manufacturer of the Device Bay Controller. This register is a read-only register that contains \$1260, the 16-bit Intersil Corporation PCI SIG identification number. This number is contained in the lower two bytes of the register; the upper two bytes are always read as \$0000.

| Bits 31:16 | Bits 15:0                    |      |

|------------|------------------------------|------|

| \$0000     | \$1260 (Intersil PCI-SIG ID) | \$00 |

## Revision ID Register, \$04

The Revision ID register contains the 8-bit device bay controller manufacturer revision ID. This number is used to identify a particular Device Bay controller from the manufacturer specified in the Vendor ID register. The Revision ID is a read-only register that contains the 8-bit revision code for the CDP1020. This number is contained in the lower byte of the register; the upper three bytes are always read as \$000000.

| Bits 31:8 | Bits 7:0    |      |

|-----------|-------------|------|

| \$000000  | Revision ID | \$04 |

# Subsystem Vendor ID Register, \$08

The Subsystem Vendor ID Register is used to identify the manufacturer of the device bay system that the CDP1020 is installed in. This register is implemented as a write-onceonly register and is designed to be written by the system BIOS immediately after either the power-on-reset, or asserting the RESET pin, which enables a write to this register. Once written, this register becomes read-only and should contain the 16-bit subsystem manufacturer identification number. This register and the Subsystem ID register are the only 16-bit registers in the CDP1020.

| Bits 15:0           |      |

|---------------------|------|

| Subsystem Vendor ID | \$08 |

#### Subsystem ID Register, \$0A

The Subsystem ID register contains a 16-bit subsystem vendor defined ID number. Typically, this number would

define the device bay system revision or model number. Like the Subsystem Vendor ID, this register is implemented as a write-once-only register and is designed to be written by the system BIOS immediately after either the power-on-reset, or asserting the RESET pin, which enables a write to this register. Once written, this register becomes read-only. This register and the Subsystem Vendor ID register are the only 16-bit registers in the CDP1020.

| Bits 15:0    |      |

|--------------|------|

| Subsystem ID | \$0A |

# Device Bay Controller Capabilities Register, \$0C

The Device Bay Controller Capabilities Register (DBCCR) is designed to allow the operating system to easily identify the features of the Device Bay system controlled by the CDP1020. This register contains five write-once-only bits, defined below. These bits, like those in the Subsystem Vendor ID Register, are designed to be written by the system BIOS immediately after power-on. Once written, they become read-only. The upper 27 bits of the DBCCR are always read as 0 This register is set to \$00000002 at reset (two bays, no security locks).

| Bits 31:5 | Bit 4   | Bits 3:0    |      |

|-----------|---------|-------------|------|

| \$00000   | SECLOCK | BAYCNT[3:0] | \$0C |

#### **BITS 31:5**

Reserved for future use. Always read as 0.

#### SECLOCK

The SECLOCK bit indicates the presence of an optional physical security lock on at least one of the device bays controlled by the CDP1020. If set, then at least one of the device bays has the physical security lock, the state of which is available in the bay status register BSTRx. If clear, no physical security lock exists in the system. SECLOCK is implemented as a write-once-only bit intended to be written by the BIOS immediately after system power-on. Once written to, this bit becomes read-only.

#### BAYCNT[3:0]

The four BAYCNT bits represent the number of bays controlled by the CDP1020 in binary form. These bits, like the SECLOCK bit, are implemented as a write-once-only bits intended to be written by the BIOS immediately after system power-on. Once written to, they become read-only. Since the CDP1020 is a two bay controller, the only valid values that can be written to the BAYCNT[3:0] bits are 0, 1 and 2. If the OS tries to write any other value, the CDP1020 will write a value of 2 (%0010) to this bit field.

## Bay Control and Enable Register, BCERx

The CDP1020 incorporates two separate bay control and enable registers, one for each bay. The organization of these two registers is identical. BCER0 is located at address \$10; BCER1 is at \$18. Both BCER registers are cleared at reset.

#### **BITS 31:8**

Reserved. Always read as 0.

#### BIT 7, LOCK\_CTL

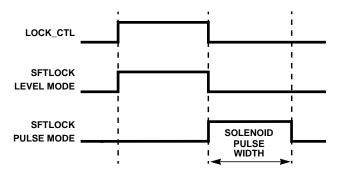

The LOCK\_CTL is a read/write bit that controls the software controlled solenoid interlock for each bay. This bit has two distinct modes of operation, depending on the value written into the SOL[3:0] bits in the SFR.

If the SOL[3:0] bits in the SFR contain any nonzero value, the LOCK\_CTL bit logic is in "pulsed" mode. In pulse mode, the SFTLOCK output will be asserted for a fixed time duration when the LOCK\_CTL is changed from a logic 1 to a logic 0. Writing a 0 to this bit while it is already 0 has no effect. Writing a 1 to this bit while it is a 0 will set the bit, but will not affect the SFTLOCK output. The duration of the SFTLOCK pulse is controlled by the SPD and SOL[3:0] bits in the SFR. Refer to the *Special Function Register* text for more details.

If the SOL[3:0] bit in the SFR are all 0, the LOCK\_CTL circuitry is in "level" mode. In this case, the SFTLOCK output corresponding to the LOCK\_CTL bit will simply follow the state of the LOCK\_CTL bit. When the LOCK\_CTL is set, the SFTLOCK output will be high; likewise, when the LOCK\_CTL bit is clear, the SFTLOCK output will be low. Figure 7 shows the relationship between the LOCK\_CTL bit and its corresponding SFTLOCK output in both level and pulsed modes.

# BITS 6:4, BAY\_STREQ[2:0]

This three bit field represents the state of the bay as requested by the operating system. It does not necessarily represent the actual state of the bay. The states are represented as such:

| 000 | No change requested                   |

|-----|---------------------------------------|

| 001 | Request Bay State = Device Inserted   |

| 010 | Request Bay State = Device Enabled    |

| 011 | Request Bay State = Removal Requested |

| 100 | Request Bay State = Removal Allowed   |

| 101 | Reserved                              |

| 110 | Reserved                              |

| 111 | Reserved                              |

|     |                                       |

If 000 is written, then no change to the current bay state is requested and the current nonzero value of this field is retained. This allows the operating system to modify other bits in this register without affecting the bay state. A bay state change will only occur when these fields are written if a device is inserted ( $\overline{1394PRx}$  &  $\overline{USBPRx}$  = 0). These bits may be read or written at any time by the operating system. These bits are cleared by any hardware transition to the Bay Empty State (i.e., device removal).

#### BIT 3, REMREQ EN

This read/write bit allows the operating system to enable/disable internal CDP1020 interrupts and bay state transitions due to a logic "0" input value of the REMREQx pin. If this bit is clear, the CDP1020 will not notify the OS and will not transition the bay state to Removal Requested when the REMREQx button has been pushed. If this bit is set after the REMREQ\_STS bit in the BSTR has been set, an interrupt event will be generated and a bay status change will occur. This bit is cleared by reset.

#### BIT 2, DEVSTSCHG\_EN

This is a read/write bit that enables/disables internal CDP1020 interrupt events and bay state transitions due to the setting of the DEVSTSCHG bit in the BSTR. If this bit is clear, the CDP1020 will not notify the OS whenever the bay state has changed. The DEVSTSCHG bit in the BSTRx will still reflect a bay state change.

The DEVSTSCHG\_EN bit also allows the CDP1020 to automatically transition the bay state to Device Inserted when an insertion event is the cause of the DEVSTSCHG. Hardware transitions to the Bay Empty state will always occur on a device removal, regardless of the state of the DEVSTSCHG\_EN bit. This bit is cleared by reset.

## BIT 1, REMEVTWAK\_EN

This bit enables/disables internal CDP1020 interrupt events due to device removal. This bit gates the device removal event in the DEVSTSCHG logic (see Bay Status Register, below). The intent is to conditionally allow device removal as a wake-up event.

If clear, this bit will prevent the DEVSTSCHG flag in the BSTR from being set when a device is removed and the bay is in the Removal Allowed state. A hardware transition to the Bay Empty state will still occur. This bit does not affect any of the interrupt logic if the bay is not in the Removal Allowed state. This bit is cleared by reset.

# BIT 0, PWR\_CTL

The PWR\_CTL is the enable bit for the  $V_{ID}$  power rail. When set, the internal logic of the CDP1020 will output the  $V_{GATE}$  voltage level on the PWREN pin associated with this register. (Refer to the **Power Enable System** text for more details) When clear, the PWREN pin will be pulled down to  $V_{SS}$  by a standard N-Channel output driver. This allows the gate voltage of the  $V_{ID}$  control MOSFET to be discharged quickly and the device switched off. No external pull down resistor is necessary.

This bit is cleared by reset. This bit cannot be set if there is no device in the bay  $(\overline{1394PRx} \& \overline{USBPRx} = 1)$  or if the LOCK\_CTL bit is clear. If set and a device is suddenly removed (i.e., without OS permission), the CDP1020 will clear this bit and disable the PWRENx output.

Note: A single write to the BCER may set both the LOCK\_CTL and PWR\_CTL bits at the same time.

#### Bay Status Register, BSTRx

Like the Bay Control and Enable register, there is one Bay Status register associated with each bay controlled by the CDP1020. The addresses for the BSTR registers are \$14 (BSTR0) and \$20 (BSTR1). Both BSTR registers are cleared at reset.

#### **BITS 31:11**

Reserved, always read as 0.

# BITS 10:8, BAY\_FF[2:0]

This three bit field indicates the form factor of the controlled bay:

| 000      | DB32     |

|----------|----------|

| 001      | DB20     |

| 010      | DB13     |

| 011- 111 | Reserved |

These bits are write-once only bits after a power-on reset and should be written by the system BIOS or the operating system at start-up. Once written, these bits become read-only. Subsequent internal and external resets do not affect the write status of these bits. The value of these bits is indeterminate at power on and are not affected by any type of reset.

#### BIT 7, SL STS

The read only SL\_STS indicates the state of the external security lock. This bit simply reflects the inverted state of the SECUREx pin. If clear, external security lock is disengaged. If set, the lock is engaged.

The state of this bit depends on the external state of the SECUREx pin and the state of the SECLOCK bit in the DBCCR register (see above). If the SECLOCK bit is clear, this bit will always read as a "0". If SECLOCK is set, the state of this bit will reflect the inverted state of the SECUREx pin.

## BIT 6:4, BAY\_ST[2:0]

This three bit field represents the actual state of the bay. These bits are read only. The bay state is represented as such:

| 000 | Bay Empty              |  |

|-----|------------------------|--|

| 001 | Device Inserted        |  |

| 010 | Device Enabled         |  |

| 011 | Removal Requested      |  |

| 100 | Device Removal Allowed |  |

| 101 | Reserved               |  |

| 110 | Reserved               |  |

| 111 | Reserved               |  |

Bay states and how they are controlled is described in the **State Machine Logic** text.

#### BIT 3, REMREQ\_STS

This bit indicates that the removal request button for this bay has been pressed (REMREQx pin has been driven low). This bit is referred to as a "sticky status bit"; once set, the you must write a "1" to this bit position to clear it. If the REMREQ\_EN bit in the associated control register is set, the CDP1020 will generate a REMREQ interrupt event when this bit is set. A REMREQ interrupt event will cause a hardware transition of the bay state to Removal Allowed and assert the ALRT pin of the CDP1020 to notify the OS of the REMREQx button press.

#### **BIT 2, DEVSTSCHG**

This bit indicates that a hardware event has occurred that has changed the status of the device bay. This could be caused by a device insertion or a device removal. This bit, like the REMREQ\_STS bit, is a sticky status bit; once set, the OS must write a "1" to clear it.

This bit will be set on all device removals except when the REMEVTWAK\_EN bit in the BCER is clear and the bay is in the Removal Allowed state.

If the DEVSTSCHG bit is set due to an insertion event and the DEVSTSCHG\_EN bit in the BCER is set, the CDP1020 will hardware transition the bay state to Device Inserted and assert the ALRT pin to notify the system of the insertion. This bit is cleared by reset.

#### BIT 1, 1394PRSN\_STS

This bit reflects the inverted state of the  $\overline{1394PRx}$  pin associated with this status register. If the  $\overline{1394PRx}$  pin is high, this bit will read cleared. If the  $\overline{1394PRx}$  pin is low (1394 device inserted) this pin will read high. The setting of this bit can generate a device status change event. This bit is cleared by reset.

# BIT 0, USBPRSN\_STS

This bit reflects the inverted state of the USBPRx pin associated with this status register. If the USBPRx pin is high, this bit will read cleared. If the USBPRx pin is low (USB device inserted) this pin will read high. The setting of this bit can generate a device status change event. This bit is cleared by reset.

-----

## Special Function Register, \$FC

The Special Function Register (SFR) allows control of various features not explicitly defined in the Device Bay Specification 0.90. This register contains write-once-only bits, which are designed to be written by the system BIOS immediately after power-on. Once written, they become read-only. The upper 24 bits of the SFR are always read as 0. All bits are cleared on reset.

**BITS 31:8**

Reserved for future use. Always read as 0...

| Bits 31:8 | Bits 7:5 | Bits 4:1 | Bit 1 |      |

|-----------|----------|----------|-------|------|

| \$00000   | ITO[2:0] | SOL[3:0] | SPD   | \$FC |

#### **BITS 31:8**

Reserved for future use. Always read as 0.

#### BITS 7:5, ITO[2:0]

Bits 7, 6 and 5 define the Insertion Time-Out (ITO) bits field of the SFR.

These bits allow the OS/BIOS to specify the amount of time the CDP1020 will wait, from when it detects the insertion of a device until it notifies the OS. The insertion time-out should be used to allow Device Bay devices time to settle mechanically into the bay before they are enabled.

The 3-bit ITO field defines the time-out in 8 discrete increments of 800ms (nominal at 4MHz). The table below shows typical time-out values.

#### **INSERTION TIME-OUT VALUES (NOMINAL AT 4MHz)**

| ITO[2:0] | TIME-OUT VALUE |

|----------|----------------|

| 000      | 0s             |

| 001      | 0.8s           |

| 010      | 1.6s           |

| 011      | 2.4s           |

| 100      | 3.2s           |

| 101      | 4.0s           |

| 110      | 4.8s           |

| 111      | 5.6s           |

Please note that these time-out values do not account for the fact that all presence inputs are debounced for 50ms before any time-out period begins. The time-out defaults to 0 after reset.

#### SOL[3:0]

The SOL[3:0] bits, along with the SPD bit, control the configuration and duration of the software lock solenoid drive pulse. Once written to, these bits become read-only.

If %0000 is written to the SOL[3:0] bits, the solenoid output is put into "level" mode. In level mode, the SFTLOCK output simply follows the state of the corresponding LOCK\_CTL bit (see Figure 8).

If a nonzero value is written to the SOL[3:0] bits, then the solenoid control output is put into "pulsed" mode. In this mode, the solenoid output is pulsed anytime the LOCK\_CTL bit is written from a 1 to a 0 (refer to Figure 8). The length of the pulse is determined by both the value written into the SOL[3:0] bits and the SPD bit.

With the SPD bit clear, the solenoid control circuitry is set to output short pulses. In terms of a prescaler, the solenoid pulse width is the value of the SOL[3:0] x 50ms. With the SPD bit set, the solenoid control is in long pulse mode. Here, the prescaler is set to SOL[3:0] x 800ms. The table below shows solenoid pulse widths for all values of SOL[3:0] and the SPD bit.

#### **SOLENOID PULSE WIDTHS (NOMINAL AT 4MHz)**

| SOL[3:0] | SOLENOID PULSE, SOLENOID PUL<br>SPD = 0 SPD = 1 |       |

|----------|-------------------------------------------------|-------|

| 0000     | LEVEL                                           | LEVEL |

| 0001     | 50ms                                            | 0.8ms |

| 0010     | 100ms                                           | 1.6s  |

| 0011     | 150ms                                           | 2.4s  |

| 0100     | 200ms                                           | 3.2s  |

| 0101     | 250ms                                           | 4.0s  |

| 0110     | 300ms                                           | 4.8s  |

| 0111     | 350ms                                           | 5.6s  |

| 1000     | 400ms                                           | 6.4s  |

| 1001     | 450ms                                           | 7.2s  |

| 1010     | 500ms                                           | 8.0s  |

| 1011     | 550ms                                           | 8.8s  |

| 1100     | 600ms                                           | 9.6s  |

| 1101     | 650ms                                           | 10.4s |

| 1110     | 700ms                                           | 11.2s |

| 1111     | 750ms                                           | 12.0s |

NOTE: Writing to SOL[3:0] bits will clear all LOCK\_CTL bits and SFTLOCK outputs. Because these bits in the SFR are write-once-only, this situation will only occur on the first write. Subsequent writes to these bits will not cause the LOCK\_CTL bits to clear.

#### **SPD**

The SPD bit controls the length of the solenoid pulse when in pulse mode: long pulses If set, short pulses If clear. If the SOL[3:0] bits are clear, the SPD bit has no effect.

FIGURE 8. LOCK\_CTL BIT/SFTLOCK OUTPUT

RELATIONSHIP IN LEVEL AND PULSE MODES

# Effects of Reset

#### Resets

The CDP1020 has two reset modes: an active low external reset pin (RESET) and an internal power-on reset function. Both are logically OR'ed together internally.

#### **RESET** Pin

The RESET input pin is used to provide an orderly start-up procedure and return the CDP1020 to a known state. When using the external reset mode, the RESET pin must stay low for a minimum of six (6) oscillator cycles (typically 1.5µs with a 4MHz clock). The RESET pin contains an internal Schmitt Trigger to improve noise immunity.

#### Power-On Reset

The internal power-on reset occurs when a positive transition is detected on  $V_{DD}$ . The power-on reset is used strictly for power turn-on conditions and should not be used to detect any drops in the power supply voltage. There is no provision for a power-down reset.

The power-on circuitry provides a two oscillator cycle delay from the time that the oscillator becomes active. If the external RESET pin is low at the end of the time out, the CDP1020 remains in the reset condition until RESET goes high. The following list contains the actions of reset on internal circuits, but not necessarily in order of occurrence.

- BCER0 and BCER1 reset to \$00000000

- BSTR0 and BSTR1 reset to \$00000000

- SFR reset to \$00000000

- · All PWREN, SFTLOCK, and LED outputs cleared

- DBCCR set to two bays, no security locks \$00000002

- · All Write-Once permissions reset

- AD0 and AD1 inputs sampled for I<sup>2</sup>C/SMBus address

- Internal address pointer reset to \$00

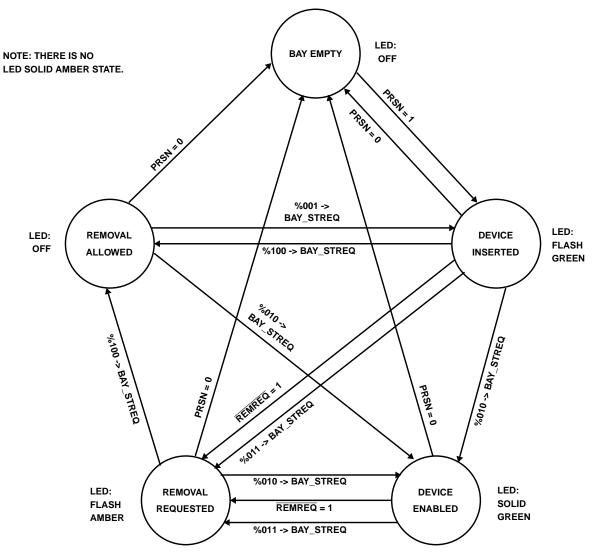

# State Machine Logic

The CDP1020 contains two functionally identical state machine logic blocks, one for each bay. Each of these blocks is responsible for monitoring external Device Bay events (i.e., device insertion, device removal, remove requests), controlling the locking mechanism and power enable signal for each bay, updating the state of the bay in response to OS commands and external events as shown in Figure 9.

There are five separate functional states that each bay of the CDP1020 can be in at any one time. Each of the two bay controllers within the CDP1020 functions completely independently of the other. The following sections detail state machine operation in each of the five states, including state transitions, operating system responsibility, and I/O functions.

In the following sections, the bay state controller will be referred to generically; that is as a bay "x" controller. Thus, bay "x" has a control register BCERx, a status register BSTRx, and so on.

The state of the device bay controller is changed through either hardware events (device inserted, device removed) and software events (OS writes into CDP1020 registers can change the bay state under certain conditions).

## Interrupt Events

An interrupt event is defined as one of the following:

- The insertion of a device into a bay with the corresponding DEVSTSCHG EN bit set

- Removal of a device after the insertion time-out in any state other than Removal Allowed and the DEVSTSCHG EN bit is set

- Removal of a device in the Removal Allowed state with both the REMWAKEVT and DEVSTSCHG\_EN flags set

- User assertion of the REMREQ input when the associated REMREQ\_EN bit is set and a device is present in the bay

2 ----

FIGURE 9. CDP1020 BAY STATE DIAGRAM

The first events listed above is known as an *insertion interrupt event*. On an insertion interrupt event, the bay state machine is transitioned to the Device Inserted state, the bay status LED is set to flash green, and the  $\overline{ALRT}$  output is asserted to notify the OS of the device insertion.

The second and third events are *removal interrupt events*. If the DEVSTSCHG\_EN flag is set, the CDP1020 will assert its ALRT output to notify the OS of the device removal. Regardless of the state of the DEVSTSCHG\_EN bit, the CDP1020 will always transition the bay state to Bay Empty, clear the PWREN flag, turn of the PWREN output, and clear the bay state request field of the associated BCER.

The last event is a *remove request event*. When a user presses the REMREQ button on a bay with a device inserted, the CDP1020 will set the REMREQ\_STS flag for that bay. If the REMREQ\_EN bit is set, the CDP1020 will assert its ALRT output to notify the OS.

Figure 4 shows the output logic for the ALRT pin. As shown in this diagram, an interrupt event can be generated by setting an enable flag after the status bit has been set by some hardware event. For example, the REMREQ\_EN flag is clear and a user presses the REMREQ button. The CDP1020 will set the REMREQ\_STS flag, but will not generate an interrupt event. Now, the OS sets the REMREQ\_EN flag. As soon as this occurs, the CDP1020 will assert its ALRT output and generate a REMREQ interrupt event.

#### Insertion Time Out

When a device is inserted into a bay, it will make electrical contact with device bay connector very quickly. However, in most systems there will need to a delay while the user releases the device and it settles into the bay itself.

The insertion time out function of the CDP1020 allows a system designer to specify a delay time that the CDP1020 will wait before notifying the OS that a device has been inserted. This

delay time is set at system power on whenever the CDP1020 is initialized by writing the appropriate value into the ITO[2:0] bit field of the SFR. As shown in the SFR text, the insertion timeout delay can range from 0s to 5.6s in increments of 800ms.

The feature that makes the CDP1020 insertion time out function different from a simple insertion delay is that the CDP1020 will begin to flash the bay status LED green immediately after the device has been detected (if the DEVSTSCHG\_EN flag for the bay is set). This is important because it gives the user instant feedback that the device has been recognized.

It is important to note that even though the bay status LED is flashing, the CDP1020 has not responded to the device insertion. During the insertion time out period, the status bits (1394PRSN\_STS and USBPRSN\_STS) remain clear and the bay state is NOT transitioned in the Device Inserted state. Thus, if the OS were to read the CDP1020 during the insertion time out period, it would not know that a device was in the bay.

Once the insertion time out period is over, the CDP1020 will generate an insertion event (assuming the DEVSTSCHG\_EN flag is set) and the state controller will enter the Device Inserted state.

It is important to note that while waiting for the insertion time out, the CDP1020 has not fully registered the device in the bay. Thus, if the device were forcibly removed during this time, a removal event would not be generated. The CDP1020 would simply reset the insertion time out counter and stop flashing the bay status LED.

## Bay Empty

A bay empty state is defined exclusively as both the presence inputs for the bay (1394PRx and USBPRx) de-asserted. The state of these pins is controlled by the insertion and removal of devices in the bay. As shown in Figure 9, the insertion of a device (and the assertion of one or both of the presence pins) causes the CDP1020 to recognize that a device is in the bay. If the DEVSTSCHG\_EN flag for the bay is set, an insertion interrupt event will be generated and the state machine to transition bay state from Bay Empty (%000) to Device Inserted (%001).

Typically the Bay Empty state will be returned to from either the Device Inserted state (before the device has been enabled) or the Device Removal Allowed state (after the OS has powered down the device). However, the Bay Empty state can also be entered from Removal Requested and Device Enabled states if the device was forcibly removed from the system. In all cases, if the CDP1020 detects that both presence pins have been deasserted, the Bay Empty state will be entered and the PWREN output for the V<sub>ID</sub> MOSFET gate driver will be disabled.

The bay empty state is reflected by the bay state machine by setting BAY\_ST[2:0] field (bits 6:4 of the bay status register) to %000. The bay empty state can be entered from any of

the other four bay states and is entered exclusively through hardware transitions controlled by the CDP1020; OS writing into the BCER cannot change the bay state to Bay Empty.

Entering the Bay Empty state from any state other than Removal Allowed will cause the CDP1020 to generate a removal interrupt event if the DEVSTSCHG\_EN bit in the BCER is set. A removal event will be generated if the bay was in the Removal Allowed state and both the REMEVTWAK the DEVSTSCHG\_EN bits in the BCER are set. In both cases, the CDP1020 will notify the host system via the ALRT pin.

In the Bay Empty state the bay status LED (LEDGx and LEDAx) outputs will be off.

## **Device Inserted State**

The Device Inserted state, %001, is entered in one of two manners. When a device is inserted, the CDP1020 will transition to the Device Inserted state (after the insertion time out period) if the DEVSTSCHG\_EN bit for the bay in question is set. In such a case, the CDP1020 will generate an insertion event, set the DEVSTSCHG bit in the BSTR, flash the bay status LED green and notify the OS through the  $\overline{ALRT}$  pin.

Alternately, the OS can transition the CDP1020 to the Device Inserted state by writing a %001 to the BAY\_STREQ bit field in the BCER. This can only be done from any other bay state as long as a device is inserted in the bay.

While in the CDP1020 is in the Device Inserted state the OS will typically engage the software controlled lock for the bay, enable  $V_{\text{ID}}$  to the bay and enumerate the device on its native communication bus. While in this state, the bay status LED will flash green at 1Hz.

#### Device Enabled

In the Device Enabled state, the device inserted into the bay has  $V_{\text{ID}}$  enabled and is fully functional. This state cannot be entered through hardware action; only the OS writing %010 to the BAY\_STREQ bits in the BCER can transition the bay state to Device Enabled.

In the Device Enabled state, if the presence pins are deasserted at any time, the CDP1020 hardware will automatically transition the bay state to Bay Empty, clear the PWR\_CTL bit and disable the PWRENx outputs. The PWRENx and PWR\_CTL states are not affected by the state transitions to the Device Enabled state.

While in this state the bay status LED will be solid green.

## Device Removal Requested

The Device Removal Requested state, like the Device Inserted state, can be entered either through an OS write to the BCERx or through hardware actions.