# TrueTri⊳ngle **Product Specifications** July 2002

(1 of 4)

#### **Features**

- ☐ InGaP HBT Technology

- ☐ 6mm Square, 50 Ohm Power Module Package

- **☐** Single Positive Supply

- ☐ 35% Linear Power Added Efficiency

- **□** 50% Analog Power Added Efficiency

- □ +28.5 dBm Output Power (CDMA Mode)

- **□ 30 dB Gain at Operating Output Power**

- **☐** On-Board Power Down Mode

#### **Applications**

- **☐** Cellular Multi-Mode Handsets

- **☐** Cellular Infrastructure

- **☐** Wireless Local Loop Subscriber Units

- **□** CDMA Handsets

- ☐ CDMA2K 1X Handsets

## **Description**

The CHP0230-PM is a 50 ohm matched, single supply, linear power amplifier module intended for use in cellular handsets and wireless local loop subscriber units. The highly integrated amplifier meets the requirements of CDMA and CDMA2K 1X systems. It is a member of Celeritek's new **TrueTriangle**<sup>™</sup> family of 3V power amplifier modules.

The CHP0230-PM is packaged in a low-cost, space

efficient, 6mm square, matched module that provides excellent

# 824 to 849 MHz 28.5 dBm, Cellular **InGaP HBT Amplifier Module**

electrical stability and low thermal resistance. The module operates from a fixed positive voltage and requires no external matching which significantly reduces space, cost and enhances ease of use.

The 6x6 mm package is self contained, incorporating 50 ohm input and output matching networks optimized for output power, linearity and efficiency.

Celeritek's InGaP HBT technology offers a thermally robust and reliable PAM (power amplifier module) solution.

#### **Absolute Maximum Ratings**

| Parameter                             | Rating  | Parameter                             | Rating | Parameter             | Rating           |

|---------------------------------------|---------|---------------------------------------|--------|-----------------------|------------------|

| Collector Voltage (+V <sub>cc</sub> ) | +6.0 V* | Reference Voltage (V <sub>ref</sub> ) | +3.1 V | Operating Temperature | -40°C to +100°C  |

| Collector Current (I <sub>cc</sub> )  | 1.2 A   | Power Dissipation                     | 5 W    | Storage Temperature   | -65°C to +150°C  |

| RF Input Power                        | 7 dBm   |                                       |        | Soldering Temperature | 260°C for 5 Sec. |

<sup>\*</sup> RF Off.

## **Recommended Operating Conditions**

| Parameter                                                      | Тур           | Units | Parameter                        | Тур        | Units |

|----------------------------------------------------------------|---------------|-------|----------------------------------|------------|-------|

| Collector Voltage (+V <sub>cc</sub> )                          | 3.2 to 4.1    | Volts | Operating Temperature (PC Board) | -20 to +70 | °C    |

| Reference Voltage (V <sub>ref</sub> )<br>(Fixed and regulated) | +2.95 (±1.2%) | Volts | MP -                             |            |       |

#### **Application Information**

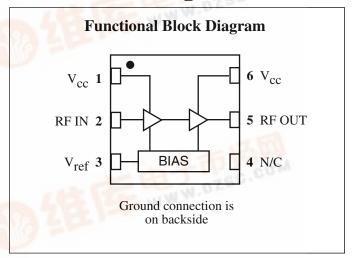

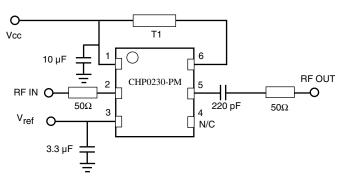

The CHP0230-PM is a two-stage amplifier that requires a single regulated positive supply along with the unregulated battery voltage for proper operation. Vref is a regulated 2.95 reference voltage for the bias control circuitry. It can also be used as a power down mode select. Vcc is an unregulated supply voltage directly from the battery. Vcc should be applied prior to Vref and before RF input power. The CHP0230-PM can be operated over a range of supply voltages and bias points by adjustment of Vref. It is important that the maximum power dissipation of the package be observed at all times and that the maximum Voltage across the device is not exceeded.

### **Circuit Design Considerations**

**Biasing** The positive Vcc supply voltages are applied to pins 1 and 6. Most bypass decoupling is provided on-board. Vref is applied to pin 3.

The recommended DC bypass capacitance is shown in the schematic diagram on Page 4.

Inadequate bypass capacitance and inductance around the DC supply lines can compromise the adjacent channel power ratio (ACPR), reduce power gain and/or create oscillations.

# TrueTri>ngle™

#### **Electrical Characteristics**

Unless otherwise specified, the following specifications are guaranteed at room temperature with collector voltage  $(+V_{CC}) = 3.6 \text{ V}$ .

| Parameter                                           | Condition                                         | Min | Тур   | Max | Units     |

|-----------------------------------------------------|---------------------------------------------------|-----|-------|-----|-----------|

| Frequency Range                                     |                                                   | 824 |       | 849 | MHz       |

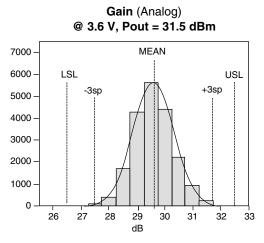

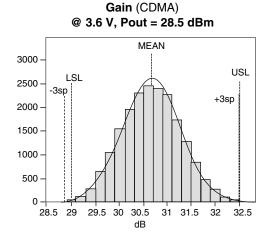

| Gain                                                | @ Digital power output                            | 29  | 30    | 33  | dB        |

| Gain Ripple*                                        | 824-849 MHz                                       |     |       | 1.5 | dB        |

| Gain Variation                                      | Over supply voltage                               |     | 2     |     | dB/V      |

|                                                     | Over temperature                                  |     | 0.03  |     | dB/°C     |

| Power Output                                        | CDMA mode                                         |     | +28.5 |     | dBm       |

|                                                     | Analog                                            |     | +31.0 |     | dBm       |

| Harmonics                                           | 2nd @ Po = +31.5 dBm                              |     | -30   |     | dBc       |

|                                                     | 3rd @ Po = +31.5 dBm                              |     | -30   |     | dBc       |

| Noise Power in Receive Band                         | 30 kHz bandwidth                                  |     | -90   |     | dBm       |

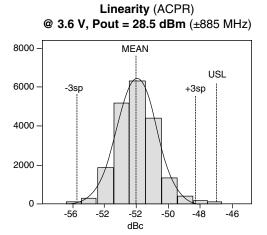

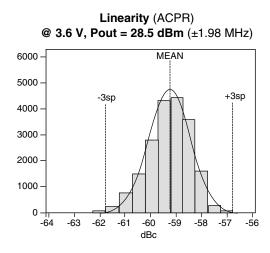

| Linearity (ACPR)                                    | CDMA mode @ +28.5 dBm Pout, 885 kHz offset        |     | -52   | -47 | dBc/30KHz |

|                                                     | CDMA mode @ +28.5 dBm Pout, 1.9 MHz offset        |     | -59   | -56 | dBc/30KHz |

|                                                     | CDMA2K 1X mode** @ +27.8 dBm Pout, 885 kHz offset |     | -49   | -47 | dBc/30KHz |

|                                                     | CDMA2K 1X mode** @ +27.8 dBm Pout, 1.9 MHz offset |     | -58   | -56 | dBc/30KHz |

| Noise Figure                                        |                                                   |     | 4.0   | 5.0 | dB        |

| Input Return Loss                                   |                                                   |     | -10   |     | dB        |

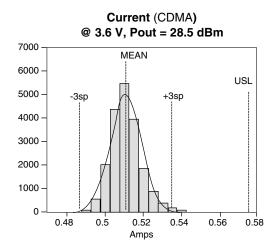

| $\overline{I_{cc}} (V_{cc} = 3.6 \text{ V})$        | Pout = $+12.0 \text{ dBm} - \text{CDMA mode}$     |     | 105   | 112 | mA        |

|                                                     | Pout = $+28.5 \text{ dBm} - \text{CDMA mode}$     |     | 515   | 560 | mA        |

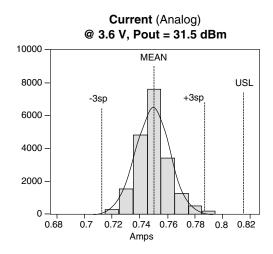

|                                                     | Pout = $+31.5$ dBm - Analog mode                  |     | 750   | 815 | mA        |

| Quiescent Current (I <sub>q</sub> )                 | No RF                                             |     | 60    |     | mA        |

| V <sub>ref</sub> Supply Current (I <sub>ref</sub> ) |                                                   |     | 2.0   | 5.0 | mA        |

| V <sub>ref</sub> Supply Voltage (V <sub>ref</sub> ) | Fixed and regulated (1.2% tolerance)              |     | 2.95  |     | V         |

| Leakage Current                                     | $V_{ref} = 0 \text{ V}, V_{cc} = 3.6 \text{ V}$   |     |       | 10  | μΑ        |

<sup>\*</sup> Specifications guaranteed over the temperature range of -20°C to +70°C. \*\* Modulation HPSK in 1.2288 MHz, RC3 PAR = 4.7 @ 1% CCDF.

- Continued from Page 1 -

**Modulation** When biased as specified, the CHP0230-PM will achieve the required adjacent channel response for the digital system specified. Celeritek tests 100% of each product under digital modulation to ensure correlation to customer applications.

#### **Thermal**

- 1. The ground pad on the backside of the CHP0230-PM must be soldered to the ground plane.

- 2. All leads of the package must be soldered to the appropriate electrical connection.

## **Product Specifications - July 2002**

# TrueTri>ngle<sup>TM</sup>

## **Product Consistency Distribution**

Note: Unless otherwise specified, the following data was taken at 836 MHz.

# **CHP0230-PM**

# TrueTri>ngle<sup>™</sup>

#### **Recommended Application Circuit**

Note: This schematic represents the topology of the application circuit recommended by Celeritek.

T1 line is important to ensure best bypassing. Optimum performance is achieved through an electrical length of 20°min. at 835 MHz.

**Evaluation Board Schematic**

Board substrate:

ER = 4.60

Thickness = 0.031 in.

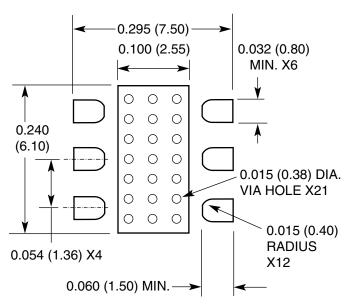

#### **PCB Footprint** (Minimum Pad Dimensions)

DIMENSIONS IN INCHES (mm)

DRAWING NOT TO SCALE

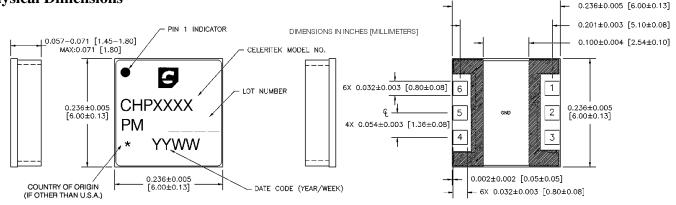

#### **Physical Dimensions**

#### **Ordering Information**

The CHP0230-PM is available in a surface mount 50 ohm matched module and devices are available in tube or tape and reel.

Part Number for Ordering

**Package**

CHP0230-PM-0000

PM6 surface mount power package in tube

CHP0230-PM-000T

PM6 surface mount power package in tape and reel

PB-CHP0230-PM

**Evaluation Board with SMA connectors for CHP0230-PM**

Celeritek reserves the right to make changes without further notice to any products herein. Celeritek makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Celeritek assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Celeritek does not convey any license under its patent rights nor the rights of others. Celeritek products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Celeritek product could create a situation where personal injury or death may occur. Should Buyer purchase or use Celeritek products for any such unintended or unauthorized application, Buyer shall indemnify and hold Celeritek and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Celeritek was negligent regarding the design or manufacture of the part. Celeritek is a registered trademark of Celeritek, Inc. Celeritek, Inc. is an Equal Opportunity/Affirmative Action Employer.