## 捷多邦,专业PCB打样工厂,24小时加急出货

June 2001

1.5 MHz (min)

67.5 dB (min)

200 mW (max)

580 ns (typ)

Guaranteed

National Semiconductor

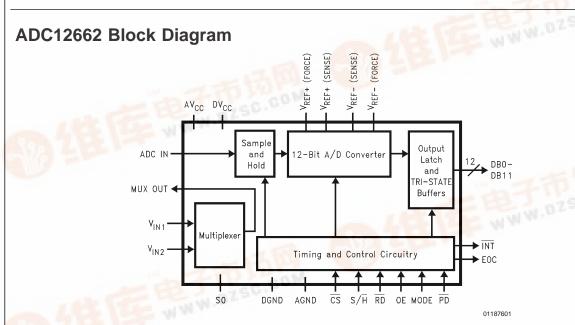

## ADC12662 12-Bit, 1.5 MHz, 200 mW A/D Converter with Input Multiplexer and Sample/Hold **General Description Features**

Using an innovative multistep conversion technique, the 12-bit ADC12662 CMOS analog-to-digital converter digitizes signals at a 1.5 MHz sampling rate while consuming a maximum of only 200 mW on a single +5V supply. The ADC12662 performs a 12-bit conversion in three lower-resolution "flash" conversions, yielding a fast A/D without the cost and power dissipation associated with true flash approaches.

The analog input voltage to the ADC12662 is tracked and held by an internal sampling circuit, allowing high frequency input signals to be accurately digitized without the need for an external sample-and-hold circuit. The ADC12662 features two sample-and-hold/flash comparator sections which allow the converter to acquire one sample while converting the previous. This pipelining technique increases conversion speed without sacrificing performance. The multiplexer output is available to the user in order to perform additional external signal processing before the signal is digitized.

When the converter is not digitizing signals, it can be placed in the Standby mode; typical power consumption in this mode is 250 µW.

- Built-in sample-and-hold

- Single +5V supply

- Single channel or 2 channel multiplexer operation

- Low Power Standby mode

## **Key Specifications**

- Sampling rate

- Conversion time

- Signal-to-Noise Ratio, f<sub>IN</sub> = 100 kHz

- Power consumption ( $f_s = 1.5$  MHz)

- No missing codes over temperature

## Applications

- Digital signal processor front ends

- Instrumentation

- Disk drives

- Mobile telecommunications

- Waveform digitizers

## **Ordering Information**

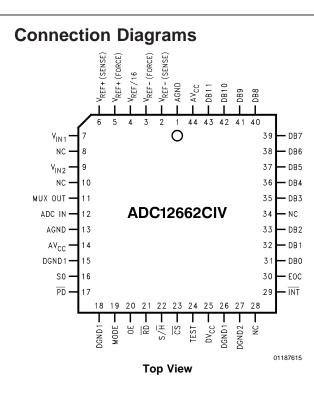

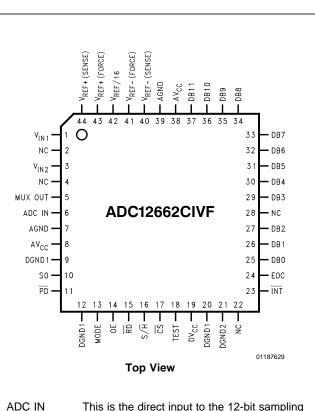

| Industrial (-40°C $\leq$ T <sub>A</sub> $\leq$ +85°) | Package                          |

|------------------------------------------------------|----------------------------------|

| ADC12662CIV                                          | V44 Plastic Leaded Chip Carrier  |

| ADC12662CIVF                                         | VGZ44A Plastic Quad Flat Package |

ADC12662 12-Bit, 1.5 MHz, 200 mW A/D Converter with Input Multiplexer and Sample/Hold

## **Pin Descriptions**

| AV <sub>CC</sub>                    | These are the two positive analog supply inputs. They should always be connected to the same voltage source, but are brought out separately to allow for separate bypass capacitors. Each supply pin should be bypassed to AGND with a $0.1  \mu F$ ceramic capacitor in parallel with a $10  \mu F$ tantalum capacitor.                                                                                                                                                                                                                                               |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DV <sub>CC</sub>                    | This is the positive digital supply input. It should always be connected to the same voltage as the analog supply, $AV_{CC}$ . It should be bypassed to DGND2 with a 0.1 $\mu$ F ceramic capacitor in parallel with a 10 $\mu$ F tantalum capacitor.                                                                                                                                                                                                                                                                                                                   |

| AGND,                               | DGND1,<br>DGND2<br>These are the power supply ground pins.<br>There are separate analog and digital ground<br>pins for separate bypassing of the analog<br>and digital supplies. The ground pins should<br>be connected to a stable, noise-free system<br>ground. All of the ground pins should be<br>returned to the same potential. AGND is the<br>analog ground for the converter. DGND1 is<br>the ground pin for the digital control lines.<br>DGND2 is the ground return for the output<br>databus. See Section 6.0 LAYOUT AND<br>GROUNDING for more information. |

| DB0–DB11                            | These are the TRI-STATE output pins, enabled by $\overline{\text{RD}}$ , $\overline{\text{CS}}$ , and OE.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>IN1</sub> , V <sub>IN2</sub> | These are the analog input pins to the multiplexer. For accurate conversions, no input pin (even one that is not selected) should be driven more than 50 mV below ground or 50 mV above $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                                                                 |

| MUX OUT                             | This is the output of the on-board analog input multiplexer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

This is the direct input to the 12-bit sampling A/D converter. For accurate conversions, this pin should not be driven more than 50 mV below ground or 50 mV above  $V_{CC}$ .

- This pin selects the analog input that will be connected to the ADC12662 during the conversion. The input is selected based on the state of S0 when EOC makes its high-to-low transition. Low selects  $V_{\rm IN1}$ , high selects  $V_{\rm IN2}$ .

- MODE This pin should be tied to DGND1.

- This is the active low Chip Select control input. When low, this pin enables the  $\overline{RD}$ , S/ $\overline{H}$ , and OE inputs. This pin can be tied low.

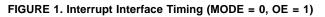

- This is the active low Interrupt output. When using the Interrupt Interface Mode (*Figure 1*), this output goes low when a conversion has been completed and indicates that the conversion result is available in the output latches. This output is always high when RD is held low (*Figure 2*).

- This is the End-of-Conversion control output. This output is low during a conversion.

- This is the active low Read control input. When  $\overline{\text{RD}}$  is low (and  $\overline{\text{CS}}$  is low), the  $\overline{\text{INT}}$  output is reset and (if OE is high) data appears on the data bus. This pin can be tied low.

- This is the active high Output Enable control input. This pin can be thought of as an inverted version of the  $\overline{RD}$  input (see *Figure 6*). Data output pins DB0–DB11 are TRI-STATE when OE is low. Data appears on DB0–DB11 only when OE is high and  $\overline{CS}$ and  $\overline{RD}$  are both low. This pin can be tied high.

- This is the Sample/Hold control input. The analog input signal is held and a new conver-

**S**0

CS

INT

EOC

RD

OE

S/H

| Pin Desc                                                                           | criptions (Continued)                                                                                                                                   |                      | information.                                                                                                            |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|

| sion is initiated by the falling edge control input (when $\overline{CS}$ is low). | sion is initiated by the falling edge of this control input (when $\overline{CS}$ is low).                                                              | $V_{REF+(SENSE)},$   | V <sub>REF-(SENSE)</sub><br>These are the positive and negative voltage<br>reference sense pins, respectively. See Sec- |

| PD                                                                                 | This is the Power Down control input. This pin should be held high for normal operation.                                                                |                      | tion 4, REFERENCE INPUTS, for more information.                                                                         |

|                                                                                    | When this pin is pulled low, the device goes into a low power standby mode.                                                                             | V <sub>REF</sub> /16 | This pin should be bypassed to AGND with a 0.1 µF ceramic capacitor.                                                    |

| $V_{REF+(FORCE)}$ ,                                                                | $V_{\text{REF-(FORCE)}}$<br>These are the positive and negative voltage reference force inputs, respectively. See Section 4, REFERENCE INPUTS, for more | TEST                 | This pin should be tied to $DV_CC.$                                                                                     |

## Absolute Maximum Ratings (Notes 1,

### 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage ( $V_{CC} = DV_{CC} =$ |                                 |

|---------------------------------------|---------------------------------|

| AV <sub>CC</sub> )                    | -0.3V to +6V                    |

| Voltage at Any Input or Output        | -0.3V to V <sub>CC</sub> + 0.3V |

| Input Current at Any Pin (Note 3)     | 25 mA                           |

| Package Input Current (Note 3)        | 50 mA                           |

| Power Dissipation (Note 4)            |                                 |

| ADC12662CIV                           | 875 mW                          |

| ESD Susceptibility (Note 5)           | 2000V                           |

| Soldering Information (Note 6)        |                                 |

| V Package, Infrared, 15 seconds       | +300°C                          |

| VF Package                   |                 |

|------------------------------|-----------------|

| Vapor Phase (60 seconds)     | 215°C           |

| Infrared (15 seconds)        | 220°C           |

| Storage Temperature Range    | –65°C to +150°C |

| Maximum Junction Temperature |                 |

| (T <sub>JMAX</sub> )         | 150°C           |

## Operating Ratings (Notes 1, 2)

| Temperature Range         | $T_{MIN} \leq T_{A} \leq T_{MAX}$ |

|---------------------------|-----------------------------------|

| ADC12662CIV, ADC12662CIVF | $-40^{\circ}C \le T_A \le$        |

|                           | +85°C                             |

| Supply Voltage Range      |                                   |

| $(DV_{CC} = AV_{CC})$     | 4.75V to 5.25V                    |

|                           |                                   |

## **Converter Characteristics**

The following specifications apply for  $DV_{CC} = AV_{CC} = +5V$ ,  $V_{REF+(SENSE)} = +4.096V$ ,  $V_{REF-(SENSE)} = AGND$ , and  $f_s = 1.5$  MHz, unless otherwise specified. Boldface limits apply for  $T_A = T_J$  from  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = +25^{\circ}C$ .

| Symbol              | Parameter                              | Conditions                                          | Тур      | Limit                                   | Units              |

|---------------------|----------------------------------------|-----------------------------------------------------|----------|-----------------------------------------|--------------------|

|                     |                                        |                                                     | (Note 7) | (Note 8)                                | (Limit)            |

|                     | Resolution                             |                                                     |          | 12                                      | Bits               |

|                     | Differential Linearity Error           | T <sub>MIN</sub> to T <sub>MAX</sub>                | ±0.4     | ±0.95                                   | LSB (max)          |

|                     | Integral Linearity Error<br>(Note 9)   | T <sub>MIN</sub> to T <sub>MAX</sub>                | ±0.4     | ±1.5                                    | LSB (max)          |

|                     | Offset Error                           | T <sub>MIN</sub> to T <sub>MAX</sub>                | ±0.3     | ±2.0                                    | LSB (max)          |

|                     | Full-Scale Error                       | T <sub>MIN</sub> to T <sub>MAX</sub>                | ±0.3     | ±1.5                                    | LSB (max)          |

|                     | Power Supply Sensitivity<br>(Note 15)  | $DV_{CC} = AV_{CC} = 5V \pm 5\%$                    |          | ±0.75                                   | LSB (max)          |

| R <sub>REF</sub>    | Reference Resistance                   |                                                     | 1000     | 600<br>1300                             | Ω (min)<br>Ω (max) |

| V <sub>REF(+)</sub> | V <sub>REF+(SENSE)</sub> Input Voltage |                                                     |          | AV <sub>cc</sub>                        | V (max)            |

| V <sub>REF(-)</sub> | V <sub>REF-(SENSE)</sub> Input Voltage |                                                     |          | AGND                                    | V (min)            |

| V <sub>IN</sub>     | Input Voltage Range                    | To $V_{\text{IN1}},V_{\text{IN2}},\text{or}$ ADC IN |          | AV <sub>CC</sub> +0.05V<br>AGND – 0.05V | V (max)<br>V (min) |

|                     | ADC IN Input Leakage                   | AGND to AV <sub>CC</sub> – 0.3V                     | 0.1      | 3                                       | μA (max)           |

| C <sub>ADC</sub>    | ADC IN Input Capacitance               |                                                     | 25       |                                         | pF                 |

|                     | MUX On-Channel Leakage                 | AGND to AV <sub>CC</sub> – 0.3V                     | 0.1      | 3                                       | µA (max)           |

|                     | MUX Off-Channel Leakage                | AGND to AV <sub>CC</sub> – 0.3V                     | 0.1      | 3                                       | μA (max)           |

| C <sub>MUX</sub>    | Multiplexer Input Cap                  |                                                     | 7        |                                         | pF                 |

|                     | MUX Off Isolation                      | $f_{IN} = 100 \text{ kHz}$                          | 92       |                                         | dB                 |

### Dynamic Characteristics (Note 10)

The following specifications apply for  $DV_{CC} = AV_{CC} = +5V$ ,  $V_{REF+(SENSE)} = +4.096V$ ,  $V_{REF-(SENSE)} = AGND$ ,  $R_S = 25\Omega$ ,  $f_{IN} = 100$  kHz, 0 dB from fullscale, and  $f_s = 1.5$  MHz, unless otherwise specified. **Boldface limits apply for T\_A = T\_J from T\_{MIN} to T\_MAX;** all other limits  $T_A = T_J = +25^{\circ}C$ .

| Symbol | Parameter            | Conditions                           | Тур      | Limit    | Units    |

|--------|----------------------|--------------------------------------|----------|----------|----------|

|        |                      |                                      | (Note 7) | (Note 8) | (Limit)  |

| SINAD  | Signal-to-Noise Plus | T to T                               | 70       | 67.0     | dB (min) |

|        | Distortion Ratio     | T <sub>MIN</sub> to T <sub>MAX</sub> | 70       | 07.0     |          |

### Dynamic Characteristics (Note 10) (Continued)

The following specifications apply for  $DV_{CC} = AV_{CC} = +5V$ ,  $V_{REF+(SENSE)} = +4.096V$ ,  $V_{REF-(SENSE)} = AGND$ ,  $R_S = 25\Omega$ ,  $f_{IN} = 100$  kHz, 0 dB from fullscale, and  $f_s = 1.5$  MHz, unless otherwise specified. **Boldface limits apply for T\_A = T\_J from T\_{MIN} to T\_MAX;** all other limits  $T_A = T_J = +25^{\circ}C$ .

| Symbol | Parameter                  | Conditions                           | Тур      | Limit    | Units      |

|--------|----------------------------|--------------------------------------|----------|----------|------------|

|        |                            |                                      | (Note 7) | (Note 8) | (Limit)    |

| SNR    | Signal-to-Noise Ratio      | T to T                               | 70       | 67.5     | dB (min)   |

|        | (Note 11)                  | T <sub>MIN</sub> to T <sub>MAX</sub> | 10       | 07.5     | UB (IIIII) |

| THD    | Total Harmonic Distortion  | T to T                               | -80      | -70      | dBc (max)  |

|        | (Note 12)                  | T <sub>MIN</sub> to T <sub>MAX</sub> | -00      | -70      |            |

| ENOB   | Effective Number of Bits   | T 454                                | 11.0     | 40.0     | Dite (min) |

|        | (Note 13)                  | T <sub>MIN</sub> to t <sub>MAX</sub> | 11.3     | 10.8     | Bits (min) |

| IMD    | Intermodulation Distortion | f <sub>IN</sub> = 88.7 kHz, 89.5 kHz | -80      |          | dBc        |

## **DC Electrical Characteristics**

The following specifications apply for  $DV_{CC} = AV_{CC} = +5V$ ,  $V_{REF+(SENSE)} = +4.096V$ ,  $V_{REF-(SENSE)} = AGND$ , and  $f_s = 1.5$  MHz, unless otherwise specified. Boldface limits apply for  $T_A = T_J$  from  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = +25^{\circ}C$ .

| Symbol               | Parameter                                              | Conditions                                                                     | Typ<br>(Note 7) | Limit<br>(Note 8) | Units<br>(Limit)   |

|----------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|-----------------|-------------------|--------------------|

| V <sub>IN(1)</sub>   | Logical "1" Input Voltage                              | $DV_{CC} = AV_{CC} = +5.5V$                                                    |                 | 2.0               | V (min)            |

| V <sub>IN(0)</sub>   | Logical "0" Input Voltage                              | $DV_{CC} = AV_{CC} = +4.5V$                                                    |                 | 0.8               | V (max)            |

| I <sub>IN(1)</sub>   | Logical "1" Input Current                              |                                                                                | 0.1             | 1.0               | μA (max)           |

| I <sub>IN(0)</sub>   | Logical "0" Input Current                              |                                                                                | 0.1             | 1.0               | μA (max)           |

| V <sub>out(1)</sub>  | Logical "1" Output Voltage                             | $DV_{CC} = AV_{CC} = +4.5V,$ $I_{OUT} = -360 \ \mu A$ $I_{OUT} = -100 \ \mu A$ |                 | 2.4<br>4.25       | V (min)<br>V (min) |

| V <sub>OUT(0)</sub>  | Logical "0" Output Voltage                             | $DV_{CC} = AV_{CC} = +4.5V,$ $I_{OUT} = 1.6 \text{ mA}$                        |                 | 0.4               | V (max)            |

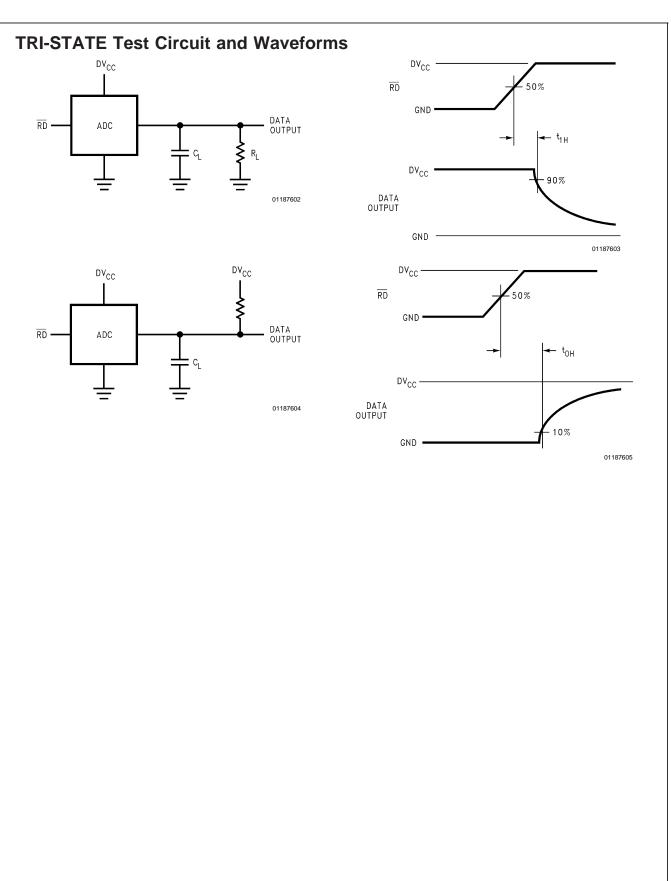

| lout                 | TRI-STATE <sup>®</sup> Output<br>Leakage Current       | Pins DB0-DB11                                                                  | 0.1             | 3                 | μA (max)           |

| C <sub>OUT</sub>     | TRI-STATE Output Capacitance                           | Pins DB0–DB11                                                                  | 5               |                   | pF                 |

| C <sub>IN</sub>      | Digital Input Capacitance                              |                                                                                | 4               |                   | pF                 |

| DI <sub>CC</sub>     | DV <sub>CC</sub> Supply Current                        |                                                                                | 2               | 3                 | mA (max)           |

| Al <sub>cc</sub>     | AV <sub>CC</sub> Supply Current                        |                                                                                | 32              | 37                | mA (max)           |

| I <sub>STANDBY</sub> | Standby Current (DI <sub>CC</sub> + AI <sub>CC</sub> ) | $\overline{PD} = 0V$                                                           | 50              |                   | μA                 |

## **AC Electrical Characteristics**

The following specifications apply for  $DV_{CC} = AV_{CC} = +5V$ ,  $V_{REF+(SENSE)} = +4.096V$ ,  $V_{REF-(SENSE)} = AGND$ , and  $f_s = 1.5$  MHz, unless otherwise specified. Boldface limits apply for  $T_A = T_J$  from  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = +25^{\circ}C$ .

| Symbol            | Parameter                       | Conditions | Тур      | Limit    | Units     |

|-------------------|---------------------------------|------------|----------|----------|-----------|

|                   |                                 |            | (Note 7) | (Note 8) | (Limits)  |

| f                 | Maximum Sampling Rate           |            |          | 1.5      | MHz (min) |

| f <sub>s</sub>    | (1/t <sub>throughput</sub> )    |            |          | 1.5      |           |

| t <sub>CONV</sub> | Conversion Time                 |            | 590      | 510      | ns (min)  |

|                   | (S/H Low to EOC High)           |            | 580      | 660      | ns (max)  |

| +                 | Aperture Delay                  |            | 20       |          | 20        |

| t <sub>AD</sub>   | (S/H Low to Input Voltage Held) |            | 20       |          | ns        |

| . –               | S/H Pulse Width                 |            | 10       | 5        | ns (min)  |

| t <sub>S/H</sub>  |                                 |            | 10       | 400      | ns (max)  |

| +                 | S/H Low to EOC Low              |            | 00       | 60       | ns (min)  |

| t <sub>EOC</sub>  |                                 |            | 90 12    | 126      | ns (max)  |

### AC Electrical Characteristics (Continued)

The following specifications apply for  $DV_{CC} = AV_{CC} = +5V$ ,  $V_{REF+(SENSE)} = +4.096V$ ,  $V_{REF-(SENSE)} = AGND$ , and  $f_s = 1.5$  MHz, unless otherwise specified. Boldface limits apply for  $T_A = T_1$  from  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_1 = +25^{\circ}C$ .

| Symbol                            | Parameter                                                              | Conditions                          | Тур      | Limit    | Units       |

|-----------------------------------|------------------------------------------------------------------------|-------------------------------------|----------|----------|-------------|

|                                   |                                                                        |                                     | (Note 7) | (Note 8) | (Limits)    |

| +                                 | Access Time                                                            | C <sub>L</sub> = 100 pF             | 10       | 20       | ns (max)    |

| t <sub>ACC</sub>                  | (RD Low or OE High to Data Valid)                                      |                                     |          |          | ns (max)    |

| + +                               | TRI-STATE Control                                                      | $R_{L} = 1k, C_{L} = 10 \text{ pF}$ | 25       | 40       | ns (max)    |

| t <sub>1H</sub> , t <sub>oH</sub> | (RD High or OE Low to Databus TRI-STATE)                               |                                     | 2.5      | 40       | IIS (IIIdX) |

| t <sub>INTH</sub>                 | Delay from RD Low to INT High                                          | C <sub>L</sub> = 100 pF             | 35       | 60       | ns (max)    |

|                                   | Delay from EOC High to INT Low                                         | $C_1 = 100  pF$                     | -25      | -35      | ns (min)    |

|                                   | Delay non LOC high to intr Low                                         |                                     |          | -5       | ns (max)    |

| t <sub>UPDATE</sub>               | EOC High to New Data Valid                                             |                                     | 5        | 15       | ns (max)    |

| +                                 | Multiplexer Address Setup Time                                         |                                     |          | 50       | ns (min)    |

| t <sub>MS</sub>                   | (MUX Address Valid to EOC Low)                                         |                                     |          | 50       |             |

| +                                 | Multiplexer Address Hold Time                                          |                                     |          | 50       | ns (min)    |

| t <sub>MH</sub>                   | (EOC Low to MUX Address Invalid)                                       |                                     |          | 50       | 113 (11111) |

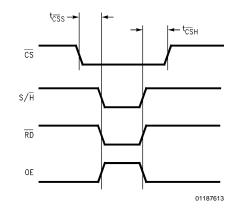

| tcss                              | CS Setup Time                                                          |                                     |          | 20       | ns (min)    |

| CSS                               | (CS Low to RD Low, S/H Low, or OE High)                                |                                     |          | 20       | 115 (11111) |

| +                                 | CS Hold Time                                                           |                                     |          | 20       | ns (min)    |

| t <sub>CSH</sub>                  | $(\overline{CS}$ High after $\overline{RD}$ High, S/H High, or OE Low) |                                     |          | 20       | ns (min)    |

| +                                 | Wake-Up Time                                                           |                                     | 1        |          | 115         |

| t <sub>WU</sub>                   | (PD High to First S/H Low)                                             |                                     | '        |          | μs          |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional. These ratings do not guarantee specific performance limits, however. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND (GND = AGND = DGND), unless otherwise specified.

**Note 3:** When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} < \text{GND or } V_{IN} > V_{CC})$  the absolute value of current at that pin should be limited to 25 mA or less. The 50 mA package input current limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two.

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$  and the ambient temperature  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.  $\theta_{JA}$  for the V (PLCC) package is 55°C/W.  $\theta_{JA}$  for the VF (PQFP) package is 62°C/W. In most cases the maximum derated power dissipation will be reached only during fault conditions.

Note 5: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor. Machine model ESD rating is 200V.

Note 6: See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in a current National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

Note 7: Typicals are at +25  $^\circ\text{C}$  and represent most likely parametric norm.

Note 8: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 9: Integral Linearity Error is the maximum deviation from a straight line between the measured offset and full scale endpoints.

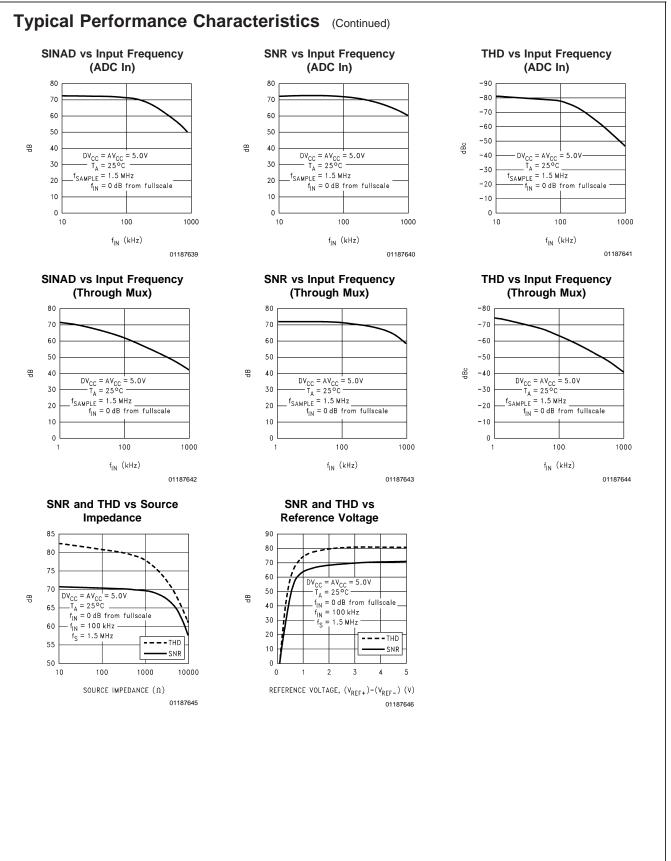

Note 10: Dynamic testing of the ADC12662 is done using the ADC IN input. The input multiplexer adds harmonic distortion at high frequencies. See the graph in the Typical Performance Characteristics section for a typical graph of THD performance vs input frequency with and without the input multiplexer.

Note 11: The signal-to-noise ratio is the ratio of the signal amplitude to the background noise level. Harmonics of the input signal are not included in its calculation. Note 12: The contributions from the first nine harmonics are used in the calculation of the THD.

Note 13: Effective Number of Bits (ENOB) is calculated from the measured signal-to-noise plus distortion ratio (SINAD) using the equation ENOB = (SINAD – 1.76)/6.02.

Note 14: The digital power supply current takes up to 10 seconds to decay to its final value after PD is pulled low. This prohibits production testing of the standby current. Some parts may exhibit significantly higher standby currents than the 50 µA typical.

Note 15: Power Supply Sensitivity is defined as the change in the Offset Error or the Full Scale Error due to a change in the supply voltage.

#### **Typical Performance Characteristics Offset and Fullscale** Error Change vs Linearity Error Change Mux ON Resistance **Reference Voltage** vs Reference Voltage vs Input Voltage ±0.6 380 $-DV_{CC} = AV_{CC} = 5.0V_{-}$ $-T_A = 25°C$ OFFSET AND FULLSCALE ERROR CHANGE (LSB) = 25°C ±1.50 340 LINEARITY ERROR CHANGE (LSB) $DV_{CC} = AV_{CC} = 5.0V$ $T_A = 25°C$ ±0.5 f<sub>SAMPLE</sub> = 1.5 MHz ON RESISTANCE (D) 300 ±1.25 f<sub>SAMPLE</sub> = 1.5 MHz ±0.4 260 ±1.00 AV<sub>CC</sub> = 4.5 ±0.3 220 = 5.0AV<sub>CC</sub> ±0.75 = 5.5V 180 ±0.2 MUX ±0.50 140 ±0.1 FULLSCALE 100 ±0.25 60 0.0 2 3 4 5 0.0 1.0 2.0 3.0 4.0 5.0 0.00 2 3 4 5 Reference voltage, $(\mathrm{v}_{\mathrm{REF}^{+}})\text{-}(\mathrm{v}_{\mathrm{REF}^{-}})$ (V) ANALOG INPUT VOLTAGE (V) REFERENCE VOLTAGE, $(V_{REF+})-(V_{REF-})$ (V) 01187631 01187632 01187630 **Current Consumption in Digital Supply Current Analog Supply Current** Standby Mode vs Voltage vs Temperature vs Temperature on Digital Input Pins 2.3 34 260 $DV_{CC} = AV_{CC} = 5.0V$ $T_A = 25°C$ 240 DIGITAL SUPPLY CURRENT (mA) ANALOG SUPPLY CURRENT (mA) CURRENT (µA) 220 33 5.250 200 2.2 180 5.0V 32 160 75) 140 2.1 31 DIGITAL SUPPLY 120 100 30 80 2.0 60 29 40 20 1.9 28 0 -55-35-15 5 25 45 65 85 105 125 --55 -35 -15 5 25 45 65 85 105 125 0 1 2 3 4 5 AMBIENT TEMPERATURE (°C) AMBIENT TEMPERATURE (°C) INPUT VOLTAGE (V) 01187633 01187634 01187635 Conversion Time (t<sub>CONV</sub>) EOC Delay Time (t<sub>EOC</sub>) vs Temperature vs Temperature **Spectral Response** 630 110 f<sub>S</sub> = 1.6 MSPS 0 dB f<sub>S</sub> = 1.5 MHz f<sub>S</sub> = 1.5 MHz $f_{IN} = 94 \text{ kHz}, 0 \text{ dB} \text{ from}$ CONVERSION TIME (t<sub>CONV</sub>) (ns) 620 EOC DELAY TIME (t<sub>EOC</sub>) (ns) \_ fullscale \_ 105 -20 dB SNR: 71.3 dB 610 . THD: -78.1 dBc 100 -40 dB 1 75V SINAD: -70.6 dB $DV_{CC} = AV_{CC} = 5.0V$ $T_A = 25°C$ 600 5.0V -60 dB 5.25V 95 590 -80 dB 90 580 -100 dB 4 75 570 85 80 160 320 480 640 800 80 240 400 560 720 -55-35-15 5 25 45 65 85 105 125 -55-35-15 5 25 45 65 85 105 125 FREQUENCY (kHz) AMBIENT TEMPERATURE (°C) AMBIENT TEMPERATURE (°C) 01187638 01187636 01187637

#### **Timing Diagrams** → <sup>t</sup>AD n + 1 n + 2 n V<sub>IN</sub> CS <sup>t</sup>тнкоиднрит • t<sub>CONV</sub> I t<sub>S/H</sub> $\rm S/\bar{H}$ $t_{\rm EOC}$ EOC ™s t<sub>мн</sub> S0 n + 1 n + 2 t<sub>INTL</sub> → INT <sup>t</sup>INTΗ $\overline{\mathsf{RD}}$ 🗲 t<sub>1 Н, ОН</sub> t<sub>ACC</sub>-DATA (n) DATA (n - 1) DBO-DB11 • 01187609

## Timing Diagrams (Continued)

### **Functional Description**

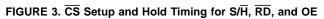

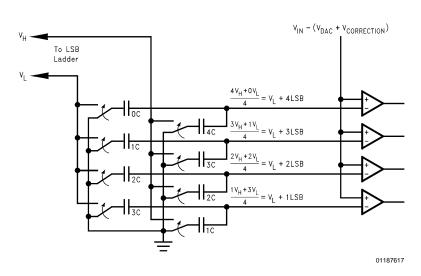

The ADC12662 performs a 12-bit analog-to-digital conversion using a 3 step flash technique. The first flash determines the six most significant bits, the second flash generates four more bits, and the final flash resolves the two least significant bits. *Figure 4* shows the major functional blocks of the converter. It consists of a 2½-bit Voltage Estimator, a resistor ladder with two different resolution voltage spans, a sample/hold capacitor, a 4-bit flash converter with front end multiplexer, a digitally corrected DAC, and a capacitive voltage divider. To pipeline the converter, there are two sample/hold capacitors and 4-bit flash sections, which allows the converter to acquire the next input sample while converting the previous one. Only one of the flash converter pairs is shown in *Figure 4* to reduce complexity.

#### **FIGURE 4. Functional Block Diagram**

The resistor string near the center of the block diagram in Figure 4 generates the 6-bit and 10-bit reference voltages for the first two conversions. Each of the 16 resistors at the bottom of the string is equal to 1/1024 of the total string resistance. These resistors form the LSB Ladder (The weight of each resistor on the LSB ladder is actually equivalent to four 12-bit LSBs. It is called the LSB ladder because it has the highest resolution of all the ladders in the converter) and have a voltage drop of 1/1024 of the total reference voltage (V<sub>REF+</sub> – V<sub>REF-</sub>) across each of them. The remaining resistors form the **MSB Ladder**. It is comprised of eight groups of eight resistors each connected in series (the lowest MSB ladder resistor is actually the entire LSB ladder). Each MSB Ladder section has 1/8 of the total reference voltage across it. Within a given MSB ladder section, each of the eight MSB resistors has 1/64 of the total reference voltage across it. Tap points are found between all of the resistors in both the MSB and LSB ladders. The Comparator Multiplexer can connect any of these tap points, in two adjacent groups of eight, to the sixteen comparators shown at the right of *Figure 4*. This function provides the necessary reference voltages to the comparators during the first two flash conversions.

The six comparators, seven-resistor string (Estimator DAC ladder), and Estimator Decoder at the left of *Figure 4* form the Voltage Estimator. The Estimator DAC, connected between  $V_{REF+}$  and  $V_{REF-}$ , generates the reference voltages for the six Voltage Estimator comparators. The comparators perform a very low resolution A/D conversion to obtain an "estimate" of the input voltage. This estimate is used to control the placement of the Comparator Multiplexer, connecting the appropriate MSB ladder section to the sixteen flash comparators. A total of only 22 comparators (6 in the

## Functional Description (Continued)

Voltage Estimator and 16 in the flash converter) is required to quantize the input to 6 bits, instead of the 64 that would be required using a traditional 6-bit flash.

Prior to a conversion, the Sample/Hold switch is closed, allowing the voltage on the S/H capacitor to track the input voltage. Switch 1 is in position 1. A conversion begins by opening the Sample/Hold switch and latching the output of the Voltage Estimator. The estimator decoder then selects two adjacent banks of tap points along the MSB ladder. These sixteen tap points are then connected to the sixteen flash converters. For example, if the input voltage is between 5/16 and 7/16 of V<sub>REF</sub> (V<sub>REF</sub> = V<sub>REF+</sub> – V<sub>REF-</sub>), the estimator decoder instructs the comparator multiplexer to select the sixteen tap points between 2/8 and 4/8 (4/16 and 8/16) of V<sub>REF</sub> and connects them to the sixteen flash converters. The first flash conversion is now performed, producing the first 6 MSBs of data.

At this point, Voltage Estimator errors as large as 1/16 of V<sub>REF</sub> will be corrected since the flash converters are connected to ladder voltages that extend beyond the range specified by the Voltage Estimator. For example, if  $(7/16)V_{REF}$  <  $V_{IN}$  <  $(9/16)V_{REF}$ , the Voltage Estimator's comparators tied to the tap points below (9/16)V<sub>REE</sub> will output "1"s (000111). This is decoded by the estimator decoder to "10". The 16 comparators will be placed on the MSB ladder tap points between (3%)  $V_{\text{REF}}$  and (5%)  $V_{\text{REF}}.$  This overlap of (1/16)V<sub>REF</sub> will automatically cancel a Voltage Estimator error of up to 256 LSBs. If the first flash conversion determines that the input voltage is between  $(3/8)V_{REF}$  and ((4/8)V<sub>REE</sub> – LSB/2), the Voltage Estimator's output code will be corrected by subtracting "1", resulting in a corrected value of "01" for the first two MSBs. If the first flash conversion determines that the input voltage is between  $(4/8)V_{REF}$  -LSB/2) and  $(5\%)V_{REF}$ , the voltage estimator's output code is unchanged.

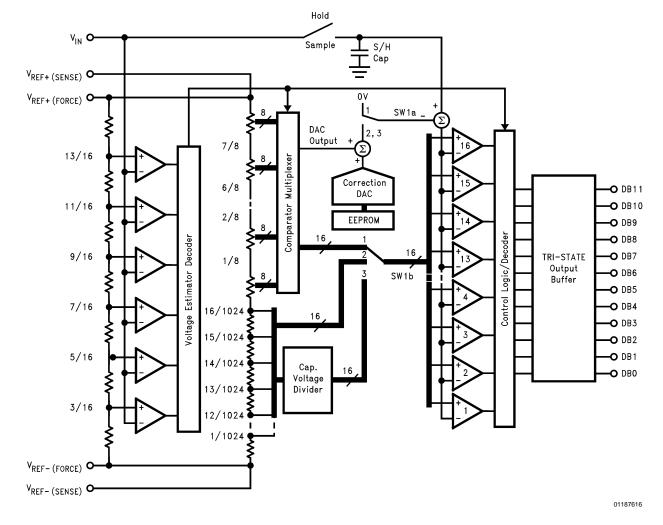

The results of the first flash and the Voltage Estimator's output are given to the factory-programmed on-chip EE-PROM which returns a correction code corresponding to the error of the MSB ladder at that tap. This code is converted to a voltage by the Correction DAC. To generate the next four bits, SW1 is moved to position 2, so the ladder voltage and the correction voltage are subtracted from the input voltage. The remainder is applied to the sixteen flash converters and compared with the 16 tap points from the LSB ladder. The result of this second conversion is accurate to 10 bits and describes the input remainder as a voltage between two tap points ( $V_H$  and  $V_L$ ) on the LSB ladder. To resolve the last two bits, the voltage across the ladder resistor (between  $V_H$ and  $V_L$ ) is divided up into 4 equal parts by the capacitive voltage divider, shown in *Figure 5*. The divider also creates 6 LSBs below  $V_L$  and 6 LSBs above  $V_H$  to provide overlap used by the digital error correction. SW1 is moved to position 3, and the remainder is compared with these 16 new voltages. The output is combined with the results of the Voltage Estimator, first flash, and second flash to yield the final 12-bit result.

By using the same sixteen comparators for all three flash conversions, the number of comparators needed by the multi-step converter is significantly reduced when compared to standard multi-step techniques.

## **Applications Information**

### **1.0 MODES OF OPERATION**

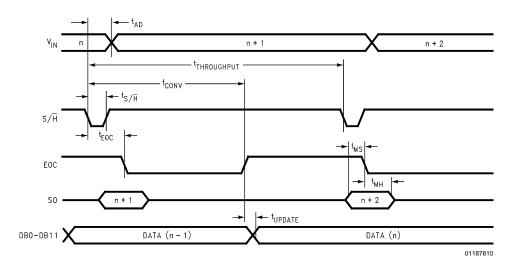

The ADC12662 has two interface modes: An interrupt/read mode and a high speed mode. *Figure 1* and *2* show the timing diagrams for these interfaces.

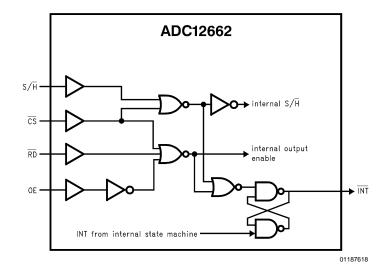

In order to clearly show the relationship between  $S/\overline{H}$ ,  $\overline{CS}$ ,  $\overline{RD}$ , and OE, the control logic decoding section of the ADC12662 is shown in *Figure 6*.

#### Interrupt Interface

As shown in *Figure 1*, the falling edge of  $S/\overline{H}$  holds the input voltage and initiates a conversion. At the end of the conversion, the EOC output goes high and the  $\overline{INT}$  output goes low, indicating that the conversion results are latched and may be read by pulling  $\overline{RD}$  low. The falling edge of  $\overline{RD}$  resets the  $\overline{INT}$  line. Note that  $\overline{CS}$  must be low to enable  $S/\overline{H}$  or  $\overline{RD}$ .

#### **High Speed Interface**

The Interrupt interface works well at lower speeds, but few microprocessors could keep up with the 1  $\mu$ s interrupts that would be generated if the ADC12662 was running at full speed. The most efficient interface is shown in *Figure 2*. Here the output data is always present on the databus, and the  $\overline{\text{INT}}$  to  $\overline{\text{RD}}$  delay is eliminated.

## Applications Information (Continued)

FIGURE 5. The Capacitive Voltage Divider

#### 2.0 THE ANALOG INPUT

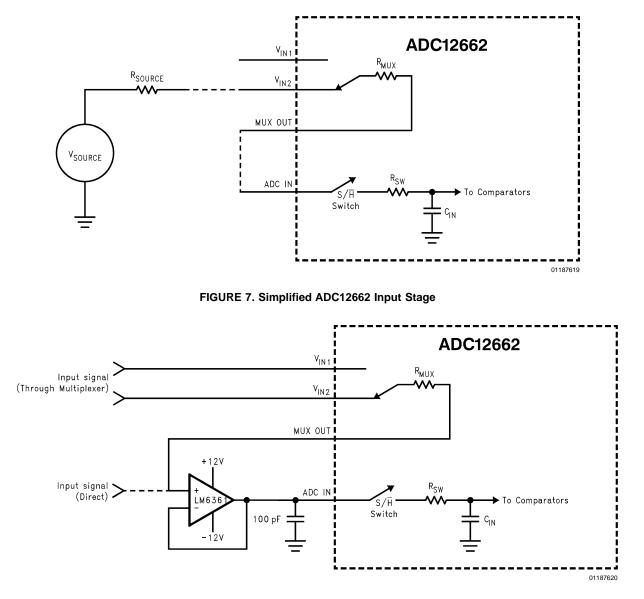

The analog input of the ADC12662 can be modeled as two small resistances in series with the capacitance of the input hold capacitor (C<sub>IN</sub>), as shown in *Figure 7*. The S/H switch is closed during the Sample period, and open during Hold. The source has to charge C<sub>IN</sub> to the input voltage within the sample period. Note that the source impedance of the input voltage (R<sub>SOURCE</sub>) has a direct effect on the time it takes to charge C<sub>IN</sub>. If R<sub>SOURCE</sub> is too large, the voltage across C<sub>IN</sub> will not settle to within 0.5 LSBs of V<sub>SOURCE</sub> before the conversion begins, and the conversion results will be incorrect. From a dynamic performance viewpoint, the combination of R<sub>SOURCE</sub>, R<sub>MUX</sub>, R<sub>SW</sub>, and C<sub>IN</sub> form a low pass filter. Minimizing R<sub>SOURCE</sub> will increase the frequency response of the input stage of the converter.

Typical values for the components shown in Figure 7 are:  $R_{MUX}$  = 100Ω,  $R_{SW}$  = 100Ω, and  $C_{IN}$  = 25 pF. The settling time to n bits is:

$t_{\text{SETTLE}} = (R_{\text{SOURCE}} + R_{\text{MUX}} + R_{\text{SW}}) * C_{\text{IN}} * n * \text{In (2)}.$ The bandwidth of the input circuit is:  $f_{-3dB}$  = 1/(2 \* 3.14 \* ( $R_{SOURCE}$  +  $R_{MUX}$  +  $R_{SW}$ ) \*  $C_{IN}$ ) The ADC12662 is operated in a pipelined sequence, with one hold capacitor acquiring the next sample while a conversion is being performed on the voltage stored on the other hold capacitor. This gives the source over  $t_{CONV}$  seconds to charge the hold capacitor to its final value. At 1.5 MHz, the settling time must be less than 667 ns. Using the settling time equation and component values given, the maximum source impedance that will allow the input to settle to 1/2 LSB (n = 13) at full speed is ~2.8 k $\Omega$ . To ensure 1/2 LSB settling over temperature and device-to-device variation,  $R_{SOURCE}$  should be a maximum of 500 $\Omega$  when the converter is operated at full speed.

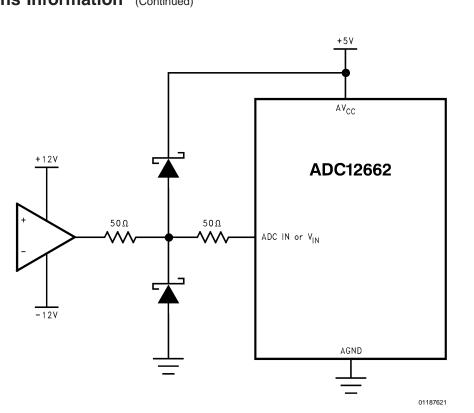

If the signal source has a high output impedance, its output should be buffered with an operational amplifier capable of driving a switched 25 pF/100 $\Omega$  load. Any ringing or instabilities at the op amp's output during the sampling period can result in conversion errors. The LM6361 high speed op amp is a good choice for this application due to its speed and its ability to drive large capacitive loads. *Figure 8* shows the

## Applications Information (Continued)

LM6361 driving the ADC IN input of an ADC12662. The 100 pF capacitor at the input of the converter absorbs some of the high frequency transients generated by the  $S/\overline{H}$  switching, reducing the op amp transient response requirements. The 100 pF capacitor should only be used with high speed op amps that are unconditionally stable driving capacitive loads.

Another benefit of using a high speed buffer is improved THD performance when using the multiplexer of the ADC12662. The MUX on-resistance is somewhat non-linear over input voltage, causing the RC time constant formed by  $C_{IN}$ ,  $R_{MUX}$ , and  $R_{SW}$  to vary depending on the input voltage. This results in increasing THD with increasing frequency. Inserting the buffer between the MUX OUT and the ADC IN terminals as shown in *Figure 8* will eliminate the loading on  $R_{MUX}$ , significantly reducing the THD of the multiplexed system.

#### FIGURE 8. Buffering the Input with an LM6361 High Speed Op Amp

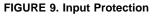

Correct converter operation will be obtained for input voltages greater than AGND – 50 mV and less than AV<sub>CC</sub> + 50 mV. Avoid driving the signal source more than 300 mV higher than AV<sub>CC</sub>, or more than 300 mV below AGND. If an analog input pin is forced beyond these voltages, the current flowing through that pin should be limited to 25 mA or less to avoid permanent damage to the IC. The sum of all the

overdrive currents into all pins must be less than 50 mA. When the input signal is expected to extend more than 300 mV beyond the power supply limits for any reason (unknown/uncontrollable input voltage range, power-on transients, fault conditions, etc.) some form of input protection, such as that shown in *Figure 9*, should be used.

### Applications Information (Continued)

#### **3.0 ANALOG MULTIPLEXER**

The ADC12662 has an input multiplexer that is controlled by the logic level on pin S0 when EOC goes low, as shown in *Figure 1* and *2*. Multiplexer setup and hold times with respect to the S/ $\overline{H}$  input can be determined by these two equations:

$t_{MS (wrt S/H)} = t_{MS} - t_{EOC (min)} = 50 - 60 = -10 \text{ ns}$

$t_{MH (wrt S/H)} = t_{MH} + t_{EOC (max)} = 50 + 125 = 175 \text{ ns}$

Note that  $t_{MS \text{ (wrt S/H)}}$  is a negative number; this indicates that the data on S0 must become valid within 10 ns after  $S/\overline{H}$  goes low in order to meet the setup time requirements. S0 must be valid for a length of

$(t_{MH} + t_{EOC (max)}) - (t_{MS} - t_{EOC (min)}) = 185 \text{ ns.}$ Table 1 shows how the input channels are assigned:

## TABLE 1. ADC12662 InputMultiplexer Programming

| S0 | Channel          |

|----|------------------|

| 0  | V <sub>IN1</sub> |

| 1  | V <sub>IN2</sub> |

The output of the multiplexer is available to the user via the MUX OUT pin. This output allows the user to perform additional signal processing, such as filtering or gain, before the

signal is returned to the ADC IN input and digitized. If no additional signal processing is required, the MUX OUT pin should be tied directly to the ADC IN pin.

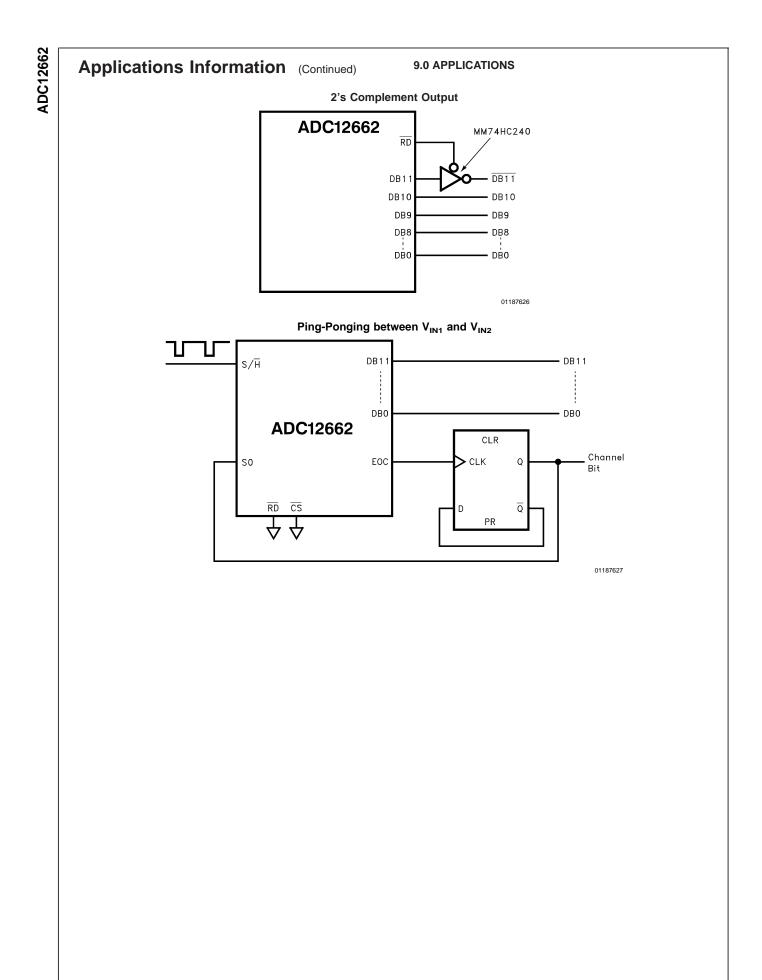

See Section 9.0 (APPLICATIONS) for a simple circuit that will alternate between the two inputs while converting at full speed.

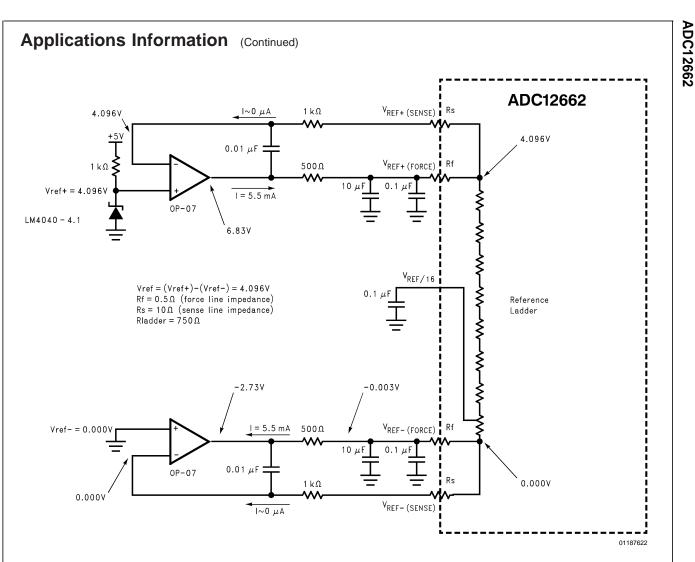

#### **4.0 REFERENCE INPUTS**

In addition to the fully differential V<sub>REF+</sub> and V<sub>REF-</sub> reference inputs used on most National Semiconductor ADCs, the ADC12662 has two sense outputs for precision control of the ladder voltage. These sense inputs compensate for errors due to IR drops between the reference source and the ladder itself. The resistance of the reference ladder is typically 750 $\Omega$ . The parasitic resistance (R<sub>P</sub>) of the package leads, bond wires, PCB traces, etc. can easily be 0.5 $\Omega$  to 1.0 $\Omega$  or more. This may not be significant at 8-bit or 10-bit resolutions, but at 12 bits it can introduce voltage drops causing offset and gain errors as large as 6 LSBs.

The ADC12662 provides a means to eliminate this error by bringing out two additional pins that sense the exact voltage at the top and bottom of the ladder. With the addition of two op amps, the voltages on these internal nodes can be forced to the exact value desired, as shown in *Figure 10*.

Since the current flowing through the SENSE lines is essentially zero, there is negligible voltage drop across  ${\rm R}_{\rm S}$  and the 1 k $\Omega$  resistor, so the voltage at the inverting input of the op amp accurately represents the voltage at the top (or bottom) of the ladder. The op amp drives the FORCE input and forces the voltage at the ends of the ladder to equal the voltage at the op amps's non-inverting input, plus or minus its input offset voltage. For this reason op amps with low  $V_{\rm OS}$ , such as the LM627 or LM607, should be used for this application. When used in this configuration, the ADC12662 has less than 2 LSBs of offset and 1.5 LSB of gain error without any user adjustments.

The 0.1  $\mu F$  and 10  $\mu F$  capacitors on the force inputs provide high frequency decoupling of the reference ladder. The 500 $\Omega$  force resistors isolate the op amps from this large capacitive load. The 0.01  $\mu F/1~k\Omega$  network provides zero phase shift at high frequencies to ensure stability. Note that the op amp supplies in this example must be ±10V to ±15V to meet the input/output voltage range requirements of the LM627 and supply the sub-zero voltage to the  $V_{REF-}$  (FORCE) pin. The  $V_{REF/16}$  output should be bypassed to analog ground with a 0.1  $\mu F$  ceramic capacitor.

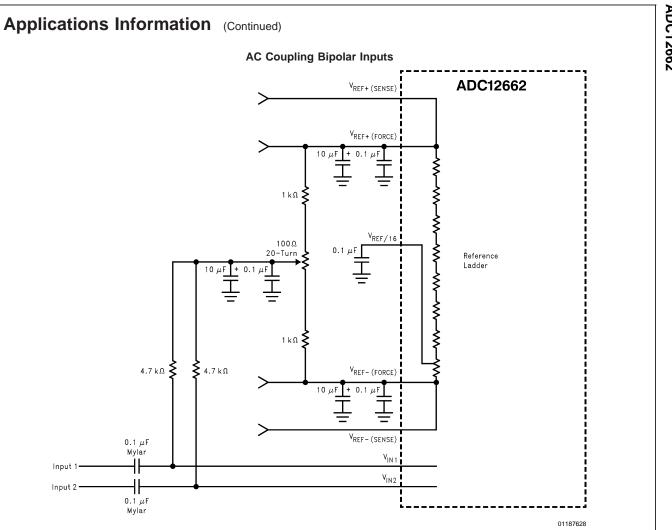

The reference inputs are fully differential and define the zero to full-scale range of the input signal. They can be configured

to span up to 5V ( $V_{REF-} = 0V$ ,  $V_{REF+} = 5V$ ), or they can be connected to different voltages (within the 0V to 5V limits) when other input spans are required. The ADC12662 is tested at  $V_{REF-}$  (SENSE) = 0V,  $V_{REF+}$  (SENSE) = 4.096V. Reducing the reference voltage span to less than 4V increases the sensitivity (reduces the LSB size) of the converter; however noise performance degrades when lower reference voltages are used. A plot of dynamic performance vs reference voltage is given in the Typical Performance Characteristics section.

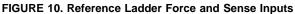

If the converter will be used in an application where DC accuracy is secondary to dynamic performance, then a simpler reference circuit may suffice. The circuit shown in *Figure 11* will introduce several LSBs of offset and gain error, but INL, DNL, and all dynamic specifications will be unaffected. All bypass capacitors should be located as close to the ADC12662 as possible to minimize noise on the reference ladder. The  $V_{\rm REF/16}$  output should be bypassed to analog ground with a 0.1 µF ceramic capacitor.

The LM4040 shunt voltage reference is available with a 4.096V output voltage. With initial accuracies as low as  $\pm$  0.1%, it makes an excellent reference for the ADC12662.

## Applications Information (Continued) ADC12662 V<sub>REF</sub>+ (SENSE) NC 4.093V 4.096V V<sub>REF+</sub> (FORCE) LM4040-4.1 REF/16 Reference Ladder V<sub>REF</sub>-(FORCE) V<sub>REF</sub>-(SENSE) 0.003V NC 01187623

#### 5.0 POWER SUPPLY CONSIDERATIONS

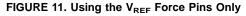

The ADC12662 is designed to operate from a single +5V power supply. There are two analog supply pins (AV<sub>CC</sub>) and one digital supply pin (DV<sub>CC</sub>). These pins allow separate external bypass capacitors for the analog and digital portions of the circuit. To guarantee proper operation of the converter, all three supply pins should be connected to the same voltage source. In systems with separate analog and digital supplies, the converter should be powered from the analog supply.

The ground pins are AGND (analog ground), DGND1 (digital input ground), and DGND2 (digital output ground). These pins allow for three separate ground planes for these sections of the chip. Isolating the analog section from the two digital sections reduces digital interference in the analog circuitry, improving the dynamic performance of the converter. Separating the digital outputs from the digital inputs (particularly the S/H input) reduces the possibility of ground bounce from the 12 data lines causing jitter on the S/H input. The analog ground plane should be connected to the Digital2 ground plane at the ground return for the power supply. The Digital1 ground plane should be tied to the Digital2 ground plane at the DGND1 and DGND2 pins.

Both AV<sub>CC</sub> pins should be bypassed to the AGND ground plane with 0.1  $\mu$ F ceramic capacitors. One of the two AV<sub>CC</sub> pins should also be bypassed with a 10  $\mu$ F tantalum capacitor. DV<sub>CC</sub> should be bypassed to the DGND2 ground plane with a 0.1  $\mu$ F capacitor in parallel with a 10  $\mu$ F tantalum capacitor.

### 6.0 LAYOUT AND GROUNDING

In order to ensure fast, accurate conversions from the ADC12662, it is necessary to use appropriate circuit board layout techniques. Separate analog and digital ground planes are required to meet datasheet AC and DC limits. The analog ground plane should be low-impedance and free of noise from other parts of the system.

All bypass capacitors should be located as close to the converter as possible and should connect to the converter and to ground with short traces. The analog input should be isolated from noisy signal traces to avoid having spurious signals couple to the input. Any external component (e.g., a filter capacitor) connected across the converter's input should be connected to a very clean analog ground return point. Grounding the component at the wrong point will result in increased noise and reduced conversion accuracy.

## Applications Information (Continued)

*Figure 12* gives an example of a suitable layout, including power supply routing, ground plane separation, and bypass capacitor placement. All analog circuitry (input amplifiers, filters, reference components, etc.) should be placed on the analog ground plane. All digital circuitry and I/O lines (excluding the S/H input) should use the digital2 ground plane as ground. The digital1 ground plane should only be used for the S/H signal generation.

FIGURE 12. PC Board Layout

#### 7.0 DYNAMIC PERFORMANCE

The ADC12662 is AC tested and its dynamic performance is guaranteed. In order to meet these specifications, the clock source driving the S/ $\overline{H}$  input must be free of jitter. For the best AC performance, a crystal oscillator is recommended. For operation at or near the ADC12662's 1.5 MHz maximum sampling rate, a 1.5 MHz squarewave will provide a good signal for the S/ $\overline{H}$  input. As long as the duty cycle is near 50%, the waveform will be low for about 333 ns, which is within the 400 ns limit. When operating the ADC12662 at a sample rate of 1.25 MHz or below, the pulse width of the S/ $\overline{H}$  signal must be smaller than half the sample period.

ADC12662

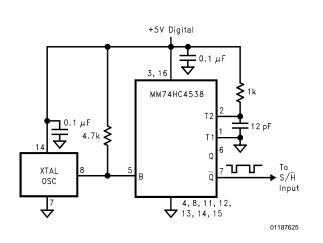

FIGURE 13. Crystal Clock Source

Figure 13 is an example of a low jitter  $S/\overline{H}$  pulse generator that can be used with the ADC12662 and allow operation at sampling rates from DC to 1.5 MHz. A standard 4-pin DIP crystal oscillator provides a stable 1.5 MHz squarewave. Since most DIP oscillators have TTL outputs, a 4.7k pullup resistor is used to raise the output high voltage to CMOS input levels. The output is fed to the trigger input (falling edge) of an MM74HC4538 one-shot. The 1k resistor and 12 pF capacitor set the pulse length to approximately 100 ns. The S/H pulse stream for the converter appears on the Q output of the HC4538. This is the S/H clock generator used on the ADC12062EVAL evaluation board. For lower power, a CMOS inverter-based crystal oscillator can be used in place of the DIP crystal oscillator. See Application Note AN-340 in the National Semiconductor CMOS Logic Databook for more information on CMOS crystal oscillators.

#### 8.0 COMMON APPLICATION PITFALLS

**Driving inputs (analog or digital) outside power supply rails.** The Absolute Maximum Ratings state that all inputs must be between GND – 300 mV and  $V_{CC}$  + 300 mV. This rule is most often broken when the power supply to the converter is turned off, but other devices connected to it (op amps, microprocessors) still have power. Note that if there is no power to the converter, DGND = AGND = DV<sub>CC</sub> = AV<sub>CC</sub> = 0V, so all inputs should be within ±300 mV of AGND and DGND.

Driving a high capacitance digital data bus. The more capacitance the data bus has to charge for each conversion, the more instantaneous digital current required from  $DV_{CC}$  and DGND. These large current spikes can couple back to the analog section, decreasing the SNR of the converter. While adequate supply bypassing and separate analog and digital ground planes will reduce this problem, buffering the digital data outputs (with a pair of MM74HC541s, for example) may be necessary if the converter must drive a heavily loaded databus.

www.national.com

**Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Email: support@nsc.com

www.national.com

National Semiconductor

Europe

Fax:

+49 (0) 180-530 85 86

Email:

europe.support@nsc.com

Deutsch

Tel:

+49 (0) 69 9508 6208

English

Tel:

+44 (0) 870 24 0 2171

Français

Tel:

+33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: ap.support@nsc.com

National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.