CMOS 8-Bit Microcontroller

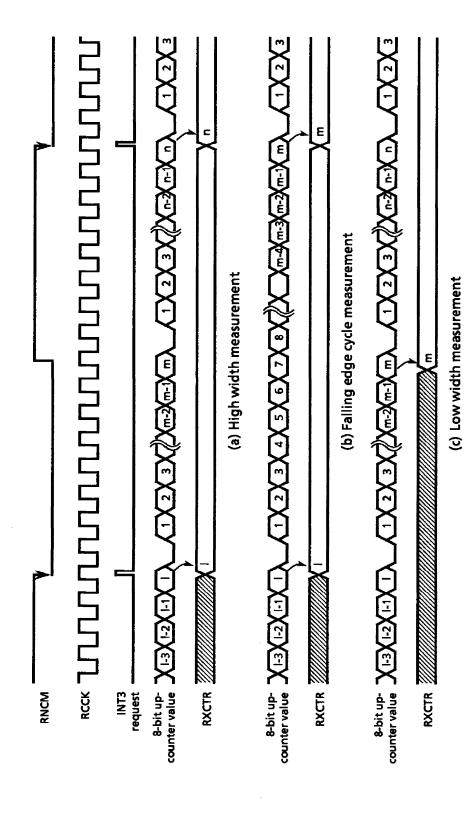

# TMP87CH36N, TMP87CK36N, TMP87CM36N

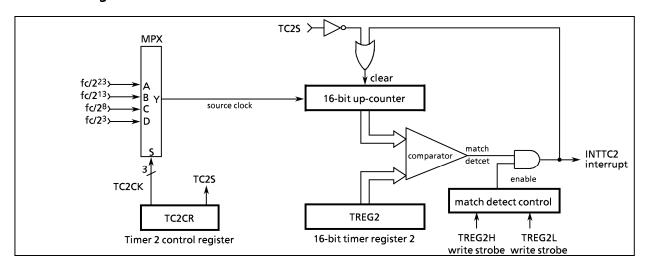

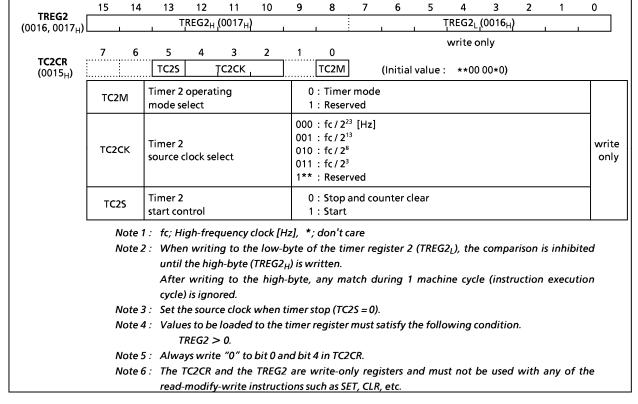

The 87CH36/CK36/CM36 is high speed and high performance 8-bit single chip microcomputer. This MCU contains CPU core, ROM, RAM, input/output ports, six multi-function timer/counter, serial bus interface, onscreen display, PWM, 6-bit A/D conversion inputs and remote control signal preprocessor on a chip.

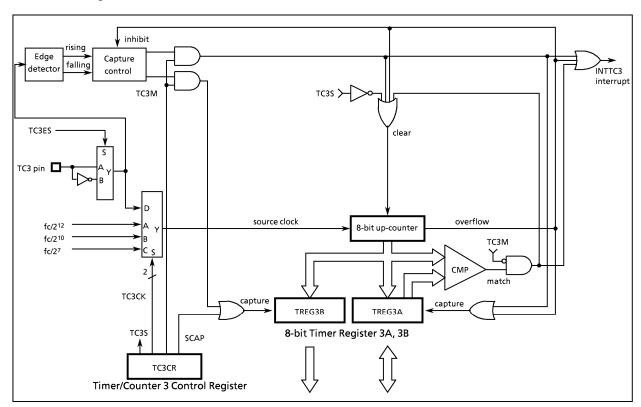

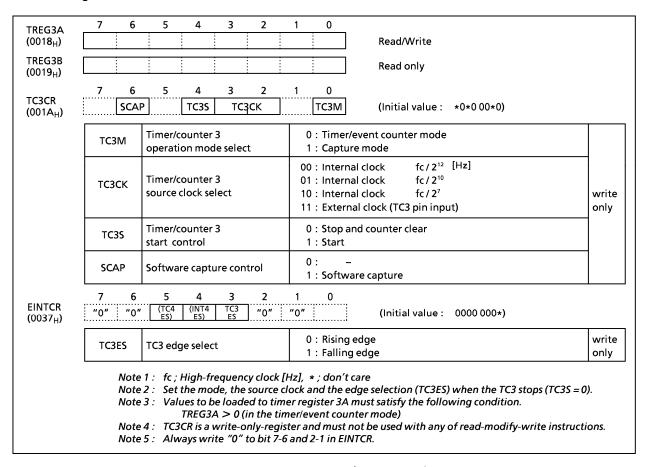

| Part No.   | ROM       | RAM      | Package           | OTP MCU    |  |

|------------|-----------|----------|-------------------|------------|--|

| TMP87CH36N | 16 Kbytes | 0.54     |                   |            |  |

| TMP87CK36N | 24 Kbytes | 1 Kbytes | SDIP42-P-600-1.78 | TMP87PM36N |  |

| TMP87CM36N | 32 Kbytes |          |                   |            |  |

#### **Features**

◆8-bit single chip microcomputer TLCS-870 Series

lacktriangleInstruction execution time: 0.5  $\mu$ s (at 8 MHz)

412 basic instructions

Multiplication and Division (8 bits x 8 bits, 16 bits ÷ 8 bits)

Bit manipulations (Set/Clear/Complement/Move/Test/Exclusive Or)

16-bit data operations

1-byte jump/subroutine-call (Short relative jump / Vector call)

12 interrupt sources (External: 3, Internal: 9)

All sources have independent latches each, and nested interrupt control is available.

Edge-selectable external interrupts with noise reject

High-speed task switching by register bank changeover

◆6 Input/Output ports (34 pins)

High current output: 4 pins (typ. 20 mA)

The information contained herein is subject to change without notice.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, ransportation instruments, traffic signal instruments, combustion control instruments, medical instruments and the customer's own risk.

The pro<mark>ducts described</mark> in this document are subject to the foreign exchange and foreign trade laws.

TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

Purchase of TOSHIBA I<sup>2</sup> C components conveys a license under the Philips I<sup>2</sup> C Patent Rights to use these components in an I<sup>2</sup> C system, provided that the system conforms to the I<sup>2</sup> C Standard Specification as defined by Philips.

> 87CH36-1 2004-10-01

- ◆Two 16-bit Timers

- ◆Two 8-bit Timer/Counters

- Timer, Event counter, Capture (Pulse width/duty measurement) modes

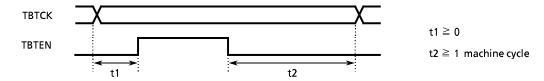

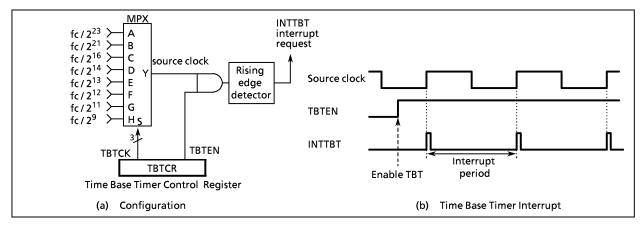

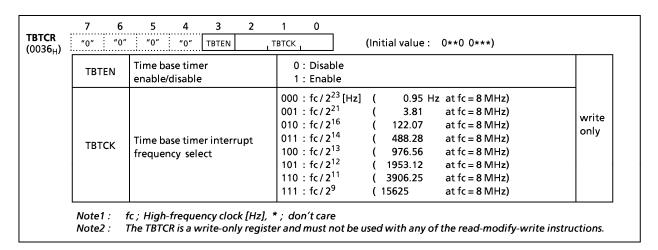

- ◆Time Base Timer (Interrupt frequency: 1 Hz to 16384 Hz)

- ◆Watchdog Timer

- Interrupt source/reset output (programmable)

- ◆ Serial bus Interface

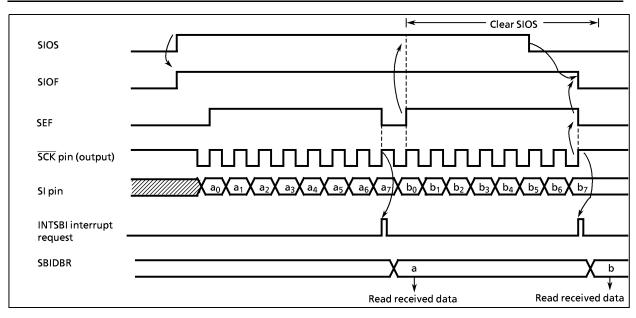

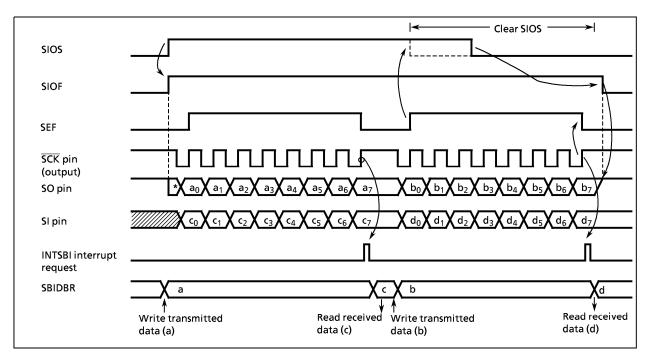

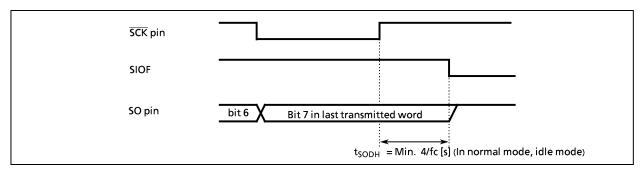

- I<sup>2</sup>C-bus, 8-bit SIO modes

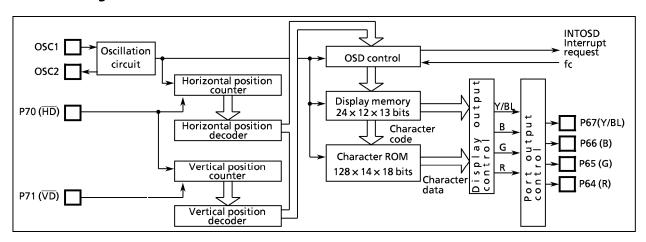

- ◆On-screen display circuit

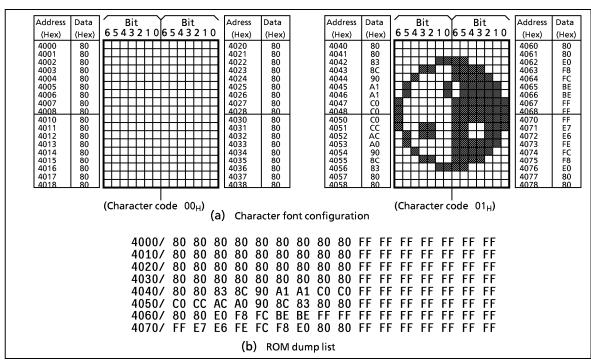

- Character patterns : 128 characters

- Characters displayed : 24 columns x 12 lines

- Composition : 14 × 18 dots

- Size of character : 3 kinds (line by line)

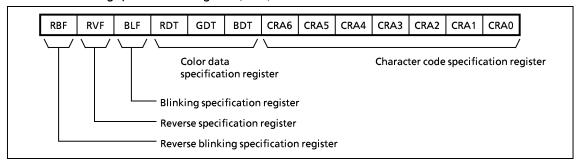

- Color of character : 8 kinds (character by character)

- Variable display position : Horizontal 128 steps, Vertical 256 steps

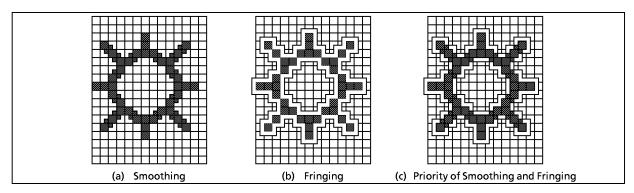

- Fringing, Smoothing function

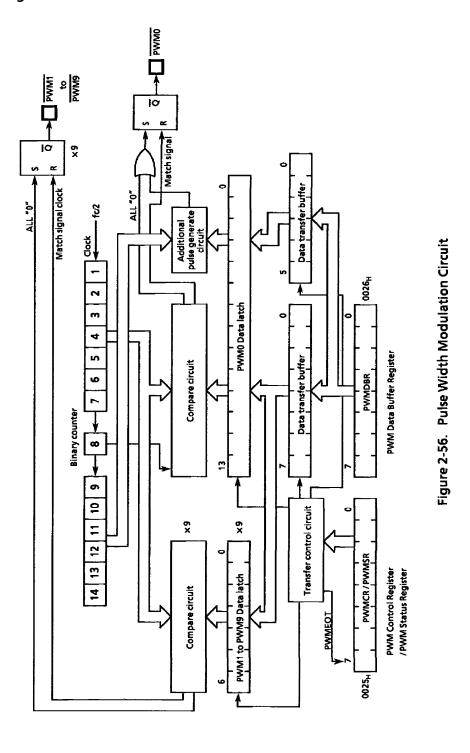

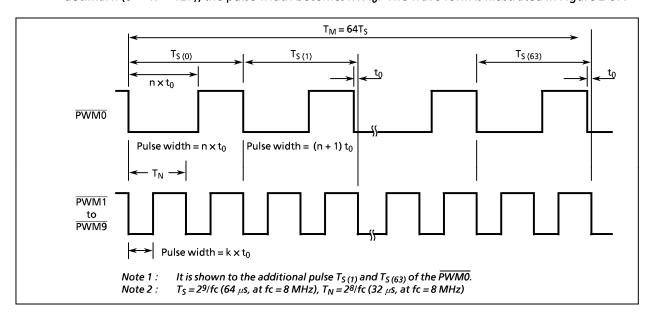

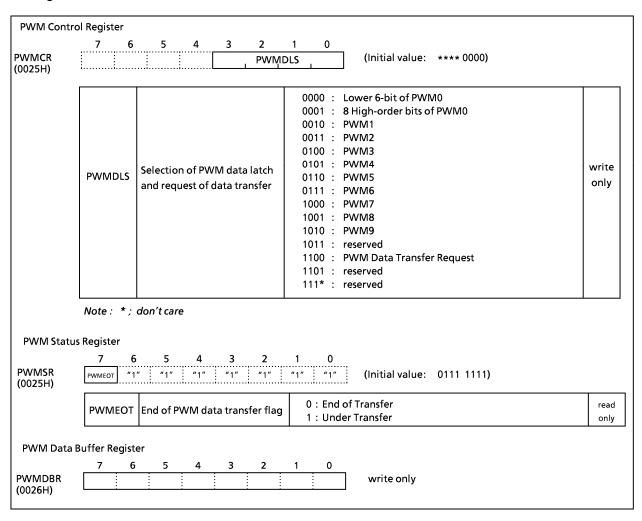

- ◆D/A conversion (Pulse Width Modulation) outputs

- 14-bit resolution (1 channel)

- 7-bit resolution (9 channels)

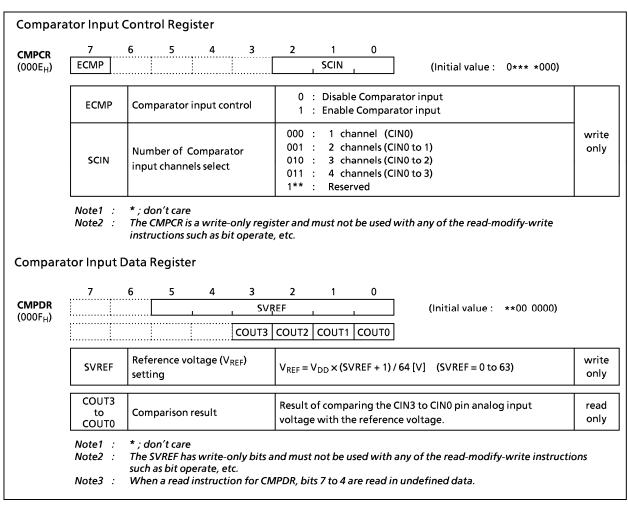

- ◆6-bit A/D conversion input (4 channels)

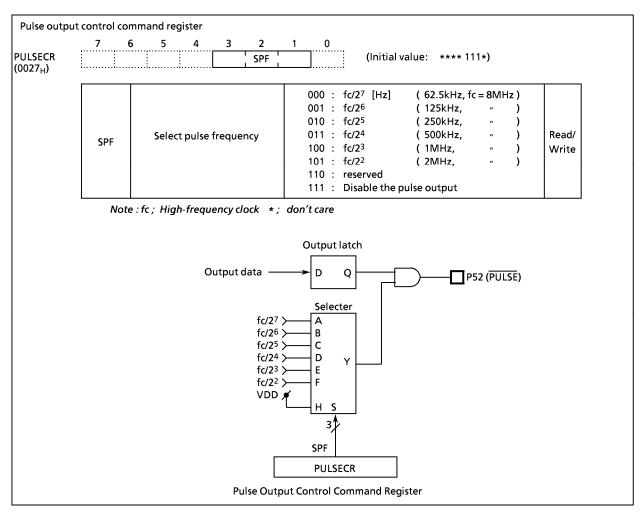

- ◆ Pulse output (Clock for PLL IC)

- ◆Remote control signal preprocessor

- ◆Two Power saving operating modes

- STOP mode: Oscillation stops. Battery/Capacitor back-up. Port output hold/high-impedance.

- IDLE mode : CPU stops, and Peripherals operate. Release by interrupts.

- ◆Operating voltage: 4.5 to 5.5 V at 8 MHz

- ◆Emulation Pod : BM87CM37N0A

#### Pin Assignments (Top View) ]<del><</del>─VDD (PWM0) P40 <del>←</del> 42 SDIP42-P-600-1.78 (PWM1) P41 2 41 ]<del>< →</del>P36 (SCK) 3 (PWM2) P42 40 →P35 (SDA/SO) (PWM3) P43 <del><</del> 4 □<del>< ></del>P34 (SCL / SI) 39 (PWM4) P44 <del>←</del> 5 □<del>< →</del>P33 (TC4) 38 (PWM5) P45 <del>←</del> 6 37 ]<del>< →</del>P32 (INT4) (PWM6) P46 <del>←</del> 7 ]<del>< →</del>P31 (TC3) 36 (<del>PWM7</del>) P47 <del><</del> 8 35 □ ← → P30 (INT3 / RXIN) (PWM8) P50 <del><</del> 9 34 →P20 (INT5 / STOP) (PWM9) P51 <del>←</del> 10 □<del>< →</del>RESET 33 (PULSE) P52 <del>←</del> <del>□ ></del> xouτ 11 32 P53 <del><</del> 12 31 D<del>≺</del>—XIN (CIN0) P54 <del>< →</del> 13 30 ]<del>≺</del>—TEST →OSC2 (CIN1) P55 <del><</del> 14 29 (CIN2) P56 15 28 -OSC1 27 <del>|≺ →</del>P71 (<del>VD</del>) (CIN3) P57 <del><</del> 16 17 26 ]<del>< →</del>P70 (HD) 18 25 ]<del>< →</del>P67 (Y / BL) □<del>< ></del>P66 (B) 19 P62 <del><</del> 24 I/O Ports P63 20 23 ]<del>< →</del>P65 (G) P67 P71 21 22 →P64 (R) to P60 to P70 **Block Diagram** Display Character Y/BL Memory ROM B,G,R VD HD P6 Р7 Osc. connecting pins for OSC1 On-screen display circuit on-screen 1 OSC2 $\Diamond$ display Power VDD-P S w Program Counter Stack Pointer **Data Memory** (RAM) Flags RBS ALU Register Banks Reset I/O RESET System Controller Test Pin TEST Interrupt Controller **Program Memory** (ROM) Standby Controller Time Base 16-bit 8-bit **Timing Generator** Timer Timer Timer/Counter TC1 TC2 TC3 TC4 Resonator ∫ XIN-Connecting \XOUT High Clock Watchdog Inst.Register frequ. Generator Pins Inst. Decoder **1** 1 $\odot$ <u> 1</u> Serial Bus Interface-ver.A (SIO/I<sup>2</sup>C) P4 6-bit A/D Р3 D/A Converter P5 Pulse Remote control P2 Generato signal preprocessor P20 P47 to P40 P57 P36 to P50 to P30 I/O Ports

# **Pin Function**

| Pin Name                               | Input/Output                                                                               | F                                                                                                                                                                                              | unction                                                                |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|

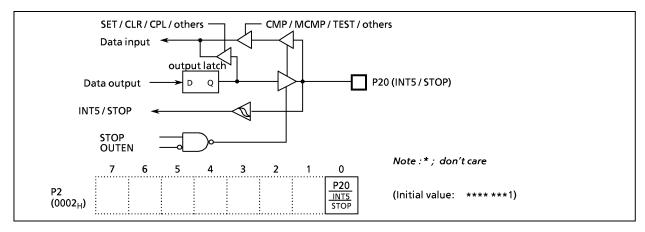

| P20 (INT5/STOP)                        | I/O (Input)                                                                                | 1-bit input / output port with latch.<br>When used as an input port, the latch<br>must be set to "1".                                                                                          | External interrupt input 5 or STOP mode release signal input           |  |  |

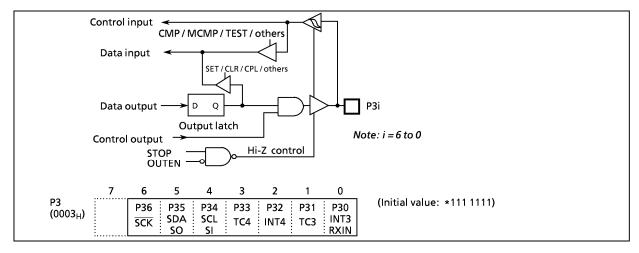

| P36 (SCK)                              | 1/0 (1/0)                                                                                  |                                                                                                                                                                                                | SIO serial clock input/output                                          |  |  |

| P35 (SDA/SO)                           | I/O (I/O/Output)                                                                           | 7-bit input/output port with latch.                                                                                                                                                            | I <sup>2</sup> Cbus serial data input/output or SIO serial data output |  |  |

| P34 (SCL/SI)                           | I/O (I/O/Input)                                                                            | When used as an input port, a serial bus interface input/output, a timer/counter                                                                                                               | I <sup>2</sup> Cbus serial clock input/output or SIO serial data input |  |  |

| P33 (TC4)                              |                                                                                            | input, a remote control signal preprocessor input, or an external                                                                                                                              | Timer/Counter 4 input                                                  |  |  |

| P32 (INT4)                             | I/O (Input)                                                                                | interrupt input, the latch must be set to                                                                                                                                                      | External interrupt input 4                                             |  |  |

| P31 (TC3)                              |                                                                                            | <b>, "1"</b> .                                                                                                                                                                                 | Timer/Counter 3 input                                                  |  |  |

| P30 (INT3/RXIN)                        | I/O (Input/Input)                                                                          |                                                                                                                                                                                                | External interrupt input 3 or remote control signal preprocessor input |  |  |

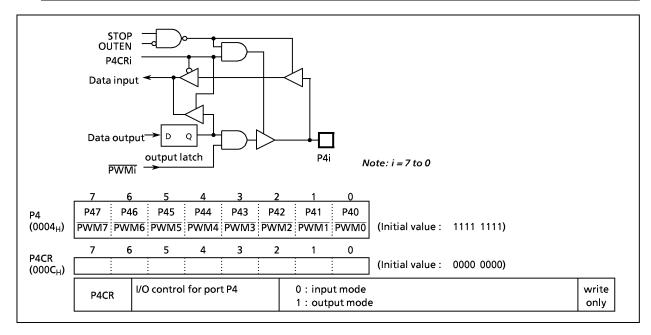

| P47 (PWM7)<br>to P41 (PWM1)            | (PWM1) (tri-state). Each bit of this port can be individually configured as an input or an |                                                                                                                                                                                                | 7-bit D/A conversion (PWM) outputs                                     |  |  |

| P40 ( <del>PWM0</del> )                | I/O (Output)                                                                               | output under software control. During reset, all bits are configured as inputs. When used as a PWM output, the latch must be set to "1".                                                       | 14-bit D/A conversion (PWM) output                                     |  |  |

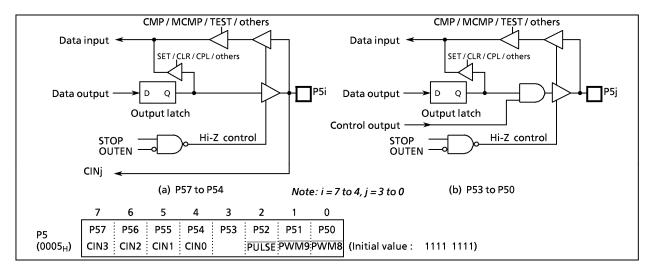

| P57 (CIN3)<br>to P54 (CIN0)            | I/O (Input)                                                                                | 8-bit input/output port with latch.                                                                                                                                                            | 6-bit A/D conversion (Comparator) inputs                               |  |  |

| P53                                    | I/O                                                                                        | When used as an input port, a                                                                                                                                                                  |                                                                        |  |  |

| P52 (PULSE)                            |                                                                                            | comparator input, a PWM output, or a pulse output, the latch must be set to                                                                                                                    | Pulse output (Clock for PLL IC)                                        |  |  |

| P51 (PWM9)<br>P50 (PWM8)               | I/O (Output)                                                                               | "1".                                                                                                                                                                                           | 7-bit D/A conversion (PWM) outputs                                     |  |  |

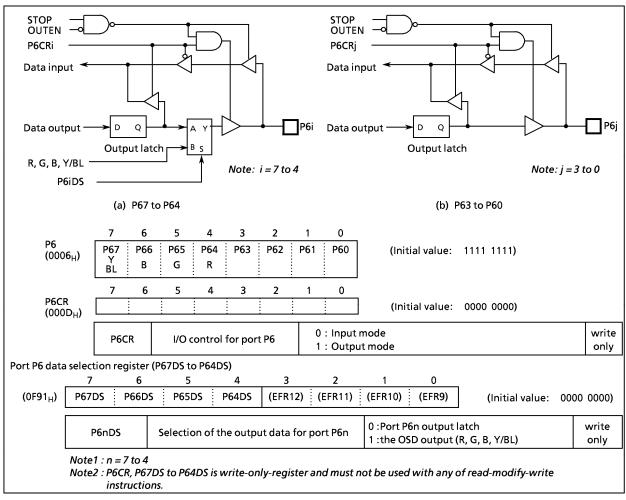

| P67 (Y/BL)                             |                                                                                            | 8-bit programmable input/output port<br>(P67 to P64 : tri-state, P63 to P60 : High                                                                                                             | Focus signal output or Background blanking control signal output       |  |  |

| P66 (B)<br>P65 (G)<br>P64 (R)          | I/O (Output)                                                                               | current output). Each bit of this port can<br>be individually configured as an input or<br>an output under software control.<br>During reset, all bits are configured as                       | RGB output                                                             |  |  |

| P63<br>P62<br>P61<br>P60               | 1/0                                                                                        | inputs. When used as the R, G, B, Y / BL outputs of on-screen display circuit, each bit of the P6 port data selection register (bits 7 to 4 in address 0F91 <sub>H</sub> ) must be set to "1". | High current output.                                                   |  |  |

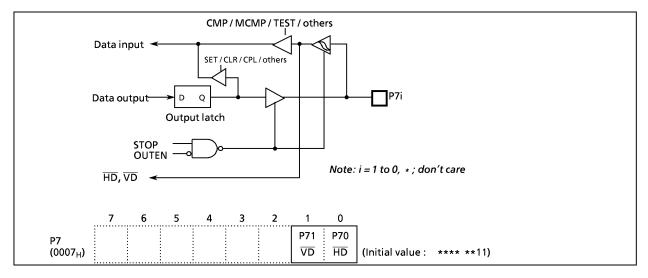

| P71 (VD)                               | I/O (Input)                                                                                | 2-bit input/output port with latch. When used as an input ports, or a vertical synchronous signal input and horizontal                                                                         | Vertical synchronous signal input                                      |  |  |

| P70 (HD)                               |                                                                                            | synchronous signal input, the latch must be set to "1".                                                                                                                                        | Horizontal synchronous signal input                                    |  |  |

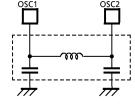

| OSC1, OSC2                             | Input Output                                                                               | Resonator connecting pins for on-screen di                                                                                                                                                     | isplay circuitry.                                                      |  |  |

| XIN, XOUT                              | Input, Output                                                                              | Resonator connecting pins. For inputting e                                                                                                                                                     | external clock, XIN is used and XOUT is opened.                        |  |  |

| RESET                                  | 1/0                                                                                        | Reset signal input or watchdog timer output/address-trap- reset output/system-clock-resoutput.                                                                                                 |                                                                        |  |  |

| TEST                                   | Input                                                                                      | Test pin for out-going test. Be tied to low.                                                                                                                                                   |                                                                        |  |  |

| VDD, VSS Power Supply + 5 V, 0 V (GND) |                                                                                            |                                                                                                                                                                                                |                                                                        |  |  |

# **Operational Description**

#### 1. CPU Core Functions

The CPU core consists of a CPU, a system clock controller, an interrupt controller, and a watchdog timer. This section provides a description of the CPU core, the program memory (ROM), the data memory (RAM), and the reset circuit.

### 1.1 Memory Address Map

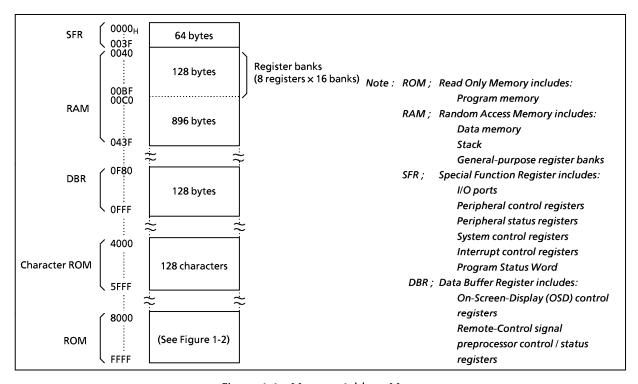

The TLCS-870 Series is capable of addressing 64 Kbytes of memory. Figure 1-1 shows the memory address maps of the 87CH36/K36/M36. In the TLCS-870 Series, the memory is organized 4 address spaces (ROM, RAM, SFR, and DBR). It uses a memory mapped I/O system, and all I/O registers are mapped in the SFR / DBR address spaces. There are 16 banks of general-purpose registers. The register banks are also assigned to the first 128 bytes of the RAM address space.

Figure 1-1. Memory Address Map

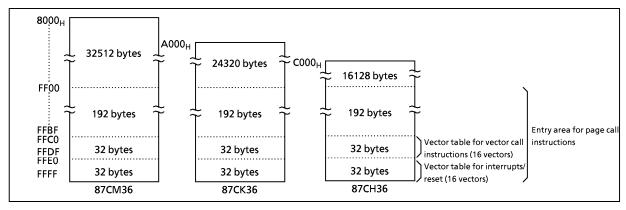

Figure 1-2. ROM Address Maps

# 1.2 Program Memory (ROM)

The 87CH36 has a 16 Kbytes (addresses  $C000_H$  to  $FFFF_H$ ), the 87CK36 has a 24 Kbytes (addresses  $A000_H$  to  $A0000_H$  to  $A0000_H$  to  $A0000_H$  to  $A0000_H$  to  $A0000_H$

- (1) Interrupt / Reset vector table (addresses FFE0<sub>H</sub> to FFFF<sub>H</sub>)

This table consists of a reset vector and 15 interrupt vectors (2 bytes/vector). These vectors store a reset start address and 15 interrupt service routine entry addresses.

- (2) Vector table for vector call instructions (addresses FFC0<sub>H</sub> to FFDF<sub>H</sub>)

This table stores call vectors (subroutine entry address, 2 bytes/vector) for the vector call instructions [CALLV n]. There are 16 vectors. The CALLV instruction increases memory efficiency when utilized for frequently used subroutine calls (called from 3 or more locations).

- (3) Entry area (addresses FF00<sub>H</sub> to FFFF<sub>H</sub>) for **page call** instructions

This is the subroutine entry address area for the page call instructions [CALLP n]. Addresses FF00<sub>H</sub>

FFBF<sub>H</sub> are normally used because address FFC0<sub>H</sub> to FFFF<sub>H</sub> are used for the vector tables.

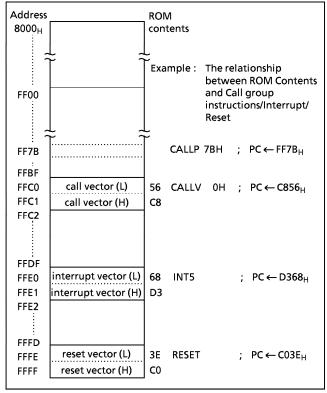

Programs and fixed data are stored in the program memory. The instruction to be executed next is read from the address indicated by the current contents of the program counter (PC). There are relative jump and absolute jump instructions. The concepts of page or bank boundaries are not used in the program memory concerning any jump instruction.

Example : The relationship between the jump instructions and the PC.

- ① 5-bit PC-relative jump [JRS cc, \$+2+d] E8C4H: JRS T, \$+2+08H When JF = 1, the jump is made to E8CE<sub>H</sub>, which is 08<sub>H</sub> added to the contents of the PC. (The PC contains the address of the instruction being executed + 2; therefore, in this case, the PC contents are E8C4<sub>H</sub> + 2 = E8C6<sub>H</sub>.)

- ② 8-bit PC-relative jump [JR cc, \$+2+d] E8C4H: JR Z, \$+2+80H When ZF = 1, the jump is made to E846H, which is FF80H (-128) added to the current contents of the PC.

- 3 16-bit absolute jump [JP a] E8C4H: JP 0C235H An unconditional jump is made to address C235<sub>H</sub>. The absolute jump instruction can jump anywhere within the entire 64K-byte space.

Figure 1-3. Program Memory Map

In the TLCS-870 Series, the same instruction used to access the data memory (e.g. [LD A, (HL)]) is also used to read out fixed data (ROM data) stored in the program memory. The register-offset PC-relative addressing (PC + A) instructions can also be used, and the code conversion, table look-up and n-way multiple jump processing can easily be programmed.

Example 1 : Loads the ROM contents at the address specified by the HL register pair contents into the

accumulator (HL  $\geq$  8000<sub>H</sub> for 87CH36/K36/M36):

LD A, (HL);  $A \leftarrow ROM(HL)$

Example 2 : Converts BCD to 7-segment code (common anode LED). When  $A = 05_H$ ,  $92_H$  is output to

port P5 after executing the following program:

ADD A, TABLE-\$-4; P5  $\leftarrow$ ROM (TABLE + A)

LD (P5), (PC+A) JRS T, SNEXT

TABLE: DB OCOH, OF9H, OA4H, OBOH, 99H, 92H, 82H,

0D8H, 80H, 98H

SNEXT:

Notes: "\$" is a header address of ADD instruction.

DB is a byte data difinition instruction.

Example 3 : N-way multiple jump in accordance with the contents of

accumulator (0  $\leq$  A  $\leq$  3):

SHLC A ; if  $A = 00_H$  then  $PC \leftarrow C234_H$ JP (PC+A) if  $A = 01_H$  then  $PC \leftarrow C378_H$

if  $A = 02_H$  then  $PC \leftarrow DA37_H$ if  $A = 03_H$  then  $PC \leftarrow E1B0_H$

DW 0C234H, 0C378H, 0DA37H, 0E1B0H

Note: DW is a word data definition instruction.

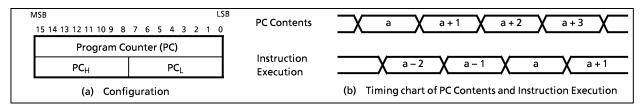

# 1.3 Program Counter (PC)

The program counter (PC) is a 16-bit register which indicates the program memory address where the instruction to be executed next is stored. After reset, the user defined reset vector stored in the vector table (addresses FFFF<sub>H</sub> and FFFE<sub>H</sub>) is loaded into the PC; therefore, program execution is possible from any desired address. For example, when CO<sub>H</sub> and 3E<sub>H</sub> are stored at addresses FFFF<sub>H</sub> and FFFE<sub>H</sub>, respectively, the execution starts from address CO3E<sub>H</sub> after reset.

The TLCS-870 Series utilizes pipelined processing (instruction pre-fetch); therefore, the PC always indicates 2 addresses in advance. For example, while a 1-byte instruction stored at address C123<sub>H</sub> is being executed, the PC contains C125<sub>H</sub>.

Figure 1-4. Program Counter

SHLC A

JP (PC + A)

78

37 DA

B0

# Data Memory (RAM)

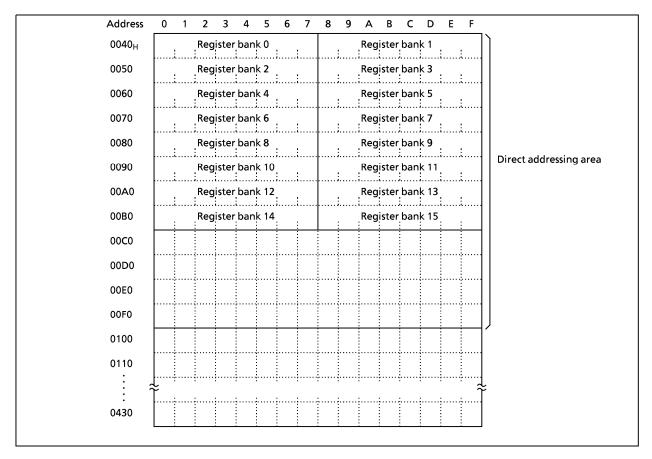

The 87CH36/K36/M36 have 1Kbytes (addresses 0040H to 043FH) of data memory (static RAM). Figure 1-5 shows the data memory map.

Addresses 0000H to 00FFH are used as a direct addressing area to enhance instructions which utilize this addressing mode; therefore, addresses 0040H to 00FFH in the data memory can also be used for user flags or user counters. General-purpose register banks (8 registers x 16 banks) are also assigned to the 128 bytes of addresses 0040<sub>H</sub>-00BF<sub>H</sub>. Access as data memory is still possible even when being used for registers. For example, when the contents of the data memory at address 0040H is read out, the contents of the accumulator in the bank 0 are also read out. The stack can be located anywhere within the data memory except the register bank area. The stack depth is limited only by the free data memory size. For more details on the stack, see section "1.7 Stack and Stack Pointer".

The TLCS-870 Series cannot execute programs placed in the data memory. When the program counter indicates a data memory address, a bus error occurs and an address-trap-reset applies. The RESET pin goes low during the address-trap-reset.

```

Example 1: If bit 2 at data memory address 00C0<sub>H</sub> is "1", 00<sub>H</sub> is written to data memory at address

```

00E3<sub>H</sub>; otherwise, FF<sub>H</sub> is written to the data memory at address 00E3<sub>H</sub>:

```

(00C0H).2; if (00C0_H)_2 = 0 then jump

```

JRS T,SZERO

CLR (00E3H) ;  $(00E3_{H})$  ←  $00_{H}$

JRS T, SNEXT

SZERO : LD (00E3H), 0FFH ;  $(00E3_H) \leftarrow FF_H$

SNEXT:

Example 2: Increments the contents of data memory at address 00F5<sub>H</sub>, and clears to 00<sub>H</sub> when 10<sub>H</sub> is exceeded:

INC (00F5H) ;  $(00F5_H) \leftarrow (00F5_H) + 1$

AND (00F5H), 0FH;  $(00F5H) \leftarrow (00F5H) \land 0FH$

The data memory contents become unstable when the power supply is turned on; therefore, the data memory should be initialized by an initialization routine. Note that the general-purpose registers are mapped in the RAM; therefore, do not clear RAM at the current bank addresses.

Example : Clears RAM to "00H" except the bank 0:

> LD HL, 0048H; Sets start address to HL register pair ; Sets initial data (00<sub>H</sub>) to A register LD A, H

LD BC, 03F7H; Sets number of byte to BC register pair

SRAMCLR: LD (HL+), A

DEC BC

JRS F, SRAMCLR

Figure 1-5. Data Memory Map

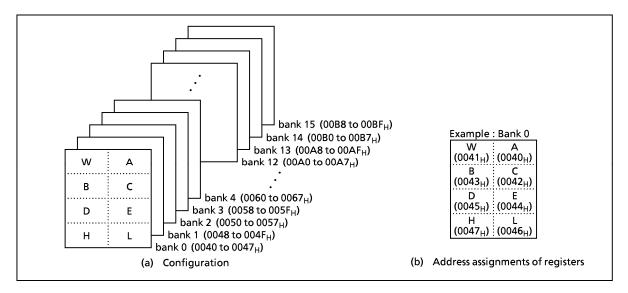

## 1.5 General-purpose Register Banks

General-purpose registers are mapped into addresses 0040<sub>H</sub> to 00BF<sub>H</sub> in the data memory as shown in Figure 1-5. There are 16 register banks, and each bank contains eight 8-bit registers W, A, B, C, D, E, H, and L. Figure 1-6 shows the general-purpose register bank configuration.

Figure 1-6. General-purpose Register Banks

In addition to access in 8-bit units, the registers can also be accessed in 16-bit units as the register pairs WA, BC, DE, and HL. Besides its function as a general-purpose register, the register also has the following functions:

#### (1) A, WA

The A register functions as an 8-bit accumulator and WA the register pair functions as a 16-bit accumulator (W is high byte and A is low byte). Registers other than A can also be used as accumulators for 8-bit operations.

Examples: ① ADD A, B; Adds B contents to A contents and stores the result into A.

② SUB WA, 1234H; Subtracts 1234H from WA contents and stores the result into

WA.

③ SUB E, A ; Subtracts A contents from E contents, and stores the result

into E.

### (2) HL, DE

The HL and DE specify a memory address. The HL register pair functions as data pointer (HL) / index register (HL + d) / base register (HL + C), and the DE register pair function as a data pointer (DE). The HL also has an auto-post- increment and auto-pre-decrement functions. This function simplifies multiple digit data processing, software LIFO (last-in first-out) processing, etc.

Example 1: ① LD A, (HL) ; Loads the memory contents at the address specified by HL into A.

② LD A, (HL + 52H) ; Loads the memory contents at the address specified by the value obtained by adding 52H to HL contents into A.

③ LD A, (HL + C) ; Loads the memory contents at the address specified by the value obtained by adding the register C contents to HL contents into A.

④ LD A, (HL +) ; Loads the memory contents at the address specified by HL

into A. Then increments HL.

⑤ LD A, (-HL); Decrements HL. Then loads the memory contents at the

address specified by new HL into A.

The TLCS-870 Series can transfer data directly memory to memory, and operate directly between

Example 2: Block transfer

LD B, n-1; Sets (number of bytes to transfer) – 1 to B

LD HL, DSTA ; Sets destination address to HL

memory data and memory data. This facilitates the programming of block processing.

LD DE, SRCA; Sets source address to DE

SLOOP : LD (HL), (DE) ; (HL)  $\leftarrow$  (DE)

INC HL ;  $HL \leftarrow HL + 1$ INC DE ;  $DE \leftarrow DE + 1$ DEC B ;  $B \leftarrow B - 1$

JRS F, SLOOP; if B≥0 then loop

2004-10-01

#### (3) B, C, BC

Registers B and C can be used as 8-bit buffers or counters, and the BC register pair can be used as a 16-bit buffer or counter. The C register functions as an offset register for register-offset index addressing (refer to example 1 ③ above) and as a divisor register for the division instruction [DIV gg, C].

Example 1: Repeat processing

LD B, n ; Sets n as the number of repetitions to B

SREPEAT: processing (n + 1 times processing)

DEC B

JRS F, SREPEAT

Example 2: Unsigned integer division (16-bit ÷ 8-bit)

DIV WA, C; Divides the WA contents by the C contents, places the quotient in

Aand the remainder in W.

The general-purpose register banks are selected by the 4-bit register bank selector (RBS). During reset, the RBS is initialized to "0". The bank selected by the RBS is called the current bank.

Together with the flag, the RBS is assigned to address  $003F_H$  in the SFR as the program status word (PSW). There are 3 instructions [LD RBS, n], [PUSH PSW] and [POP PSW] to access the PSW. The PSW can be also operated by the memory access instruction.

Example 1: Incrementing the RBS

INC (003FH); RBS  $\leftarrow$  RBS + 1

Example 2: Reading the RBS

LD A, (003FH);  $A \leftarrow PSW (A_{3-0} \leftarrow RBS, A_{7-4} \leftarrow Flags)$

Highly efficient programming and high-speed task switching are possible by using bank changeover to save registers during interrupt and to transfer parameters during subroutine processing.

During interrupt, the PSW is automatically saved onto the stack. The bank used before the interrupt was accepted is restored automatically by executing an interrupt return instruction [RETI]/[RETN]; therefore, there is no need for the RBS save/restore software processing.

The TLCS-870 Series supports a maximum of 15 interrupt sources. One bank is assigned to the main program, and one bank can be assigned to each source. Also, to increase the efficiency of data memory usage, assign the same bank to interrupt sources which are not nested.

Example : Saving /restoring registers during interrupt task using bank changeover.

PINT1 : LD RBS, n ; RBS  $\leftarrow$  n (Bank changeover)

Interrupt processing

RETI ; Maskable interrupt return (Bank restoring)

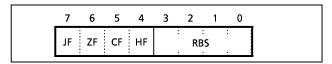

# 1.6 Program Status Word (PSW)

The program status word (PSW) consists of a register bank selector (RBS) and four flags, and the PSW is assigned to address 003F<sub>H</sub> in the SFR.

The RBS can be read and written using the memory access instruction (e. g. [LD A, (003FH)], [LD (003FH), A], however the flags can only be read. When writing to the PSW, the change specified by the instruction is made without writing data to the flags. For example, when the instruction [LD (003FH), 05H] is executed, "5" is written to the RBS and the JF is set to "1", but the other flags are not affected. [PUSH PSW] and [POP PSW] are PSW access instructions.

# 1.6.1 Register bank selector (RBS)

The register bank selector (RBS) is a 4-bit register used to select general-purpose register banks. For example, when RBS = 2, bank 2 is currently selected. During reset, the RBS is initialized to "0".

Figure 1-7. PSW (Flags, RBS) Configuration

### 1.6.2 Flags

The flags are configured with the upper 4 bits: a zero flag, a carry flag, a half carry flag and a jump status flag. The flags are set or cleared under conditions specified by the instruction. These flags except the half carry flag are used as jump condition "cc" for conditional jump instructions [JR cc, +2+d]/[JRS cc, +2+d]. After reset, the jump status flag is initialized to "1", other flags are not affected.

# (1) Zero flag (ZF)

The ZF is set to "1" if the operation result or the transfer data is  $00_H$  (for 8-bit operations and data transfers)/0000<sub>H</sub> (for 16-bit operations); otherwise the ZF is cleared to "0".

During the bit manipulation instructions [SET, CLR, and CPL], the ZF is set to "1" if the contents of the specified bit is "0"; otherwise the ZF is cleared to "0".

This flag is set to "1" when the upper 8 bits of the product are  $00_H$  during the multiplication instruction [MUL], and when  $00_H$  for the remainder during the division instruction [DIV]; otherwise it is cleared to "0".

## (2) Carry flag (CF)

The CF is set to "1" when a carry out of the MSB (most significant bit) of the result occurred during addition or when a borrow into the MSB of the result occurred during subtraction; otherwise the CF is cleared to "0". During division, this flag is set to "1" when the divisor is  $00_H$  (divided by zero error), or when the quotient is  $100_H$  or higher (quotient overflow error); otherwise it is cleared. The CF is also affected during the shift/rotate instructions [SHLC, SHRC, ROLC, and RORC]. The data shifted out from a register is set to the CF.

This flag is also a 1-bit register (a boolean accumulator) for the bit manipulation instructions. Set/clear/complement are possible with the CF manipulation instructions.

RORC A

## (3) Half carry flag (HF)

The HF is set to "1" when a carry occurred between bits 3 and 4 of the operation result during an 8-bit addition, or when a borrow occurred from bit 4 into bit 3 of the result during an 8-bit subtraction; otherwise the HF is cleared to "0". This flag is useful in the decimal adjustment for BCD operations (adjustments using the [DAA r], or [DAS r] instructions).

Example: BCD operation

(The A becomes  $47_H$  after executing the following program when A =  $19_H$ , B =  $28_H$ )

ADD A, B;  $A \leftarrow 41_H$ ,  $HF \leftarrow 1$

DAA A ;  $A \leftarrow 41_H + 06H = 47_H$  (decimal-adjust)

# (4) Jump status flag (JF)

Zero or carry information is set to the JF after operation (e.g. INC, ADD, CMP, TEST).

The JF provides the jump condition for conditional jump instructions [JRS T/F, +2+d], [JR T/F, +2+d] (T or F is a condition code). Jump is performed if the JF is "1" for a true condition (T), or the JF is "0" for a false condition (F).

The JF is set to "1" after executing the load/exchange/swap/nibble rotate/jump instruction, so that [JRS T, \$ + 2 + d] and [JR T, \$ + 2 + d] can be regarded as an unconditional jump instruction.

Example: Jump status flag and conditional jump instruction

INC A

JRS T, SLABLE1; Jump when a carry is caused by the immediately

: preceding operation instruction.

LD A, (HL)

JRS T, SLABLE2; JF is set to "1" by the immediately preceding

instruction, making it an unconditional jump instruction.

Example: The accumulator and flags become as shown below after executing the following instructions when the WA register pair, the HL register pair, the data memory at

address  $00C5_{H}$ , the carry flag and the half carry flag contents being "219 $A_{H}$ ", "00 $C5_{H}$ ",

"D7<sub>H</sub>", "1" and "0", respectively.

| Instruction |             | Acc. after | Flag after execution |    |    |    |  |

|-------------|-------------|------------|----------------------|----|----|----|--|

|             | ti deti ori | execution  | JF                   | ZF | CF | HF |  |

| ADDC        | A, (HL)     | 72         | 1                    | 0  | 1  | 1  |  |

| SUBB        | A, (HL)     | C2         | 1                    | 0  | 1  | 0  |  |

| СМР         | A, (HL)     | 9A         | 0                    | 0  | 1  | 0  |  |

| AND         | A, (HL)     | 92         | 0                    | 0  | 1  | 0  |  |

| LD          | A, (HL)     | D7         | 1                    | 0  | 1  | 0  |  |

| ADD         | А, 66Н      | 00         | 1                    | 1  | 1  | 1  |  |

| Instruction    | Acc. after | Flag after execution |    |    |    |  |

|----------------|------------|----------------------|----|----|----|--|

| msa dellon     | execution  | JF                   | ZF | CF | HF |  |

| INC A          | 9В         | 0                    | 0  | 1  | 0  |  |

| ROLC A         | 35         | 1                    | 0  | 1  | 0  |  |

| RORC A         | CD         | 0                    | 0  | 0  | 0  |  |

| ADD WA, 0F508H | 16A2       | 1                    | 0  | 1  | 0  |  |

| MUL W, A       | 13DA       | 0                    | 0  | 1  | 0  |  |

| SET A.5        | ВА         | 1                    | 1  | 1  | 0  |  |

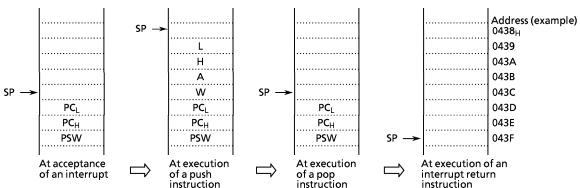

#### 1.7 Stack and Stack Pointer

#### 1.7.1 Stack

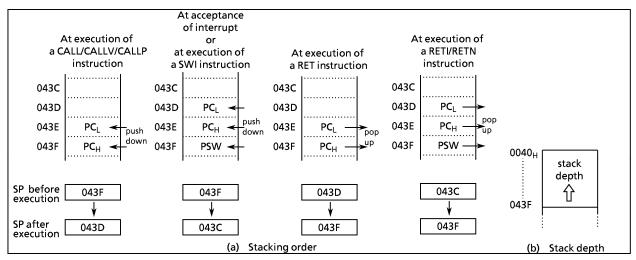

The stack provides the area in which the return address or status, etc. are saved before a jump is performed to the processing routine during the execution of a subroutine call instruction or the acceptance of an interrupt. On a subroutine call instruction [CALL a] / [CALLP n] / [CALLV n], the contents of the PC (the return address) is saved; on an interrupt acceptance, the contents of the PC and the PSW are saved (the PSW is pushed first, followed by PC<sub>H</sub> and PC<sub>L</sub>). Therefore, a subroutine call occupies two bytes on the stack; an interrupt occupies three bytes.

When returning from the processing routine, executing a subroutine return instruction [RET] restores the contents to the PC from the stack; executing an interrupt return instruction [RETI] / [RETN] restores the contents to the PC and the PSW (the PC<sub>L</sub> is popped first, followed by PC<sub>H</sub> and PSW).

The stack can be located anywhere within the data memory space except the register bank area, therefore the stack depth is limited only by the free data memory size.

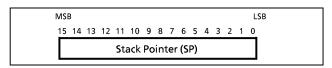

# 1.7.2 Stack pointer (SP)

The stack pointer (SP) is a 16-bit register containing the address of the next free locations on the stack. The SP is post-decremented when a subroutine call or a push instruction is executed, or when an interrupt is accepted; and the SP is pre-incremented when a return or a pop instruction is executed. Figure 1-9 shows the stacking order.

Figure 1-8. Stack Pointer

The SP is not initialized hardware-wise but requires initialization by an initialize routine (sets the highest stack address). [LD SP, mn], [LD SP, gg] and [LD gg, SP] are the SP access instructions (mn; 16-bit immediate data, gg; register pair).

Example 1: To initialize the SP

LD SP, 043FH; SP←043F<sub>H</sub>

Example 2: To read the SP

LD HL, SP ; HL←SP

Figure 1-9. Stack

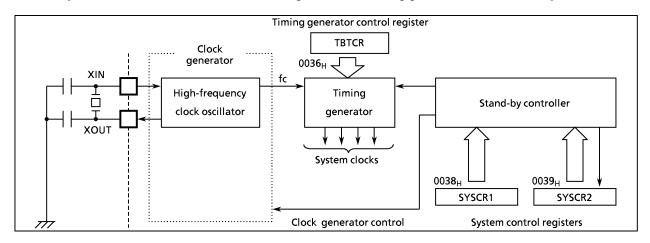

# 1.8 System Clock Controller

The system clock controller consists of a clock generator, a timing generator, and a stand-by controller.

Figure 1-10. System Clock Controller

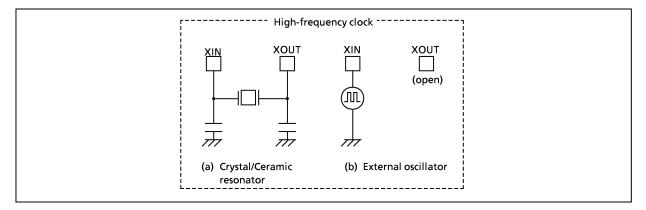

# 1.8.1 Clock generator

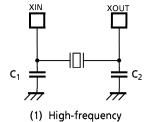

The clock generator generates the basic clock which provides the system clocks supplied to the CPU core and peripheral hardware. It contains a oscillation circuit for the high-frequency clock.

The high-frequency (fc) clock can be easily obtained by connecting a resonator between the XIN/XOUT pins, respectively. Clock input from an external oscillator is also possible. In this case, external clock is applied to the XIN pin with the XOUT pin not connected. The 87CH36/K36/M36 is not provided an RC oscillation.

Figure 1-11. Examples of Resonator Connection

Note: Accurate Adjustment of the Oscillation Frequency:

Although hardware to externally and directly monitor the basic clock pulse is not provided, the oscillation frequency can be adjusted by providing a program to output fixed frequency pulses to the port while disabling all interrupts and monitoring this pulse. With a system requiring adjustment of the oscillation frequency, the adjusting program must be created beforehand.

# 1.8.2 Timing generator

The timing generator generates from the basic clock the various system clocks supplied to the CPU core and peripheral hardware. The timing generator provides the following functions:

- ① Generation of main system clock

- ② Generation of source clocks for time base timer

- 3 Generation of source clocks for watchdog timer

- ④ Generation of internal source clocks for timer/counters TC1 to TC4

- ⑤ Generation of warm-up clocks for releasing STOP mode

- 6 Generation of a clock for releasing reset output

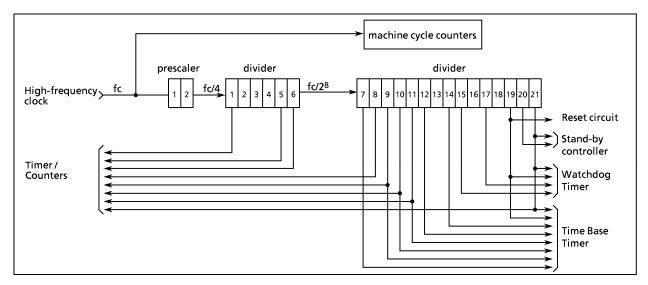

#### (1) Configuration of Timing Generator

The timing generator consists of a 21-stage divider with a divided-by-4 prescaler, a main system clock generator, and machine cycle counters, shown in Figure 1-12 as follows. During reset and upon releasing STOP mode, the divider is cleared to "0", however, the prescaler is not cleared.

Figure 1-12. Configuration of Timing Generator

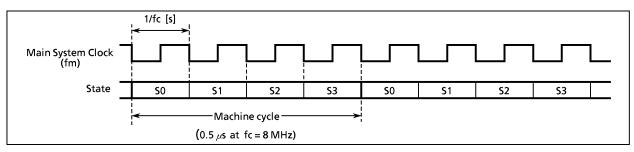

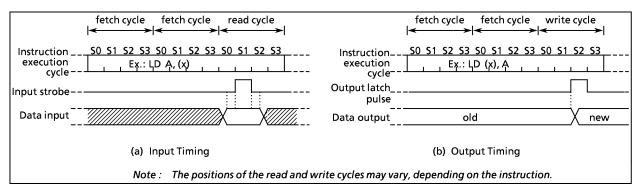

#### (2) Machine Cycle

Instruction execution and peripherals hardware operation are synchronized with the main system clock. The minimum instruction execution unit is called an "machine cycle". There are a total of 10 different types of instructions for the TLCS-870 Series: ranging from 1-cycle instructions which require one machine cycle for execution to 10-cycle instructions which require 10 machine cycles for execution.

A machine cycle consists of 4 states (S0 to S3), and each state consists of one main system clock.

Figure 1-13. Machine Cycle

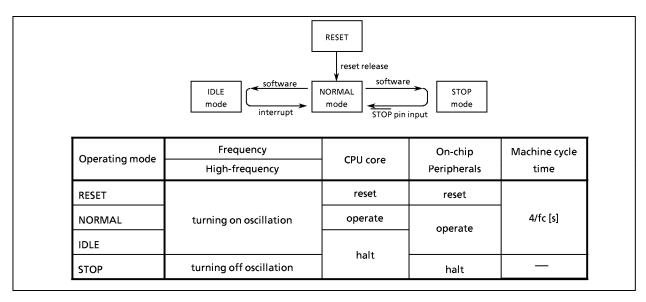

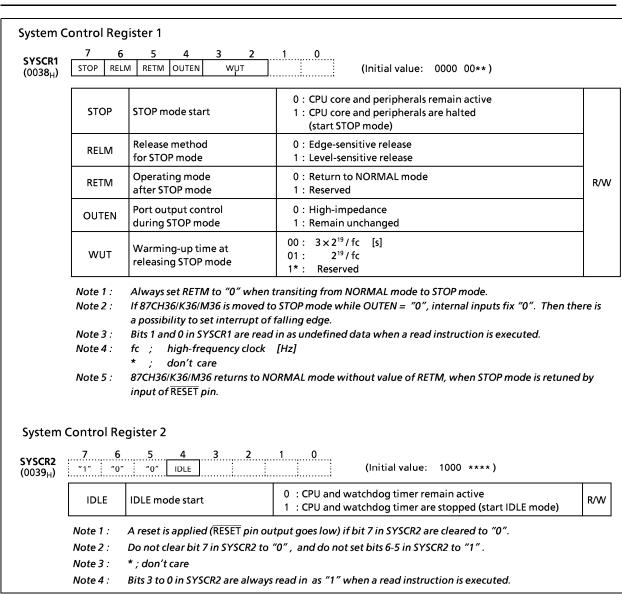

# 1.8.3 Stand-by controller

The stand-by controller starts and stops the oscillation circuit for the high-frequency clock. Operating modes are controlled by the system control registers (SYSCR1, SYSCR2).

Figure 1-14 shows the operating mode transition diagram and Figure 1-15 shows the system control registers.

### (1) Operating mode

- ① NORMAL mode

- In this mode, both the CPU core and on-chip peripherals operate.

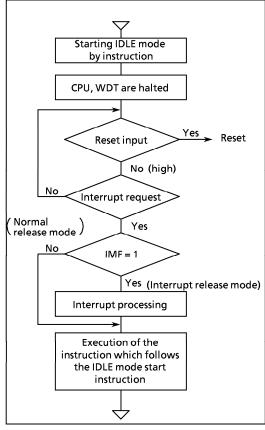

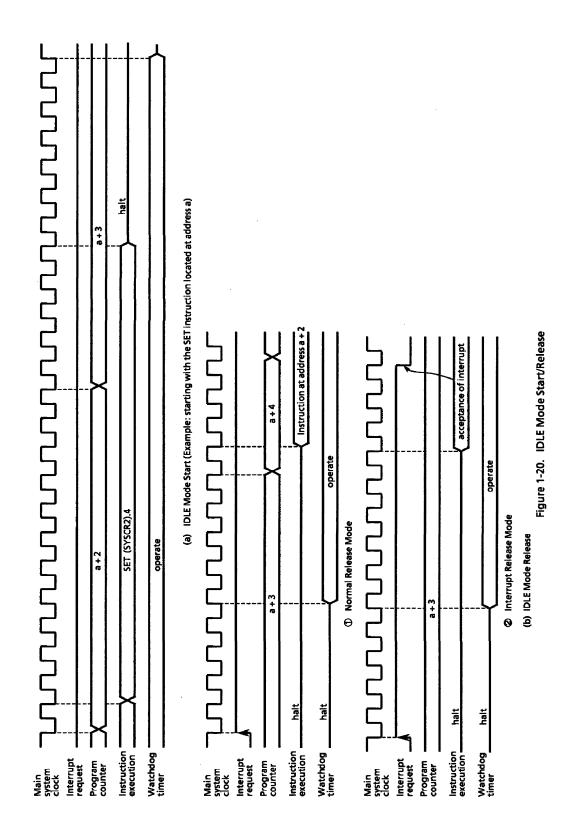

- ② IDLE mode

In this mode, the internal oscillation circuit remains active. The CPU and the watchdog timer are halted; however, on-chip peripherals remain active. IDLE mode is started by setting IDLE bit in the system control register 2 (SYSCR2), and IDLE mode is released to NORMAL mode by an interrupt request from on-chip peripherals or external interrupt inputs. When IMF (interrupt master enable flag) is "1" (interrupt enable), the execution will resume upon acceptance of the interrupt, and the operation will return to normal after the interrupt service is completed. When IMF is "0" (interrupt disable), the execution will resume with the next instruction which follows IDLE mode start instruction.

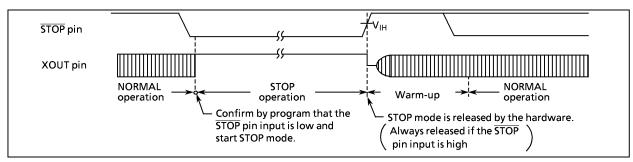

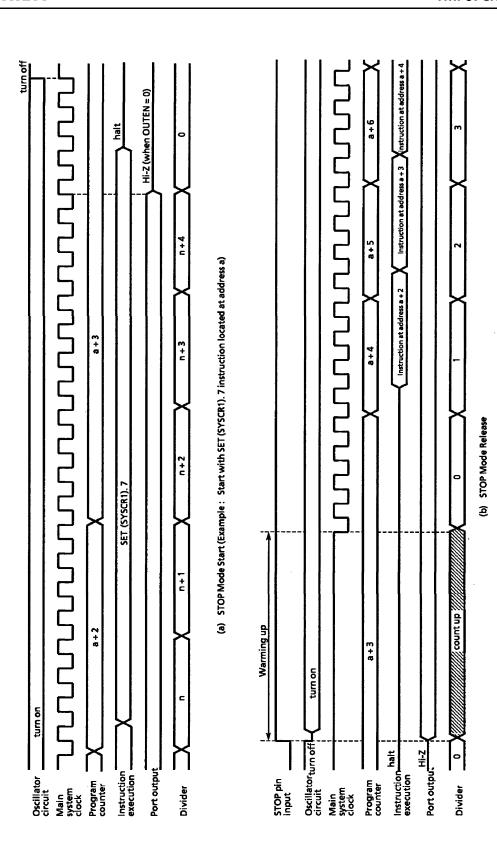

#### 3 STOP mode

In this mode, the internal oscillation circuit is turned off, causing all system operations to be halted. The internal status immediately prior to the halt is held with the lowest power consumption during this mode. The output status of all output ports can be set to either output hold or high-impedance under software control.

STOP mode is started by setting STOP bit in the system control register 1 (SYSCR1), and STOP mode is released by an input (either level-sensitive or edge-sensitive can be programmably selected) to the STOP pin. After the warming-up period is completed, the execution resumes with the next instruction which follows the STOP mode start instruction.

Figure 1-14. Operating Mode Transition Diagram

Figure 1-15. System Control Registers

#### 1.8.4 Operating mode control

#### (1) **STOP** mode

STOP mode is controlled by the system control register 1 (SYSCR1) and the STOP pin input. The STOP pin is also used both as a port P20 and an INT5 (external interrupt input 5) pin. STOP mode is started by setting STOP (bit 7 in SYSCR1) to "1". During STOP mode, the following status is maintained.

- ① Oscillation is turned off, and all internal operations are halted.

- The data memory, registers and port output latches are all held in the status in effect before STOP mode was entered. The port output can be select either output hold or high-impedance by setting OUTEN (bit 4 in SYSCR1).

- 3 The divider of the timing generator is cleared to "0".

- The program counter holds the address of the instruction following the instruction which started STOP mode.

STOP mode includes a level-sensitive release mode and an edge-sensitive release mode, either of which can be selected with RELM (bit 6 in SYSCR1).

## a. Level-sensitive release mode (RELM = 1)

In this mode, STOP mode is released by setting the  $\overline{\text{STOP}}$  pin high. This mode is used for capacitor back-up when the main power supply is cut off and for long term battery back-up.

When the STOP pin input is high, executing an instruction which starts the STOP mode will not place in STOP mode but instead will immediately start the release sequence (warm-up). Thus, to start STOP mode in the level-sensitive release mode, it is necessary for the program to first confirm that the STOP pin input is low. The following method can be used for confirmation:

• Using an external interrupt input INT5 (INT5 is a falling edge-sensitive input).

Example: Starting STOP mode with an INT5 interrupt. (TMP87CH36/K36/M36)

PINT5: TEST (P2). 0 ; To reject noise, STOP mode does not start JRS F, SINT5 if port P20 is at high

LD (SYSCR1), 01000000B ; Sets up the level-sensitive release mode.

SET (SYSCR1) . 7 ; Starts STOP mode LDW

(clears interrupt latches)

SINT5: RETI

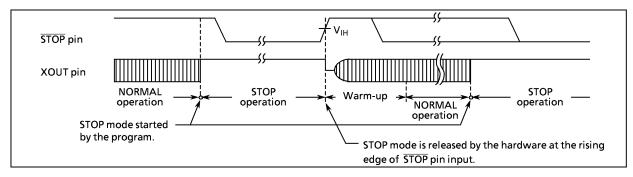

Figure 1-16. Level-sensitive Release Mode

Note1: After warming up is started, when STOP pin input is changed "L" level, STOP mode is not

Note2: When changing to the level-sensitive release mode from the edge-sensitive release mode, the release mode is not switched until a rising edge of the STOP pin input is detected.

# b. Edge-sensitive release mode (RELM = 0)

In this mode, STOP mode is released by a rising edge of the  $\overline{\text{STOP}}$  pin input. This is used in applications where a relatively short program is executed repeatedly at periodic intervals. This periodic signal (for example, a clock from a low-power consumption oscillator) is input to the  $\overline{\text{STOP}}$  pin.

In the edge-sensitive release mode, STOP mode is started even when the STOP pin input is high.

Example: Starting STOP mode operation in the edge-sensitive release mode (TMP87CM36)

LD (SYSCR1), 00000000B ; OUTEN ← 0 (specifies high-impedance)

DI ; IMF ← 0 (disables interrupt service)

SET (SYSCR1). STOP ; STOP ← 1 (activates stop mode)

LDW (IL), 1110011111111111B;  $IL12, 11 \leftarrow 0$

(clears interrupt latches)

EI ; IMF ← 1 (enables interrupt service)

Figure 1-17. Edge-sensitive Release Mode

#### STOP mode is released by the following sequence:

- ① The high-frequency clock oscillator is turned on.

- ② A warming-up period is inserted to allow oscillation time to stabilize. During warm-up, all internal operations remain halted. Two different warming-up times can be selected with WUT (bits 2 and 3 in SYSCR1) as determined by the resonator characteristics.

- When the warming-up time has elapsed, normal operation resumes with the instruction following the STOP mode start instruction (e.g. [SET (SYSCR1). 7]). The start is made after the divider of the timing generator is cleared to "0".

|                              | <b>3</b> 1           |            |  |  |

|------------------------------|----------------------|------------|--|--|

| WUT                          | At fc = 4.194304 MHz | At fc=8MHz |  |  |

| 3 × 2 <sup>19</sup> / fc [s] | 375 [ms]             | 196.6 [ms] |  |  |

| 2 <sup>19</sup> / fc         | 125                  | 65.5       |  |  |

Table 1-1. Warming-up Time example

Note: The warming-up time is obtained by dividing the basic clock by the divider: therefore, the warming-up time may include a certain amount of error if there is any fluctuation of the oscillation frequency when STOP mode is released. Thus, the warming-up time must be considered an approximate value.

STOP mode can also be released by setting the  $\overline{\text{RESET}}$  pin low, which immediately performs the normal reset operation.

Figure 1-18. STOP Mode Start / Release

Note: When STOP mode is released with a low hold voltage, the following cautions must be observed. The power supply voltage must be at the operating voltage level before releasing the STOP mode. The RESET pin input must also be high, rising together with the power supply voltage. In this case, if an external time constant circuit has been connected, the RESET pin input voltage will increase at a slower rate than the power supply voltage. At this time, there is a danger that a reset may occur if input voltage level of the RESET pin drops below the non-inverting high-level input voltage (hysteresis input).

## (2) IDLE mode

IDLE mode is controlled by the system control register 2 and maskable interrupts. The following status is maintained during IDLE mode.

- ① Operation of the CPU and watchdog timer is halted. On-chip peripherals continue to operate.

- ② The data memory, CPU registers and port output latches are all held in the status in effect before IDLE mode was entered.

- 3 The program counter holds the address of the instruction following the instruction which started IDLE mode.

IDLE mode includes a normal release mode and an interrupt release mode. Selection is made with the interrupt master enable flag (IMF). Releasing the IDLE mode returns to NORMAL mode.

# a. Normal release mode (IMF = "0")

IDLE mode is released by any interrupt source enabled by the individual interrupt enable flag (EF). Execution resumes with the instruction following the IDLE mode start instruction (e.g. [SET (SYSCR2).4]). Normally, IL (Interrupt Latch) of interrupt source to release IDLE mode must be cleared by load instructions.

Figure 1-19. IDLE Mode

# b. Interrupt release mode (IMF = "1")

IDLE mode is released and interrupt processing is started by any interrupt source enabled with the individual interrupt enable flag (EF). After the interrupt is processed, the execution resumes from the instruction following the instruction which started IDLE mode.

IDLE mode can also be released by setting the RESET pin low, which immediately performs the reset operation. After reset, the 87CH36/K36/M36 are placed in NORMAL mode.

Note: When a watchdog timer interrupt is generated immediately before IDLE mode is started, the watchdog timer interrupt will be processed but IDLE mode will not be started.

# 1.9 Interrupt Controller

The 87CH36/K36/M36 has a total of 12 interrupt sources: 3 externals and 9 internals. Nested interrupt control with priorities is also possible. Two of the internal sources are pseudo non-maskable interrupts; the remainder are all maskable interrupts.

Interrupt latches (IL) that hold the interrupt requests are provided for interrupt sources. Each interrupt vector is independent.

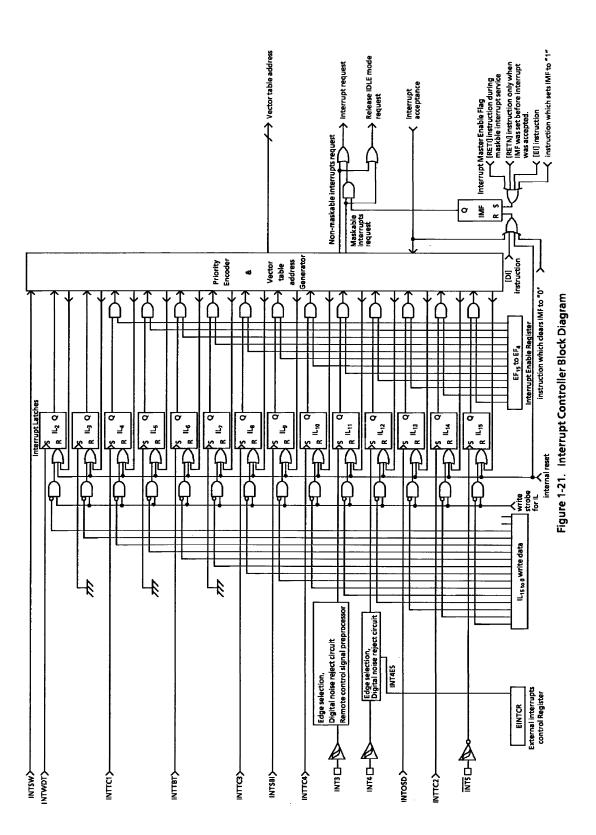

The interrupt latch is set to "1" when an interrupt request is generated and requests the CPU to accept the interrupt. The acceptance of maskable interrupts can be selectively enabled and disabled by the program using the interrupt master enable flag (IMF) and the individual interrupt enable flags (EF). When two or more interrupts are generated simultaneously, the interrupt is accepted in the highest priority order as determined by the hardware. Figure 1-21 shows the interrupt controller.

Table 1-2. Interrupt Sources

|                       | Interrupt Source                                              | Enable Condition           | Interrupt<br>Latch | Vector Table<br>Address | Priority |

|-----------------------|---------------------------------------------------------------|----------------------------|--------------------|-------------------------|----------|

| Internal/<br>External | rnal (Reset) Non-Maskable                                     |                            | _                  | FFFE <sub>H</sub>       | High 0   |

| Internal              | INTSW (Software interrupt)                                    | Pseudo                     | _                  | FFFC <sub>H</sub>       | 1        |

| Internal              | INTWDT (Watchdog Timer interrupt)                             | non-maskable               | IL <sub>2</sub>    | FFFA <sub>H</sub>       | 2        |

|                       | reserved                                                      | IMF = 1, INT0EN = 1        | IL <sub>3</sub>    | FFF8 <sub>H</sub>       | 3        |

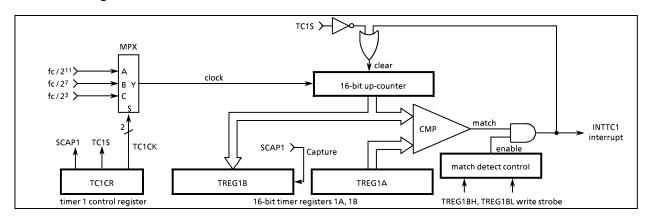

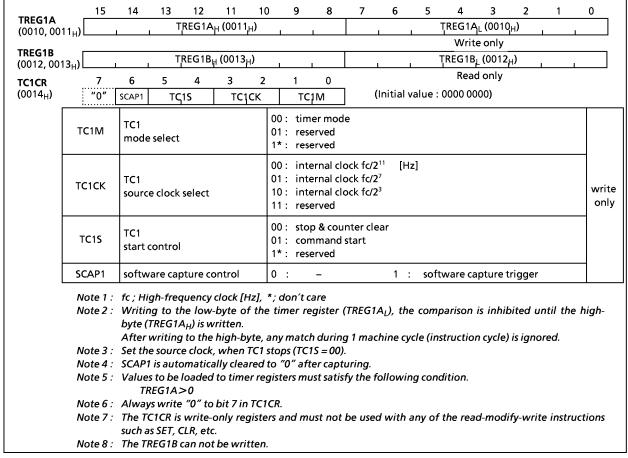

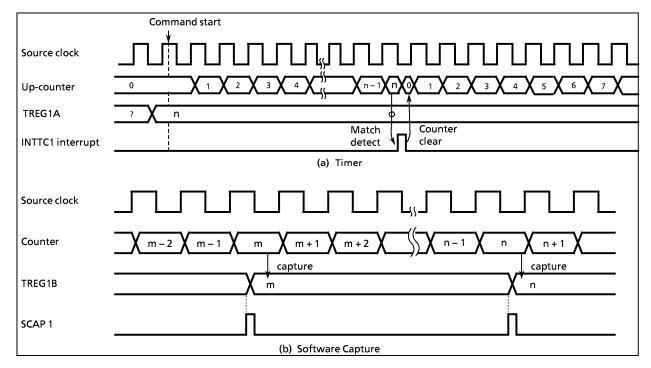

| Internal              | INTTC1 (16-bit TC1 interrupt)                                 | IMF · EF <sub>4</sub> = 1  | IL <sub>4</sub>    | FFF6 <sub>H</sub>       | 4        |

|                       | reserved                                                      | IMF • EF <sub>5</sub> = 1  | IL <sub>5</sub>    | FFF4 <sub>H</sub>       | 5        |

| Internal              | INTTBT (Time Base Timer interrupt)                            | IMF • EF <sub>6</sub> = 1  | IL <sub>6</sub>    | FFF2 <sub>H</sub>       | 6        |

|                       | reserved                                                      | IMF • EF <sub>7</sub> = 1  | IL <sub>7</sub>    | FFF0 <sub>H</sub>       | 7        |

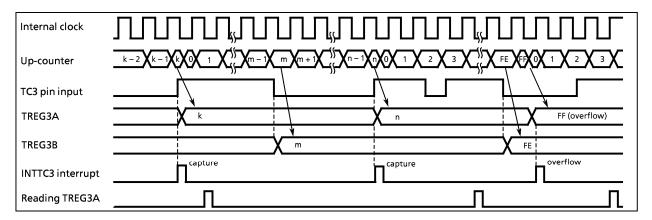

| Internal              | INTTC3 (8-bit TC3 interrupt)                                  | IMF • EF <sub>8</sub> = 1  | IL <sub>8</sub>    | FFEE <sub>H</sub>       | 8        |

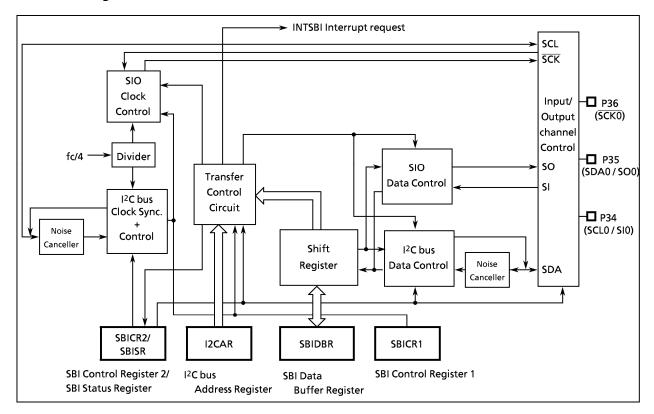

| Internal              | INTSBI (Serial bus Interface interrupt)                       | IMF · EF <sub>9</sub> = 1  | IL <sub>9</sub>    | FFEC <sub>H</sub>       | 9        |

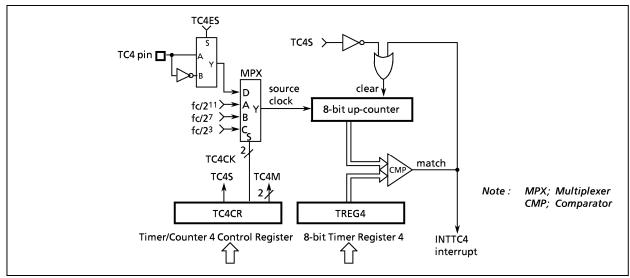

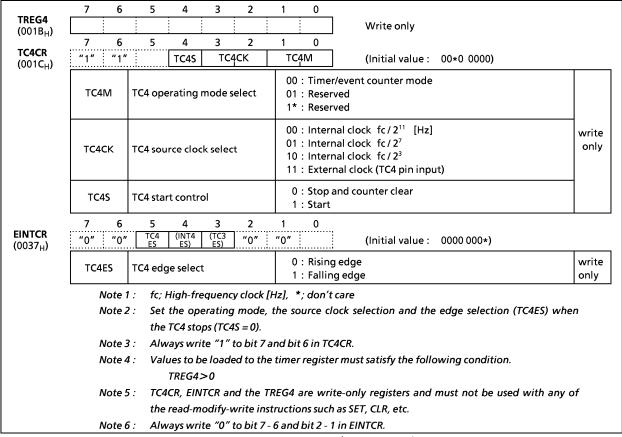

| Internal              | INTTC4 (8-bit TC4 interrupt)                                  | IMF • EF <sub>10</sub> = 1 | IL <sub>10</sub>   | FFEA <sub>H</sub>       | 10       |

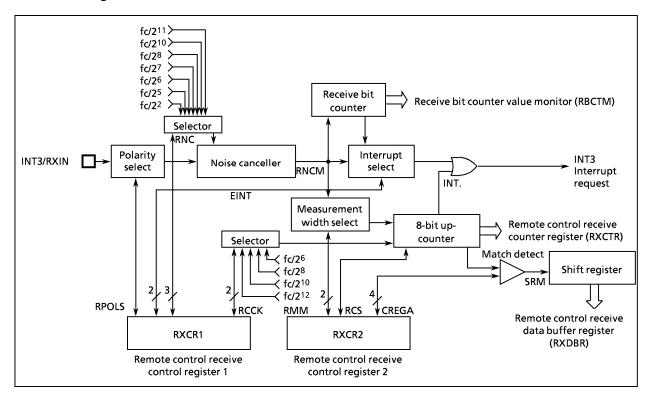

| External              | INT3 (External interrupt 3, Remote control receive interrupt) | IMF • EF <sub>11</sub> = 1 | IL <sub>11</sub>   | FFE8 <sub>H</sub>       | 11       |

| External              | INT4 (External interrupt 4)                                   | IMF • EF <sub>12</sub> = 1 | IL <sub>12</sub>   | FFE6 <sub>H</sub>       | 12       |

| Internal              | INTOSD (OSD interrupt)                                        | IMF • EF <sub>13</sub> = 1 | IL <sub>13</sub>   | FFE4 <sub>H</sub>       | 13       |

| Internal              | INTTC2 (16-bit TC2 interrupt)                                 | IMF • EF <sub>14</sub> = 1 | IL <sub>14</sub>   | FFE2 <sub>H</sub>       | 14       |

| External              | INT5 (External interrupt 5)                                   | IMF • EF <sub>15</sub> = 1 | IL <sub>15</sub>   | FFEO <sub>H</sub>       | Low 15   |

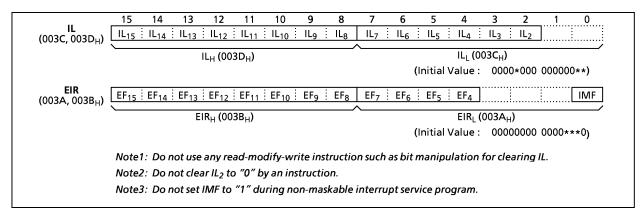

## (1) Interrupt Latches (IL<sub>15</sub> to <sub>2</sub>)

Interrupt latches are provided for each source, except for a software interrupt. The latch is set to "1" when an interrupt request is generated, and requests the CPU to accept the interrupt. The latch is cleared to "0" just after the interrupt is accepted. All interrupt latches except INT3 are initialized to "0" during reset. The interrupt latch of INT3 is unstable during reset.

The interrupt latches are assigned to addresses  $003C_H$  and  $003D_H$  in the SFR. Each latch can be cleared to "0" individually by an instruction; however, the read-modify-write instruction such as bit manipulation or operation instructions cannot be used (Do not clear the  $IL_2$  for a watchdog timer interrupt to "0"). Thus, interrupt requests can be cancelled and initialized by the program. Note that interrupt latches cannot be set to "1" by any instruction.

The contents of interrupt latches can be read out by an instruction. Therefore, testing interrupt requests by software is possible.

Example 1: Clears interrupt latches

LDW (IL), 1110101010111111B;  $|L_{12}, L_{10}, L_{8}, L_{6} \leftarrow 0$

Example 2 : Reads interrupt latches

LD WA, (IL) ;  $W \leftarrow IL_H$ ,  $A \leftarrow IL_L$

Example 3: Tests an interrupt latch

TEST (ILH).4 ; if  $IL_{12} = 1$  then jump

JR F, SSET

#### (2) Interrupt Enable Register (EIR)

The interrupt enable registers (EIR) enable and disable the acceptance of interrupts, except for the pseudo non-maskable interrupts (software and watchdog timer interrupts). Pseudo non-maskable interrupts are accepted regardless of the contents of the EIR; however, the pseudo non-maskable interrupts cannot be nested more than once at the same time. For example, the watchdog timer interrupt is not accepted during the software interrupt service.

The EIR consists of an interrupt master enable flag (IMF) and individual interrupt enable flags (EF). These registers are assigned to addresses 003A<sub>H</sub> and 003B<sub>H</sub> in the SFR, and can be read and written by an instruction (including read-modify-write instructions such as bit manipulation instructions).

#### ① Interrupt Master enable Flag (IMF)

The interrupt master enable flag (IMF) enables and disables the acceptance of all interrupts, except for pseudo non-maskable interrupts. Clearing this flag to "0" disables the acceptance of all maskable interrupts. Setting to "1" enables the acceptance of interrupts.

When an interrupt is accepted, this flag is cleared to "0" to temporarily disable the acceptance of maskable interrupts. After execution of the interrupt service program, this flag is set to "1" by the maskable interrupt return instruction [RETI] to again enable the acceptance of interrupts. If an interrupt request has already been occurred, interrupt service starts immediately after execution of the [RETI] instruction.

Pseudo non-maskable interrupts are returned by the [RETN] instruction. In this case, the IMF is set to "1" only when pseudo non-maskable interrupt service is started with interrupt acceptance enabled (IMF = 1). Note that the IMF remains "0" when cleared by the interrupt service program. The IMF is assigned to bit 0 at address 003AH in the SFR, and can be read and written by an instruction. The IMF is normally set and cleared by the [EI] and [DI] instructions, and the IMF is initialized to "0" during reset.

## ② Individual interrupt Enable Flags (EF<sub>15</sub> to EF<sub>4</sub>)

These flags enable and disable the acceptance of individual maskable interrupts. Setting the corresponding bit of an individual interrupt enable flag to "1" enables acceptance of an interrupt, setting the bit to "0" disables acceptance.

Example 1 : Sets EF for individual interrupt enable, and sets IMF to "1".

LDW (EIR), 111010000000001B;  $EF_{15}$  to  $EF_{13}$ ,  $EF_{11}$ ,  $IMF \leftarrow 1$

Example 2 : Sets an individual interrupt enable flag to "1".

SET (EIRH).4 ;  $EF_{12} \leftarrow 1$

Figure 1-22. Interrupt Latch (IL) and Interrupt Enable Register (EIR)

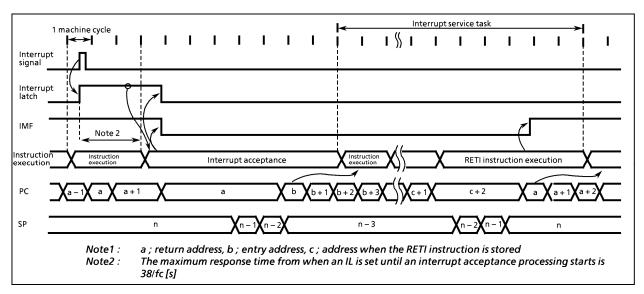

## 1.9.1 Interrupt sequence

An interrupt request is held until the interrupt is accepted or the interrupt latch is cleared to "0" by a reset or an instruction. Interrupt acceptance sequence requires 8 machine cycles (4  $\mu$ s at fc = 8 MHz in NORMAL mode) after the completion of the current instruction execution. The interrupt service task terminates upon execution of an interrupt return instruction [RETI] (for maskable interrupts) or [RETN] (for pseudo non-maskable interrupts).

#### (1) Interrupt acceptance processing is as follows:

- ① The interrupt master enable flag (IMF) is cleared to "0" to temporarily disable the acceptance of any following maskable interrupts. When a non-maskable interrupt is accepted, the acceptance of any following interrupts is temporarily disabled.

- ② The interrupt latch (IL) for the interrupt source accepted is cleared to "0".

- ③ The contents of the program counter (return address) and the program status word are saved (pushed) onto the stack. The stack pointer is decremented 3 times.

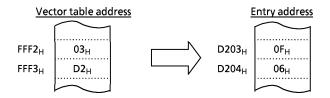

- The entry address of the interrupt service program is read from the vector table address, and the entry address is loaded to the program counter.

- The instruction stored at the entry address of the interrupt service program is executed.

Figure 1-23. Timing Chart of Interrupt Acceptance and Interrupt Return Instruction

Example: Correspondence between vector table address for INTTBT and the entry address of the interrupt service program.

A maskable interrupt is not accepted until the IMF is set to "1" even if a maskable interrupt of higher priority than that of the current interrupt being serviced.

When nested interrupt service is necessary, the IMF is set to "1" in the interrupt service program. In this case, acceptable interrupt sources are selectively enabled by the individual interrupt enable flags.

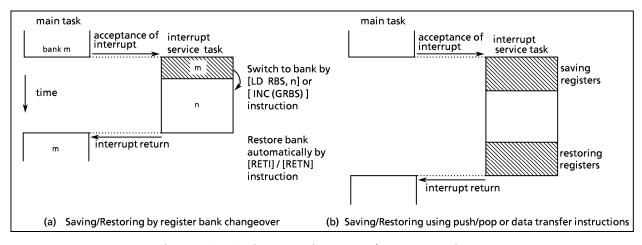

(2) Saving/Restoring General-purpose Register

During interrupt acceptance processing, the program counter and the program status word are automatically saved on the stack, but not the accumulator and other registers. These registers are saved by the program if necessary. Also, when nesting multiple interrupt services, it is necessary to avoid using the same data memory area for saving registers.

The following method is used to save/restore the general-purpose registers:

① General-purpose register save/restore by register bank changeover: General-purpose registers can be saved at high-speed by switching to a register bank that is not in use. Normally, bank 0 is used for the main task and banks 1 to 15 are assigned to interrupt service tasks. To increase the efficiency of data memory utilization, the same bank is assigned for interrupt sources which are not nested.

The switched bank is automatically restored by executing an interrupt return instruction [RETI] or [RETN]. Therefore, it is not necessary for a program to save the RBS.

Example: Register Bank Changeover

```

PINTxx : LD RBS, n ; Switches to bank n (1 \( \mu \)s at 8 MHz)

Interrupt processing

RETI ; Restores bank and Returns

```

Figure 1-24. Saving/Restoring General-purpose Registers

② General-purpose register save/restore using push and pop instructions:

To save only a specific register, and when the same interrupt source occurs more than once, the general-purpose registers can be saved/restored using push/pop instructions.

Example: Register save using push and pop instructions

PINTxx : PUSH WA ; Save WA register pair

PUSH HL; Save HL register pair

interrupt processing

POP HL; Restore HL register pair POP WA; Restore WA register pair

RETI ; Return

③ General-purpose registers save/restore using data transfer instructions: Data transfer instructions can be used to save only a specific general-purpose register during processing of a single interrupt.

Example : Saving/restoring a register using data transfer instructions

PINTxx : LD (GSAVA), A ; Save A register

interrupt processing

LD A, (GSAVA); Restore A register

RETI : Return

The interrupt return instructions [RETI] / [RETN] perform the following operations.

|   | [RETI] Maskable interrupt return                                                             |   | [RETN] Non-maskable interrupt return                                                                                                                                                                                              |

|---|----------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | The contents of the program counter and the program status word are restored from the stack. | 1 | The contents of the program counter and program status word are restored from the stack.                                                                                                                                          |

| 2 | The stack pointer is incremented 3 times.                                                    | 2 | The stack pointer is incremented 3 times.                                                                                                                                                                                         |

| 3 | The interrupt master enable flag is set to "1".                                              | 3 | The interrupt master enable flag is set to "1" only when a non-maskable interrupt is accepted in interrupt enable status. However, the interrupt master enable flag remains at "0" when so clear by an interrupt service program. |

Interrupt requests are sampled during the final cycle of the instruction being executed. Thus, the next interrupt can be accepted immediately after the interrupt return instruction is executed.

Note: When the interrupt processing time is longer than the interrupt request generation time, the interrupt service task is performed but not the main task.

# 1.9.2 Software interrupt (INTSW)

Executing the [SWI] instruction generates a software interrupt and immediately starts interrupt processing (INTSW is highest prioritized interrupt). However, if processing of a non-maskable interrupt is already underway, executing the SWI instruction will not generate a software interrupt but will result in the same operation as the [NOP] instruction. Thus, the [SWI] instruction behaves like the [NOP] instruction.

Note: At the development tool, if processing of a non-maskable interrupt is already underway, executing the SWI instruction will generate a software interrupt as a software brake.

Use the [SWI] instruction only for detection of the address error or for debugging.

Address Error Detection

$FF_H$  is read if for some cause such as noise the CPU attempts to fetch an instruction from a non-existent memory address. Code  $FF_H$  is the SWI instruction, so a software interrupt is generated and an address error is detected. The address error detection range can be further expanded by writing  $FF_H$  to unused areas of the program memory. the address trap reset is generated in case that an instruction is fetched from RAM or SFR areas.

Note: The fetch data from addresses  $7F80_H$  to  $7FFF_H$  (test ROM area) is not "FFH".

② Debugging

Debugging efficiency can be increased by placing the SWI instruction at the software break point setting address.

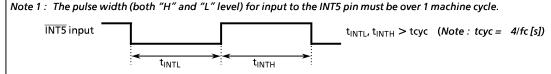

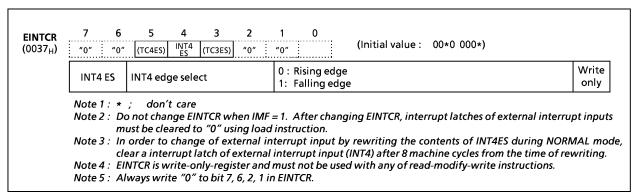

# 1.9.3 External interrupts

The 87CH36/K36/M36 has three external interrupt inputs (INT3, INT4, and INT5). Two of these are equipped with digital noise rejection circuits (pulse inputs of less than a certain time are eliminated as noise). Edge selection is also possible with INT3 and INT4.

Edge selection of INT4 pin input is performed by the external interrupt control register (EINTCR). Edge selection and noise rejection control for INT3 pin input are performed by the Remote-control signal processor control registers. (refer to the selection of the Remote-control signal processor.)

| Source | Pin  | Secondary<br>function pin | Enable conditions          | Edge                                                      | Digital noise reject                                                                                                     |

|--------|------|---------------------------|----------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| INT3   | INT3 | P30/RXIN                  | IMF · EF <sub>11</sub> = 1 | falling edge,<br>rising edge or<br>falling/rising<br>edge | Refer to the selection of the Remote control signal preprocessor.                                                        |

| INT4   | INT4 | P32                       | IMF · EF <sub>12</sub> = 1 | falling edge<br>or<br>rising edge                         | Pulses of less than 7/fc [s] are eliminated as noise. Pulses of equal to or more than 24/fc [s] are regarded as signals. |

| INT5   | ĪNT5 | P20/STOP                  | IMF • EF <sub>15</sub> = 1 | falling <sub>edge</sub>                                   | — (hysteresis input)                                                                                                     |

Table 1-3. External Interrupts

Note 2: If a noiseless signal is input to the external interrupt pin, the maximum time from the edge of input signal until the IL is set is as follows:

① INT4 pin 25/fc [s]

Note 3: When high-impedance is specified for port output in stop mode, port input is forcibly fixed to low level internally. Thus, interrupt latches of external interrupt inputs except P20 (INT5/STOP) which are also used as ports may be set to "1". To specify high-impedance for port output in stop mode, first disable interrupt service (IMF = 0), activate stop mode. After releasing stop mode, clear interrupt latches using load instruction, then, enable interrupt service.

Example : Activating stop mode (TMP87CH36/K36/M36) :

LD (SYSCR1), 01000000B ; OUTEN←0 (specifies high-impedance)

DI ; IMF←0 (disables interrupt service)

SET (SYSCR1).STOP ; STOP←1 (activates stop mode)

LDW (IL), 111001110101111B; IL12, 11, 7, 5, 3←0 (clears interrupt latches)

EI ; IMF←1 (enables interrupt service)

Figure 1-25. External Interrupt Control Register

# 1.10 Watchdog Timer (WDT)

The watchdog timer rapidly detects the CPU malfunction such as endless looping caused by noise or the like, and resumes the CPU to the normal state.

The watchdog timer signal for detecting malfunction can be selected either as a reset output or a non-maskable interrupt request. However, selection is possible only once after reset. At first, the reset output is selected.

When the watchdog timer is not being used for malfunction detection, it can be used as a timer to generate an interrupt at fixed intervals.

# 1.10.1 Watchdog timer configuration

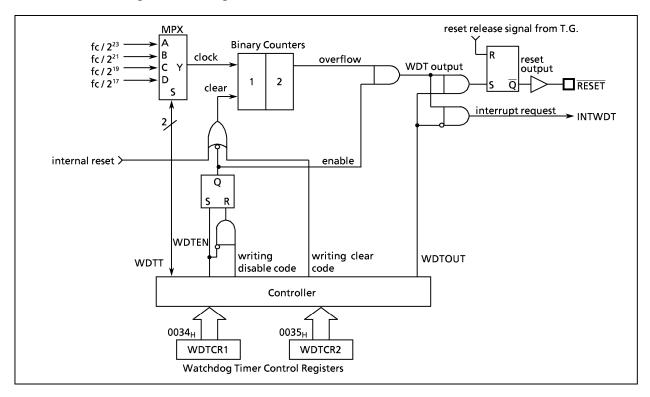

Figure 1-26. Watchdog Timer Configuration

# 1.10.2 Watchdog timer control

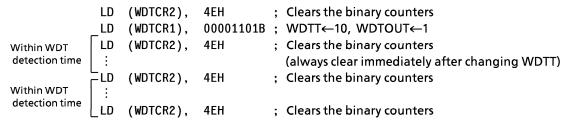

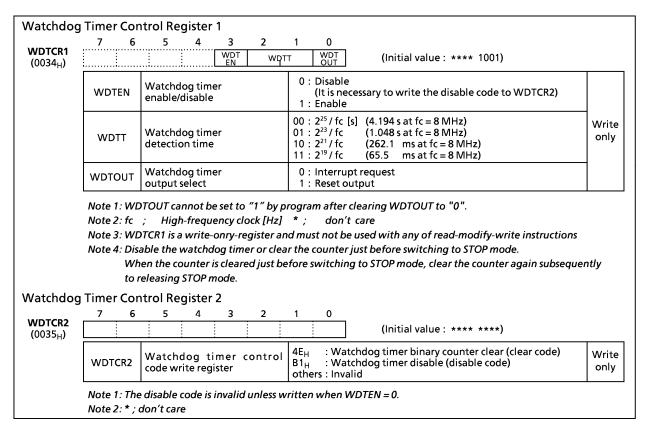

Figure 1-26 shows the watchdog timer control registers (WDTCR1, WDTCR2). The watchdog timer is automatically enabled after reset.

- (1) Malfunction detection methods using the watchdog timer The CPU malfunction is detected as follows:

- ① Setting the detection time, selecting output, and clearing the binary counter.

- ② Repeatedly clearing the binary counter within the setting detection time.

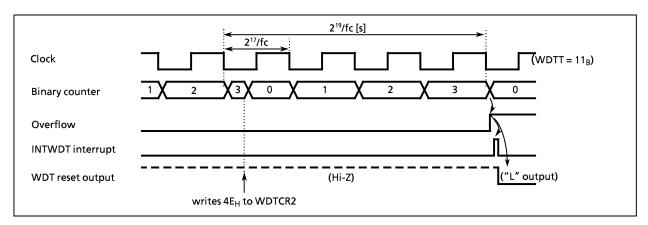

If a CPU malfunction occurs for any cause, the watchdog timer output will become active on the rise of an overflow from the binary counters unless the binary counters are cleared. At this time, when WDTOUT = 1 a reset is generated, which drives the RESET pin low to reset the internal hardware and the external circuits. When WDTOUT = 0, a watchdog timer interrupt (INTWDT) is generated.

The watchdog timer temporarily stops counting in STOP mode (including warm-up) or IDLE mode, and automatically restarts (continues counting) when STOP/IDLE mode is released.

Example: Sets the watchdog timer detection time to 221/fc [s] and resets the CPU malfunction.

Figure 1-27. Watchdog Timer Control Registers

2004-10-01

## (2) Watchdog Timer Enable

The watchdog timer is enabled by setting WDTEN (bit 3 in WDTCR1) to "1". WDTEN is initialized to "1" during reset, so the watchdog timer operates immediately after reset is released.

Example: Enables watchdog timer

LD (WDTCR1), 00001000B; WDTEN←1

#### (3) Watchdog Timer Disable

The watchdog timer is disabled by writing the disable code (B1<sub>H</sub>) to WDTCR2 after clearing WDTEN (bit 3 in WDTCR1) to "0". The watchdog timer is not disabled if this procedure is reversed and the disable code is written to WDTCR2 before WDTEN is cleared to "0". The watchdog timer is halted temporarily in STOP mode (including warm-up) and IDLE mode, and restarts automatically after STOP or IDLE mode is released.

During disabling the watchdog timer, the binary counters are cleared to "0".

Example: Disables watchdog timer

LDW (WDTCR1) , 0B101H ; WDTEN←0, WDTCR2←disable code

# 1.10.3 Watchdog timer interrupt (INTWDT)

This is a pseudo non-maskable interrupt which can be accepted regardless of the contents of the EIR. If a watchdog timer interrupt or a software interrupt is already accepted, however, the new watchdog timer interrupt waits until the previous non-maskable interrupt processing is completed (the end of the [RETN] instruction execution).

The stack pointer (SP) should be initialized before using the watchdog timer output as an interrupt source with WDTOUT.

Example: Watchdog timer interrupt setting up.

LD SP, 043FH; Sets the stack pointer

LD (WDTCR1), 00001000B; WDTOUT←0

#### 1.10.4 Watchdog timer reset

If the watchdog timer output becomes active, a reset is generated, which drives the  $\overline{\text{RESET}}$  pin (sink open drain output) low to reset the internal hardware and the external circuits. The reset output time is  $2^{20}$ /fc [s] (131 ms at fc = 8 MHz).

Figure 1-28. Watchdog Timer Interrupt / Reset

## 1.11 Reset Circuit

The TLCS-870 Series has four types of reset generation procedures: an external reset input, an address-trap-reset, a watchdog timer reset and a system-clock-reset. Table 1-4 shows on-chip hardware initialization by reset action. The internal source reset circuit (watchdog timer reset, address trap reset, and system clock reset) is not initialized when power is turned on. Thus, output from the RESET pin may go low (2<sup>20</sup>/fc [s.] 131msec at 8 MHz) when power is turned on.

| On-chip Hardware                                      |       | Initial Value                             | On-chip Hardware            | Initial Value                     |

|-------------------------------------------------------|-------|-------------------------------------------|-----------------------------|-----------------------------------|

| Program counter                                       | (PC)  | (FFFF <sub>H</sub> )·(FFFE <sub>H</sub> ) | Divider of Timing generator | 0                                 |

| Register bank selector                                | (RBS) | 0                                         |                             |                                   |

| Jump status flag                                      | (JF)  | 1                                         | Watchdog timer              | Enable                            |

| Interrupt master enable flag                          | (IMF) | 0                                         | Output latches of I/O ports | Refer to I/O port circuitry       |

| Interrupt individual enable flag<br>Interrupt latches | (IL)  | 0                                         | Control registers           | Refer to each of control register |

Table 1-4. Initializing Internal Status by Reset Action

## 1.11.1 External reset input

When the RESET pin is held at low for at least 3 machine cycles (12/fc [s]) with the power supply voltage within the operating voltage range and oscillation stable, a reset is applied and the internal state is initialized.

When the  $\overline{\text{RESET}}$  pin input goes high, the reset operation is released and the program execution starts at the vector address stored at addresses FFFEH to FFFFH.

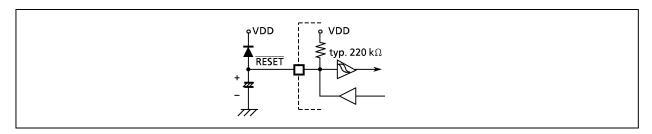

The RESET pin contains a Schmitt trigger (hysteresis) with an internal pull-up resistor. A simple power-on-reset can be applied by connecting an external capacitor and a diode.

Figure 1-29. Simple Power-on-Reset Circuitry

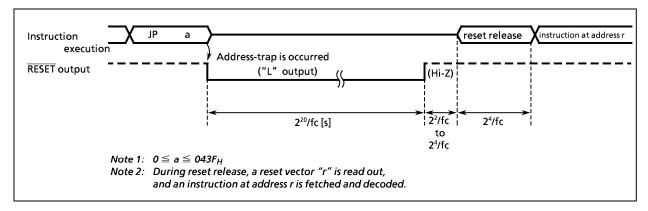

## 1.11.2 Address-trap-reset

If a CPU malfunction occurs and an attempt is made to fetch an instruction from the RAM or the SFR area (addresses  $0000_H$  to  $043F_H$ ), an address-trap-reset will be generated. Then, the  $\overline{\text{RESET}}$  pin output will go low. The reset time is  $2^{20}/\text{fc}$  [s] (131ms at fc = 8 MHz).

Figure 1-30. Address-Trap-Reset

## 1.11.3 Watchdog timer reset

Refer to Section "1.10 Watchdog Timer".

## 1.11.4 System-clock-reset

Clearing both bits 7 and 6 in SYSCR2 to "0" stops high-frequency oscillation, and causes the MCU to deadlock. This can be prevented by automatically generating a reset signal whenever (bit7 in SYSCR2) = (bit6 in SYSCR2) = 0 is detected to continue the oscillation. Then, the  $\overline{\text{RESET}}$  pin output goes low from high-impedance. The reset time is  $2^{20}/\text{fc}$  [s] (131 ms at fc = 8 MHz).

## 2. On-Chip Peripherals Functions

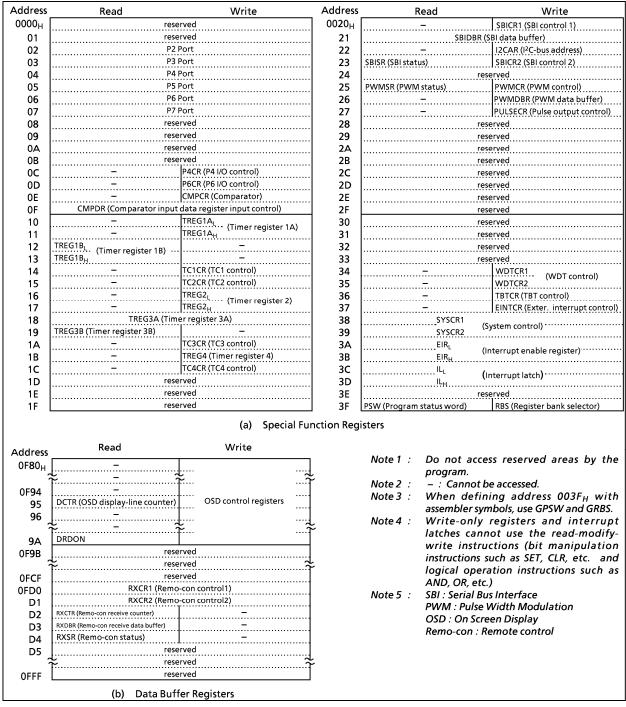

## 2.1 Special Function Registers (SFR) and Data Buffer Registers (DBR)

The TLCS-870 Series uses the memory mapped I/O system and all peripherals control and data transfers are performed through the special function registers (SFR) and data buffer registers (DBR). The SFR are mapped to addresses  $0000_{\rm H}$  to  $003F_{\rm H}$ , and the DBR to addresses  $0F80_{\rm H}$  to  $0FFF_{\rm H}$ . Figure 2-1 shows the list of the 87CH36/K36/M36 SFRs and DBRs.

Figure 2-1. SFR & DBR

### 2.2 **I/O Ports**

The 87CH36/K36/M36 has 6 parallel input/output ports (34pins) as follows:

|         | Primary Function | Secondary Functions                                                                                               |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------|

| Port P2 | 1-bit I/O port   | external interrupt input, and STOP mode release signal input                                                      |

| Port P3 | 7-bit I/O port   | external interrupt input, remote control signal input, timer/counter input, and serial bus interface input/output |

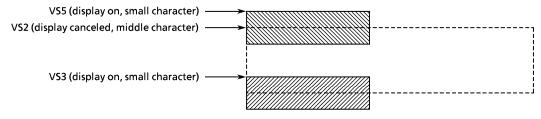

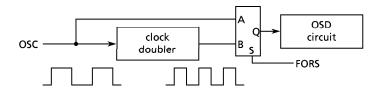

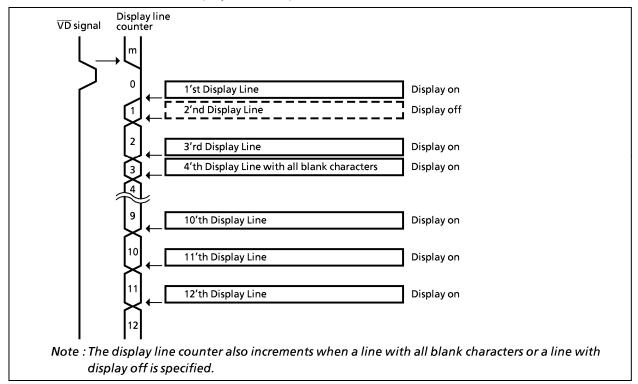

| Port P4 | 8-bit I/O port   | pulse width modulation output                                                                                     |