CIRRUS LOGIC®

**CL-PS6700***Preliminary Data Book*

## FEATURES

- Direct interface to CL-PS7111 low-power microcontroller

- Custom multiplexed address/data bus for low pin count

- Supports 13- and 18-MHz operating frequencies

- Fully compatible with PC Card (PCMCIA) Release 2.01 specification

- One or two CL-PS6700s per system

- Low power states

- Operating (25 mW, typical)

- Idle

- Standby (virtually zero power drain)

- Support for PC Card hot insertion and removal

- Read and write buffers

- Support for 3.3- and 5-V PC Cards

- Endian conversion

- Supports the following PC Cards:

- Memory-only card; flash, EPROM, or SRAM

- I/O card; modem and communications

- Cards configured as both I/O and memory

- DMA-capable cards (through software emulation)

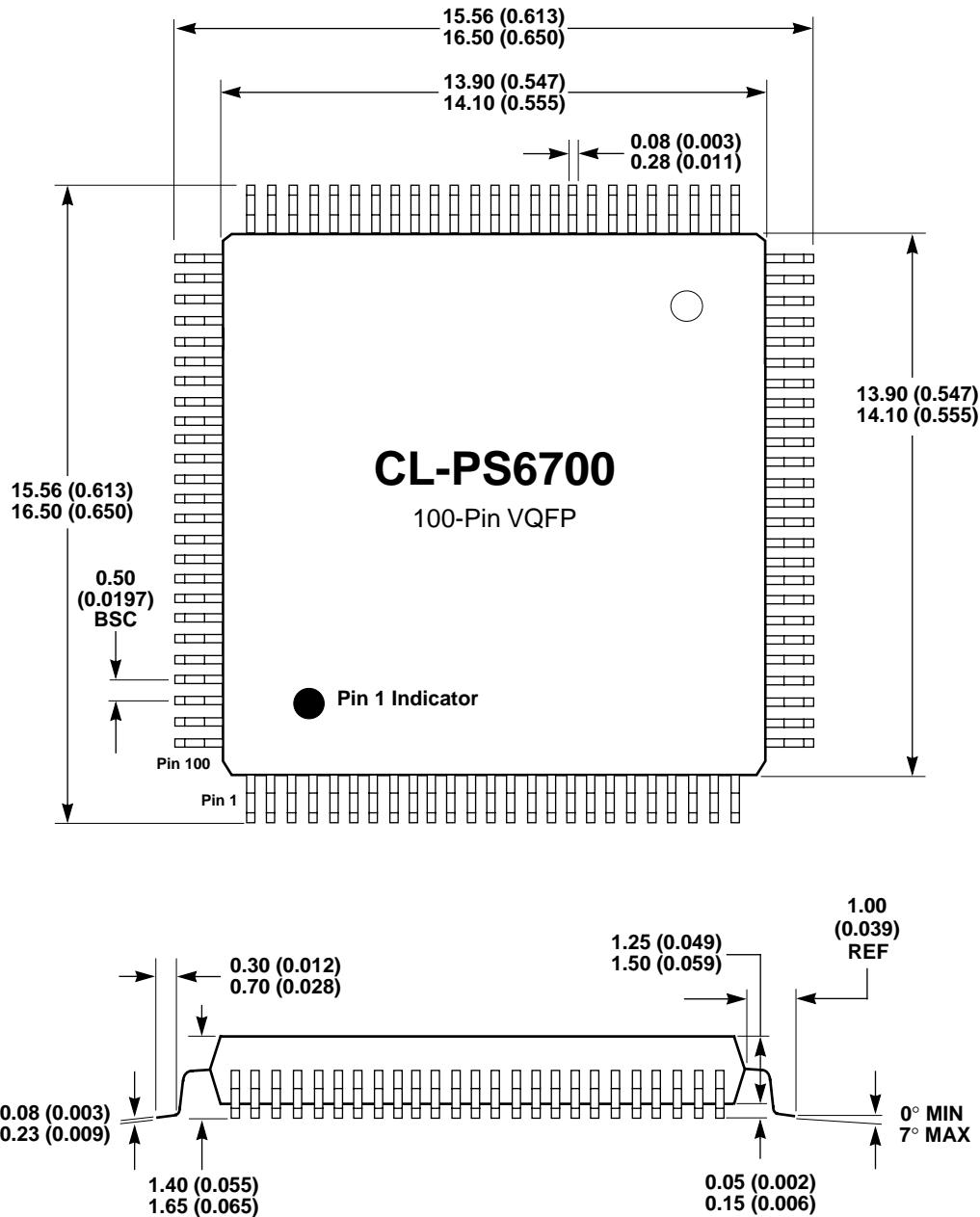

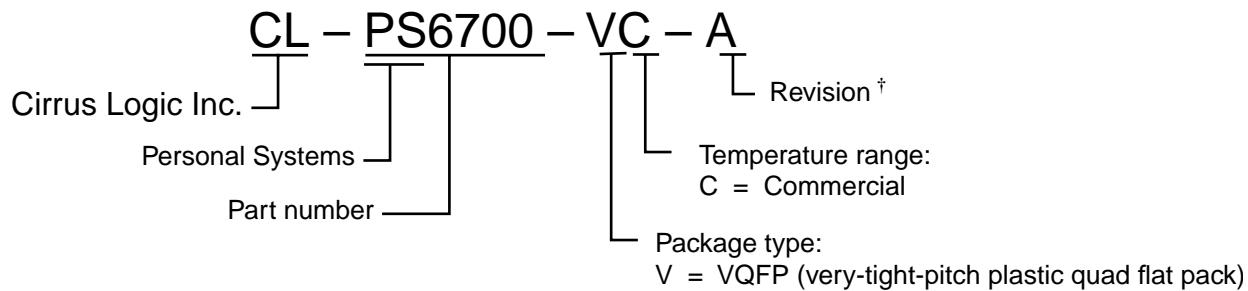

- 100-pin VQFP package

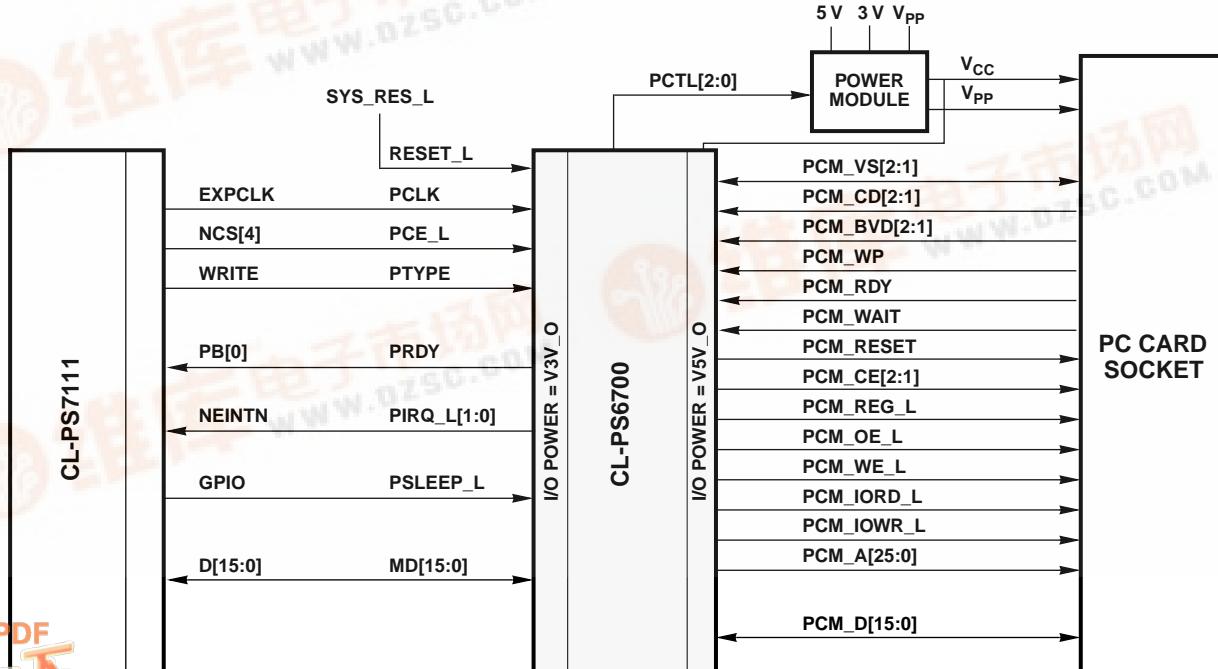

## CL-PS7111-to-CL-PS6700 Interface

## Low-Power PC Card Controller for the CL-PS7111

## OVERVIEW

The CL-PS6700 connects directly to a PC Card (PCMCIA) Release 2.01 socket and has a custom interface to the CL-PS7111 microcontroller. The CL-PS7111 can support up to two CL-PS6700 devices, which allows up to two PC Card sockets per system. Addresses and data are passed to the CL-PS6700 through 16 bits of the 32-bit Data bus (D[15:0]).

The PC Card socket is effectively isolated by the CL-PS6700. Except for power and ground pins, the pins on the socket only connect to the rest of the system through the CL-PS6700.

(cont.)

## OVERVIEW (cont.)

### **CL-PS7111-to-CL-PS6700 Interface**

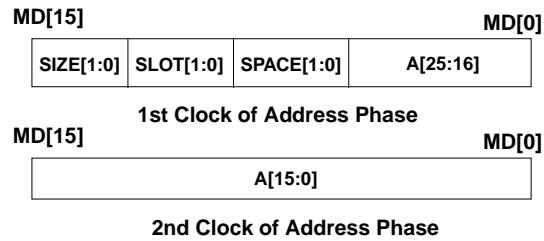

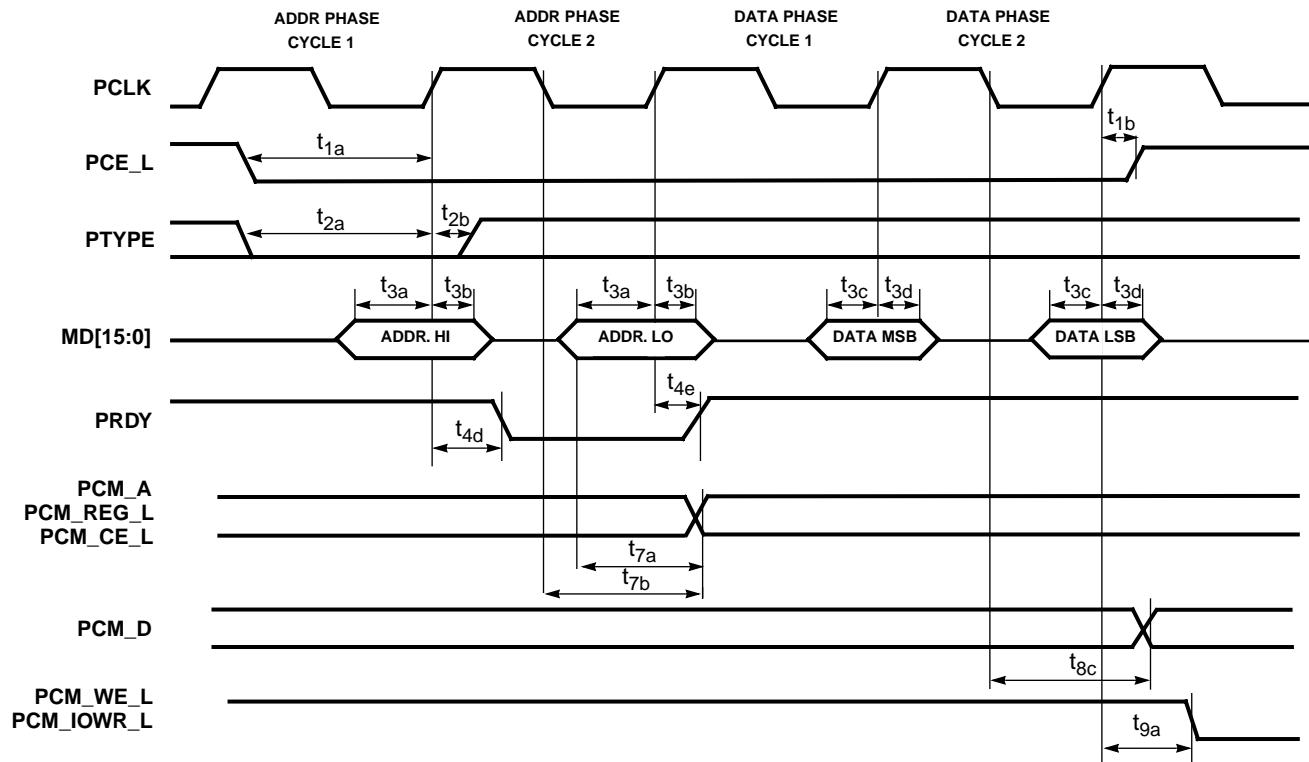

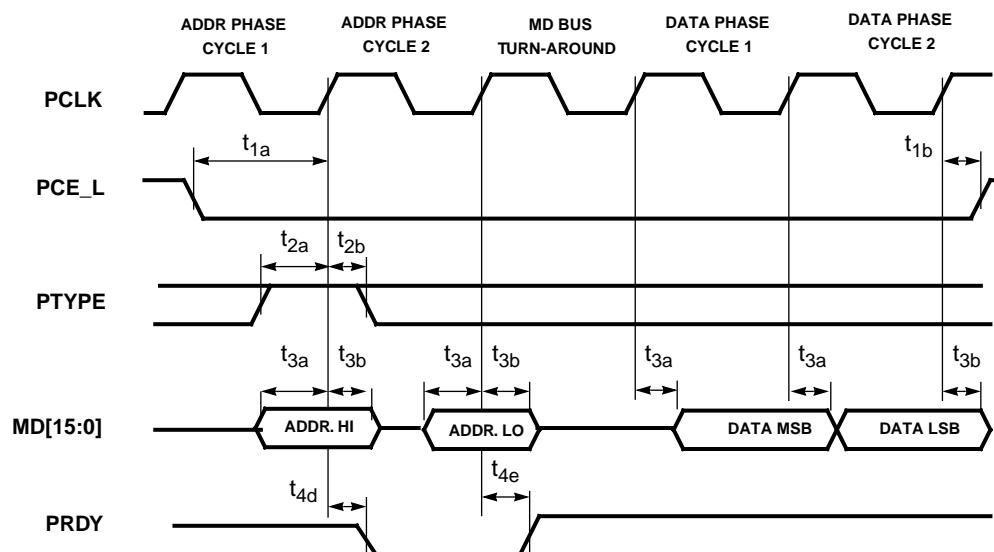

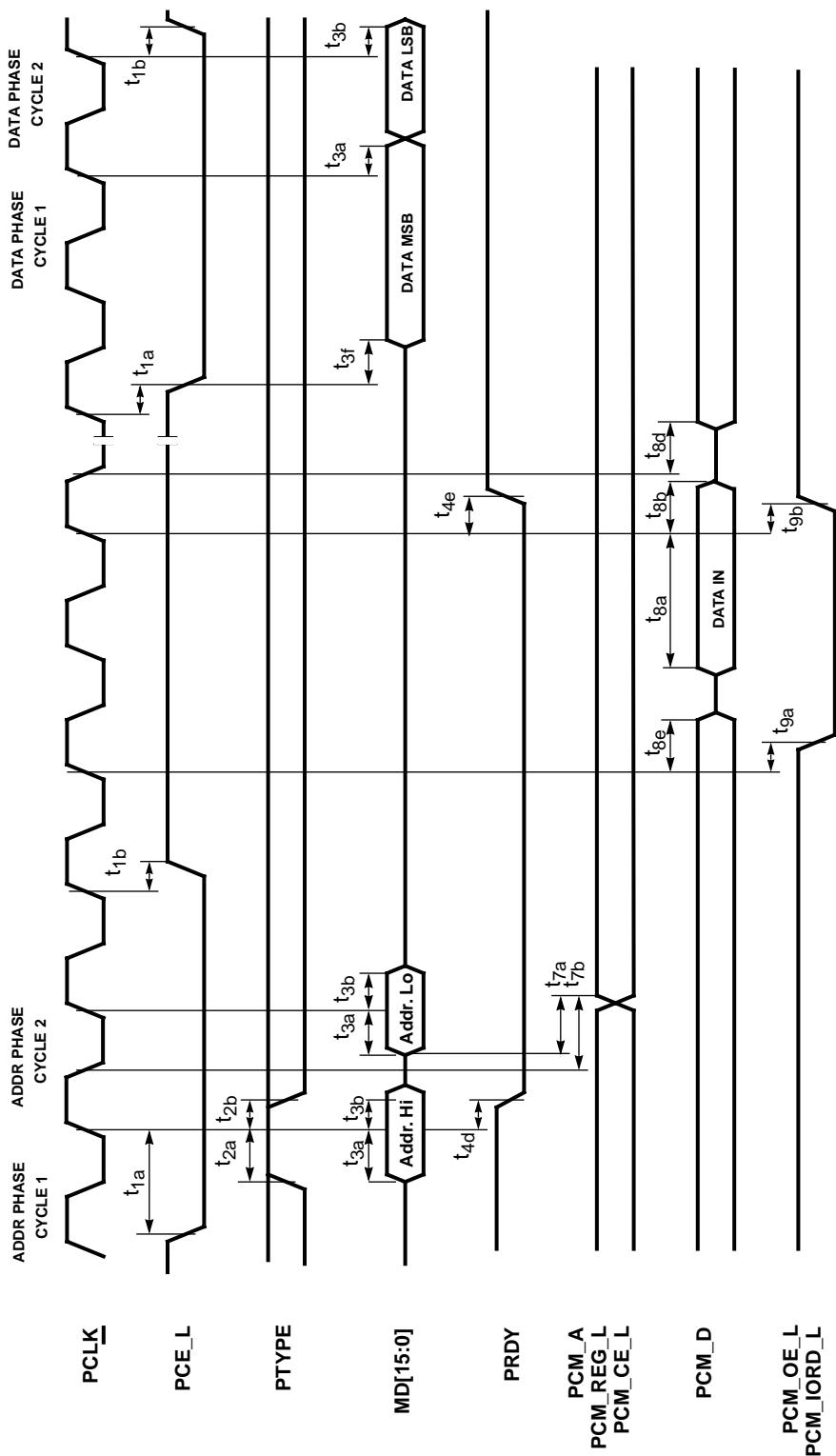

The PC Card interface requires a 26-bit address bus and a 16-bit data bus. The interface between the CL-PS6700 and CL-PS7111 consists of a 16-bit bus that carries the address and data information, and several control signals. This bus defines a two-clock address phase during which the 26-bit PC Card address and 6 control bits are transferred, and a one- or two-clock data phase during which one or four bytes of data are transferred. The data phase for reads can be deferred (for example, for a DMA access to the frame buffer of the CL-PS7111).

If a write transfer is indicated, write data appears in the third clock phase. If a word write is indicated, write data also appears in the fourth clock phase. For read transfers, the CL-PS6700 drives the bus with read data during the first one or two clocks of the data phase. This interface bus is also shared by other memory devices and up to one additional CL-PS6700 device.

The CL-PS7111 accesses the CL-PS6700 as a memory-mapped peripheral on the 16-bit memory bus. A Chip Enable signal (NCS[4]) from the CL-PS7111 selects one CL-PS6700 device for access to a particular PC Card socket. Another Chip Enable signal (NCS[5]) connects a second PC Card socket.

The CL-PS6700 implements the low-level interface to the PC Card socket and provides voltage translation for mixed-voltage systems. The CL-PS6700 also provides the data buffer and interrupt controls for the PC Card. Transfers between the two devices can be either one or four bytes.

The CL-PS6700 can be programmed to assemble/disassemble CL-PS7111 transfers to the width of the PC Card. The CL-PS6700 has read and write buffers that allow posting of both reads and writes. The read queue is single entry; the write FIFO can queue up to four CL-PS7111 transactions (up to 16 bytes).

### **Hot Insertion Support**

The CL-PS6700 PC Card controller allows PC Cards to be inserted or removed while system power is on. The CL-PS7111 controller typically applies power to a PC Card socket after it has detected a properly inserted card. The device removes the power before the card is removed (that is, when the CPU detects that the card lock is deasserted). Since each card is isolated from the system by the associated CL-PS6700, insertion and removal of cards do not cause interference on the system buses.

### **Card Configuration and Access**

After power-on or reset, a PC Card defaults to a memory-only card. The CL-PS7111 then reads the CIS of the card to determine the card type, access time, and so on, and configures the CL-PS6700 to access the card.

Each PC Card's  $V_{CC}$  and  $V_{PP}$  pins are individually controlled by its associated CL-PS6700. The CL-PS7111 controls the power to a card by writing to the CL-PS6700 registers. The CL-PS6700 ensures that its signals to the sockets are in the proper state before applying or removing power.

The CL-PS6700 device is available in an 100-pin VQFP package. The device can be used with both operating frequencies of the CL-PS7111 (13 and 18 MHz at 2.7 and 3.3 V).

## TABLE OF CONTENTS

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>CONVENTIONS .....</b>                                         | <b>5</b>  |

| <b>1. PIN INFORMATION.....</b>                                   | <b>7</b>  |

| 1.1 100-Pin VQFP Pin Diagram .....                               | 7         |

| 1.2 Pin Listings.....                                            | 8         |

| <b>2. PIN DESCRIPTIONS.....</b>                                  | <b>10</b> |

| 2.1 CL-PS7111-to-CL-PS6700 Interface Signals.....                | 10        |

| 2.1.1 Address/Data Bus Signals.....                              | 10        |

| 2.1.2 Access Control Signals.....                                | 12        |

| 2.1.3 Interrupt and Abort Signals.....                           | 13        |

| 2.1.4 Clock, Reset, and Sleep Signals .....                      | 13        |

| 2.2 PC Card Interface Signals.....                               | 14        |

| 2.2.1 Address and Data Signals .....                             | 14        |

| 2.2.2 Access Control Signals.....                                | 14        |

| 2.2.3 Additional Control for I/O Signals.....                    | 16        |

| 2.2.4 Card Detect and Battery Status Signals .....               | 16        |

| 2.2.5 Card Voltages and Reset Signals .....                      | 17        |

| 2.3 Power and Ground Pins .....                                  | 17        |

| <b>3. FUNCTIONAL DESCRIPTION.....</b>                            | <b>18</b> |

| 3.1 PC Card (PCMCIA) Interface .....                             | 18        |

| 3.1.1 PC Card Types.....                                         | 18        |

| 3.1.2 PC Card Address/Data Bus.....                              | 18        |

| 3.1.3 PC Card Address Spaces and DMA.....                        | 18        |

| 3.1.4 Byte Assembly/Disassembly and Queueing .....               | 19        |

| 3.1.5 Card Configuration.....                                    | 19        |

| 3.1.6 Hot Insertion Support .....                                | 19        |

| 3.2 Power States .....                                           | 20        |

| 3.2.1 Active State.....                                          | 20        |

| 3.2.2 Idle State.....                                            | 20        |

| 3.2.3 Standby State .....                                        | 20        |

| <b>4. REGISTERS.....</b>                                         | <b>21</b> |

| 4.1 Register Addresses.....                                      | 21        |

| 4.2 Interrupt Structure .....                                    | 23        |

| 4.3 Power Management Registers .....                             | 24        |

| 4.3.1 Power Management Register (0X0C002800) .....               | 24        |

| 4.3.2 Card Power Control Register (0X0C002C00) .....             | 25        |

| 4.4 System Interface Registers .....                             | 26        |

| 4.4.1 System Interface Configuration Register (0X0C002000) ..... | 26        |

| 4.4.2 DMA Control Register (0X0C004000) .....                    | 27        |

| 4.4.3 Device Information Register (0X0C004400) .....             | 27        |

| 4.5 Card Interface Registers .....                               | 28        |

| 4.5.1 Card Interface Configuration Register (0X0C002400) .....   | 28        |

| 4.5.2 Card Interface Timing Register 0A (0X0C003000) .....       | 29        |

| 4.5.3 Card Interface Timing Register 0B (0X0C003400) .....       | 29        |

| 4.5.4 Card Interface Timing Register 1A (0X0C003800) .....       | 30        |

| 4.5.5 Card Interface Timing Register 1B (0X0C003C00) .....       | 30        |

|                                          |           |

|------------------------------------------|-----------|

| 4.6 I/O Properties.....                  | 31        |

| <b>5. ELECTRICAL SPECIFICATIONS.....</b> | <b>33</b> |

| 5.1 Bus Timing — System Bus .....        | 35        |

| 5.2 Bus Operations .....                 | 38        |

| <b>6. PACKAGE SPECIFICATIONS .....</b>   | <b>43</b> |

| <b>7. ORDERING INFORMATION .....</b>     | <b>44</b> |

| <b>BIT INDEX.....</b>                    | <b>45</b> |

| <b>INDEX.....</b>                        | <b>46</b> |

## CONVENTIONS

This section presents conventions, abbreviations and acronyms, pin type abbreviations, and units of measure used in this data book.

### ***Abbreviations and Acronyms***

| Acronym or Abbreviation | Definition                              |

|-------------------------|-----------------------------------------|

| CIS                     | card information structure              |

| CMOS                    | complementary metal-oxide semiconductor |

| CPU                     | central processing unit                 |

| DC                      | direct current                          |

| DMA                     | direct-memory access                    |

| EPROM                   | erasable/programmable read-only memory  |

| FIFO                    | first in/first out                      |

| GPIO                    | general-purpose I/O                     |

| LSB                     | least-significant bit                   |

| MSB                     | most-significant bit                    |

| RAM                     | random-access memory                    |

| ROM                     | read-only memory                        |

| SRAM                    | static random-access memory             |

| VQFP                    | very-tight-pitch quad flat pack         |

### ***Pin Type Abbreviations***

| Abbreviation | Type              |

|--------------|-------------------|

| I            | Input             |

| O            | Output            |

| I/O          | Input/output      |

| OD-O         | Open-drain output |

### **Units of Measure**

| <b>Symbol</b> | <b>Units of Measure</b>          |

|---------------|----------------------------------|

| °C            | degree Celsius                   |

| Hz            | hertz (cycle per second)         |

| Kbyte         | kilobyte (1,024 bytes)           |

| kΩ            | kilohm                           |

| μA            | microampere                      |

| μs            | microsecond (1,000 nanoseconds)  |

| Mbyte         | megabyte (1,048,576 bytes)       |

| MHz           | megahertz (1,000 kilohertz)      |

| mA            | milliampere                      |

| ms            | millisecond (1,000 microseconds) |

| mW            | milliwatt                        |

| ns            | nanosecond                       |

| V             | volt                             |

| μW            | microwatt                        |

### **OTHER CONVENTIONS**

Hexadecimal numbers are presented with all letters in uppercase and a lowercase *h* appended. For example, *14h* and *03CAh* are hexadecimal numbers.

Binary numbers are enclosed in single quotation marks when in text. For example, '11' is a binary number.

Numbers not indicated by an *h* or single quotation marks are decimal.

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'n/c' indicates a pin that is a 'no connect'.

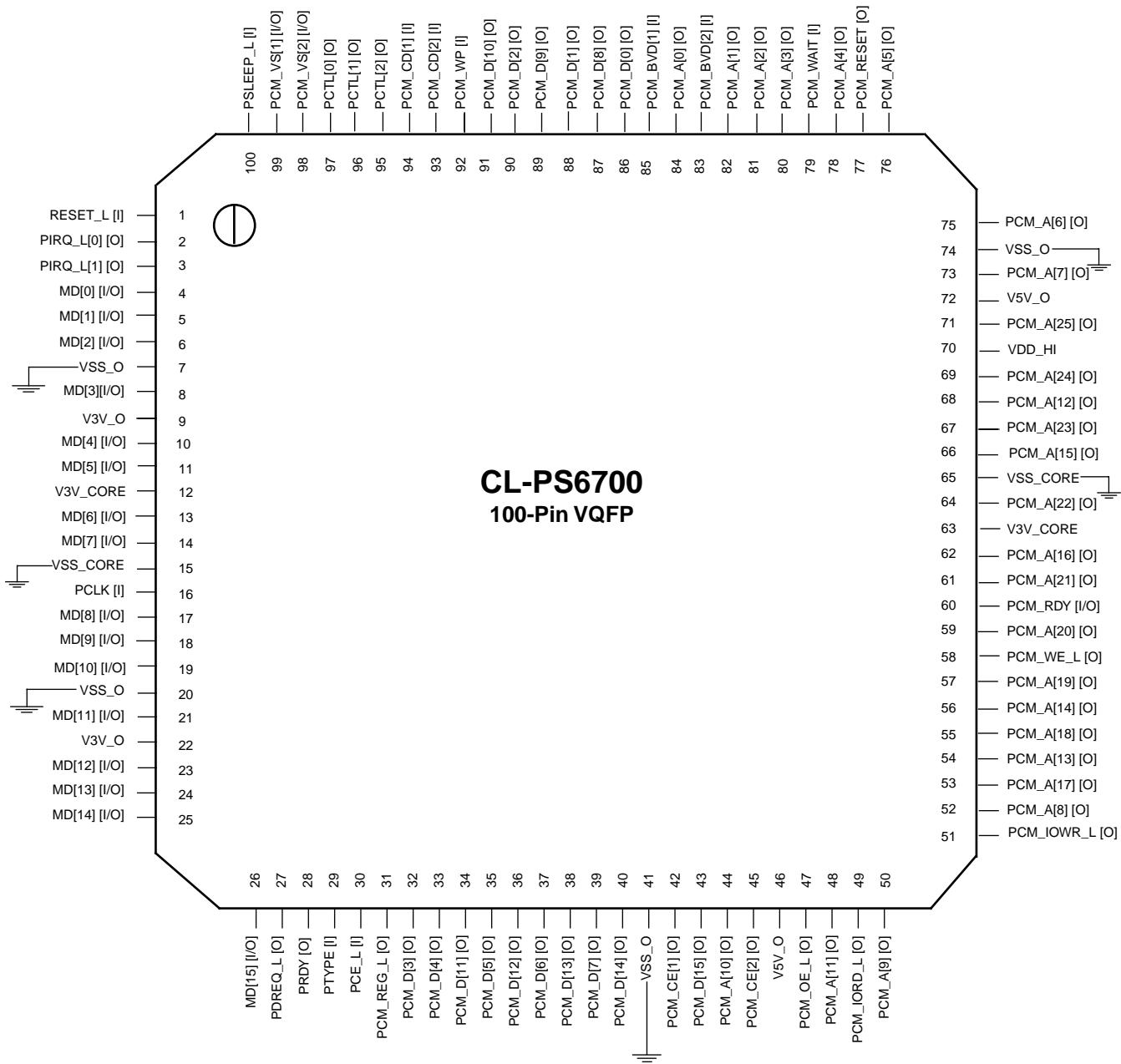

## 1. PIN INFORMATION

### 1.1 100-Pin VQFP Pin Diagram

## 1.2 Pin Listings

Table 1-1 lists the pins of the CL-PS6700 in alphabetical order. Table 1-2 lists the pins in numerical order.

**Table 1-1. Alphabetical Listing**

| Signal Name | Pin No. | Type |

|-------------|---------|------|-------------|---------|------|-------------|---------|------|-------------|---------|------|

| MD[0]       | 4       | I/O  | PCM_A[7]    | 73      | O    | PCM_D[0]    | 86      | O    | PCM_WE_L    | 58      | O    |

| MD[1]       | 5       | I/O  | PCM_A[8]    | 52      | O    | PCM_D[1]    | 88      | O    | PCM_WP      | 92      | I    |

| MD[2]       | 6       | I/O  | PCM_A[9]    | 50      | O    | PCM_D[2]    | 90      | O    | PCTL[0]     | 97      | O    |

| MD[3]       | 8       | I/O  | PCM_A[10]   | 44      | O    | PCM_D[3]    | 32      | O    | PCTL[1]     | 96      | O    |

| MD[4]       | 10      | I/O  | PCM_A[11]   | 48      | O    | PCM_D[4]    | 33      | O    | PCTL[2]     | 95      | O    |

| MD[5]       | 11      | I/O  | PCM_A[12]   | 68      | O    | PCM_D[5]    | 35      | O    | PDREQ_L     | 27      | O    |

| MD[6]       | 13      | I/O  | PCM_A[13]   | 54      | O    | PCM_D[6]    | 37      | O    | PIRQ_L[0]   | 2       | O    |

| MD[7]       | 14      | I/O  | PCM_A[14]   | 56      | O    | PCM_D[7]    | 39      | O    | PIRQ_L[1]   | 3       | O    |

| MD[8]       | 17      | I/O  | PCM_A[15]   | 66      | O    | PCM_D[8]    | 87      | O    | PRDY        | 28      | O    |

| MD[9]       | 18      | I/O  | PCM_A[16]   | 62      | O    | PCM_D[9]    | 89      | O    | PSLEEP_L    | 100     | I    |

| MD[10]      | 19      | I/O  | PCM_A[17]   | 53      | O    | PCM_D[10]   | 91      | O    | PTYPE       | 29      | I    |

| MD[11]      | 21      | I/O  | PCM_A[18]   | 55      | O    | PCM_D[11]   | 34      | O    | RESET_L     | 1       | I    |

| MD[12]      | 23      | I/O  | PCM_A[19]   | 57      | O    | PCM_D[12]   | 36      | O    | V3V_CORE    | 12      | -    |

| MD[13]      | 24      | I/O  | PCM_A[20]   | 59      | O    | PCM_D[13]   | 38      | O    | V3V_CORE    | 63      | -    |

| MD[14]      | 25      | I/O  | PCM_A[21]   | 61      | O    | PCM_D[14]   | 40      | O    | V3V_O       | 22      | -    |

| MD[15]      | 26      | I/O  | PCM_A[22]   | 64      | O    | PCM_D[15]   | 43      | O    | V3V_O       | 9       | -    |

| PCE_L       | 30      | I    | PCM_A[23]   | 67      | O    | PCM_IORD_L  | 49      | O    | V5V_O       | 46      | -    |

| PCLK        | 16      | I    | PCM_A[24]   | 69      | O    | PCM_IOWR_L  | 51      | O    | V5V_O       | 72      | -    |

| PCM_A[0]    | 84      | O    | PCM_A[25]   | 71      | O    | PCM_OE_L    | 47      | O    | VDD_HI      | 70      | -    |

| PCM_A[1]    | 82      | O    | PCM_BVD[1]  | 85      | I    | PCM_RDY     | 60      | I/O  | VSS_CORE    | 15      | -    |

| PCM_A[2]    | 81      | O    | PCM_BVD[2]  | 83      | I    | PCM_REG_L   | 31      | O    | VSS_CORE    | 65      | -    |

| PCM_A[3]    | 80      | O    | PCM_CD[1]   | 94      | I    | PCM_RESET   | 77      | O    | VSS_O       | 20      | -    |

| PCM_A[4]    | 78      | O    | PCM_CD[2]   | 93      | I    | PCM_VS[1]   | 99      | I/O  | VSS_O       | 41      | -    |

| PCM_A[5]    | 76      | O    | PCM_CE[1]   | 42      | O    | PCM_VS[2]   | 98      | I/O  | VSS_O       | 7       | -    |

| PCM_A[6]    | 75      | O    | PCM_CE[2]   | 45      | O    | PCM_WAIT    | 79      | I    | VSS_O       | 74      | -    |

**Table 1-2. Numerical Listing**

| Pin No. | Signal Name | Type |

|---------|-------------|------|---------|-------------|------|---------|-------------|------|---------|-------------|------|

| 1       | RESET_L     | I    | 26      | MD[15]      | I/O  | 51      | PCM_IOWR_L  | O    | 76      | PCM_A[5]    | O    |

| 2       | PIRQ_L[0]   | O    | 27      | PDREQ_L     | O    | 52      | PCM_A[8]    | O    | 77      | PCM_RESET   | O    |

| 3       | PIRQ_L[1]   | O    | 28      | PRDY        | O    | 53      | PCM_A[17]   | O    | 78      | PCM_A[4]    | O    |

| 4       | MD[0]       | I/O  | 29      | PTYPE       | I    | 54      | PCM_A[13]   | O    | 79      | PCM_WAIT    | I    |

| 5       | MD[1]       | I/O  | 30      | PCE_L       | I    | 55      | PCM_A[18]   | O    | 80      | PCM_A[3]    | O    |

| 6       | MD[2]       | I/O  | 31      | PCM_REG_L   | O    | 56      | PCM_A[14]   | O    | 81      | PCM_A[2]    | O    |

| 7       | VSS_O       | -    | 32      | PCM_D[3]    | O    | 57      | PCM_A[19]   | O    | 82      | PCM_A[1]    | O    |

| 8       | MD[3]       | I/O  | 33      | PCM_D[4]    | O    | 58      | PCM_WE_L    | O    | 83      | PCM_BVD[2]  | I    |

| 9       | V3V_O       | -    | 34      | PCM_D[11]   | O    | 59      | PCM_A[20]   | O    | 84      | PCM_A[0]    | O    |

| 10      | MD[4]       | I/O  | 35      | PCM_D[5]    | O    | 60      | PCM_RDY     | I/O  | 85      | PCM_BVD[1]  | I    |

| 11      | MD[5]       | I/O  | 36      | PCM_D[12]   | O    | 61      | PCM_A[21]   | O    | 86      | PCM_D[0]    | O    |

| 12      | V3V_CORE    | -    | 37      | PCM_D[6]    | O    | 62      | PCM_A[16]   | O    | 87      | PCM_D[8]    | O    |

| 13      | MD[6]       | I/O  | 38      | PCM_D[13]   | O    | 63      | V3V_CORE    | -    | 88      | PCM_D[1]    | O    |

| 14      | MD[7]       | I/O  | 39      | PCM_D[7]    | O    | 64      | PCM_A[22]   | O    | 89      | PCM_D[9]    | O    |

| 15      | VSS_CORE    | -    | 40      | PCM_D[14]   | O    | 65      | VSS_CORE    | -    | 90      | PCM_D[2]    | O    |

| 16      | PCLK        | I    | 41      | VSS_O       | -    | 66      | PCM_A[15]   | O    | 91      | PCM_D[10]   | O    |

| 17      | MD[8]       | I/O  | 42      | PCM_CE[1]   | O    | 67      | PCM_A[23]   | O    | 92      | PCM_WP      | I    |

| 18      | MD[9]       | I/O  | 43      | PCM_D[15]   | O    | 68      | PCM_A[12]   | O    | 93      | PCM_CD[2]   | I    |

| 19      | MD[10]      | I/O  | 44      | PCM_A[10]   | O    | 69      | PCM_A[24]   | O    | 94      | PCM_CD[1]   | I    |

| 20      | VSS_O       | -    | 45      | PCM_CE[2]   | O    | 70      | VDD_HI      | -    | 95      | PCTL[2]     | O    |

| 21      | MD[11]      | I/O  | 46      | V5V_O       | -    | 71      | PCM_A[25]   | O    | 96      | PCTL[1]     | O    |

| 22      | V3V_O       | -    | 47      | PCM_OE_L    | O    | 72      | V5V_O       | -    | 97      | PCTL[0]     | O    |

| 23      | MD[12]      | I/O  | 48      | PCM_A[11]   | O    | 73      | PCM_A[7]    | O    | 98      | PCM_VS[2]   | I/O  |

| 24      | MD[13]      | I/O  | 49      | PCM_IORD_L  | O    | 74      | VSS_O       | -    | 99      | PCM_VS[1]   | I/O  |

| 25      | MD[14]      | I/O  | 50      | PCM_A[9]    | O    | 75      | PCM_A[6]    | O    | 100     | PSLEEP_L    | I    |

## 2. PIN DESCRIPTIONS

### 2.1 CL-PS7111-to-CL-PS6700 Interface Signals

The conventions used for the power sources on the CL-PS7111-to-CL-PS6700 interface are listed in [Table 2-1](#).

**Table 2-1. Power Source Conventions<sup>a</sup>**

| Symbol | Power Source |

|--------|--------------|

| sys    | system       |

| pcm    | PCMCIA       |

| VDDhi  | VDDhi pin    |

<sup>a</sup> See [Section 2.3 on page 17](#) for details on power and ground pins.

#### 2.1.1 Address/Data Bus Signals

| Signal   | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD[15:0] | I/O  | sys          | <p><b>Multiplexed address and data bus:</b> The MD bus carries address information during a two-clock address phase and data during a one- or two-clock data phase.</p> <p><b>Address Phase:</b> A PC Card address is a 26-bit byte address. The MD bus carries the upper 10 address bits, plus control bits during the first clock of Chip Enable (PCE_L low), and the remaining (lower) 16 address bits during the second clock.</p> |

### 2.1.1 Address/Data Bus Signals (cont.)

| Signal   | Type | Power Source   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD[15:0] | I/O  | sys<br>(cont.) | <p><b>Data Phase:</b> If a write transfer is indicated (during the address phase), write data appears in the third clock (also a word write, during the fourth clock) of Chip Enable. For register read transfers, a two-clock data phase follows the two clocks of address phase after a one clock bus turnaround cycle. For card reads, the data phase is deferred until card data has been collected as signaled by PRDY; the data phase is initiated by a second assertion of PCE_L, and the CL-PS6700 drives this bus with read data in the clock following the assertion of PCE_L (if a word read, during the second clock following PCE_L).</p> <p>The data phase of MD[15:0] carries the transfer size and space required for the data (see <a href="#">Table 2-2</a> and <a href="#">Table 2-3</a>). SLOT[1:0] is a space reserved for future expansion.</p> |

**Table 2-2. Transfer Size**

| SIZE[1:0] | Number of bytes |

|-----------|-----------------|

| 00        | 1               |

| 11        | 4               |

**Table 2-3. Area Accessed**

| SPACE[1:0] | Area Accessed            |

|------------|--------------------------|

| 00         | Attribute space          |

| 01         | I/O space                |

| 10         | Common memory            |

| 11         | CL-PS6700 register space |

### 2.1.2 Access Control Signals

| Signal | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCE_L  | I    | sys          | <b>PC Card Chip Enable:</b> This signal, if asserted, enables the strobing of address and data information between the CL-PS7111 and the CL-PS6700 through the MD bus. For a read from PC Card memory or I/O space, the CL-PS7111 asserts PCE_L during the address phase and (possibly much later) during the data phase of a read transaction. Depending on the transaction, PCE_L is low for between two and five PCLK periods. When a read is pending, the CL-PS7111 waits for PRDY from the CL-PS6700 to complete the data phase. If the CL-PS6700 does not respond within a given time period, the CL-PS7111 times out and performs a dummy data phase by asserting PCE_L without receiving PRDY, causing the CL-PS6700 to abort the card read. If the CL-PS6700 times out card writes, it issues a WR_FAIL interrupt. |

| PTYPE  | I    | sys          | <b>PC Card Transaction Type:</b> During the first clock of PCE_L, this signal indicates whether the operation is a write or a read. A low level indicates a write and a high level indicates a read. During the second clock of the address phase, this signal indicates if the transaction was initiated by the CPU or an optional DMA controller. A low level indicates the DMA controller, and a high level indicates the CPU. If initiated by the DMA controller and the address targets the card's I/O space, a properly configured CL-PS6700 performs a DMA transfer at the card. This feature is not supported by the CL-PS7111 and is for future use only.                                                                                                                                                          |

**Table 2-4. PTYPE Signal Encoding During PCE\_L**

| PTYPE during Address Phase |                   | MD Bus Transfer Type                         |

|----------------------------|-------------------|----------------------------------------------|

| Cycle 1 (RD/WR)            | Cycle 2 (CPU/DMA) |                                              |

| 0                          | 0                 | Write operation initiated by DMA controller. |

| 0                          | 1                 | Write operation initiated by CPU.            |

| 1                          | 0                 | Read operation initiated by DMA controller.  |

| 1                          | 1                 | Read operation initiated by CPU.             |

|      |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRDY | I/O | sys | <p><b>NOTE:</b> PRDY should be pulled up with a 100-kΩ resistor.</p> <p><b>PC Card ready:</b> This signal goes to the CL-PS7111 and serves as both an address ready and data ready signal. It can also indicate a busy (card RDY/BUSY pin) status of the corresponding PC Card socket (see configuration bit “Include Card Ready in PRDY”). Normally, the CL-PS6700 leaves this signal asserted (high). When the CL-PS7111 targets a read or write transaction to the CL-PS6700, the CL-PS6700 deasserts PRDY in the second clock of the address phase until it has processed the transaction.</p> <p>For a <b>card write</b>, PRDY remains deasserted only if the write queue becomes full due to the current transaction. Otherwise, PRDY is reasserted during the next clock. When the CL-PS6700 write queue is full, PRDY is reasserted only after a queued write is disassembled (if necessary) and propagated to the PC Card socket, freeing an entry in the write queue. Therefore, the CL-PS7111 is assured that it does not get data wait states for card write operations.</p> <p>For a <b>card read</b>, the CL-PS6700 asserts PRDY when it has collected the required bytes from the PC Card. The CL-PS7111 then initiates the data phase by issuing a second PCE_L without driving the MD bus to the CL-PS6700(s). Then, the CL-PS6700 with a posted read responds with the read data.</p> <p>The CL-PS6700 registers can be read regardless of the state of PRDY. Therefore, PRDY cannot toggle during the address phase of register access if it is already deasserted. PRDY is a don't care input to the CL-PS7111 during the four (for write) or five (for read) clocks of register accesses.</p> |

|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### 2.1.2 Access Control Signals (cont.)

| Signal           | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDREQ_L/<br>GPIO | I/O  | sys          | <p><b>PC Card DMA Request:</b> When configured as PDREQ_L, this wire-OR'ed signal indicates to the CL-PS7111 that one of the PC Card sockets has issued a DMA request. Since this is shared by all PC Card sockets, the system should enable DMA to only one socket at a time and program the CL-PS7111 DMA routine.</p> <p><b>General-Purpose I/O:</b> When configured as GPIO, this signal can be used as an input capable of generating an interrupt. As a general-purpose output, it is actively driven in both output states, high and low.</p> |

### 2.1.3 Interrupt and Abort Signals

| Signal      | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIRQ_L[1:0] | OD-O | sys          | <p><b>PC Card Interrupt Request:</b> The interrupt request lines can be wire-OR'ed if there are two CL-PS6700 controllers. It signals that one or two CL-PS6700s have an interrupt pending. The exact source of pending interrupts can be read in a CL-PS6700 Interrupt Source register. External pull-up resistors for these signals are required. Alternatively, every interrupt request line can be connected to one of the CL-PS7111 active-low interrupt inputs.</p> |

### 2.1.4 Clock, Reset, and Sleep Signals

| Signal   | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK     | I    | sys          | All transfers between the CL-PS7111 and the CL-PS6700 are synchronous to this clock signal. To conserve power, PCLK can be disabled when the PC Card subsystem is not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET_L  | I    | sys          | This reset signal can be driven by one of the GPIO outputs of the CL-PS7111 or by a system reset. It is an active-low input and places all CL-PS6700 registers and outputs in their default power-up/reset condition.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

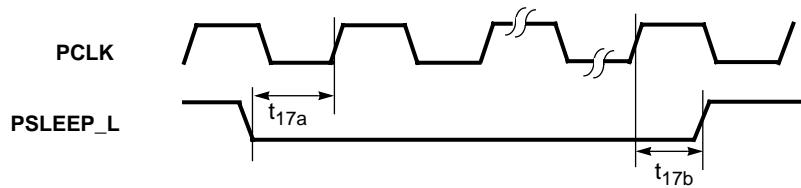

| PSLEEP_L | I    | sys          | The CL-PS7111 drives this signal either by the RUN output or by any GPIO. This active-low signal is synchronous to the rising edge of PCLK. PSLEEP_L causes the CL-PS6700 to complete or abort (as configured) any card operation in progress, enter the lowest power mode, and disable its I/O according to the <a href="#">Table 4-2 on page 32</a> . The CL-PS7111 can discontinue transactions to CL-PS6700 before asserting PSLEEP_L; if a card transaction in progress or in the queue is lost due to PSLEEP_L being asserted, an interrupt (RD_FAIL or WR_FAIL) is generated. There must be two PCLKs after PSLEEP_L is asserted to go into Standby mode. |

## 2.2 PC Card Interface Signals

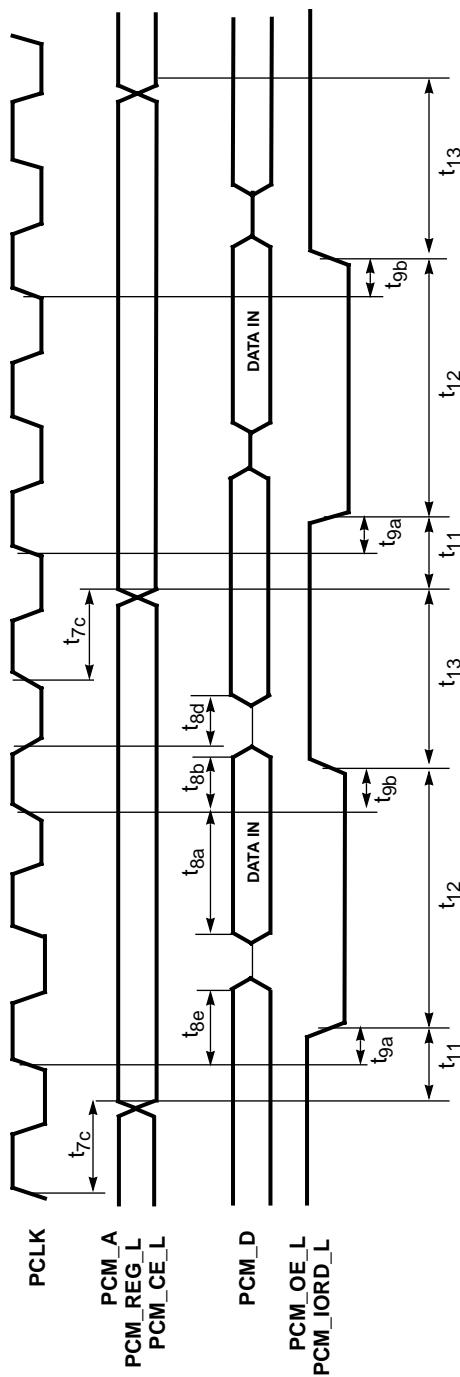

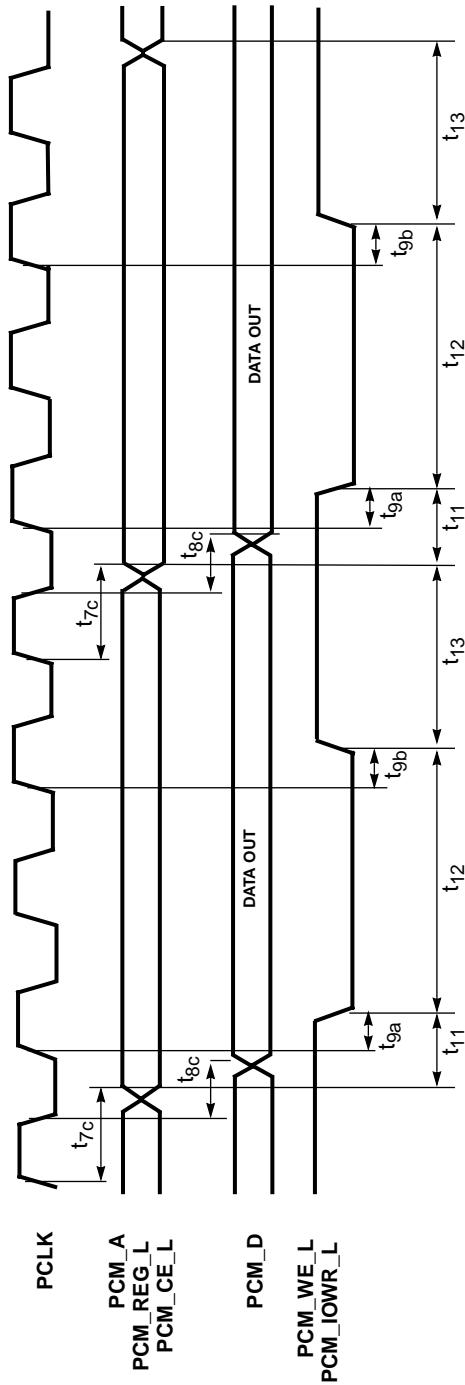

A PC Card socket can be configured as either *memory only* or *combined I/O-memory*. Some pins on the PC Card interface have different meanings in memory and I/O modes. These pins are listed as dual-mode. The mode is selected by a configuration register bit. When I/O mode is programmed, the CPU accesses either I/O space or memory space on the card according to the upper address bits. The CPU Attribute memory is accessible in either memory or I/O modes, again, selected by the upper address bits. A card DMA device is accessible only in I/O mode.

### 2.2.1 Address and Data Signals

| Signal      | Type | Power Source | Description                                                                                                                                                                                                                                            |

|-------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM_D[15:0] | I/O  | pcm          | <b>PC Card data bus:</b> Single-mode. Data transfer can be either byte or half-word (16-bit) as configured by the CPU. All byte accesses are transferred through their natural byte lane only (odd bytes on PCM_D[15:8] and even bytes on PCM_D[7:0]). |

| PCM_A[25:0] | O    | pcm          | <b>PC Card address bus:</b> Single-mode. This is a byte address during byte operations and a half-word address during half-word (16-bit) accesses (that is, A[0] is kept low).                                                                         |

### 2.2.2 Access Control Signals

| Signal        | Type | Power Source | Description                                                                                                                                                                                                                                                                                                 |

|---------------|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM_CE_L[2:1] | O    | pcm          | <b>Card enables:</b> Single-mode. These are the byte enable lines for the data bus. PCM_CE_L[1] enables even bytes, D[7:0], and PCM_CE_L[2] enables odd bytes, D[15:8].                                                                                                                                     |

| PCM_OE_L      | O    | pcm          | <b>Output enable for memory read data.</b> Single-mode. PCM_OE_L enables the card's data outputs. During a write operation, this signal is deasserted (high). During a card read DMA transfer, this signal is used as a terminal count and is asserted along with PCM_IORD_L during the last DMA card read. |

| PCM_WE_L      | O    | pcm          | <b>Write enable signal for common memory and DMA:</b> Single-mode. During a card write DMA transfer, this signal is used as a terminal count and is asserted along with PCM_IOWR_L during the last DMA card write.                                                                                          |

## 2.2.2 Access Control Signals (cont.)

| Signal                                 | Type                 | Power Source             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

|----------------------------------------|----------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|--------------------------|-----------|--------------------------|-------------|------------|------------|-----------------------------|-------------|------------|----------|---------------------|------------|-------------|----------|---------------------|----------------|-------------|------------|

| PCM_REG_L                              | O                    | pcm                      | <p>Single-mode. This signal, in conjunction with the card data strobes, PCM_OE_L, PCM_WE_L, PCM_IORD_L, and PCM_IOWR_L, determine which of the three address spaces (I/O, common memory, or attribute memory) is chosen and if the transfer is a DMA or non-DMA type.</p> <p>1 – common memory or DMA access<br/>           0 – I/O space or attribute memory space access</p>                                                                                                                                                                                                                                                                                                                           |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| <b>Table 2-5. PC Card Access Types</b> |                      |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

|                                        |                      |                          | <table border="1"> <thead> <tr> <th>Card Access Type</th><th>PCM_OE_L<br/>PCM_WE_L</th><th>PCM_IORD_L<br/>PCM_IOWR_L</th><th>PCM_REG_L</th></tr> </thead> <tbody> <tr> <td>Common Memory Read/Write</td><td>Data strobe</td><td>Deasserted</td><td>Deasserted</td></tr> <tr> <td>Attribute Memory Read/Write</td><td>Data strobe</td><td>Deasserted</td><td>Asserted</td></tr> <tr> <td>Card I/O Read/Write</td><td>Deasserted</td><td>Data strobe</td><td>Asserted</td></tr> <tr> <td>Card DMA Read/Write</td><td>Terminal count</td><td>Data strobe</td><td>Deasserted</td></tr> </tbody> </table>                                                                                                     | Card Access Type | PCM_OE_L<br>PCM_WE_L | PCM_IORD_L<br>PCM_IOWR_L | PCM_REG_L | Common Memory Read/Write | Data strobe | Deasserted | Deasserted | Attribute Memory Read/Write | Data strobe | Deasserted | Asserted | Card I/O Read/Write | Deasserted | Data strobe | Asserted | Card DMA Read/Write | Terminal count | Data strobe | Deasserted |

| Card Access Type                       | PCM_OE_L<br>PCM_WE_L | PCM_IORD_L<br>PCM_IOWR_L | PCM_REG_L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| Common Memory Read/Write               | Data strobe          | Deasserted               | Deasserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| Attribute Memory Read/Write            | Data strobe          | Deasserted               | Asserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| Card I/O Read/Write                    | Deasserted           | Data strobe              | Asserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| Card DMA Read/Write                    | Terminal count       | Data strobe              | Deasserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| PCM_WP                                 | I                    | pcm                      | <p>Dual-mode.</p> <p><b>Memory Mode:</b> This signal indicates that the card has been set to be write-protected.</p> <p><b>I/O Mode:</b> This signal becomes IOIS16_L. An asserted level (low) indicates that the I/O card is a 16-bit device. If IOIS16_L is not asserted (high), the device is assumed to be 8-bit, and data transfer occurs over byte lane D[7:0]. In this mode, the WP status of the card is available as an on-card register bit.</p> <p><b>DMA Mode:</b> This signal can be selected as DREQ from the PC Card.</p>                                                                                                                                                                 |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| PCM_WAIT_L                             | I                    | pcm                      | <p>Single-mode. This data wait signal is used by the card to delay completion of an in-progress memory or I/O access cycle. It is sampled by the CL-PS6700 with a flip-flop clocked on the rising edge of PCLK, then fed to the card interface logic. In order to be recognized, this signal must be asserted at least two clocks before the end of the command strobe.</p>                                                                                                                                                                                                                                                                                                                              |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

| PCM_RDY                                | I                    | pcm                      | <p>Dual-mode.</p> <p><b>Memory Mode:</b> This signal is deasserted while the card is busy processing a previous transfer. It is intended to signal the completion of potentially lengthy operations within the card. This signal is available as a status bit for polling by the CPU, and can generate an interrupt to the CPU. It can also form the PRDY signal to the CL-PS7111 for handshake, preventing masters from targeting a busy card.</p> <p><b>I/O Mode:</b> This signal is IREQ_L, an interrupt request generated by the I/O card. The RDY function of memory mode is available as an on-card register bit.</p> <p><b>DMA Mode:</b> This input can be selected as DREQ from the PC Card.</p> |                  |                      |                          |           |                          |             |            |            |                             |             |            |          |                     |            |             |          |                     |                |             |            |

### 2.2.3 Additional Control for I/O Signals

| Signal     | Type | Power Source | Description                                                                                                                                                                                                                                                                                   |

|------------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM_IORD_L | O    | pcm          | Single-mode.<br>Dual-mode.                                                                                                                                                                                                                                                                    |

| PCM_IOWR_L |      |              | <b>Memory Mode:</b> These signals remain deasserted.<br><b>I/O Mode:</b> These signals are asserted during read (PCM_IORD_L) and write transfer (PCM_IOWR_L) to the card I/O space or DMA devices. A PC Card does not respond to these signals unless it is configured for I/O by the system. |

| <hr/>      |      |              |                                                                                                                                                                                                                                                                                               |

| <hr/>      |      |              |                                                                                                                                                                                                                                                                                               |

### 2.2.4 Card Detect and Battery Status Signals

| Signal        | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM_CD_L[2:1] | I    | VDDhi        | 00 – Card inserted<br>01 – Card partially inserted<br>10 – Card partially inserted<br>11 – Card not inserted<br><br>Single-mode. These pins indicate whether a card has been inserted into a socket. They are positioned at opposite ends of the connector to ensure valid detection of card insertion; a properly inserted card pulls both lines <i>low</i> . They are pulled up to VDDhi within the CL-PS6700 until a card is inserted (which pulls them <i>low</i> ). These signals are available as status bits in a register, and any state change can also cause an interrupt informing the system that a card has been inserted or removed. |

| <hr/>         |      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCM_BVD[2:1]  | I    | pcm          | Dual-mode.<br><br><b>Memory Mode:</b> These bits indicate the card battery condition as outlined in <a href="#">Table 2-6</a> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

**Table 2-6. PC Card Battery Voltage Detect Encoding**

| PCM_BVD[2:1] | Battery Condition |

|--------------|-------------------|

| X0           | Battery dead      |

| 01           | Battery low       |

| 11           | Battery OK        |

**I/O Mode:** PCM\_BVD[2] becomes SPKR\_L, the Audio Digital Waveform signal, while PCM\_BVD[1] becomes the STSCHG\_L signal, a status line that indicates state changes of BVD, CD, and WP. The state of the BVD inputs can be read by the CPU in the CL-PS6700 Status registers and are also available on the PC Card registers.

### 2.2.5 Card Voltages and Reset Signals

| Signal      | Type | Power Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM_VS[2:1] | I/O  | VDDhi        | <p>Single-mode. These signals inform the host system of the voltage requirements and capabilities of the card for reading its CIS before applying power to the card. This allows 3.3-V only cards (which need not support 5-V operation during configuration). VS[2] primarily differentiates between 3.3- and 5-V cards, while VS[1] primarily differentiates between 3.3-V and X.X-V cards.</p> <p>These signals, and the three power control signals, are bidirectional signals under software control (register bits) for flexibility. All five signals are capable of generating interrupts. VS[2] can also be configured to act as the card DREQ input.</p>                 |

| PCTL[2:0]   | I/O  | VDDhi        | <p>Single-mode. These GPIO signals typically control the corresponding card's power module or switch. They determine the proper voltage for the <math>V_{CC}</math> and/or the <math>V_{PP}</math> pins of the socket. These signals are directly controlled by register bits and thus, can control serially-controlled power modules. They can also be programmed to transition to a new value automatically when the PSLEEP_L input is asserted to automatically shut down card power in case of power fault conditions. PCTL[2:0] are inputs during reset and therefore require an external pull-down or pull-up resistor to avoid power being applied to the card socket.</p> |

| PCM_RESET   | O    | pcm          | <p>Single-mode. This signal resets the PC Card, placing it into its default memory-only mode. The signal remains in a high-impedance state after power-on or system reset. Cards that implement the reset function pull up this signal with <math>&gt;100\text{ k}\Omega</math>. The CPU (after <math>&gt;1\text{ ms}</math>) should pull this signal low by writing a '0' to bit 12 of the Card Interface Configuration register.</p>                                                                                                                                                                                                                                            |

### 2.3 Power and Ground Pins

| Signal   | Group | Description                                                                                                               |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------|

| V3V_Core | core  | Power to core logic; either 5 V or 3.3 V.                                                                                 |

| V3V_O    | sys   | Power to system interface I/O buffers; either 5 V or 3.3 V, but must be the same as the CL-PS7111 power plane (V3V_Core). |

| V5V_O    | pcm   | Power to PC Card interface I/O buffers; either 5 V, 3.3 V, or 0 V.                                                        |

| VDD_HI   | VDDhi | This pin should be tied to the highest voltage in the system (as seen by CL-PS6700; either 5 V or 3.3 V).                 |

| VSS_Core |       | Ground pins for the core and input buffers.                                                                               |

| VSS_O    |       | Ground pins for output buffers.                                                                                           |

## 3. FUNCTIONAL DESCRIPTION

The CL-PS7111 communicates with the CL-PS6700 through the memory bus. This bus has a special multiplexed mode that uses 16 bits of the data bus to transfer address and data messages to the CL-PS6700. This split transaction bus supports posting a (single) read transaction so that the potentially long access time of a PC Card does not disrupt the memory bus. The protocol defines two clocks to transmit address messages, and one or two clocks for data messages. This allows efficient transfer of 32-bit words, as well as bytes and half words.

### 3.1 PC Card (PCMCIA) Interface

#### 3.1.1 PC Card Types

The supported PC Card v2.01 card types are:

- Memory-only card, such as flash or SRAM

- I/O card, such as a modem card

- Multifunction cards with both I/O and memory

- DMA-capable cards

Each card can be 3.3 V or 5 V, and power to each card is managed independently by the CL-PS7111 and the corresponding CL-PS6700. General-purpose digital I/O (PCM\_VS pins on the CL-PS6700) can be used by the CPU to detect the voltage requirements of a card before applying power.

#### 3.1.2 PC Card Address/Data Bus

The PC Card supports a 26-bit address bus and a 16-bit data bus. The CL-PS7111 multiplexes these buses into a single 16-bit bus MD[15:0]. This bus is demultiplexed by the CL-PS6700, which also implements the low-level interface to the PC Card and provides voltage translation for mixed-voltage systems. The CL-PS6700 also provides data buffering, endian conversion, and interrupt control for the PC Card. Transfers between the CL-PS7111 and the CL-PS6700 are one or four bytes.

The CL-PS7111 accesses the CL-PS6700 as a memory-mapped peripheral on the memory bus. A chip enable signal, PCE\_L of CL-PS6700, is connected to CS[4] (and CS[5] for a second PC Card socket) from the CL-PS7111.

#### 3.1.3 PC Card Address Spaces and DMA

The PC Card standard defines three address spaces for PC Cards: memory space, I/O space, and attribute space. Each of these is 64 Mbytes, requiring 26 address bits, while other command bits select the space to be accessed.

Attribute memory space contains setup information such as the CIS. Attribute memory is accessed as an 8-bit device, but only at half-word boundaries (even bytes only).

Memory and I/O space for a card can each be 8 or 16 bits in width. The width of the access made to each of these spaces by the CL-PS6700 is software configurable. In addition, I/O space accesses can be sized dynamically by the PCM\_WP (IOIS16\_L) input.

All three address spaces for each card are mapped into the CL-PS7111 memory map and are directly accessible by the CPU. In addition to these three address spaces, a card can contain a DMA target. The

CL-PS7111 does not implement a DMA controller for the PC Card, but the CPU can emulate DMA cycles by appropriately configuring the CL-PS6700, then accessing card I/O space (see [Table 4.4.2 on page 27](#)). In this case, the CL-PS6700 accesses the card using a newly defined DMA cycle (IORD/WR strobes used with -REG high).

The PC Card standard requires all cards to follow the little-endian memory model. The CL-PS7111 can support both the little-endian and big-endian modes of operation. Thus, the CL-PS6700 provides for endian conversion, which is software configurable.

### **3.1.4 Byte Assembly/Disassembly and Queueing**

Since all spaces on the cards (even I/O cards) are memory mapped, the CL-PS7111 can access the cards directly. The CL-PS6700 can be programmed to assemble/disassemble the CL-PS7111 transfers to the width of the PC Card. The CL-PS6700 has read and write buffers, allowing posting of both reads and writes. The read queue is single entry, and the write FIFO can queue up to four CL-PS7111 transactions (up to 16 bytes). Reads do not bypass queued writes (card transactions are processed in order).

Certain card access timing parameters are programmable and can be set to operate faster than the PC Card specification allows. The CL-PS6700 contains a watchdog timer that ensures that a card access is aborted if it exceeds a preprogrammed time limit, generating an interrupt to the CL-PS7111.

### **3.1.5 Card Configuration**

After power-on or reset, a PC Card defaults to a memory-only card. The CPU then reads the card's CIS to determine the card type, access time, and so on, configuring the CL-PS6700 to properly access the card.

Each PC Card's  $V_{CC}$  and  $V_{PP}$  pins are individually controlled by its corresponding CL-PS6700 pins. The CL-PS7111 controls the power to a card by writing to the CL-PS6700 registers. The CL-PS6700 ensures that its signals to the sockets are in the proper state before applying and removing power to the sockets.

### **3.1.6 Hot Insertion Support**

PC Cards are often used like floppies: The user can insert or remove cards while system power is on. Typically, the CPU only applies power to a PC Card socket after it has detected a properly inserted card and removes the power before the card is removed (that is, when the CPU detects that card lock is deasserted). Since each card is isolated from the system by its CL-PS6700, insertion and removal of cards should not cause glitches on the system buses.

## 3.2 Power States

### 3.2.1 Active State

The Active State is the normal operating state entered whenever PC Card accesses are required. In this state the PCLK input is active, the PSLEEP\_L input is deasserted, and the Idle bit in the Power Management register is cleared.

### 3.2.2 Idle State

Normally, Idle State is entered/exited dynamically in hardware (by CL-PS6700 control logic) transparent to software. This method is invoked by setting the Enable Auto Idle Mode bit in the Power Management register, and appears identical to the Active State, except that some internal clocks are gated off between transactions to conserve power. The software can enter Idle State explicitly by setting the Idle mode. In this case, access to the CL-PS6700 registers is supported, but PC Card accesses do not propagate to the card and a read fail or write fail event can occur, which can generate an interrupt to the host.

### 3.2.3 Standby State

Standby State is the lowest power state in the system and is entered by asserting the PSLEEP\_L input. At least two (rising) clock edges are required after PSLEEP\_L is asserted before the PCLK is shut off. In the Standby State the CL-PS6700 core and system interface power can remain on, but consumes near zero power (microwatts). If card transactions are queued in the CL-PS6700 when PSLEEP\_L is asserted, they are either aborted or continue until finished (requiring more than two clocks), depending on the setting of bit 9 (Standby Request During Card Access) in the Power Management register.

## 4. REGISTERS

The CL-PS6700 registers are spaced at 1-Kbyte boundaries and must be accessed by the CPU in word mode (not byte mode), even though they are all 16 bits or less in actual width. The upper 16 bits of register reads should be treated as undefined. The CL-PS6700 registers are accessible in all power states where the CL-PS6700 is powered and has a running PCLK (regardless of the state of PRDY). PC Card access should be done only when the CL-PS6700 is in Active mode.

Since register access circumvents the CL-PS6700 write queue, control of register bits, which can affect posted writes or prefetch reads such as applying and removing card power, should be done only after checking that the CL-PS6700 is idle using the Idle bit in the Interrupt Input Level register.

### 4.1 Register Addresses

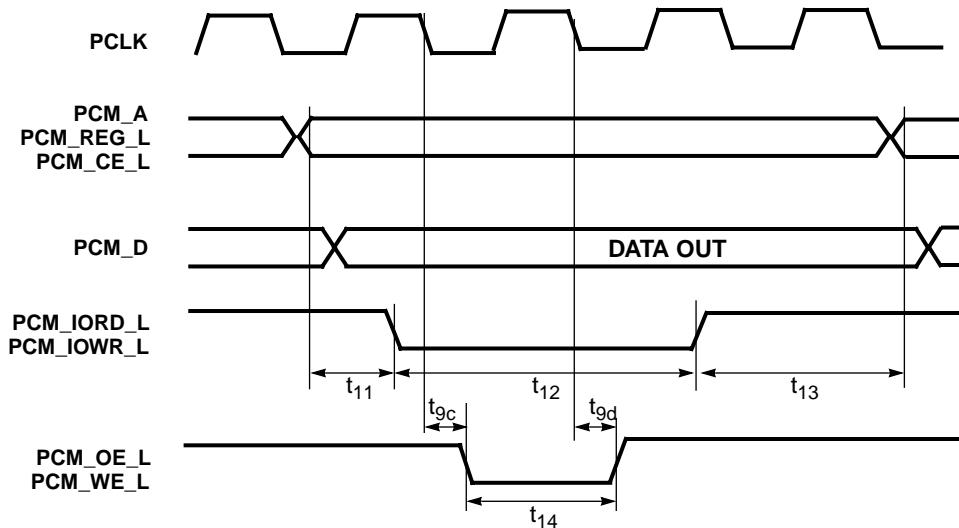

The following address conventions are used in the register tables.