捷多邦,专业PCB打样工厂,24小时加急出货

ICL7121

NOT RECOMMENDED FOR NEW DESIGNS

16-Bit Multiplying Microprocessor-Compatible D/A Converter

October 1997

#### **Features**

- 16-Bit Resolution

- Low Integral Linearity Error -0.003% FSR

- Monotonic to 16 Bits Over Full Military Temperature Range (LM Grade)

- Microprocessor Compatible with Buffered Inputs

- Bipolar Application Requires No External Resistors

- Output Current Settling Time 3μs Max (1μs Typ)

- Low Linerarity and Gain Temperature Coefficients

- Low Power Dissipation (25mW)

- Full Four-Quadrant Multiplication

- Low Differential Nonlinearity Error at Bipolor Zero

### Ordering Information

| PART NUMBER | TEMP. RANGE<br>(°C) | PACKAGE      |

|-------------|---------------------|--------------|

| ICL7121JCJI | 0 to 70             | 28 Ld CERDIP |

| ICL7121JMJI | -55 to 125          | 28 Ld CERDIP |

| ICL7121KCJI | 0 to 70             | 28 Ld CERDIP |

| ICL7121KMJI | -55 to 125          | 28 Ld CERDIP |

| ICL7121LCJI | 0 to 70             | 28 Ld CERDIP |

| ICL7121LMJI | -55 to 125          | 28 Ld CERDIP |

### Description

The ICL7121 achieves 0.003% linearity without laser trimming by combining a four quadrant multiplying DAC using thin film resistors with an on-chip PROM-controlled correction circuit. Silicon-gate CMOS circuitry keeps the power dissipation very low.

Microprocessor bus interfacing is eased using standard memory WRITE cycle timing and control. The input buffer register is loaded with the 16-bit input and directly controls the output switches. The register is transparent if WR and CS are held low.

The ICL7121 is designed and programmed for bipolar operation. There is an offset resistor to the output which should be connected to -VREF and an inverter on the MSB line, giving the DAC a 2's complement bipolar transfer function. Two extra resistors are included on the chip to facilitate the reference inversion, so that only an external opamp is needed.

#### **Pinout**

ICL7121 (OUTLINE DWG JI) **TOP VIEW**

|                        |          | -                        |

|------------------------|----------|--------------------------|

| (LSB) D <sub>0</sub> 1 | 0        | 28 CS                    |

| D <sub>1</sub> 2       |          | 27 WR                    |

| D <sub>2</sub> 3       | 199      | 26 V+                    |

| D <sub>3</sub> 4       |          | 25 I <sub>OUT</sub>      |

| D <sub>4</sub> 5       | and here | 24 AGND <sub>S</sub>     |

| D <sub>5</sub> 6       | , 1,51   | 23 AGND <sub>F</sub>     |

| D <sub>6</sub> 7       |          | 22 DGND                  |

| D <sub>7</sub> 8       |          | 21 R <sub>FB</sub>       |

| D <sub>8</sub> 9       |          | 20 R <sub>OFS</sub>      |

| D <sub>9</sub> 10      |          | 19 R <sub>INV</sub>      |

| D <sub>10</sub> 11     |          | 18 V <sub>REF</sub>      |

| D <sub>11</sub> 12     |          | 17 PROG                  |

| D <sub>12</sub> 13     |          | 16 D <sub>15</sub> (MSB) |

| D <sub>13</sub> 14     |          | 15 D <sub>14</sub>       |

|                        |          |                          |

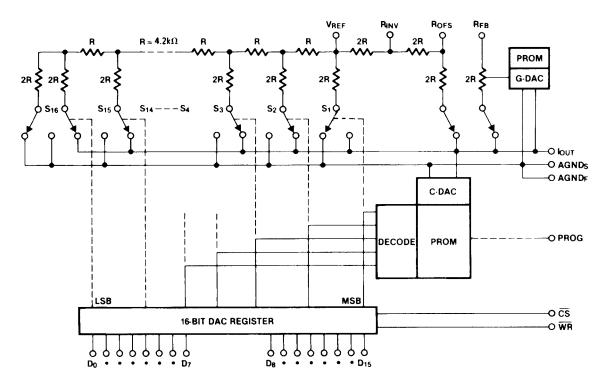

# Functional Block Diagram

# ICL7121

# Pin Descriptions

| 28 LEAD<br>CERDIP | PIN<br>NAME       |                                                                                                     | PIN DESCRIPTION                                             |  |  |  |  |  |

|-------------------|-------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| 1                 | D <sub>0</sub>    | Bit 0                                                                                               | Least Significant                                           |  |  |  |  |  |

| 2                 | D <sub>1</sub>    | Bit1                                                                                                |                                                             |  |  |  |  |  |

| 3                 | D <sub>2</sub>    | Bit 2                                                                                               |                                                             |  |  |  |  |  |

| 4                 | D <sub>3</sub>    | Bit 3                                                                                               |                                                             |  |  |  |  |  |

| 5                 | D <sub>4</sub>    | Bit 4                                                                                               |                                                             |  |  |  |  |  |

| 6                 | D <sub>5</sub>    | Bit 5                                                                                               |                                                             |  |  |  |  |  |

| 7                 | D <sub>6</sub>    | Bit 6                                                                                               |                                                             |  |  |  |  |  |

| 8                 | D <sub>7</sub>    | Bit 7                                                                                               | Lead Bare Breather Tools                                    |  |  |  |  |  |

| 9                 | D <sub>8</sub>    | Bit 8                                                                                               | Input Data Bits (High = True)                               |  |  |  |  |  |

| 10                | D <sub>9</sub>    | Bit 9                                                                                               |                                                             |  |  |  |  |  |

| 11                | D <sub>10</sub>   | Bit 10                                                                                              |                                                             |  |  |  |  |  |

| 12                | D <sub>11</sub>   | Bit 11                                                                                              |                                                             |  |  |  |  |  |

| 13                | D <sub>12</sub>   | Bit 12                                                                                              |                                                             |  |  |  |  |  |

| 14                | D <sub>13</sub>   | Bit 13                                                                                              |                                                             |  |  |  |  |  |

| 15                | D <sub>14</sub>   | Bit 14                                                                                              |                                                             |  |  |  |  |  |

| 16                | D <sub>15</sub>   | Bit 15                                                                                              | Most significant                                            |  |  |  |  |  |

| 17                | PROG              | Used for pro                                                                                        | Used for programming only. Tie to +5V for normal operation. |  |  |  |  |  |

| 18                | V <sub>REF</sub>  | V <sub>REF</sub> input t                                                                            | V <sub>REF</sub> input to ladder.                           |  |  |  |  |  |

| 19                | R <sub>INV</sub>  | Summing no                                                                                          | Summing node for reference inverting amplifier.             |  |  |  |  |  |

| 20                | R <sub>OFS</sub>  | Bipolar offse                                                                                       | Bipolar offset resistor, to -V <sub>REF</sub> .             |  |  |  |  |  |

| 21                | R <sub>FB</sub>   | Feedback re                                                                                         | Feedback resistor for voltage output applications.          |  |  |  |  |  |

| 22                | DGND              | Digital Groun                                                                                       | Digital Ground Return.                                      |  |  |  |  |  |

| 23                | AGND <sub>F</sub> | Analog Ground force lines. Use to carry current from internal Analog GND connections.               |                                                             |  |  |  |  |  |

| 24                | AGND <sub>S</sub> | Analog Ground sense line. Reference point for external circuitry. Pin should carry minimal current. |                                                             |  |  |  |  |  |

| 25                | lout              | Current output pin.                                                                                 |                                                             |  |  |  |  |  |

| 26                | V+                | Positive Supply.                                                                                    |                                                             |  |  |  |  |  |

| 27                | CS                | CHIP SELEC                                                                                          | CHIP SELECT (active low). Enables register write.           |  |  |  |  |  |

| 28                | WR                | WRITE, (active low). Writes in register. Equivalent to CS.                                          |                                                             |  |  |  |  |  |

### ICL7121

# Absolute Maximum Ratings (Note 1) Thermal Information

| Storage Temperature Range           | 65°C to 150°C |

|-------------------------------------|---------------|

| Power Dissipation (Note 2)          | 500mW         |

| Derate Linearly Above 70°C @10mW/°C |               |

| Lead Temperature (Soldering, 10s)   | 300°C         |

### **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. All voltages with respect to DGND.

- 2. Assumes all leads soldered or welded to printed circuit board.

# **Electrical Specifications** V+=+5V, $V_{REF}=+5V$ , $T_A=25^{o}C$ , AGND = DGND, $I_{OUT}$ at Ground Potential, Unless Otherwise Specified

| PARAMETER                       | TEST CONDITIONS                 | MIN    | TYP | MAX     | UNITS              |                     |

|---------------------------------|---------------------------------|--------|-----|---------|--------------------|---------------------|

| DC ACCURACY                     |                                 |        |     |         | •                  |                     |

| Resolution                      |                                 |        | 16  | -       | -                  | Bits                |

| Monotonicity                    | Guaranteed by DLE Test (Note 3) | J      | 14  | -       | -                  | Bits                |

|                                 |                                 | K      | 15  | -       | -                  | Bits                |

|                                 |                                 | L      | 16  | -       | -                  | Bits                |

| Differential Linearity Error at | $T_A = 25^{\circ}C$             | J, K   | -   | -       | ±1                 | LSB                 |

| Bipolar Zero                    |                                 | L      | -   | -       | ±1/2               | LSB                 |

|                                 | Operating Temperature Range     | J, K   | -   | -       | ±11/2              | LSB                 |

|                                 |                                 | L      | -   | -       | ±1                 | LSB                 |

| Differntial Linearity Error DLE | $T_A = 25^{\circ}C$             | J      | -   | -       | ±0.006             | %FSR                |

|                                 |                                 | K      | -   | -       | ±0.003             | %FSR                |

|                                 |                                 | L      | -   | -       | +0.003<br>-0.0015  | %FSR                |

|                                 | Operating Temperature Range     | J,KC   | -   | -       | ±0.006             | %FSR                |

|                                 |                                 | LC, KM | -   | -       | +0.0045<br>-0.003  | %FSR                |

|                                 |                                 | LM     | -   | -       | +0.0045<br>-0.0015 | %FSR                |

| Integral Linearity Error ILE    | $T_A = 25^{\circ}C$             | J      | -   | ±0.003  | ±0.006             | %FSR                |

|                                 |                                 | K,L    | -   | ±0.0015 | ±0.003             | %FSR                |

|                                 | Operating Temperature Range     | J      | -   | ±0.006  | ±0.009             | %FSR                |

|                                 |                                 | K, LM  | -   | ±0.003  | ±0.006             | %FSR                |

|                                 |                                 | LC     | -   | ±0.0015 | ±0.003             | %FSR                |

| Integral Linearity Error        |                                 | J      | -   | ±0.3    | ±1.2               | ppm/ <sup>o</sup> C |

| Temperature Coefficient         |                                 | K,L    | -   | ±0.2    | ±0.9               | ppm/ <sup>o</sup> C |

**Electrical Specifications** V+ = +5V, V<sub>REF</sub> = +5V, T<sub>A</sub> = 25°C, AGND = DGND, I<sub>OUT</sub> at Ground Potential, Unless Otherwise Specified (Continued)

| PARAMETER                                                        | TEST CONDITIONS                                                | MIN       | TYP | MAX    | UNITS  |                     |

|------------------------------------------------------------------|----------------------------------------------------------------|-----------|-----|--------|--------|---------------------|

| Unadjusted Gain Error                                            | $T_A = 25^{\circ}C$                                            | J         | -   | ±0.004 | ±0.012 | %FSR                |

|                                                                  |                                                                | K         | =   | ±0.003 | ±0.009 | %FSR                |

|                                                                  |                                                                | L         | =   | ±0.002 | ±0.006 | %FSR                |

|                                                                  | Operating Temperature Range                                    | J         | -   | ±0.002 | +0.04  | %FSR                |

|                                                                  |                                                                | K, L      | -   | ±0.01  | ±0.02  | %FSR                |

| Unadjusted Gain Error                                            | (Note 4)                                                       | J         | =   | ±1.0   | ±5.2   | ppm/ <sup>o</sup> C |

| Temperature Coefficient                                          |                                                                | K, L      | -   | ±0.5   | ±2.0   | ppm/ <sup>o</sup> C |

| Unadjusted Output Offset                                         | DAC Register Outputs All LOW (Not                              | e 6)      | -   | ±4     | ±15    | mV                  |

| Output Offset Temperature Drift                                  | Same Conditions as Above, (Note 4)                             | )         | -   | -      | ±5     | μV/ <sup>o</sup> C  |

| AC ACCURACY                                                      | •                                                              | <u> </u>  |     | •      | •      | •                   |

| Power Supply Rejection                                           | $\Delta V$ + = 5V ±10%, $T_A$ = 25°C                           | -         | ±30 | ±100   | ppm/C  |                     |

| Operating Temperature Range                                      |                                                                | -         | ±50 | ±150   | ppm/C  |                     |

| Output Current Settling Time                                     | To 1/2 LSB (Note 4)                                            | -         | 1.8 | 3      | μs     |                     |

| REFERENCE INPUT                                                  | •                                                              | <u> </u>  |     | •      | •      | •                   |

| Input Resistance                                                 | I <sub>OUT</sub> at Ground                                     |           | 3   | 4.2    | 6      | kΩ                  |

| ANALOG OUTPUT                                                    | •                                                              | <u> </u>  |     | •      | •      | •                   |

| Output Capacitance                                               | DAC Register Outputs All Low                                   | -         | 150 | -      | pF     |                     |

| (I <sub>OUT</sub> Terminal)                                      | DAC Register Outputs All High                                  |           | -   | 300    | -      | pF                  |

| DIGITAL INPUTS                                                   | •                                                              | <u> </u>  |     | •      | •      | •                   |

| LOW State Threshold                                              | Operating Temperature Range                                    |           | -   | -      | 0.8    | V                   |

| HIGH State Threshold                                             | 7                                                              |           | 2.4 | -      | -      | V                   |

| Input Current                                                    | Inputs Between DGND to V+                                      |           | =   | ±0.001 | ±1     | μΑ                  |

| Input Capacitance                                                | (Note 4)                                                       | =         | 15  | -      | pF     |                     |

| POWER SUPPLY                                                     | •                                                              | <u> </u>  |     | •      | •      |                     |

| Supply Voltage Rnage *                                           | Functional Operation (Note 5)                                  |           | 4.5 | -      | 5.5    | V                   |

| Supply Current                                                   | T <sub>A</sub> = 25 <sup>o</sup> C, Digital Inputs High or LOW |           | =   | 0.6    | 1.5    | mA                  |

| (Excluding Ladder Network)  Operating Temperature Ra HIGH or LOW |                                                                | al Inputs | -   | 1.0    | 2.5    | mA                  |

#### NOTES:

- 3. Military temperature range parts are also tested to stated limits at -55°C and 125°C.

- 4. Guaranteed by characterization but not tested on a production basis.

- 5. Guaranteed by PSRR test.

- 6. Refer to Figure 1. Measured at output amplifier A1 (A1 having zero offset).  $V_{REF} = +5V$ . Adjustable to zero with external potentiometer.

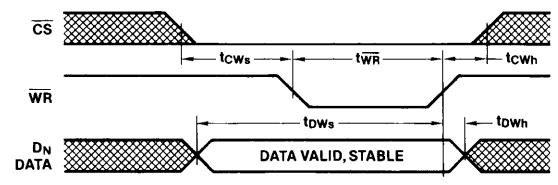

### **Switching Specifications** V+ = 5V, $T_A = 25$ °C, See Timing Diagram

| PARAMETER                     | SYMBOL           | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------|------------------|-----------------|-----|-----|-----|-------|

| CHIP SELECT-WRITE Set-Up Time | t <sub>CWs</sub> | Note 4          | 0   | -   | -   | ns    |

| CHIP SELECT-WRITE Hold Time   | t <sub>CWh</sub> | Note 4          | 0   | -   | -   | ns    |

| WRITE Pulse Width Low         | t₩R              | Note 4          | 200 | -   | -   | ns    |

| Data-WRITE Set-Up Time        | t <sub>DWs</sub> | Note 4          | 200 | =   | =   | ns    |

| Data-WRITE Hold Time          | t <sub>DWh</sub> | Note 4          | 0   | =   | -   | ns    |

## **Test Circuits**

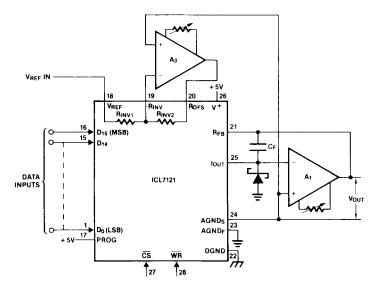

FIGURE 1. BIPOLAR OPERATION, FOUR-QUADRANT

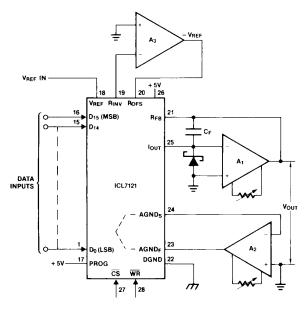

FIGURE 2. BIPOLAR OPERATION WITH FORCED GROUND

### Timing Diagram

FIGURE 3.

### **Definition of Terms**

Integral Linerarity Error - Error contributed by deviation of the DAC transfer function from a "best staight line" through the actual plot of transfer function. Normally expressed as a percentage of full scale range or in (sub)multiples of 1 LSB.

**Differential Linearity Error** - The difference between ideal and actual value of the analog output "step size" for any two adjacent digital input code. The ideal "step size" is equal to 2<sup>-n</sup> of full scale for an n-bit DAC or 1 LSB. It is expressed in (sub)multiples of 1 LSB.

**Resolution** - It is addressing the smallest distinct analog output change that a D/A converter can produce. It is commonly expressed as the number of converter bits. A converter with resolution of n bits can resolve output changes of 2<sup>-n</sup> of the full-scale range, e.g. 2<sup>-n</sup> V<sub>REF</sub> for a unipolar conversion. Resolution by no means implies linearity.

**Settling Time -** Time required for the output of a DAC to settle to within a specified error band around its final value (e.g. 1/2 LSB) for a given digital input change, i.e., all digital inputs LOW to HIGH and HIGH to LOW.

**Gain Error -** The difference between actual and ideal analog output values at full-scale range, ie.e. all digital inputs at HIGH state. It is expressed as a percentage of full-scale range or in (sub)multiples of 1 LBB.

$\mbox{\bf Output Capacitance}$  - Capcitance from  $\mbox{\bf I}_{\mbox{\scriptsize OUT}}$  terminal to ground.

### **Detailed Description**

The ICL7121 consists of a 16-bit primary DAC, PROM controlled correction DACs, input buffer registers, and microprocessor interface logic. The 16-bit primary DAC is an R-2R thin film resistor ladder with N-channel MOS SPDT current steering switches. Precise balancing of the switch resistances and all other resistors in the ladder results in excellent temperature stability.

The low linearity error is achieved by programming a floating polysilicon gate PROM array which controls a 12-bit correction DAC (C-DAC). The most significant bits of the primary

DAC register address this PROM array. Thus for every combination of the primary DAC's most significant bits a different C-DAC code is selected, allowing correctino of superposition erros. These errors are cuased by bit interaction on the primary ladder's current bus and by voltage non-linearity in the feedback resistor. Superposition errors cannot be corrected by any method that corrects individual bits only, such as laser trimming.

The onboard PROM also controls the 6-bit gain DAC. The G-DAC reduces gain error to less than 0.006% FSR by diverting to analog ground up to 2% of the current flowing in R<sub>FB</sub>.

Since the PROM programming occurs in packaged form, it corrects for resistor shifts caused by the thermal stresses of packaging, unlike wafer-level trimming methods. Also, since the thin film resistors do not suffer laser trimming stresses, no degradation of time-stability results.

### **Applications**

#### **Bipolar Operation**

The circuit diagram for the normal configuration of the ICL7121 is shown in Figure 1. The positive and negative reference voltages allow full four-qudrant multiplication. Amplifier A3, together with the internal resistors  $R_{INV1}$  and  $R_{INV2}$ , forms a simple voltage inverter circuit to generate -  $V_{REF}$  for the  $R_{OFS}$  offset input pin. This will give the nominal "digital input code/analog otuput value" relationship of Table 1. Note that the value of  $R_{FB}$  is equal to 2R so full scale range is  $2V_{REF}$ .

The offset binary transfer function can be achieved simply by inverting the MSB. Inversion of the MSB can be done by an inverter or may be done in software.

**TABLE 1. 2'S COMPLEMENT BIPOLAR OPERATION**

|      | DIGITAL INPUT |      |      |                                            |

|------|---------------|------|------|--------------------------------------------|

| MSB  |               |      | LSB  | ANALOG OUTPUT                              |

| 0111 | 1111          | 1111 | 1111 | -V <sub>REF</sub> (1 - 1/2 <sup>15</sup> ) |

| 0111 | 1111          | 1111 | 1110 | -V <sub>REF</sub> (1 - 1/2 <sup>14</sup> ) |

| 0000 | 0000          | 0000 | 0001 | -V <sub>REF</sub> (1/2 <sup>15</sup> )     |

**TABLE 1. 2'S COMPLEMENT BIPOLAR OPERATION**

| DIGITAL INPUT |      |      |      |                                            |

|---------------|------|------|------|--------------------------------------------|

| MSB           |      |      | LSB  | ANALOG OUTPUT                              |

| 0000          | 0000 | 0000 | 0000 | 0                                          |

| 1111          | 1111 | 1111 | 1111 | +V <sub>REF</sub> (1/2 <sup>15</sup> )     |

| 1000          | 0000 | 0000 | 0010 | +V <sub>REF</sub> (1 - 1/2 <sup>14</sup> ) |

| 1000          | 0000 | 0000 | 0001 | +V <sub>REF</sub> (1 - 1/2 <sup>15</sup> ) |

| 1000          | 0000 | 0000 | 0000 | +V <sub>REF</sub>                          |

Amplifier  $A_1$  is the output amplifier. An additional amplifier  $A_2$  may be used to force  $AGND_F$  if the ground reference piont is established elsewhere that at the DAC, as in Figure 2.

A feedback compensation capacitor,  $C_F$ , improves the settling time by reducing ringing. This capacitor is normally in the 10pF - 40pF range, depending on layout and the output amplifier selected. If  $C_F$  is too small, rigning or oscillation can occur when using an op amp with a high gain bandwidth. If  $C_F$  is too large, the response of the output amplifier will be overdamped and will settle slowly.

The input circuits of some high speed op amps will sink large currents to their negative supply during power up and power down. The Schottky diode at  $I_{OUT}$  limits any negative-going transitions to less than -0.4V, avoiding the SCR latchup which could result if significant current was injected into the parasitic diode between  $I_{OUT}$  and DGND of the ICL7121. This diode is not needed when using the ICL7650 ultra low

VOS op amp.

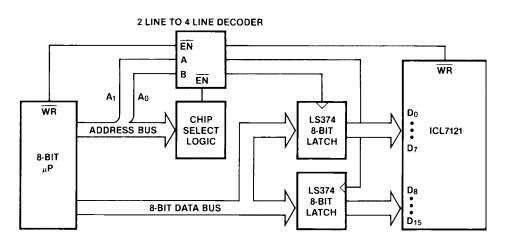

#### **Digital Interface**

The ICL7121 has a 16-bit latch onboard and can interface directly to a 16-bit data bus. As shown in Figure 4, external latches or peripheral ICs can be used to interface to an 8-bit data bus. To ensure that the data is written into the onboard latch, the data must be valid 200ns before the rising edge of  $\overline{\text{WR}}$ . If  $\overline{\text{WR}}$  and  $\overline{\text{CS}}$  are both low, the onboard latch is transparent and the input data is directly applied to the internal R-2R ladder switches. While this simplifies interfacing in non-microprocessor systems, having  $\overline{\text{WR}}$  low before data is valid may cause additional glitchews in some microprocessor systems. To avoid these glitches, data must be valid at the time  $\overline{\text{WR}}$  goes low.

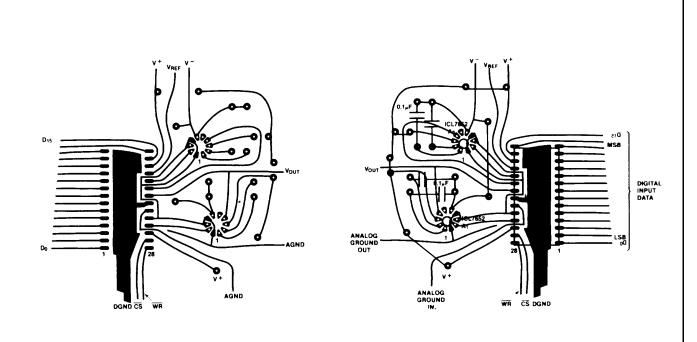

All digital interfaces can suffer from capacitive coupling between the digital lines and the analog section. There are two general precautions that will reduce this capacitive coupling problem: 1) reduce stray capacitance between digital lines and analog lines; and 2) reduce the number of transitions on the digital inputs. Careful board layout and shielding can minimize the capacitive coupling (see Figure 5). The activity on the digital input lines can be reduced by using external latches or peripheral interface ICs between the microprocessor bus and the ICL7121. This will reduce the number of transitions on the digital data and control lines of the ICL7121, thereby reducing the amount of digital noise coupled into the sensitve analog sections.

FIGURE 4. INTERFACE TO 8-BIT MICROPROCESSOR

FIGURE 5A. PRINTED CIRCUIT SIDE OF BOARD

FIGURE 5B. TOP SIDE WITH COMPONENT PLACEMENT

FIGURE 5. PRINTED CIRCUIT BOARD LAYOUT (SINGLE SIDED BOARD)

### Operational Amplifier Section

The input offset voltage, input current, gain, and bandwidth of the op amps used affect the circuit performance. Since the output impedance of  $I_{OUT}$  varies with the digital input code, the input current of amplifier  $A_1$  will cause a code-dependent error at  $V_{OUT}$ , degrading the linearity. The input bias current should be significantly less than 1 LSB current, which is about 10nA. In a similar manner, any offset voltage in  $A_1$  will cause linearity errors. The offset voltage of the output amplifier should be significantly less than 1 LSB (153 $\mu$ V at  $V_{REF}=5V$ ).

The voltage output setting time is highly dependent on the slew rate and gain-bandwidth of  $A_1$ , so for high speed operation a high speed op amp such as the HA2600 is recommended. For applications where high speed is not required, the ICL7650 or ICL7652 can be used for  $A_1$ . Since the ICL7650/52 offset voltage is less than  $5\mu V$ , no offset trimming is needed. To get a full 5V output swing from these op amps,  $\pm 7.5V$  supplies should be used for the ICL7650/52.

Amplifer  $A_3$ , which is used to generate the inverted reference, needs only to have a stable offset and to be able to drive a  $3k\Omega$  load. Since this is strictly a DC amplifier, the low noise ICL7652 is an ideal choice. Any variation in the offset voltage of  $A_3$  will result in a drift in the bipolar zero, but will not affect the linearity of the ICL7121.

Amplifier  $A_3$ , used to generate a high quality ground, also meeds a low offset and the ability to sink up to 2mA.

### Multiplying Mode Performance

While the ICL7121 can perform full four-quadrant muliplication, full 0.003% linearity is guaranteed only at  $V_{REF} = +5V$ . This is because the voltage coefficient of resistance of the R-2R ladder and the feedback resistor are significant at the 14-bit or 16-bit level. This effect is most significant at high voltages, and adds errors on the order of 0.01% for a  $\pm 10V$  full-scale. While the ICL7121 is tested and specified for  $V_{REF} = +5V$ , the R-2R ladder has the same voltage across it when  $V_{REF} = -5V$ . Therefore, voltage coefficients do not add any error with a -5V reference voltage.

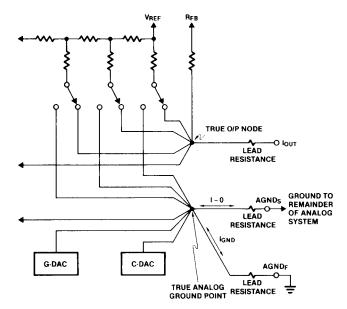

#### Grounding

Careful consideration must be given to grounding in any high accuracy system. The current into the analog ground point inside the chip varies signficantly with the input code value, and the inevitable resistances between this point and any external connection point can lead to signficant voltage drop errors. For this reason, two separate leads are brought out from this point on the IC: AGND<sub>S</sub> and AGND<sub>F</sub>. The varying current should be absorbed through the AGND<sub>F</sub> pin, and the AGND<sub>S</sub> pin will then accurately reflect the voltage on the internal current summing point, as shown in Figure 6. Output signals should ideally be referenced to the sense pin AGND<sub>S</sub>, as shown in the application circuits.

FIGURE 6. GROUND CONNECTIONS