# 捷多邦,专业PCB打样工厂,24小时加急出货

June 1999

Wideband, Closed-Loop Monolithic Buffer Amplifier

ational Semiconductor

# CLC110 Wideband, Closed-Loop Monolithic Buffer Amplifier

## **General Description**

Using a unique closed-loop design, the CLC110 buffer offers a high-fidelity, high-performance alternative to conventional openloop buffers. For example, the – 3dB bandwidth is 730MHz ( $0.5V_{pp}$ ) and the settling time to 0.2% is typically only 5ns. Yet all this is achieved while maintaining excellent signal fidelity as demonstrated by the – 65dBc harmonic distortion at 20MHz – a value unmatched by any high-speed buffer.

The CLC110 is an ideal choice for a wide variety of applications. With its speed and accuracy, the CLC110 offers designers the benefit of buffering signals which might otherwise go unbuffered due to performance penalties imposed by conventional buffers. For example, the CLC110 is well suited for use within closed-loop systems such as amplifier or phase locked loop systems; with its 400ps rise time, its effect on loop dynamics is usually negligible.

Ultra-fast flash A/D converter systems can also benefit from the speed of the CLC110. And, since most flash A/D's have capacitive inputs, the CLC110's dynamic performance has been characterized for various loads. In addition, the amplifier specifications are for a  $100\Omega$  load.

The CLC110 is available in several versions to meet a variety of requirements. A three-letter suffix determines the version:

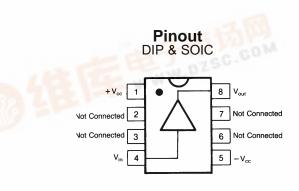

CLC110AJP -40°C to +85°C 8-pin plastic DIP CLC110AJE -40°C to +85°C 8-pin plastic SOIC DESC SMD number: 5962-89975

### **Features**

- Closed-loop, unity-gain operation

- -3dB bandwidths of 730MHz (0.5V<sub>pp</sub>)

- 0.2% settling in 5ns

- Low power, 150mW

- Low distortion, -65dBc at 20MHz

## **Applications**

- Ultra-fast flash A/D conversion

- Line driving

- High-speed communications

- Impedance transformation

- Power buffers

- IF processors

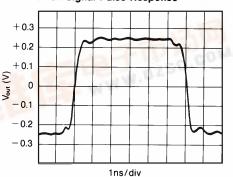

Small Signal Pulse Response

| CLC110 Electrical Characteristics ( $V_{cc} = \pm 5V$ , $R_L = 100\Omega$ , $R_s = 50\Omega$ ; unless specified)                                                                                                                                                                      |                                                                                                       |                                                 |                                                            |                                                    |                                                          |                                                      |                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|

| PARAMETERS                                                                                                                                                                                                                                                                            | CONDITIONS                                                                                            | TYP                                             | MIN AND MAX RATINGS                                        |                                                    | UNITS                                                    | SYMBOL                                               |                                                         |

| Ambient Temperature                                                                                                                                                                                                                                                                   | CLC110AJ                                                                                              | +25°C                                           | -40°C                                                      | +25°C                                              | +85°C                                                    |                                                      |                                                         |

| FREQUENCY DOMAIN PE<br>- 3dB bandwidth                                                                                                                                                                                                                                                | $\begin{array}{l} \textbf{RFORMANCE}^{1} \\ V_{out} < 0.5 V_{pp} \\ V_{out} < 5 V_{pp} \end{array}$   | 730<br>90                                       | >400<br>>50                                                | >400<br>>55                                        | >300<br>>50                                              | MHz<br>MHz                                           | SSBW<br>LSBW                                            |

| gain flatness<br>peaking<br>rolloff<br>group delay<br>linear phase deviation                                                                                                                                                                                                          | $V_{out} < 0.5V_{pp}$<br>DC to 200MHz<br>DC to 200MHz<br>DC to 200MHz<br>DC to 200MHz<br>DC to 200MHz | 0<br>0<br>0.75<br>0.7                           | <0.8<br><1.0<br><1.0<br><1.5                               | <0.5<br><0.8<br><1.0<br><1.5                       | <0.6<br><1.2<br><1.2<br><2.0                             | dB<br>dB<br>ns<br>∘                                  | GFPH<br>GFRH<br>GD<br>LPD                               |

| TIME DOMAIN PERFORMANCE <sup>1</sup><br>rise and fall time 0.5V step                                                                                                                                                                                                                  |                                                                                                       | 0.4                                             | <1.0                                                       | <1.0                                               | <1.4                                                     | ns                                                   | TRS                                                     |

| (input signal rise/fall<br>overshoot                                                                                                                                                                                                                                                  | 0.5V step                                                                                             | 0                                               | <15                                                        | <10                                                | <15                                                      | %                                                    | OS                                                      |

| (input signal rise/fall<br>rise and fall time<br>(input signal rise/fall                                                                                                                                                                                                              | 5V step                                                                                               | 4.5                                             | <8.5                                                       | <7.5                                               | <8.5                                                     | ns                                                   | TRL                                                     |

| settling time to $\pm 0.2\%$<br>slew rate                                                                                                                                                                                                                                             | 2V step                                                                                               | 5<br>800                                        | <10<br>>450                                                | <10<br>>500                                        | <10<br>>450                                              | ns<br>V/ <i>µ</i> s                                  | TSP<br>SR                                               |

| DISTORTION AND NOISE PERFORMANCE<br>2nd harmonic distortion                                                                                                                                                                                                                           |                                                                                                       |                                                 |                                                            |                                                    |                                                          |                                                      |                                                         |

|                                                                                                                                                                                                                                                                                       | 2V <sub>pp</sub> , 20MHz<br>2V <sub>pp</sub> , 50MHz                                                  | -65<br>-60                                      | <-48<br><-48                                               | <-55<br><-55                                       | <-55<br><-55                                             | dBc<br>dBc                                           | HD2<br>HHD2                                             |

| 3rd harmonic distortion                                                                                                                                                                                                                                                               | 2V <sub>pp</sub> , 20MHz<br>2V <sub>pp</sub> , 50MHz                                                  | -65<br>-60                                      | <-55<br><-50                                               | <-55<br><-50                                       | <-55<br><-45                                             | dBc<br>dBc                                           | HD3<br>HHD3                                             |

| equivalent input noise<br>noise floor<br>integrated noise                                                                                                                                                                                                                             | > 1MHz<br>1MHz to 200MHz                                                                              | -158<br>40                                      | <-155<br><57                                               | <-155<br><57                                       | <154<br><63                                              | dBm(1Hz)<br>μV                                       | SNF<br>INV                                              |

| STATIC, DC PERFORMANCE   small signal gain into 100Ω load   integral endpoint linearity ±2V full scale   * output offset voltage   average temperature coefficient   * input bias current   average temperature coefficient   power supply rejection ratio   * supply current no load |                                                                                                       | 0.97<br>0.2<br>2<br>20<br>20<br>200<br>50<br>15 | >0.95<br><0.8<br><16<br><100<br><100<br><700<br>>45<br><20 | >0.96<br><0.4<br><8.0<br><br><50<br><br>>45<br><20 | >0.95<br><0.3<br><13<br><50<br><50<br><300<br>>45<br><20 | V/V<br>%FS<br>mV<br>μV/°C<br>μA<br>nA/°C<br>dB<br>mA | GA<br>ILIN<br>VIO<br>DVIO<br>IBN<br>DIBN<br>PSRR<br>ICC |

| MISCELLANEOUS PERFO<br>input resistance<br>capacitance<br>output impedance<br>output voltage range<br>output current                                                                                                                                                                  | at DC<br>100Ω load                                                                                    | 160<br>1.6<br>2<br>±4<br>±70                    | $>50 <2.5 <3.5 >\pm 3.0 >\pm 45$                           | >100<br><2.2<br><3.0<br>>±3.2<br>>±50              | >200<br><2.5<br><3.5<br>>±3.2<br>>±50                    | kΩ<br>pF<br>Ω<br>V<br>mA                             | RIN<br>CIN<br>RO<br>VO<br>IO                            |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

| Absolute Maximum Ratings                                                                                                                                                                                                                     |                                              |             | Miscellaneous Ratings                |                                                                                                                                    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>cc</sub><br>I <sub>out</sub> output is short circuit protected to ground,<br>but, maximum reliability will be obtained if<br>I <sub>out</sub> does not exceed<br>input voltage<br>junction temperature<br>operating temperature range |                                              | Notes:<br>* | AJ<br>note 1:<br>Pac                 | 100% tested at +25°C.<br>AC performance is very dependent on layout.<br>Specifications apply only in a 50Ω microstrip environment. |  |  |  |

| AI:<br>storage temperature range<br>lead solder duration (+300°C)                                                                                                                                                                            | – 40°C to +85°C<br>–65°C to +150°C<br>10 sec | Plasti      | c <b>kage</b><br>c (AJP)<br>ce Mount | θJC   θJA     65°C/W   115°C/W     t (AJE)   55°C/W   125°C/W                                                                      |  |  |  |

# **Reliability Information**

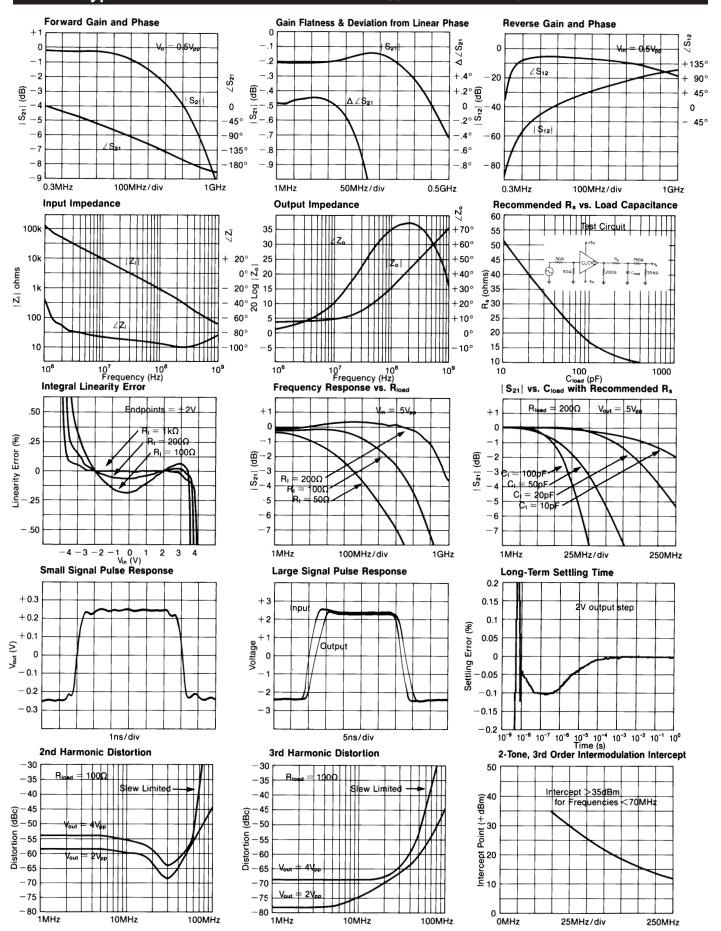

# CLC110 Typical Performance Characteristics ( $V_{CC} = \pm 5V$ , $R_L = 100\Omega$ , $R_s = 50\Omega$ ; unless specified)

$R_{out}$  is chosen for desired output impedance. (CLC110  $R_{out} = 2\Omega$ )

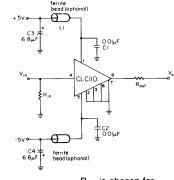

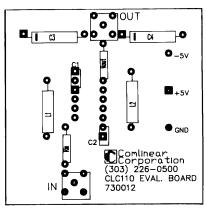

Figure 1: recommended circuit and evaluation board schematic

#### Operation

The CLC110 is based upon a unique, patented closed-loop design, which provides the accuracy characteristics of a closed-loop amplifier, yet also has unmatched dynamic performance.

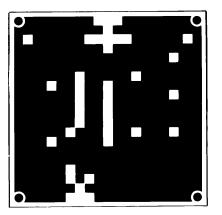

#### Printed Circuit Layout and Supply Bypassing

As with any high-frequency device, a good PCB layout is required for optimum performance. This is especially important for a device as fast as the CLC110, which has a typical bandwidth of 730MHz.

To minimize capacitive feedthrough, the pins not connected internally (pins 2, 3, 6, and 7) should be connected to the ground plane. Input and output traces should be laid out as transmission lines with the appropriate termination resistors very near the CLC110. On a 0.065 inch epoxy PCB material, a 50 $\Omega$  transmission line (commonly called stripline) can be constructed by using a trace width of 0.1" over a complete ground plane.

Figure 1 shows recommended power supply bypassing. The ferrite beads are optional and are recommended only where additional isolation is needed from high-frequency (>400MHz) resonances of the power supply.

Parasitic or load capacitance directly on the output of the CLC110 will introduce additional phase shift in the device, which can lead to decreased phase margin and frequency response peaking. A small series resistor before the capacitance effectively decouples this effect. The graphs on the preceding page illustrate the required resistor value and the resulting performance vs. capacitance.

Precision buffed resistors (PRP8351 series from Precision Resistive Products), which have low parasitic reactances, were used to develop the data sheet specifications. Precision carbon composition resistors or standard spirally-trimmed RN55D metal film resistors will work, though they will cause a degradation of AC performance due to their reactive nature at high frequencies.

#### **Evaluation Board**

An evaluation board (part CLC730012) is available for the CLC110 to assist in the evaluation of the CLC110. It may also be used as a guide in developing a printed circuit layout. Figure 1 shows the board's schematic; Figures 2 through 4 show the board layout.

Evaluation Board Parts List:

- R<sub>in</sub> select for desired input impedance

- Rout select for desired output impedance

- C1, C2 0.1µF ceramic radial lead

- C<sub>3</sub>, C<sub>4</sub> 6.8µF (Sprague 150D series)

- L<sub>1</sub>, L<sub>2</sub> ferrite beads (optional) (Ferroxcube #VK 200 19/4B)

Hardware (optional) SocketsCambion flush-mount connector jacks (#450-2598-01-06-00) SMA Connectors (female) Amphenol 901-144 (straight) Amphenol 901-143 (angled)

Figure 2: component placement guide

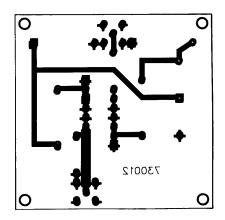

Figure 3: solder side (bottom) as viewed from component side (top)

R<sub>in</sub> is chosen for desired input impedance. This page intentionally left blank.

## **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

R

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.