June 1999

# CLC5654 Very High-Speed, Low-Cost, Quad Operational Amplifier

# **General Description**

The CLC5654 is a quad, current feedback operational amplifier that is perfect for many cost-sensitive applications that require high performance. This device also offers excellent economy in board space and power, consuming only 5mA per amplifier while providing 70mA of output current capability. Applications requiring significant density of high speed devices such as video routers, matrix switches and high-order active filters will benefit from the configuration of the CLC5654 and the low channel-to-channel crosstalk of 70dB at 5MHz.

The CLC5654 provides excellent performance for video applications. Differential gain and phase of 0.03% and 0.03° makes this device well suited for many professional composite video systems, but consumer applications will also be able to take advantage of these features due to the device's low cost. The CLC5654 offers superior dynamic performance with a small signal bandwidth of 450MHz and slew rate of 2000V/µs. These attributes are well suited for many component video applications such as driving RGB signals down significant lengths of cable. These and many other application can also take advantage of the 0.1dB flatness to 40MHz.

Combining wide bandwidth with low cost makes the the CLC5654 an attractive option for active filters. SAW filters are often used in IF filters in the 10's of MHz range, but higher order filters designed around a quad operational amplifier may offer an economical alternative to the typical SAW approach and offer greater freedom in the selection of filter parameters. National Semiconductor's Comlinear Products Group has published a wide array of liturature on active filters and a list of these publications can be found on the last page of this datasheet.

# **Features**

- 450MHz small signal bandwidth

- 2000 V/µs slew rate

- 5mA / channel supply current

- -71/-82dBc HD2/HD3 (5MHz)

- 0.03%, 0.03° differential gain, phase

- 70mA output current

- 12ns settling to 0.1%

# **Applications**

- High performance RGB video

- Video switchers & routers

- Video line driver

- Active filters

- IF amplifier

- Twisted pair driver/receiver

# Non-Inverting Frequency Response $A_v = 12$ $A_v = 12$ $A_v = 13$ $A_v = 14$ $A_v = 10$ $A_v = 10$

# Typical Configurations **Non-Inverting Gain Inverting Gain Pinout** DIP & SOIC 6.8µF 6.8µF 0.1μF $0.1 \mu F$ 1/4 CLC5654 1/4 CLC5654 4 $R_f$ Note: R<sub>b</sub> provides DC bias for the non-inverting input. 0.1μF 0.1μF Select $R_t$ to yield desired $R_{in} = R_t || R_a$ . 6.8µF 6.8µF

| PARAMETERS                               | CONDITIONS                     | TYP   | MIN/MAX | RATINGS     | UNITS  | NOTES |

|------------------------------------------|--------------------------------|-------|---------|-------------|--------|-------|

| Ambient Temperature                      | CLC5654I                       | +25°C | +25°C   | -40 to 85°C |        |       |

| FREQUENCY DOMAIN RESPONS                 | SE                             |       |         |             |        |       |

| -3dB bandwidth                           | $A_v = 1$                      | 450   | _       | _           | MHz    |       |

|                                          | $V_o$ < $0.5V_{pp}$            | 350   | _       | _           | MHz    |       |

|                                          | $V_0^{\circ} < 5V_{pp}^{\rho}$ | 100   | _       | _           | MHz    |       |

| 0.1dB bandwidth                          |                                | 40    | _       | _           | MHz    |       |

| differential gain                        | NTSC, $R_L = 150\Omega$        | 0.03  | _       | _           | dB     |       |

| differential phase                       | NTSC, $R_L = 150\Omega$        | 0.03  | _       | _           | dB     |       |

| TIME DOMAIN RESPONSE                     |                                |       |         |             |        |       |

| rise and fall time                       | 0.5V step                      | 1.2   | _       | _           | ns     |       |

|                                          | 5V step                        | 2.7   | _       | _           | ns     |       |

| settling time to 0.1%                    | 2V step                        | 12    | _       | _           | ns     |       |

| overshoot                                | 0.5V step                      | 7     | _       | _           | %      |       |

| slew rate                                |                                | 2000  | _       | _           | V/μs   |       |

| <b>DISTORTION AND NOISE RESPO</b>        | ONSE                           |       |         |             |        |       |

| 2 <sup>nd</sup> harmonic distortion      | 2V <sub>pp</sub> , 5MHz        | -71   | _       | _           | dBc    |       |

| 3 <sup>rd</sup> harmonic distortion      | 2V <sub>pp</sub> , 5MHz        | -82   | _       | _           | dBc    |       |

| equivalent input noise                   | **                             |       |         |             |        |       |

| voltage (e <sub>ni</sub> )               | >1MHz                          | 3.3   | _       | _           | nV/√Hz |       |

| non-inverting current (i <sub>bn</sub> ) | >1MHz                          | 2.5   | _       | _           | pA/√Hz |       |

| inverting current (i <sub>bi</sub> )     | >1MHz                          | 12    | _       | _           | pA/√Hz |       |

| crosstalk (input inferred)               | 10MHz                          | 76    | _       | _           | dBc    |       |

| STATIC DC PERFORMANCE                    |                                |       |         |             |        |       |

| input offset voltage                     |                                | 2.5   | 6       | 11          | mV     | A     |

| average drift                            |                                | 18    | _       | 55          | μV/°C  |       |

| input bias current (non-inverting)       |                                | 6     | 15      | 28          | μΑ     | A     |

| average drift                            |                                | 40    | _       | 160         | nA/°C  |       |

| input bias current (inverting)           |                                | 5     | 12      | 20          | μΑ     | A     |

| average drift                            |                                | 25    | _       | 120         | nA/°C  |       |

| power supply rejection ratio             | DC                             | 55    | 47      | 45          | dB     |       |

| common-mode rejection ratio              | DC                             | 50    | 45      | 43          | dB     |       |

| supply current (per channel)             | R <sub>L</sub> = ∞             | 5     | 6.7     | 7           | mA     | A     |

| MISCELLANEOUS PERFORMANCE                |                                |       |         |             |        |       |

| input resistance (non-inverting)         |                                | 1     | 0.5     | 0.25        | ΜΩ     |       |

| input capacitance (non-inverting)        |                                | 1     | 2       | 2           | pF     |       |

| common-mode input range                  |                                | ±2.2  | ±2.0    | ±1.4        | ·V     |       |

| output voltage range                     | $R_L = 150\Omega$              | ±2.6  | ±2.5    | ±2.3        | V      |       |

| output current                           | _                              | 70    | 50      | 40          | mA     |       |

| output resistance, closed loop           | DC                             | 0.2   | 0.3     | 0.6         | mΩ     |       |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# Notes

A) J-level: spec is 100% tested at +25°C.

# Reliability Information

Transistor Count 152

MTBF (based on limited test data) 12.5Mhr

# Package Thermal Resistance

| Package            | θ <sub>JC</sub> | $\theta_{JA}$ |  |

|--------------------|-----------------|---------------|--|

| Plastic (IN)       | 60°C/W          | 110°C/W       |  |

| Surface Mount (IM) | 55°C/W          | 125°C/W       |  |

# **Absolute Maximum Ratings**

supply voltage ( $V_{CC}$  -  $V_{EE}$ ) +14V output current 95mA common-mode input voltage  $V_{EE}$  to  $V_{CC}$  maximum junction temperature +150°C storage temperature range -65°C to +150°C lead temperature (soldering 10 sec) +300°C

| Orc | lering | Information |

|-----|--------|-------------|

|     |        |             |

| Model Temperature Range |                | Description          |  |  |

|-------------------------|----------------|----------------------|--|--|

| CLC5654IN               | -40°C to +85°C | 14-pin PDIP          |  |  |

| CLC5654IM               | -40°C to +85°C | 14-pin SOIC          |  |  |

| CLC5654IMX              | -40°C to +85°C | 14-pin tape and reel |  |  |

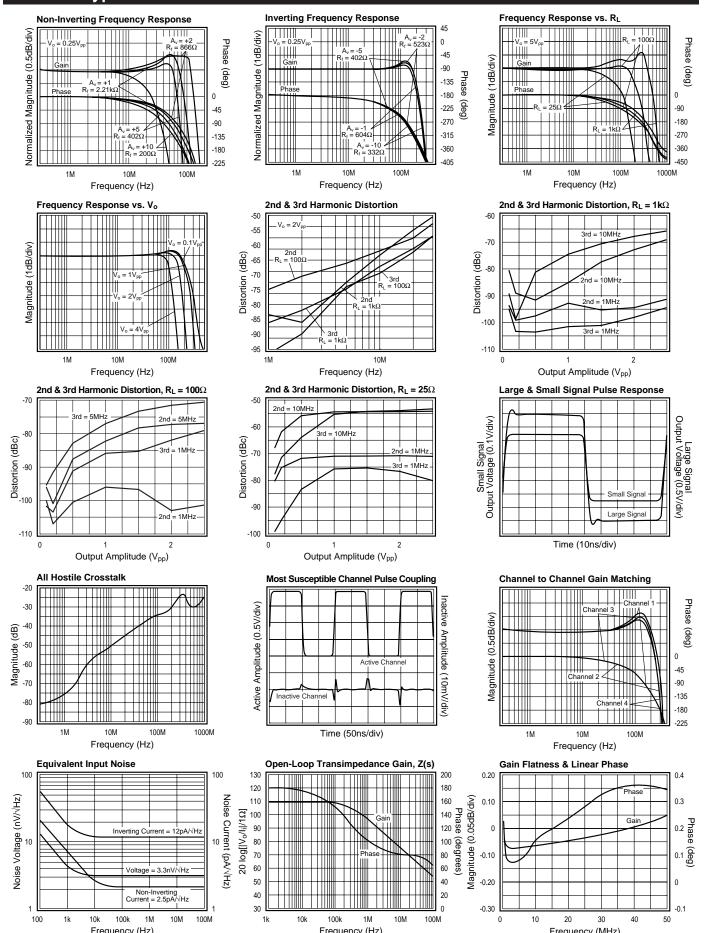

# CLC5654 Typical Performance (A $_v$ = +2, R $_f$ = 866 $\Omega$ , R $_L$ = 100 $\Omega$ , V $_s$ = ±5V, unless specified)

# **Current Feedback Amplifiers**

Some of the key features of current feedback technology are:

- Independence of AC bandwidth and voltage gain

- Inherently stable at unity gain

- Adjustable frequency response with R<sub>f</sub>

- High slew rate

- Fast settling

Current feedback operation can be described using a simple equation. The voltage gain for a non-inverting or inverting current feedback amplifier is approximated by Equation 1.

$$\frac{V_o}{V_i} = \frac{A_v}{1 + \frac{R_f}{Z(j\omega)}}$$

Equation 1

where:

A, is the closed loop DC voltage gain R<sub>f</sub> is the feedback resistor Z(jω) is the open loop transimpedance gain

The denominator of Equation 1 is approximately equal to 1 at low frequencies. Near the -3dB corner frequency, the interaction between  $R_f$  and  $Z(j\omega)$ dominates the circuit performance. The value of the feedback resistor has a large affect on the circuits performance. Increasing R<sub>f</sub> has the following affects:

- Decreases loop gain

- Decreases bandwidth

- Reduces gain peaking

- Lowers pulse response overshoot

- Affects frequency response phase linearity

# **Layout Considerations**

A proper printed circuit layout is essential for achieving high frequency performance. National provides evaluation boards for the CLC5654 (CLC730024 - DIP, CLC730031 - SOIC) and suggests their use as a guide for high frequency layout and as an aid for device testing and characterization. General layout and supply bypassing play major roles in high frequency performance. Follow the steps below as a basis for high frequency layout:

- Include 6.8µF tantalum and 0.1µF ceramic capacitors on both supplies.

- Place the 6.8µF capacitors within 0.75 inches of the power pins.

- Place the 0.1µF capacitors less than 0.1 inches from the power pins.

- Remove the ground plane under and around the part, especially near the input and output pins to reduce parasitic capacitance.

- Minimize all trace lengths to reduce series inductances.

- Use flush-mount printed circuit board pins for prototyping, never use high profile DIP sockets.

# **Active Filter Application Notes**

- OA-21 Simplified Component Pre-Distortion for High Speed Active Filters

- OA-26 Designing High-Speed Active Filters

- OA-27 Low-Sensitivity, Lowpass Filter Design

- OA-28 Low-Sensitivity, Bandpass Filter Design with Tuning Method

- OA-29 Low-Sensitivity, Highpass Filter Design with Parasitic Compensation

### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at 1-800-272-9959 or fax 1-800-737-7018.

# Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **National Semiconductor** Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

# **National Semiconductor Europe**

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

### **National Semiconductor** Hong Kong Ltd.

2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong

Tel: (852) 2737-1600 Fax: (852) 2736-9960

# **National Semiconductor** Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408