# ispClock 5600 Family

In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer

November 2004 Preliminary Data Sheet

### **Features**

- 10MHz to 320MHz Input/Output Operation

- Low Output to Output Skew (<50ps)

- Low Jitter Peak-to-Peak (<60ps)</p>

- Up to 20 Programmable Fan-out Buffers

- Programmable output standards and individual enable controls

- LVTTL, LVCMOS, HSTL, SSTL, LVDS, LVPECL

- · Programmable output impedance

- 40 to  $70\Omega$  in  $5\Omega$  increments

- · Programmable slew rate

- Up to 10 banks with individual V<sub>CCO</sub> and GND

- 1.5V, 1.8V, 2.5V, 3.3V

#### **■** Fully Integrated High-Performance PLL

- Programmable lock detect

- · Multiply and divide ratio controlled by

- Input divider (5 bits)

- Feedback divider (5 bits)

- Five output dividers (5 bits)

- · Programmable On-chip Loop Filter

#### ■ Precision Programmable Phase Adjustment (Skew) Per Output

- 16 settings; minimum step size 195ps

- Locked to VCO frequency

- Up to +/- 12ns skew range

- · Coarse and fine adjustment modes

#### ■ Up to Five Clock Frequency Domains

# ■ Flexible Clock Reference and External Feedback Inputs

- Programmable input standards

- LVTTL, LVCMOS, SSTL, HSTL, LVDS, LVPECL

- Clock A/B selection multiplexer

- Feedback A/B selection multiplexer

- Programmable termination

# Four User-programmable Profiles Stored in E<sup>2</sup>CMOS<sup>®</sup> Memory

Supports both test and multiple operating configurations

# ■ Full JTAG Boundary Scan Test In-System Programming Support

- Exceptional Power Supply Noise Immunity

- Commercial (0 to 70°C) and Industrial (-40 to 85°C) Temperature Ranges

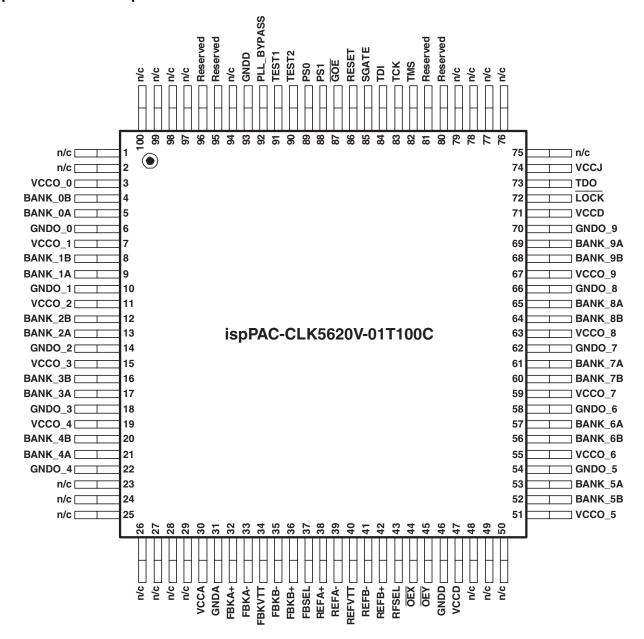

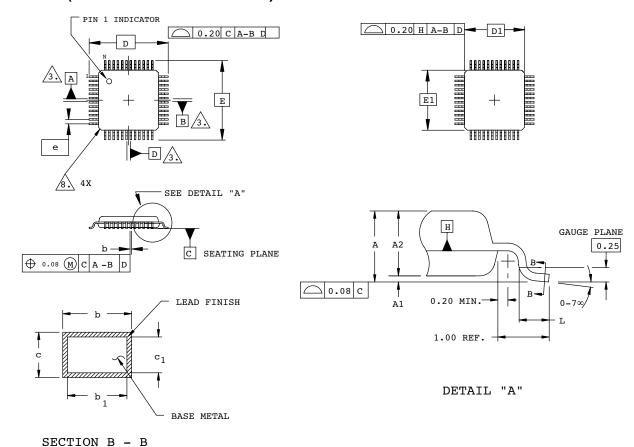

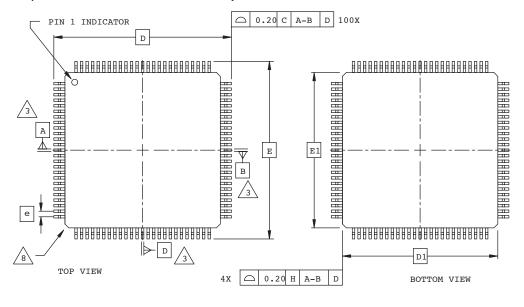

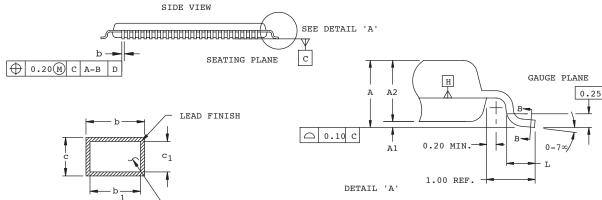

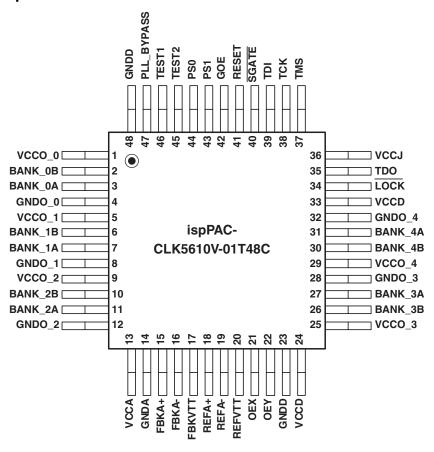

- 100-pin and 48-pin TQFP Packages

#### Applications

- Circuit board common clock generation and distribution

- · PLL-based frequency generation

- · High fan-out clock buffer

- Zero-delay clock buffer

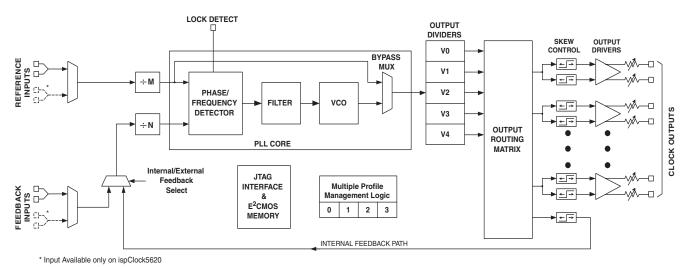

### **Product Family Block Diagram**

© 2004 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### **General Description and Overview**

The ispClock5610 and ispClock5620 are in-system-programmable high-fanout PLL-based clock drivers designed for use in high performance communications and computing applications. The ispClock5610 provides up to 10 single-ended or five differential clock outputs, while the ispClock5620 provides up to 20 single-ended or 10 differential clock outputs. Each pair of outputs may be independently configured to support separate I/O standards (LVDS, LVPECL, LVTTL, LVCMOS, SSTL, HSTL) and output frequency. In addition, each output provides independent programmable control of termination, slew-rate, and timing skew. All configuration information is stored on-chip in non-volatile E<sup>2</sup>CMOS memory.

The ispClock5600's PLL and divider systems supports the synthesis of clock frequencies differing from that of the reference input through the provision of programmable input and feedback dividers. A set of five post-PLL V-dividers provides additional flexibility by supporting the generation of five separate output frequencies. Loop feedback may be taken internally from the output of any of the five V-dividers, or externally through FBKA+/- or FBKB+/- pins.

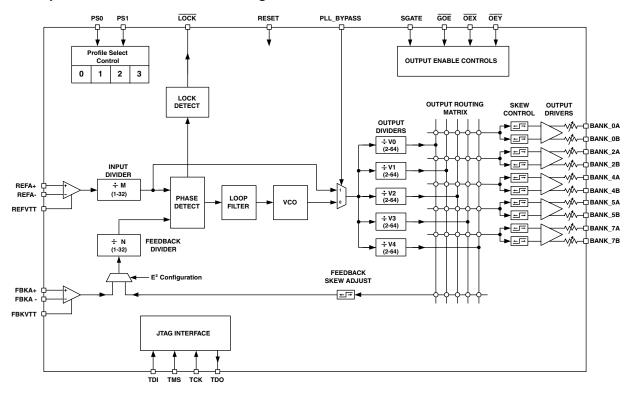

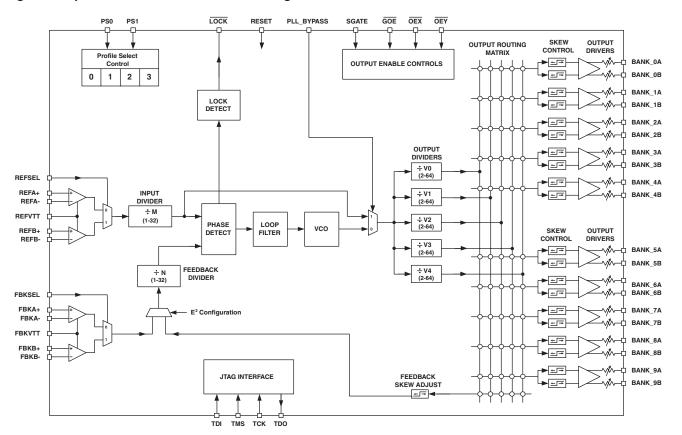

The core functions of all members of the ispClock5600 family are identical, the differences between devices being restricted to the number of inputs and outputs, as shown in the following table. Figures 1 and 2 show functional block diagrams of the ispClock5610 and ispClock5620.

Table 1. ispClock5600 Family Members

| Device       | Ref. Input Pairs | Feedback Input Pairs | Clock Outputs |

|--------------|------------------|----------------------|---------------|

| ispClock5610 | 1                | 1                    | 10            |

| ispClock5620 | 2                | 2                    | 20            |

Figure 1. ispClock5610 Functional Block Diagram

Figure 2. ispClock5620 Functional Block Diagram

# **Absolute Maximum Ratings**

|                                               | ispClock5600V |

|-----------------------------------------------|---------------|

| Core Supply Voltage V <sub>CCD</sub>          | 0.5 to 5.5V   |

| PLL Supply Voltage V <sub>CCA</sub>           | 0.5 to 5.5V   |

| JTAG Supply Voltage V <sub>CCJ</sub>          | 0.5 to 5.5V   |

| Output Driver Supply Voltage V <sub>CCO</sub> | 0.5 to 4.5V   |

| Input Voltage                                 | 0.5 to 4.5V   |

| Output Voltage <sup>1</sup>                   | 0.5 to 4.5V   |

| Storage Temperature                           | 65 to 150°C   |

| Junction Temperature with power supplied      | 40 to 130°C   |

1. When applied to an output when in high-Z condition

# **Recommended Operating Conditions**

|                      |                                   |                 | ispClod | k5600V |       |  |

|----------------------|-----------------------------------|-----------------|---------|--------|-------|--|

| Symbol               | Parameter                         | Conditions      | Min.    | Max.   | Units |  |

| V <sub>CCD</sub>     | Core Supply Voltage               |                 | 3.0     | 3.6    | V     |  |

| V <sub>CCJ</sub>     | JTAG I/O Supply Voltage           |                 | 1.62    | 3.6    | V     |  |

| $V_{CCA}$            | Analog Supply Voltage             |                 | 3.0     | 3.6    | V     |  |

| V <sub>CCXSLEW</sub> | V <sub>CC</sub> Turn-on Ramp Rate | All supply pins | _       | 0.33   | V/μs  |  |

| т.                   | Operating Junction Temperature    | Commercial      | 0       | 100    | °C    |  |

| T <sub>JOP</sub>     | Operating Junction Temperature    | Industrial      | -40     | 115    |       |  |

| т                    | Ambient Operating Temperature     | Commercial      | 0       | 70¹    | °C    |  |

| I'A                  | Ambient Operating Temperature     | Industrial      | -40     | 85¹    |       |  |

1. Device power dissipation may also limit maximum ambient operating temperature.

# Recommended Operating Conditions – $V_{CCO}$ vs. Logic Standard

|        |                  |       | V <sub>CCO</sub> (V) |       |      | V <sub>REF</sub> (V) |      |                         | V <sub>TT</sub> (V)    |                         |

|--------|------------------|-------|----------------------|-------|------|----------------------|------|-------------------------|------------------------|-------------------------|

| Logi   | ic Standard      | Min.  | Тур.                 | Max.  | Min. | Тур.                 | Max. | Min.                    | Тур.                   | Max.                    |

| LVTTL  |                  | 3.0   | 3.3                  | 3.6   | _    | _                    | _    | _                       | _                      | _                       |

| LVCMO  | S 1.8V           | 1.71  | 1.8                  | 1.89  | _    | _                    | _    | _                       | _                      | _                       |

| LVCMO  | S 2.5V           | 2.375 | 2.5                  | 2.625 | _    | _                    | _    | _                       | _                      | _                       |

| LVCMO  | S 3.3V           | 3.0   | 3.3                  | 3.6   | _    | _                    | _    | _                       | _                      | _                       |

| SSTL2  | Class 1          | 2.375 | 2.5                  | 2.625 | 1.15 | 1.25                 | 1.35 | V <sub>REF</sub> - 0.04 | _                      | V <sub>REF</sub> + 0.04 |

| SSTL3  | Class 1          | 3.0   | 3.3                  | 3.6   | 1.30 | 1.50                 | 1.70 | V <sub>REF</sub> - 0.05 | $V_{REF}$              | V <sub>REF</sub> + 0.05 |

| HSTL C | lass 1           | 1.425 | 1.5                  | 1.575 | 0.68 | 0.75                 | 0.90 | _                       | 0.5 x V <sub>CCO</sub> | _                       |

| LVPECI | L (Differential) | 3.0V  | 3.3V                 | 3.6V  | _    | _                    | _    | _                       | _                      | _                       |

| LVDS   | $V_{CCO} = 2.5V$ | 2.375 | 2.5V                 | 2.625 | _    | _                    | _    | _                       | _                      | _                       |

| LVDS   | $V_{CCO} = 3.3V$ | 3.0   | 3.3                  | 3.6   | _    | _                    | _    | _                       | _                      | _                       |

Note: '--' denotes V<sub>REF</sub> or V<sub>TT</sub> not applicable to this logic standard

# E<sup>2</sup>CMOS Memory Write/Erase Characteristics

| Parameter              | Conditions | Min. | Тур. | Max. | Units |

|------------------------|------------|------|------|------|-------|

| Erase/Reprogram Cycles |            | 1000 | _    | _    |       |

# **Performance Characteristics – Power Supply**

| Symbol           | Parameter                               | Parameter Conditions                                                                                                           |                       | Max.                | Units |

|------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|-------|

| I <sub>CCD</sub> | Core Supply Current                     | f <sub>VCO</sub> = 640MHz                                                                                                      | 150                   | 160                 | mA    |

| I <sub>CCA</sub> | Analog Supply Current                   | f <sub>VCO</sub> = 640MHz                                                                                                      | 5.5                   | 7                   | mA    |

| I <sub>cco</sub> | Output Driver Supply Current (per Bank) | $V_{CCO} = 1.8V^{1}$ , LVCMOS<br>$V_{CCO} = 2.5V^{1}$ , LVCMOS<br>$V_{CCO} = 3.3V^{1}$ , LVCMOS<br>$V_{CCO} = 3.3V^{2}$ , LVDS | 13<br>18<br>24<br>7.5 | 15<br>24<br>35<br>8 | mA    |

| I <sub>CCJ</sub> | JTAG I/O Supply Current (static)        | $V_{CCJ} = 1.8V$<br>$V_{CCJ} = 2.5V$<br>$V_{CCJ} = 3.3V$                                                                       | 200<br>300<br>300     | 300<br>400<br>400   | μΑ    |

1. Supply current consumed by each bank, both outputs active, 18pF load, 320MHz output frequency.

2. Supply current consumed by each bank,  $100\Omega$ , 5pf differential load, 320MHz output frequency.

# DC Electrical Characteristics – Single-ended Logic

|                   | V <sub>I</sub> | V <sub>IL</sub> (V)     |                         | V <sub>IH</sub> (V) |                          |                                      |                      |                      |

|-------------------|----------------|-------------------------|-------------------------|---------------------|--------------------------|--------------------------------------|----------------------|----------------------|

| Logic Standard    | Min.           | Max.                    | Min.                    | Max.                | V <sub>OL</sub> Max. (V) | V <sub>OH</sub> Min. (V)             | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) |

| LVTTL/LVCMOS 3.3V | -0.3           | 0.8                     | 2                       | 3.6                 | 0.4                      | V <sub>CCO</sub> - 0.4               | 4 <sup>1</sup>       | -4 <sup>1</sup>      |

| LVCMOS 1.8V       | -0.3           | 0.35V <sub>CCO</sub>    | 0.65V <sub>CCO</sub>    | 3.6                 | 0.4                      | V <sub>CCO</sub> - 0.4               | 4 <sup>1</sup>       | -4 <sup>1</sup>      |

| LVCMOS 2.5V       | -0.3           | 0.7                     | 1.7                     | 3.6                 | 0.4                      | V <sub>CCO</sub> - 0.4               | 4 <sup>1</sup>       | -4 <sup>1</sup>      |

| SSTL2 Class 1     | -0.3           | V <sub>REF</sub> - 0.18 | V <sub>REF</sub> + 0.18 | 3.6                 | 0.54 <sup>2</sup>        | V <sub>CCO</sub> - 0.81 <sup>2</sup> | 7.6                  | -7.6                 |

| SSTL3 Class 1     | -0.3           | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                 | 0.9 <sup>2</sup>         | V <sub>CCO</sub> - 1.3 <sup>2</sup>  | 8                    | -8                   |

| HSTL Class 1      | -0.3           | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6                 | 0.43                     | V <sub>CCO</sub> - 0.4 <sup>3</sup>  | 8                    | -8                   |

1. Specified for  $50\Omega$  internal series output termination.

2. Specified for  $40\Omega$  internal series output termination.

3. Specified for  $\approx$ 20 $\Omega$  internal series output termination.

# **DC Electrical Characteristics – LVDS**

| Symbol           | Parameter                                 | Conditions                                    | Min.  | Тур.  | Max.  | Units |

|------------------|-------------------------------------------|-----------------------------------------------|-------|-------|-------|-------|

| V <sub>ICM</sub> | Common Mode Input Voltage                 |                                               | 0.05  | _     | 2.35  | V     |

| $V_{THD}$        | Differential Input Threshold              |                                               | ±100  | _     | _     | mV    |

| V <sub>IN</sub>  | Input Voltage                             |                                               | 0     | _     | 2.4   | V     |

| V <sub>OH</sub>  | Output High Voltage                       | $R_T = 100\Omega$                             | _     | 1.375 | 1.60  | V     |

| V <sub>OL</sub>  | Output Low Voltage                        | $R_T = 100\Omega$                             | 0.9   | 1.03  | _     | V     |

| V <sub>OD</sub>  | Output Voltage Differential               | $R_T = 100\Omega$                             | 250   | 400   | 480   | mV    |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between H and L |                                               | _     | _     | 50    | mV    |

| V <sub>OS</sub>  | Output Voltage Offset                     | Common Mode Output Voltage                    | 1.125 | 1.20  | 1.375 | V     |

| $\Delta V_{OS}$  | Change in V <sub>OS</sub> Between H and L |                                               | _     | _     | 50    | mV    |

| I <sub>SA</sub>  | Output Short Circuit Current              | V <sub>OD</sub> = 0V, Outputs Shorted to GND  | _     | _     | 24    | mA    |

| I <sub>SAB</sub> | Output Short Circuit Current              | $V_{OD} = 0V$ , Outputs Shorted to Each Other | _     | _     | 12    | mA    |

# **DC Electrical Characteristics – Differential LVPECL**

| Symbol                                          | Parameter                         | Test Conditions                          | Min.                    | Тур. | Max.                    | Units      |

|-------------------------------------------------|-----------------------------------|------------------------------------------|-------------------------|------|-------------------------|------------|

| V                                               | Input Voltago High                | $V_{CCO} = 3.0 \text{ to } 3.6 \text{V}$ | V <sub>CCO</sub> - 1.17 | _    | V <sub>CCO</sub> - 0.88 | V          |

| V <sub>IH</sub> Input Voltage High              |                                   | $V_{CCO} = 3.3V$                         | 2.14                    | _    | 2.42                    | , v        |

| V <sub>IL</sub>                                 | Input Voltage Low                 | $V_{CCO} = 3.0 \text{ to } 3.6 \text{V}$ | V <sub>CCO</sub> - 1.81 | _    | V <sub>CCO</sub> - 1.48 | V          |

| VIL                                             | V <sub>IL</sub> Imput voltage Low | $V_{CCO} = 3.3V$                         | 1.49                    | _    | 1.83                    | ] <b>'</b> |

| V <sub>OH</sub>                                 | Output High Voltage <sup>1</sup>  | $V_{CCO} = 3.0 \text{ to } 3.6 \text{V}$ | V <sub>CCO</sub> - 1.07 | _    | V <sub>CCO</sub> - 0.88 | V          |

| VOH                                             | Output High Voltage               | $V_{CCO} = 3.3V$                         | 2.23                    | _    | 2.42                    | ] <b>'</b> |

| V <sub>OI</sub> Output Low Voltage <sup>1</sup> |                                   | $V_{CCO} = 3.0 \text{ to } 3.6 \text{V}$ | V <sub>CCO</sub> - 1.81 | _    | V <sub>CCO</sub> - 1.62 | V          |

| V <sub>OL</sub>                                 | Output Low voltage                | V <sub>CCO</sub> = 3.3V                  | 1.49                    | _    | 1.68                    | ] <b>'</b> |

1.  $100\Omega$  differential termination.

# DC Electrical Characteristics – Input/Output Loading

| Symbol                            | Parameter               | Conditions    | Min. | Тур. | Max. | Units |

|-----------------------------------|-------------------------|---------------|------|------|------|-------|

| I <sub>LK</sub>                   | Input Leakage           | Note 1        | _    | _    | ±10  | μΑ    |

| I <sub>PU</sub>                   | Input Pull-up Current   | Note 2        | _    | 80   | 120  | μΑ    |

| I <sub>PD</sub>                   | Input Pull-down Current | Note 3        | _    | 120  | 150  | μΑ    |

| I <sub>OLK</sub>                  | Tristate Leakage Output | Note 4        | _    | _    | ±10  | μΑ    |

| C <sub>IN</sub> Input Capacitance | Input Canacitance       | Notes 2, 3, 5 | _    | 8    | 10   | pF    |

|                                   |                         | Note 6        | _    | 13.5 | 15   | pF    |

1. Applies to clock reference inputs when termination 'open'.

2. Applies to TDI, TMS inputs.

3. Applies to REFSEL, PS0, PS1,  $\overline{\text{GOE}}$ , SGATE and PLL\_BYPASS.

Applies to all logic types when in tristated mode.

Applies to OEX, OEY, TCK, RESET inputs.

6. Applies to REFA+, REFA-, REFB+, REFB-, FBKA+, FBKA-, FBKB+, FBKB-.

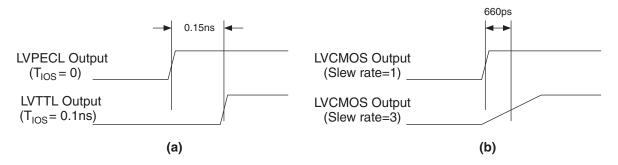

# **Switching Characteristics – Timing Adders for I/O Modes**

| Adder Type                                    | Description                             | Min.  | Тур. | Max. | Units |

|-----------------------------------------------|-----------------------------------------|-------|------|------|-------|

| t <sub>IOI</sub> Input Adders <sup>2</sup>    |                                         | •     |      |      |       |

| LVTTL_in                                      | Using LVTTL Standard                    | 0     | 0    | 0    | ns    |

| LVCMOS18_in                                   | Using LVCMOS 1.8V Standard              | 0.20  | 0.45 | 0.70 | ns    |

| LVCMOS25_in                                   | Using LVCMOS 2.5V Standard              | 0     | 0    | 0    | ns    |

| LVCMOS33_in                                   | Using LVCMOS 3.3V Standard              | 0     | 0    | 0    | ns    |

| SSTL2_in                                      | Using SSTL2 Standard                    | 1.15  | 1.35 | 1.60 | ns    |

| SSTL3_in                                      | Using SSTL3 Standard                    | 1.15  | 1.35 | 1.60 | ns    |

| HSTL_in                                       | Using HSTL Standard                     | 1.15  | 1.35 | 1.60 | ns    |

| LVDS_in                                       | Using LVDS Standard                     | 1.15  | 1.35 | 1.60 | ns    |

| LVPECL_in                                     | Using LVPECL Standard                   | 1.15  | 1.35 | 1.60 | ns    |

| t <sub>IOO</sub> Output Adders <sup>1,3</sup> |                                         |       |      | •    |       |

| LVTTL_out                                     | Output Configured as LVTTL Buffer       | -0.10 | 0.15 | 0.45 | ns    |

| LVCMOS18_out                                  | Output Configured as LVCMOS 1.8V Buffer | -0.15 | 0.15 | 0.55 | ns    |

| LVCMOS25_out                                  | Output Configured as LVCMOS 2.5V Buffer | -0.10 | 0.15 | 0.45 | ns    |

| LVCMOS33_out                                  | Output Configured as LVCMOS 3.3V Buffer | -0.10 | 0.15 | 0.45 | ns    |

| SSTL2_out                                     | Output Configured as SSTL2 Buffer       | -0.10 | 0.15 | 0.45 | ns    |

| SSTL3_out                                     | Output Configured as SSTL3 Buffer       | -0.10 | 0.15 | 0.45 | ns    |

| HSTL_out                                      | Output Configured as HSTL Buffer        | 0     | 0.15 | 0.45 | ns    |

| LVDS_out                                      | Output Configured as LVDS Buffer        | 0     | 0    | 0    | ns    |

| LVPECL_out                                    | Output Configured as LVPECL Buffer      | 0     | 0    | 0    | ns    |

| t <sub>IOS</sub> Output Slew Rate             | Adders <sup>1</sup>                     |       |      |      |       |

| Slew_1                                        | Output Slew_1 (Fastest)                 | _     | 0    | _    | ps    |

| Slew_2                                        | Output Slew_2                           | _     | 330  | _    | ps    |

| Slew_3                                        | Output Slew_3                           | _     | 660  | _    | ps    |

| Slew_4                                        | Output Slew_4 (Slowest)                 | _     | 1320 | _    | ps    |

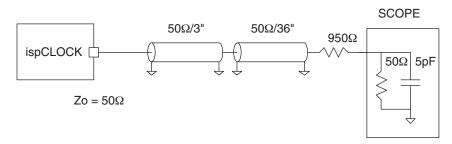

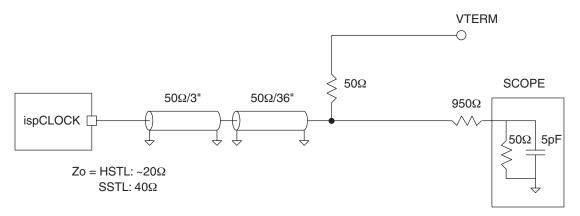

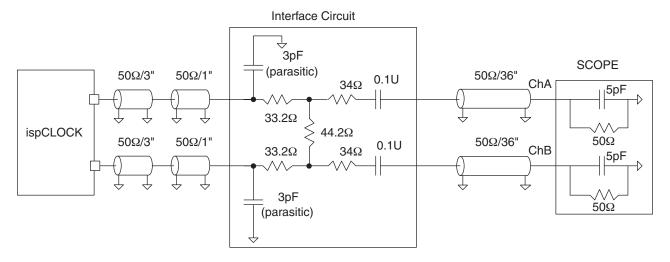

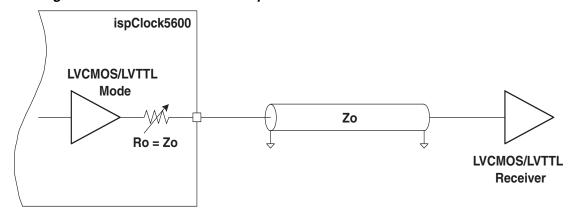

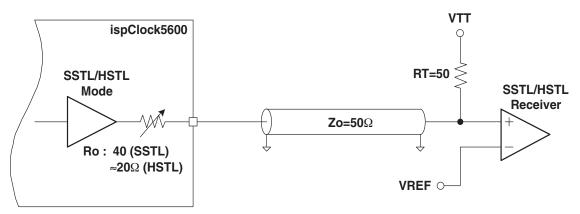

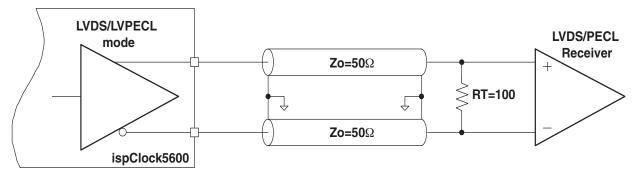

1. Measured under standard output load conditions – see Figures 3-5.

2. All input adders referenced to LVTTL.

3. All output adders referenced to LVPECL.

# Output Rise and Fall Times – Typical Values<sup>1, 2</sup>

|                     | Slew 1 (Fastest) |                | Sle            | Slew 2         |                | Slew 3         |                | Slew 4 (Slowest) |       |

|---------------------|------------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|-------|

| Output Type         | t <sub>R</sub>   | t <sub>F</sub> | t <sub>R</sub> | t <sub>F</sub> | t <sub>R</sub> | t <sub>F</sub> | t <sub>R</sub> | t <sub>F</sub>   | Units |

| LVTTL               | 0.65             | 0.45           | 0.85           | 0.60           | 1.20           | 0.90           | 1.75           | 1.30             | ns    |

| LVCMOS 1.8V         | 0.90             | 0.40           | 1.05           | 0.50           | 1.40           | 0.80           | 2.00           | 1.20             | ns    |

| LVCMOS 2.5V         | 0.70             | 0.40           | 0.90           | 0.55           | 1.20           | 0.85           | 1.80           | 1.20             | ns    |

| LVCMOS 3.3V         | 0.65             | 0.45           | 0.85           | 0.60           | 1.20           | 0.90           | 1.75           | 1.30             | ns    |

| SSTL2               | 0.65             | 0.40           | 0.90           | 0.60           | 1.35           | 0.85           | 2.30           | 1.40             | ns    |

| SSTL3               | 0.65             | 0.40           | 0.90           | 0.60           | 1.35           | 0.85           | 2.30           | 1.40             | ns    |

| HSTL                | 0.85             | 0.30           | 1.00           | 0.50           | 1.50           | 0.70           | 2.55           | 1.10             | ns    |

| LVDS <sup>3</sup>   | 0.25             | 0.20           | _              | _              | _              | _              | _              | _                | ns    |

| LVPECL <sup>3</sup> | 0.20             | 0.20           | _              | _              | _              | _              | _              | _                | ns    |

1. See Figures 3-5 for test conditions.

2. Measured between 20% and 80% points.

3. Only the 'fastest' slew rate is available in LVDS and LVPECL modes.

# **Output Test Loads**

Figures 3-5 show the equivalent termination loads used to measure rise/fall times, output timing adders and other selected parameters as noted in the various tables of this data sheet.

Figure 3. CMOS Termination Load

Figure 4. HSTL/SSTL Termination Load

Figure 5. LVDS/LVPECL Termination Load

# **Programmable Input and Output Termination Characteristics**

| Symbol           | Parameter         | Conditions                  | Min. | Тур. | Max. | Units |

|------------------|-------------------|-----------------------------|------|------|------|-------|

|                  |                   | Rin=40Ω setting             | 36   | _    | 44   |       |

|                  |                   | Rin=45Ω setting             | 40.5 | _    | 49.5 |       |

|                  |                   | Rin=50Ω setting             | 45   | _    | 55   |       |

| R <sub>IN</sub>  | Input Resistance  | Rin=55Ω setting             | 49.5 | _    | 60.5 | Ω     |

|                  |                   | Rin=60Ω setting             | 54   | _    | 66   |       |

|                  |                   | Rin=65Ω setting             | 59   | _    | 71.5 |       |

|                  |                   | Rin=70Ω setting             | 61   | _    | 77   |       |

|                  |                   | Rout≈20Ω setting, VCCO=1.5V | _    | 27   | _    |       |

|                  |                   | Rout≈20Ω setting, VCCO=1.8V | _    | 22   | _    |       |

|                  |                   | Rout≈20Ω setting, VCCO=2.5V | _    | 20   | _    |       |

|                  |                   | Rout≈20Ω setting, VCCO=3.3V | _    | 18   | _    |       |

|                  |                   | Rout=40Ω setting            | 34   | _    | 47   |       |

| R <sub>OUT</sub> | Output Resistance | Rout=45Ω setting            | 38   | _    | 55   | Ω     |

|                  |                   | Rout=50Ω setting            | 43   | _    | 61   |       |

|                  |                   | Rout=55Ω setting            | 47   | _    | 67   |       |

|                  |                   | Rout=60Ω setting            | 51   | _    | 72   |       |

|                  |                   | Rout=65Ω setting            | 55   | _    | 78   | 1     |

|                  |                   | Rout=70Ω setting            | 61   | _    | 83   |       |

# **Performance Characteristics – PLL**

| Symbol                                        | Parameter                                                    | Conditions                                                                                                     | Min.  | Тур. | Max. | Units              |

|-----------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------|------|------|--------------------|

| f <sub>REF,</sub> f <sub>FBK</sub>            | Reference and feedback input frequency range                 |                                                                                                                | 10    | _    | 320  | MHz                |

| t <sub>CLOCKHI,</sub><br>t <sub>CLOCKLO</sub> | Reference and feedback input clock HIGH and LOW times        |                                                                                                                | 1.25  | _    | _    | ns                 |

| t <sub>RINP,</sub><br>t <sub>FINP</sub>       | Reference and feedback input rise and fall times             | Measured between 20% and 80% levels                                                                            | _     | _    | 5    | ns                 |

| M <sub>DIV</sub>                              | M-divider range                                              |                                                                                                                | 1     | _    | 32   |                    |

| N <sub>DIV</sub>                              | N-Divider range                                              |                                                                                                                | 1     | _    | 32   |                    |

| f <sub>PFD</sub>                              | Phase detector input frequency range <sup>2</sup>            |                                                                                                                | 10    | _    | 320  | MHz                |

| f <sub>VCO</sub>                              | VCO operating frequency                                      |                                                                                                                | 320   | _    | 640  | MHz                |

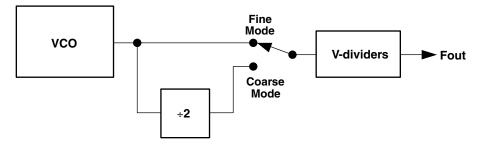

| V <sub>DIV</sub>                              | Output Divider range                                         | Even integer values only                                                                                       | 2     | _    | 64   |                    |

| f                                             | Output frequency range <sup>1</sup>                          | Fine Skew Mode,<br>f <sub>VCO</sub> = 640MHz                                                                   | 10    | _    | 320  | MHz                |

| f <sub>OUT</sub>                              | Output frequency range                                       | Coarse Skew Mode,<br>f <sub>VCO</sub> = 640MHz                                                                 | 5     | _    | 160  | MHz                |

| t <sub>JIT</sub> (cc)                         | Output adjacent-cycle jitter                                 | 1000 cycle sample <sup>3</sup>                                                                                 | _     | 45   | 60   | ps (p-p)           |

| t <sub>JIT</sub> (per)                        | Output period jitter                                         | 10000 cycle sample <sup>3</sup>                                                                                | _     | 8    | 10   | ps (RMS)           |

| +4                                            | Static phase offset                                          | PFD input frequency ≥100MHz <sup>7</sup>                                                                       | -375  | -75  | 225  | ps                 |

| tφ                                            | Static priase offset                                         | PFD input frequency <100MHz <sup>7</sup>                                                                       | -37.5 | _    | 22.5 | mUI <sup>6</sup>   |

| t <sub>DELAY</sub>                            | Reference clock to output delay                              | Internal feedback mode <sup>7</sup>                                                                            | 0.3   | 0.45 | 0.6  | ns                 |

|                                               | Output duty cycle error (see                                 | Output type LVDS, V <sub>CCO</sub> = 3.3V <sup>5</sup>                                                         | _     | _    | 260  | ps                 |

| DC <sub>ERR</sub>                             | Table 3 for nominal values) <sup>4</sup>                     | Output type LVCMOS 3.3V <sup>5</sup> f <sub>OUT</sub> >100 MHz                                                 | _     | _    | 300  | ps                 |

| t <sub>PDBYPASS</sub>                         | Reference clock to output propagation delay                  | M=1, V=2                                                                                                       | _     | 6    | _    | ns                 |

|                                               | PLL Lock time                                                | From Power-up event                                                                                            | _     | 150  | 500  | μs                 |

| $t_L$                                         | FLL LOCK UITIE                                               | From Reset event                                                                                               | _     | 15   | 50   | μs                 |

| PSR                                           | Power supply rejection, period jitter vs. power supply noise | f <sub>IN</sub> = f <sub>OUT</sub> = 100MHz<br>VCCA = VCCD = VCCO modulated<br>with 100kHz sinusoidal stimulus | _     | 0.05 | _    | ps(RMS)<br>mV(p-p) |

1. In PLL Bypass mode (PLL\_BYPASS = HIGH), output will support frequencies down to 0Hz (divider chain is a fully static design).

2. Dividers should be set so that they provide the phase detector with signals of 10MHz or greater for loop stability.

f<sub>IN</sub> = f<sub>OUT</sub> = 100 MHz, M = N = 1, V = 6, output type LVPECL.

Variation in duty cycle expressed in ps. To obtain duty cycle percentage error (%<sub>ERR</sub>) for a given output frequency (f<sub>OUT</sub>), %<sub>ERR</sub> = 100 x f<sub>OUT</sub> x DC<sub>ERR</sub>.

See Figures 3-5 for output loads.

6. milli-Unit Interval

7. Input and outputs LVPECL mode

# **Timing Specifications**

### **Skew Matching**

| Symbol            | Parameter | Conditions                                                                    | Min. | Тур. | Max. | Units |

|-------------------|-----------|-------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>SKEW</sub> |           | Between any two identically configured and loaded outputs regardless of bank. | _    | _    | 50   | ps    |

### **Programmable Skew Control**

| Symbol               | Parameter                       | Conditions                                   | Min. | Тур.  | Max. | Units |  |

|----------------------|---------------------------------|----------------------------------------------|------|-------|------|-------|--|

|                      |                                 | Fine Skew Mode, f <sub>VCO</sub> = 320 MHz   | _    | 5.86  | _    |       |  |

| +                    | Skew Control Range <sup>1</sup> | Fine Skew Mode, f <sub>VCO</sub> = 640 MHz   | _    | 2.93  | _    |       |  |

| <sup>T</sup> SKRANGE | Skew Control hange              | Coarse Skew Mode, f <sub>VCO</sub> = 320 MHz | _    | 11.72 | _    | ns    |  |

|                      |                                 | Coarse Skew Mode, f <sub>VCO</sub> = 640 MHz | _    | 5.86  | _    |       |  |

| SK <sub>STEPS</sub>  | Skew Steps per range            |                                              | _    | 16    | _    |       |  |

|                      |                                 | Fine Skew Mode, f <sub>VCO</sub> = 320 MHz   | _    | 390   | _    | ps    |  |

| <b>+</b>             | Skew Step Size <sup>2</sup>     | Fine Skew Mode, f <sub>VCO</sub> = 640 MHz   | _    | 195   | _    |       |  |

| <sup>t</sup> SKSTEP  | Skew Step Size                  | Coarse Skew Mode, f <sub>VCO</sub> = 320 MHz | _    | 780   | _    |       |  |

|                      |                                 | Coarse Skew Mode, f <sub>VCO</sub> = 640 MHz | _    | 390   | _    |       |  |

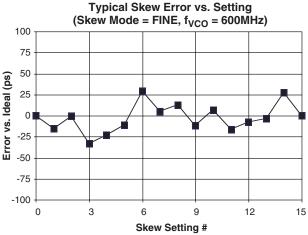

| t <sub>SKERR</sub>   | Skew Time Error <sup>3</sup>    | Fine skew mode                               | _    | 30    | _    | ps    |  |

|                      | Skew Tillle Effor               | Coarse skew mode                             | _    | 50    | _    |       |  |

- 1. Skew control range is a function of VCO frequency (f<sub>VCO</sub>). In fine skew mode T<sub>SKRANGE</sub> = 15/(8 x f<sub>VCO</sub>). In coarse skew mode  $T_{SKRANGE} = 15/(4 \text{ x f}_{VCO})$ .

- 2. Skew step size is a function of VCO frequency ( $f_{VCO}$ ). In fine skew mode  $T_{SKSTEP} = 1/(8 \text{ x } f_{VCO})$ . In coarse skew mode  $T_{SKSTEP} = 1/(4 \text{ x f}_{VCO})$ .

3. Only applicable to outputs with non-zero skew settings.

#### **Control Functions**

| Symbol                | Parameter Conditions                                  |  |    | Тур. | Max. | Units               |

|-----------------------|-------------------------------------------------------|--|----|------|------|---------------------|

| t <sub>DIS/OE</sub>   | Delay Time, OEX or OEY to Output Disabled/<br>Enabled |  | _  | 10   | 20   | ns                  |

| t <sub>DIS/GOE</sub>  | Delay Time, GOE to Output Disabled/Enabled            |  | _  | 10   | 20   | ns                  |

| t <sub>SUSGATE</sub>  | Setup Time, SGATE to Output Clock Start/<br>Stop      |  | 3  | _    | _    | cycles <sup>1</sup> |

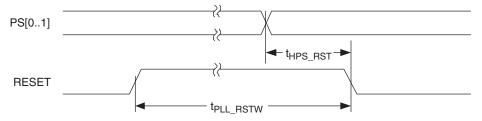

| t <sub>PLL_RSTW</sub> | PLL Reset Pulse Width <sup>2</sup>                    |  | 1  | _    | _    | ms                  |

| t <sub>RSTW</sub>     | Logic Reset Pulse Width <sup>3</sup>                  |  | 20 | _    | _    | ns                  |

| t <sub>HPS_RST</sub>  | Hold time for RESET past change in PS[01]             |  | 20 | _    | _    | ns                  |

- 1. Output clock cycles for the particular output being controlled.

- 2. Will completely reset PLL.

- 3. Will only reset digital logic.

Figure 6. RESET and Profile Select Timing

# **Timing Specifications (Cont.)**

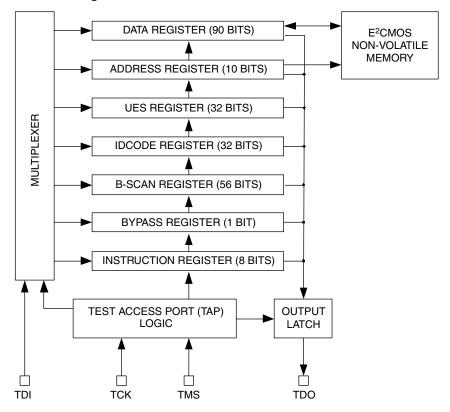

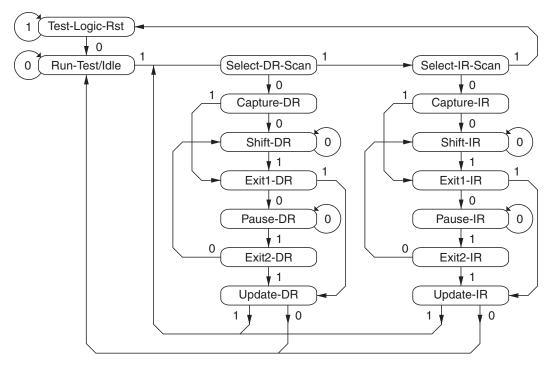

# **Boundary Scan Logic**

| Symbol               | Parameter                                                           | Min. | Max. | Units |

|----------------------|---------------------------------------------------------------------|------|------|-------|

| t <sub>BTCP</sub>    | TCK (BSCAN Test) Clock Cycle                                        | 40   | _    | ns    |

| t <sub>BTCH</sub>    | TCK (BSCAN Test) Pulse Width High                                   | 20   | _    | ns    |

| t <sub>BTCL</sub>    | TCK (BSCAN Test) Pulse Width Low                                    | 20   | _    | ns    |

| t <sub>BTSU</sub>    | TCK (BSCAN Test) Setup Time                                         | 8    | _    | ns    |

| t <sub>BTH</sub>     | TCK (BSCAN Test) Hold Time                                          | 10   | _    | ns    |

| t <sub>BRF</sub>     | TCK (BSCAN Test) Rise and Fall Rate                                 | 50   | _    | mV/ns |

| t <sub>BTCO</sub>    | TAP Controller Falling Edge of Clock to Valid Output                | _    | 10   | ns    |

| t <sub>BTOZ</sub>    | TAP Controller Falling Edge of Clock to Data Output Disable         | _    | 10   | ns    |

| t <sub>BTVO</sub>    | TAP Controller Falling Edge of Clock to Data Output Enable          | _    | 10   | ns    |

| t <sub>BVTCPSU</sub> | BSCAN Test Capture Register Setup Time                              | 8    | _    | ns    |

| t <sub>BTCPH</sub>   | BSCAN Test Capture Register Hold Time                               | 10   | _    | ns    |

| t <sub>BTUCO</sub>   | BSCAN Test Update Register, Falling Edge of Clock to Valid Output   | _    | 25   | ns    |

| t <sub>BTUOZ</sub>   | BSCAN Test Update Register, Falling Edge of Clock to Output Disable | _    | 25   | ns    |

| t <sub>BTUOV</sub>   | BSCAN Test Update Register, Falling Edge of Clock to Output Enable  | _    | 25   | ns    |

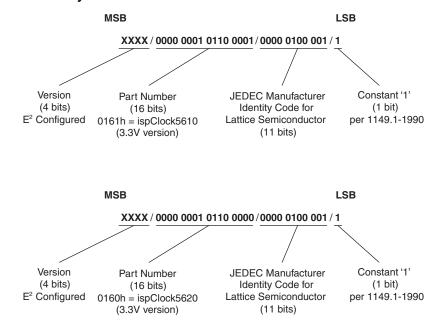

# **JTAG Interface and Programming Mode**

| Symbol              | Parameter                            | Condition | Min. | Тур. | Max. | Units |

|---------------------|--------------------------------------|-----------|------|------|------|-------|

| f <sub>MAX</sub>    | Maximum TCK Clock Frequency          |           | _    | _    | 25   | MHz   |

| t <sub>CKH</sub>    | TCK Clock Pulse Width, High          |           | 20   | _    | _    | ns    |

| t <sub>CKL</sub>    | TCK Clock Pulse Width, Low           |           | 20   | _    | _    | ns    |

| t <sub>ISPEN</sub>  | Program Enable Delay Time            |           | 15   | _    | _    | μs    |

| t <sub>ISPDIS</sub> | Program Disable Delay Time           |           | 30   | _    | _    | μs    |

| t <sub>HVDIS</sub>  | High Voltage Discharge Time, Program |           | 30   | _    | _    | μs    |

| t <sub>HVDIS</sub>  | High Voltage Discharge Time, Erase   |           | 200  | _    | _    | μs    |

| t <sub>CEN</sub>    | Falling Edge of TCK to TDO Active    |           | _    | _    | 15   | ns    |

| t <sub>CDIS</sub>   | Falling Edge of TCK to TDO Disable   |           | _    | _    | 15   | ns    |

| t <sub>SU1</sub>    | Setup Time                           |           | 8    | _    | _    | ns    |

| t <sub>H</sub>      | Hold Time                            |           | 10   | _    | _    | ns    |

| t <sub>CO</sub>     | Falling Edge of TCK to Valid Output  |           | _    | _    | 15   | ns    |

| t <sub>PWV</sub>    | Verify Pulse Width                   |           | 30   | _    | _    | μs    |

| t <sub>PWP</sub>    | Programming Pulse Width              |           | 10   | _    | _    | ms    |

| t <sub>BEW</sub>    | Bulk Erase Pulse Width               |           | 200  | _    | _    | ms    |

# **Timing Diagrams**

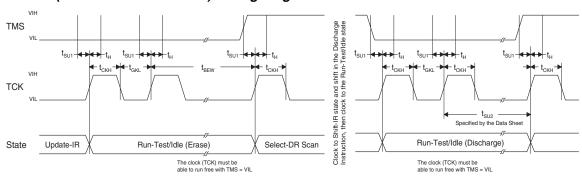

Figure 7. Erase (User Erase or Erase All) Timing Diagram

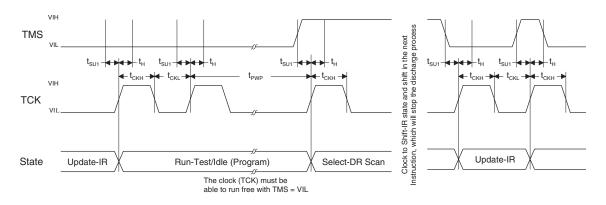

Figure 8. Programming Timing Diagram

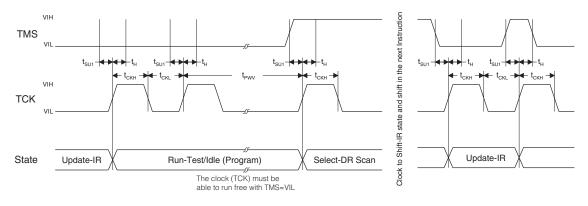

Figure 9. Verify Timing Diagram

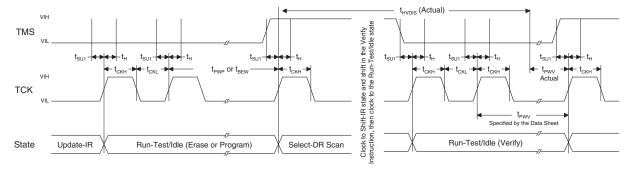

Figure 10. Discharge Timing Diagram

### **Typical Performance Characteristics**

# **Detailed Description**

### **PLL Subsystem**

The ispClock5600 provides an integral phase-locked-loop (PLL) which may be used to generate output clock signals at lower, higher, or the same frequency as a user-supplied input reference signal. The core functions of the PLL are an edge-sensitive phase detector, a programmable loop filter, and a high-speed voltage-controlled oscillator (VCO). Additionally, a set of programmable input, output and feedback dividers (M, N, V[1..5]) is provided to support the synthesis of different output frequencies.

#### **Phase/Frequency Detector**

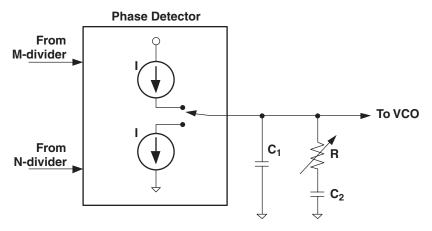

The ispClock5600 provides an edge-sensitive phase/frequency detector (PFD), which means that the device will function properly over a wide range of input clock reference duty cycles. It is only necessary that the input reference clock meet specified minimum HIGH and LOW times (t<sub>CLOCKHI</sub>, t<sub>CLOCKLO</sub>) for it to be properly recognized by the PFD. The PFD's output is of a classical charge-pump type, outputting charge packets which are then integrated by the PLL's loop filter.

A lock-detection feature is also associated with the PFD. When the ispClock5600 is in a LOCKED state, the  $\overline{\text{LOCK}}$  output pin goes LOW. The lock detector has two operating modes; phase lock mode and frequency lock mode. In phase-lock mode, the  $\overline{\text{LOCK}}$  signal is asserted if the phases of the reference and feedback signals match, whereas in frequency-lock mode the  $\overline{\text{LOCK}}$  signal is asserted when the frequencies of the feedback and reference signals

match. The option of which mode to use is programmable and may be set using PAC-Designer software (available from the Lattice web site at <a href="https://www.latticesemi.com">www.latticesemi.com</a>).

In phase-lock mode the lock detector asserts the  $\overline{\mathsf{LOCK}}$  signal as soon as a lock condition is determined. In frequency-lock mode, however, the PLL must be in a locked condition for a set number of phase detector cycles before the  $\overline{\mathsf{LOCK}}$  signal will be asserted. The number of cycles required before asserting the  $\overline{\mathsf{LOCK}}$  signal in frequency-lock mode can be set from 16 through 256.

When the lock condition is lost the  $\overline{LOCK}$  signal will be de-asserted immediately in both phase-lock and frequency-lock detection modes. In frequency-lock mode, however, if the input reference signal is stopped, the  $\overline{LOCK}$  output may continue to be asserted. In phase-lock mode, a loss of the input reference signal will always result in de-assertion of the  $\overline{LOCK}$  output.

#### **Loop Filter**

A simplified schematic for the ispClock5600 loop filter is shown in Figure 11. The filter's capacitors are fixed, and the response is controlled by setting the value of the phase-detector's output current source's and the value of the variable resistor. The phase detector output current has 14 possible settings, ranging from  $3\mu$ A to  $55\mu$ A, while the resistor may be set to any one of six values ranging from 2.3K to 9.3K. This provides a total of 84 unique I-R combinations which may be selected.

Figure 11. ispClock5600 Loop Filter (Simplified)

Because the selection of an optimal PLL loop filter can be a daunting task, PAC-Designer offers a set of default filter settings which will provide acceptable performance for most applications. The primary criterion for selecting one of these settings is the total division factor used in the feedback path, or the ratio between the VCO output frequency and the frequency output by the N feedback divider (N x V<sub>feedback</sub>). Table 2 lists these default settings and conditions under which they should be used.

Table 2. PAC-Designer Recommended Loop Filter Settings

| N x V <sub>FBK</sub> | Ι (μΑ) | <b>R</b> ( <b>k</b> Ω) |

|----------------------|--------|------------------------|

| 2 to 8               | 5      | 2.3                    |

| 10                   | 7      | 2.3                    |

| 12 to 14             | 9      | 2.3                    |

| 16                   | 11     | 2.3                    |

| 18 to 20             | 13     | 2.3                    |

| 22                   | 15     | 2.3                    |

| 24 to 26             | 17     | 2.3                    |

| 28                   | 19     | 2.3                    |

| 30                   | 21     | 2.3                    |

| 32 to 64             | 22     | 2.3                    |

Note that the choice of loop filter parameters can have significant effects on settling time, output jitter, and whether the PLL will be fundamentally stable and be able to lock to an incoming signal. The values recommended in Table 2 were chosen to provide maximum loop stability while still providing exceptional jitter performance. Please note that when the skew mode is set to 'coarse', the effective value of NxV must be considered to have doubled. Refer to the section titled 'Coarse Skew Mode' on page 28 for further details.

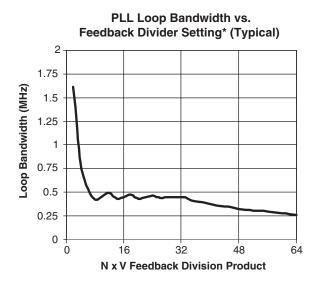

The PLL's loop bandwidth is a function of both the divider configuration and the loop filter settings. Figure 12 shows the loop bandwidth as a function of the total feedback division ratio (N x V<sub>FBK</sub>). For each NxV feedback divider point in this plot, the PLL loop filter was set to the corresponding value recommended in Table 2. The use of non-recommended loop filter settings may result in significantly different bandwidths for a given NxV divider setting.

Figure 12. PLL Loop Bandwidth vs. Feedback Divider Setting (nominal)

\*loop filter configured to recommended setting

#### **VCO**

The ispClock5600 provides an internal VCO which provides an output frequency ranging from 320MHz to 640MHz. The VCO is implemented using differential circuit design techniques which minimize the influence of power supply noise on measured output jitter. The VCO is also used to generate skews as a function of the total VCO period. Using the VCO as the basis for controlling output skew allows for highly precise and consistent skew generation, both from device-to-device, as well as channel-to-channel within the same device.

#### M. N. and V Dividers

The ispClock5600 incorporates a set of programmable dividers which provide the ability to synthesize output frequencies differing from that of the reference clock input.

The input, or M divider prescales the input reference frequency, and can be programmed with integer values over the range of 1 to 32. To achieve low levels of output jitter, it is best to use the smallest M divider value possible.

The feedback, or N divider prescales the feedback frequency and like the M divider, can also be programmed with integer values ranging from 1 to 32.

Each one of the five output, or V dividers can be independently programmed to provide even division ratios ranging from 2 to 64.

When the PLL is selected (PLL\_BYPASS=LOW) and locked, the output frequency of each V divider  $(f_k)$  may be calculated as:

$$f_{k} = f_{ref} \frac{N \times V_{fbk}}{M \times V_{k}}$$

(1)

where

fk is the frequency of V divider k

f<sub>ref</sub> is the input reference frequency

M and N are the input and feedback divider settings

V<sub>fbk</sub> is the setting of the V divider used to close the PLL feedback path

V<sub>k</sub> is the setting of the V divider used to provide output k

Note that because the feedback may be taken from any V divider, V<sub>k</sub> and V<sub>fbk</sub> may refer to the same divider.

Because the VCO has an operating frequency range spanning 320 MHz to 640 MHz, and the V dividers provide division ratios from 2 to 64, the ispClock5600 can generate output signals ranging from 5MHz to 320 MHz. For performance and stability reasons, however, there are several constraints which should be followed when selecting divider values:

- Use the smallest feasible value for the M divider

- The output frequency from the M (and N) divider should be greater or equal to 10 MHz.

- The product of the N divider and the V divider used to close the PLL's feedback loop should be less than or equal to 64 (N x V<sub>fbk</sub> ≤ 64)

#### **Output Duty Cycle**

The ispClock5600's output duty cycle varies as a function of the V divider used to generate that output. If the V-divider setting is either 2 or a multiple of 4, the nominal output duty cycle will be exactly 50%. All other V divider settings will result in non-50% output duty cycles. Table 3 summarizes the nominal output duty cycle as a function of the V divider setting. Note that if the output is inverted, the duty cycle will be equal to 100%-DC%, where DC% is the duty cycle indicated in the table. For example, with a V divider of 14, the non-inverted duty cycle from Table 3 will be 43%. For an inverted output, the duty cycle will be 100%-43% or 57%.

Table 3. Nominal Output Duty Cycle vs. V-Divider Setting

| Divider Settings<br>with 50% Output<br>Duty Cycle |     |  |  |  |

|---------------------------------------------------|-----|--|--|--|

| V                                                 | DC% |  |  |  |

| 2                                                 |     |  |  |  |

| 4                                                 |     |  |  |  |

| 8                                                 |     |  |  |  |

| 12                                                |     |  |  |  |

| 16                                                |     |  |  |  |

| 20                                                |     |  |  |  |

| 24                                                |     |  |  |  |

| 28                                                |     |  |  |  |

| 32                                                | 50  |  |  |  |

| 36                                                |     |  |  |  |

| 40                                                |     |  |  |  |

| 44                                                |     |  |  |  |

| 48                                                |     |  |  |  |

| 52                                                |     |  |  |  |

| 56                                                |     |  |  |  |

| 60                                                |     |  |  |  |

| 64                                                |     |  |  |  |

| Divider Settings with<br>Non-50% Output Duty<br>Cycles |     |  |  |  |

|--------------------------------------------------------|-----|--|--|--|

| V                                                      | DC% |  |  |  |

| 6                                                      | 33  |  |  |  |

| 10                                                     | 40  |  |  |  |

| 14                                                     | 43  |  |  |  |

| 18                                                     | 44  |  |  |  |

| 22                                                     | 45  |  |  |  |

| 26                                                     | 46  |  |  |  |

| 30                                                     | 47  |  |  |  |

| 34                                                     | 47  |  |  |  |

| 38                                                     | 47  |  |  |  |

| 42                                                     | 48  |  |  |  |

| 46                                                     | 48  |  |  |  |

| 50                                                     | 48  |  |  |  |

| 54                                                     | 48  |  |  |  |

| 58                                                     | 48  |  |  |  |

| 62                                                     | 48  |  |  |  |

|                                                        |     |  |  |  |

#### PLL\_BYPASS Mode

The PLL\_BYPASS mode is provided so that input reference signals can be coupled through to the outputs without using the PLL functions. When PLL\_BYPASS mode is enabled (PLL\_BYPASS=HIGH), the output of the M divider is routed directly to the inputs of the V dividers. In PLL\_BYPASS mode, the nominal values of the V dividers are halved, so that they provide division ratios ranging from 1 to 32. The output frequency for a given V divider ( $f_k$ ) will be determined by

$$f_{k} = \frac{f_{\text{ref}} \times 2}{M \times V_{k}} \tag{2}$$

Please note that PLL\_BYPASS mode is provided primarily for testing purposes. When PLL\_BYPASS mode is enabled, features such as lock detect and skew generation are unavailable.

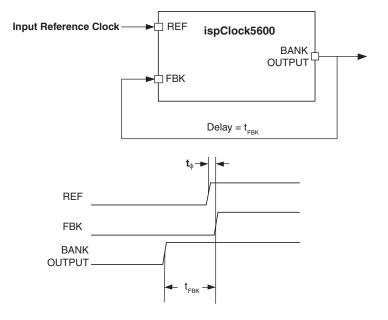

#### Reference and External Feedback Inputs

The ispClock5600 provide sets of configurable, internally-terminated inputs for both clock reference and feedback signals. In normal operation, the one of the clock reference input pairs (REFA+/- or REFB+/-) is used as a clock input.

The external feedback inputs make it possible to sample an output signal at the point of delivery. This makes it possible to provide output clocks which have very low skews in relation to the reference clock regardless of loading effects.

The ispClock5610 provides one input signal pair for reference input and one input pair for external feedback, while the ispClock5620 provides two pairs for reference signals and two pairs for feedback. To select between reference and feedback inputs, the ispClock5620 provides two CMOS-compatible digital inputs called REFSEL and FBKSEL. Table 4 shows the behavior of these two control inputs.

Table 4. REFSEL and FBKSEL Operation for ispClock5620

| REFSEL | Selected<br>Input Pair | FBKSEL | Selected<br>Input Pair |

|--------|------------------------|--------|------------------------|

| 0      | REFA+/-                | 0      | FBKA+/-                |

| 1      | REFB+/-                | 1      | FBKB+/-                |

- LVTTL (3.3V)

- LVCMOS (1.8V, 2.5V, 3.3V)

- SSTL2

- · SSTL3

- HSTL

- Differential SSTL2

- Differential SSTL3

- Differential HSTL

- LVDS

- LVPECL (differential, 3.3V)

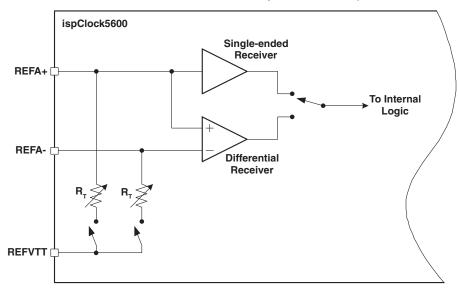

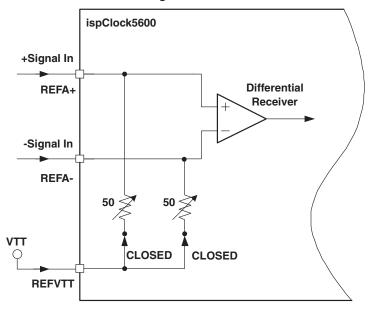

Each input also features internal programmable termination resistors, as shown in Figure 13. Note that all reference inputs (REFA+, REFA-, REFB+, REFB-) terminate to the REFVTT pin, while all feedback inputs (FBKA+, FBKB+, FBKB+, FBKB+) terminate to the FBKVTT pin.

Figure 13. ispClock5600 Clock Reference and Feedback Input Structure (REFA+/- Pair Shown)

The following usage guidelines are suggested for interfacing to supported logic families.

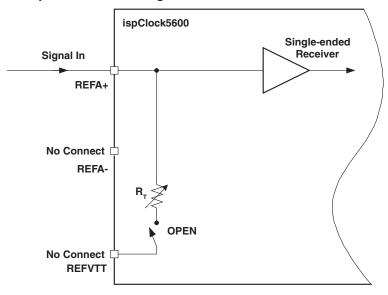

#### LVTTL (3.3V), LVCMOS (1.8V, 2.5V, 3.3V)

The receiver should be set to LVCMOS or LVTTL mode, and the input signal should be connected to the '+' terminal of the input pair (e.g. REFA+). The '-' input terminal should be left floating. CMOS transmission lines are generally source terminated, so all termination resistors should be set to the OPEN state. Figure 14 shows the proper configuration. Please note that because switching thresholds are different for LVCMOS running at 1.8V, there is a separate configuration setting for this particular standard.

Figure 14. LVCMOS/LVTTL Input Receiver Configuration

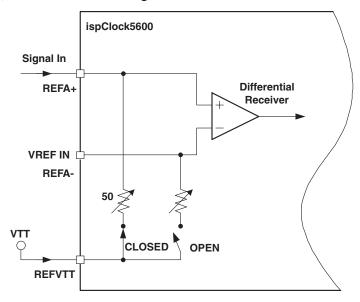

#### HSTL, SSTL2, SSTL3

The receiver should be set to HSTL/SSTL mode, and the input signal should be fed into the '+' terminal of the input pair. The '-' input terminal should be tied to the appropriate  $V_{REF}$  value, and the associated REFVTT or FBKVTT terminal should be tied to a  $V_{TT}$  termination supply. The positive input's terminating resistor should be engaged and set to  $50\Omega$ . Figure 15 shows an appropriate configuration. Refer to the "Recommended Operating Conditions - Supported Logic Standards" table in this data sheet for suitable values of  $V_{REF}$  and  $V_{TT}$ .

One important point to note is that the termination supplies must have low impedance and be able to both source and sink current without experiencing fluctuations. These requirements generally preclude the use of a resistive divider network, which has an impedance comparable to the resistors used, or of commodity-type linear voltage regulators, which can only source current. The best way to develop the necessary termination voltages is with a regulator specifically designed for this purpose. Because SSTL and HSTL logic is commonly used for high-performance memory busses, a suitable termination voltage supply is often already available in the system.

Figure 15. SSTL2, SSTL3, HSTL Receiver Configuration

#### **Differential HSTL and SSTL**

HSTL and SSTL are sometimes used in a differential form, especially for distributing clocks in high-speed memory systems. Figure 16 shows how ispClock5600 reference input should be configured for accepting these standards. The major difference between differential and single-ended forms of these logic standards is that in the differential case, the REFA- input is used as a signal input, not a reference level, and that both terminating resistors are engaged and set to  $50\Omega$ .

Figure 16. Differential HSTL/SSTL Receiver Configuration

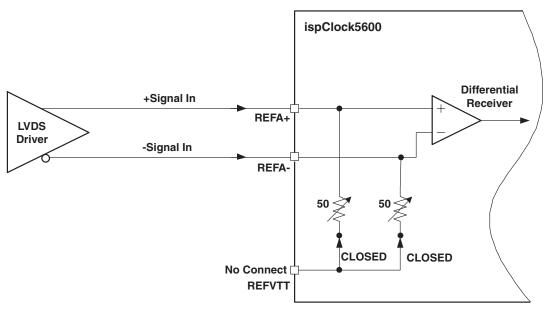

#### LVDS/Differential LVPECL

The receiver should be set to LVDS or LVPECL mode as required and both termination resistors should be engaged and set to  $50\Omega$ . The associated REFVTT or FBKVTT pin, however, should be left unconnected. This creates a floating  $100\Omega$  differential termination resistance across the input terminals. The LVDS termination configuration is shown in Figure 17.

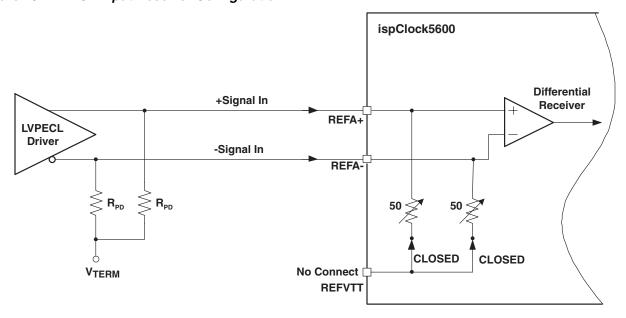

Figure 17. LVDS Input Receiver Configuration

Note that while a floating  $100\Omega$  resistor forms a complete termination for an LVDS signal line, additional circuitry may be required to satisfactorily terminate a differential LVPECL signal. This is because a true bipolar LVPECL output driver typically requires an external DC 'pull-down' path to a  $V_{TERM}$  termination voltage (typically VCC-2V) to properly bias its open emitter output stage. When interfacing to an LVPECL input signal, the ispClock5600's internal termination resistors should not be used for this pull-down function, as they may be damaged from excessive current. The pull-down should be implemented with external resistors placed close to the LVPECL driver (Figure 18)

Figure 18. LVPECL Input Receiver Configuration

Please note that while the above discussions specify using  $50\Omega$  termination impedances, the actual impedance required to properly terminate the transmission line and maintain good signal integrity may vary from this ideal. The actual impedance required will be a function of the driver used to generate the signal and the transmission medium used (PCB traces, connectors and cabling). The ispClock5600's ability to adjust input impedance over a range of  $40\Omega$  to  $70\Omega$  allows the user to adapt his circuit to non-ideal behaviors from the rest of the system without having to swap out components.

#### **Output Drivers**

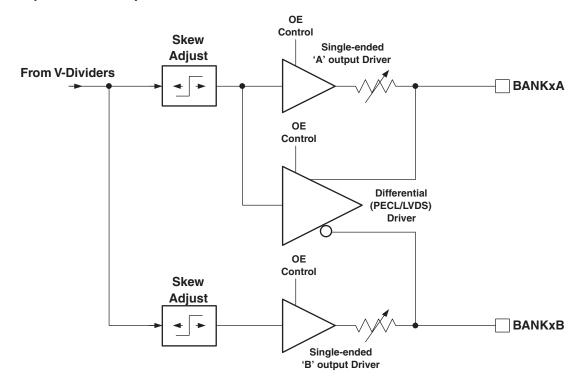

The ispClock5600 provide banks of configurable, internally-terminated high-speed dual-output line drivers. The ispClock5610 provides five driver banks, while the ispClock5620 provides ten. Each of these driver banks may be configured to provide either a single differential output signal, or a pair of single-ended output signals. Programmable internal source-series termination allows the ispClock5600 to be matched to transmission lines with impedances ranging from 40 to 70 Ohms. The outputs may be independently enabled or disabled, either from E²CMOS configuration or by external control lines. Additionally, each can be independently programmed to provide a fixed amount of signal delay or skew, allowing the user to compensate for the effects of unequal PCB trace lengths or loading effects. Figure 19 shows a block diagram of a typical ispClock5600 output driver bank and associated skew control.

Because of the high edge rates which can be generated by the ispClock5600's clock output drivers, the VCCO power supply pin for each output bank should be individually bypassed. Low ESR capacitors with values ranging from 0.01 to 0.1  $\mu$ F may be used for this purpose. Each bypass capacitor should be placed as close to its respective output bank power pins (VCCO and GNDO) pins as is possible to minimize interconnect length and associated parasitic inductances.

In the case where an output bank is unused, the associated VCCO pin may be either left floating or tied to ground to reduce quiescent power consumption. We recommend, however, that all unused VCCO pins be tied to ground where possible. All GND0 pins must be tied to ground, regardless of whether or not the associated bank is used.

Figure 19. ispClock5600 Output Driver and Skew Control

Each of the ispClock5600's output driver banks can be configured to support the following logic outputs:

- LVTTL

- LVCMOS (1.8V, 2.5V, 3.3V)

- SSTL2

- · SSTL3

- HSTL

- LVDS

- Differential LVPECL (3.3V)

To provide LVTTL, LVCMOS, SSTL2, SSTL3, and HSTL outputs, the CMOS output drivers in each bank are enabled. These circuits provide logic outputs which swing from ground to the VCCO supply rail. The choice of VCCO to be supplied to a given bank is determined by the logic standard to which that bank is configured. Because each pair of outputs has its own VCCO supply pin, each bank can be independently configured to support a different logic standard. Note that the two outputs associated with a bank must necessarily be configured to the same logic standard. The source impedance of each of the two outputs in each bank may be independently set over a range of  $40\Omega$  to  $70\Omega$  in  $5\Omega$  steps. A low impedance option ( $\approx 20\Omega$ ) is also provided for cases where low source termination is desired on a given output.

Control of output slew rate is also provided in LVTTL, LVCMOS, SSTL2, SSTL3, and HSTL output modes. Four output slew-rate settings are provided, as specified in the "Output Rise Times" and "Output Fall Times" tables in this data sheet.

To provide LVDS and differential LVPECL outputs, a separate internal driver is used which provides the correct LVDS or LVPECL logic levels when operating from a 3.3V VCCO. Because both LVDS and differential LVPECL transmission lines are normally terminated with a single  $100\Omega$  resistor between the '+' and '-' signal lines at the far

end, the ispClock5600's internal termination resistors are not available in these modes. Also note that output slew-rate control is not available in LVDS or LVPECL mode, and that these drivers always operate at a fixed slew-rate.

Polarity control (true/inverted) is available for all output drivers. In the case of single-ended output standards, the polarity of each of the two output signals from each bank may be controlled independently. In the case of differential output standards, the polarity of the differential pair may be selected.

#### **Suggested Usage**

Figure 20 shows a typical configuration for the ispClock5600's output driver when configured to drive an LVTTL or LVCMOS load. The ispClock5600's output impedance should be set to match the characteristic impedance of the transmission line being driven. The far end of the transmission line should be left open, with no termination resistors.

Figure 20. Configuration for LVTTL/LVCMOS Output Modes

Figure 21 shows a typical configuration for the ispClock5600's output driver when configured to drive SSTL2, SSTL3, or HSTL loads. The ispClock5600's output impedance should be set to  $40\Omega$  for driving SSTL2 or SSTL3 loads and to the  $\approx 20\Omega$  setting for driving HSTL. The far end of the transmission line must be terminated to an appropriate VTT voltage through a  $50\Omega$  resistor.

Figure 21. Configuration for SSTL2, SSTL3, and HSTL Output Modes

While supporting single-ended HSTL and SSTL outputs, the ispClock5600 does not support differential HSTL or SSTL outputs. Although complementary HSTL and SSTL signals may be generated by using both an inverted output and a non-inverted output similarly configured, the resulting signal pair may not meet the JEDEC differential HSTL specifications for common mode voltage or crossover voltage.

Figure 22 shows a typical configuration for the ispClock5600's output driver when configured to drive LVDS or differential LVPECL loads. The ispClock5600's output impedance is disengaged when the driver is set to LVDS or

LVPECL mode. The far end of the transmission line must be terminated with a  $100\Omega$  resistor across the two signal lines.

Figure 22. Configuration for LVDS and LVPECL Output Modes

Note that when in LVPECL output mode, the ispClock5600's output driver provides an internal pull-down, unlike a typical bipolar LVPECL driver. For this reason no external pull-down resistors are necessary and the driver may be terminated with a single  $100\Omega$  resistor across the signal lines. For proper operation, pull-down resistors should NOT be used with the ispClock5600's LVPECL output mode.

### **Thermal Management**

In applications where a majority of the ispClock5610 or ispClock5620's outputs are active and operating at or near maximum output frequency (320 MHz), package thermal limitations may need to be considered to ensure a successful design. Thermal characteristics of the packages employed by Lattice Semiconductor may be found in the document *Thermal Management* which may be obtained at <a href="https://www.latticesemi.com">www.latticesemi.com</a>.

The maximum current consumption of the digital and analog core circuitry is approximately 167mA worst case ( $I_{CCD} + I_{CCA}$ ), and each of the output banks may draw up to 35mA worst case (LVCMOS 3.3V, CL=18pF,  $f_{OUT}$ =320 MHz, both outputs in each bank enabled). This results in a total device dissipation:

$$P_{DMAX} = 3.3V \times (10 \times 35mA + 167mA) = 1.7W$$

(3)

With a maximum recommended operating junction temperature ( $T_{JOP}$ ) of 115°C for an industrial grade device, the maximum allowable ambient temperature ( $T_{AMAX}$ ) can be estimated as

$$T_{AMAX} = T_{JOP} - PD_{MAX} \times \Theta_{JA} = 115^{\circ}C - 1.7W \times 35^{\circ}C/W = 55^{\circ}C$$

(4)

where  $\Theta_{JA}$  = 35 °C/W in still air for the ispClock5620's TQFP100 package.

The above analysis represents the worst-case scenario. Significant improvement in maximum ambient operating temperature can be realized with additional cooling. Providing a 200 LFM (Linear Feet per Minute) airflow reduces  $\Theta_{JA}$  to 29°C/W, which results in a maximum ambient operating temperature of 66°C.

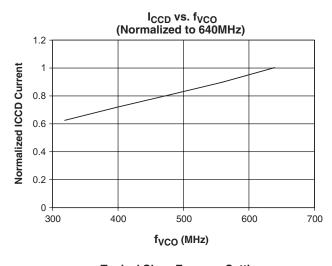

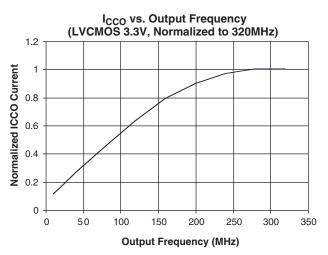

In practice, however, the absolute worst-case situation will be relatively rare, as not all outputs may be running at maximum output frequency in a given application. Additionally, if the internal VCO is operating at less than its maximum frequency (640MHz), it requires less current on the VCCD pin. In these situations, one can estimate the effective  $I_{CCO}$  for each bank and the effective  $I_{CCD}$  for the digital core functions based on output frequency and VCO frequency. Normalized curves relating current to operating frequency for these parameters may be found in the Typical Performance Characteristics section.

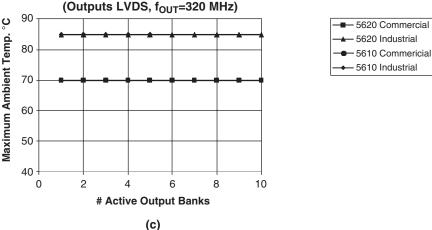

While it is possible to perform detailed calculations to estimate the maximum ambient operating temperature from operating conditions, some simpler rule-of-thumb guidance can also be obtained through the derating curves shown in Figure 23. The curves in Figure 23a show the maximum ambient operating temperature permitted when operating a given number of output banks at the maximum output frequency (320MHz). Note that it is assumed that both outputs in each bank are active.

**Temperature Derating Curves Temperature Derating Curves** (Outputs LVCMOS 3.3V, f<sub>OUT</sub>=320 MHz) (Outputs LVCMOS 3.3V, f<sub>OUT</sub>=100 MHz) 90 90 ပ ပ္ပ Maximum Ambient Temp. Maximum Ambient Temp. 70 60 50 50 40-0 6 10 10 # Active Output Banks # Active Output Banks (b) (a) **Temperature Derating Curves** (Outputs LVDS, f<sub>OUT</sub>=320 MHz) 90 ■ 5620 Commercial

Figure 23. Maximum Ambient Temperature vs. Number of Active Output Banks

Figure 23b shows another derating curve, derived under the assumption that the output frequency is 100MHz. For many applications, 100MHz outputs will be a more realistic scenario. Comparing the maximum temperature limits of Figure 23b with Figure 23a, one can see that significantly higher operating temperatures are possible in LVC-MOS 3.3V output mode with more outputs at 100MHz than at 320MHz.

The examples above used LVCMOS 3.3V logic, which represents the maximum power dissipation case at higher frequencies. For optimal operation at very high frequencies (> 150 MHz) LVDS will often be the best choice from a signal integrity standpoint. For LVDS-configured outputs, the maximum ICCO current consumption per bank is low enough that both the ispClock5610 and ispClock5620 can operate all outputs at maximum frequency over their complete rated temperature range, as shown in Figure 23c.

Note that because of variations in circuit board mounting, construction, and layout, as well as convective and forced airflow present in a given design, actual die operating temperature is subject to considerable variation from that which may be theoretically predicted from package characteristics and device power dissipation.

#### **Output Enable Controls**

The ispClock5600 family provides the user with several options for enabling and disabling output pins, as well as suspending the output clock. In addition to providing the user with the ability to reduce the device's power con-

sumption by turning off unused drivers, these features can also be used for functional testing purposes. The following inputs pins are used for output enable functions:

- GOE global output enable

- OEX, OEY secondary output enable controls

- SGATE synchronous output control

Additionally, internal E<sup>2</sup>CMOS configuration bits are provided for the purpose of modifying the effects of these external control pins.

When GOE is HIGH, all output drivers are forced into a high-Z state, regardless of any internal configuration. When GOE is LOW, the output drivers may also be enabled or disabled on an individual basis, and optionally controlled by the OEX and OEY pins. Internal E<sup>2</sup>CMOS configuration is used to establish whether the output driver is always enabled (when GOE pin is LOW), never enabled (permanently off), or selectively enabled by the state of either OEX or OEY. Bringing GOE high will also disable the internal feedback driver and will result in a loss of lock.

Synchronous output gating is provided by ispClock5600 devices through the use of the SGATE pin. The SGATE pin does not disable the output driver, but merely forces the output to either a high or low state, depending on the output driver's polarity setting. If the output driver polarity is true, the output will be forced LOW when SGATE is brought LOW, while if it is inverted, the output will be forced HIGH. A primary feature of the SGATE function is that the clock output is enabled and disabled synchronous to the selected internal clock source. This prevents the generation of partial, 'runt', output clock pulses, which would otherwise occur with simple combinatorial gating schemes. The SGATE is available to all clock outputs and is selectable on a bank-by-bank basis.

Table 5 shows the behavior of the outputs for various combinations of the output enables, SGATE input, and E<sup>2</sup>CMOS configuration.

Table 5. Clock Output Enable Functions

| GOE | OEX | OEY | E <sup>2</sup> Configuration | Output    |

|-----|-----|-----|------------------------------|-----------|

| Х   | Х   | Х   | Always OFF                   | High-Z    |

| 0   | Х   | Х   | Always ON                    | Clock Out |

| 0   | 0   | Х   | Enable on OEX                | Clock Out |

| 0   | 1   | Х   | Enable on OEX                | High-Z    |

| 0   | Х   | 0   | Enable on OEY                | Clock Out |

| 0   | Х   | 1   | Enable on OEY                | High-Z    |

| 1   | Х   | Х   | n/a                          | High-Z    |

Table 6. SGATE Function

| SGATE | Bank Controlled by SGATE? | Output Polarity | Output         |

|-------|---------------------------|-----------------|----------------|

| Х     | NO                        | True            | Clock          |

| Х     | NO                        | Inverted        | Inverted Clock |

| 0     | YES                       | True            | LOW            |

| 0     | YES                       | Inverted        | HIGH           |

| 1     | YES                       | True            | Clock          |

| 1     | YES                       | Inverted        | Inverted Clock |

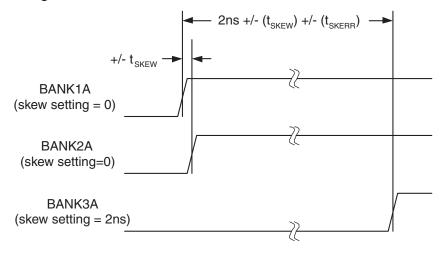

#### **Skew Control Units**

Each of the ispClock5600's clock outputs is supported by a skew control unit which allows the user to insert an individually programmable delay into each output signal. This feature is useful when it is necessary to de-skew clock signals to compensate for physical length variations among different PCB clock paths.

Unlike the skew adjustment features provided in many competing products, the ispClock5600's skew adjustment feature provides exact and repeatable delays which exhibit extremely low channel-to-channel and device-to-device variation. This is achieved by deriving all skew timing from the VCO, which results in the skew increment being a linear function of the VCO period. For this reason, skews are defined in terms of 'unit delays', which may be programmed by the user over a range of 0 to 15. The ispClock5600 family also supports both 'fine' and 'coarse' skew modes. In fine skew mode, the unit skew ranges from 195ps to 390 ps, while in the coarse skew mode unit skew varies from 390ps to 780ps. The exact unit skew (TU) may be calculated from the VCO frequency (f<sub>vco</sub>) by using the following expressions:

For fine skew mode, For coarse skew mode,

$$TU = \frac{1}{8f_{VCO}}$$

$$TU = \frac{1}{4f_{VCO}}$$

(5)

When an output driver is programmed to support a differential output mode, a single skew setting is applied to both the BANKxA+ and BANKxB- signals. When the output driver is configured to support a single-ended output standard, each of the two single-ended outputs may be assigned independent skews.

By using the internal feedback path, and programming a skew into the feedback skew control, it is possible to implement negative timing skews, in which the clock edge of interest appears at the ispClock5600's output before the corresponding edge is presented at the reference input. When the feedback skew unit is used in this way, the resulting negative skew is added to whatever skew is specified for each output. For example, if the feedback skew is set to 6TU, BANK1's skew is 8TU and BANK2's skew is 3TU, then BANK1's effective output skew will be 2TU (8TU-6TU), while BANK2's effective skew will be -3TU (3TU-6TU). This negative skew will manifest itself as BANK2's outputs appearing to lead the input reference clock, appearing as a negative propagation delay.

Please note that the skew control units are only usable when the PLL is selected. In PLL bypass mode (PLL\_BYPASS=1), output skew settings will be ineffective and all outputs will exhibit skew consistent with the device's propagation delay and the individual delays inherent in the output drivers consistent with the logic standard selected.

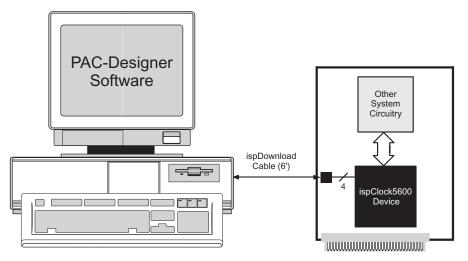

#### **Coarse Skew Mode**