# DC-to-DC Voltage Converter

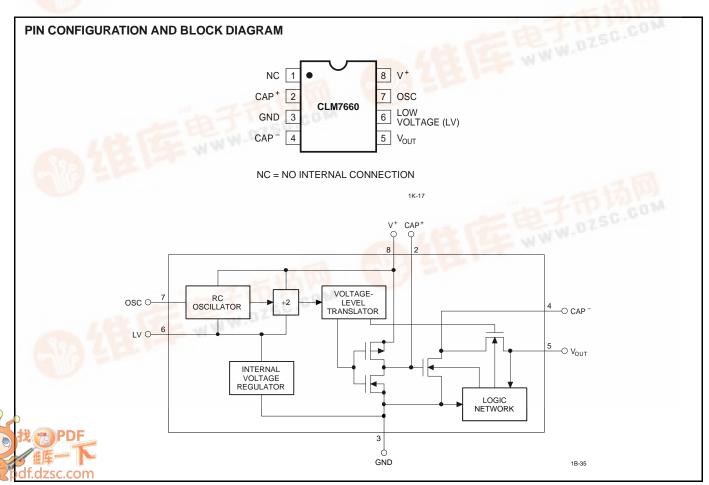

CLM7660

## **FEATURES**

| • | Converts +5V Logic Supply to ±5 System |     |                       |

|---|----------------------------------------|-----|-----------------------|

|   | Wide Input Voltage Range 1             | .5V | to 10\                |

| • | Low Power Supply                       |     | <b>500</b> μ <b>/</b> |

| • | Efficient Voltage Conversion           |     | 99.9%                 |

| • | RS232 Negative Power Supply            |     |                       |

| • | Low Cost, Simple to Use                |     |                       |

## **APPLICATIONS**

- A-to-D Converters

- D-to-A Converters

- Multiplexers

- Operational Amplifiers

## **DESCRIPTION**

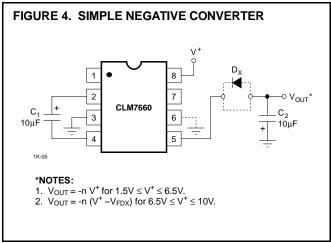

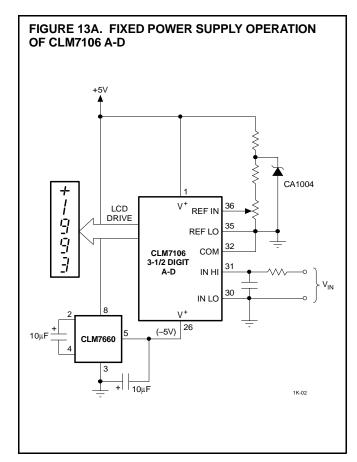

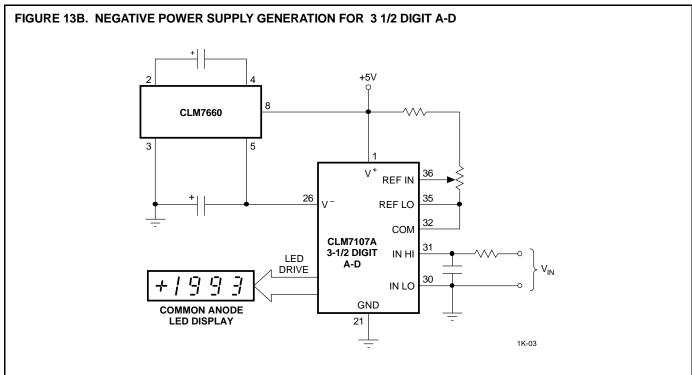

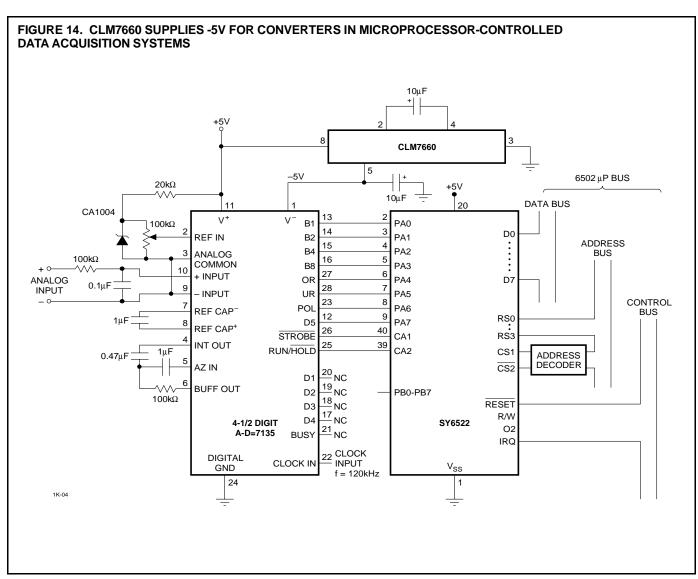

Calogic CLM7660 DC-to-DC converter will generate a negative voltage from a positive source. The CLM7660 generates -5V in +5V digital systems and with two external capacitors, the device will convert a 1.5V to 10V input signal to a -1.5V to -10V level.

Applications include analog-to-digital converters, digital-to-analog converters, operational amplifiers and multiplexers. Many of these systems require negative supply voltages. The CLM7660 allows +5V digital logic systems to incorporate these analog components without an additional main power source. Lower part count, less real estate, ease of use are just a few of the benefits of the CLM7660.

## **ORDERING INFORMATION**

| Part      | Package    | Temperature    |

|-----------|------------|----------------|

| CLM7660CP | 8 Pin DIP  | -40°C to +85°C |

| CLM7660DY | 8 Pin SOIC | -40°C to +85°C |

## CLM7660

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage+10.5V                                       |

|------------------------------------------------------------|

| LV and OSC Inputs                                          |

| Voltage (Note 1)                                           |

| for V <sup>+</sup> <5.5V                                   |

| $(V^{+}-5.5V)$ to $(V^{+}+0.3V)$                           |

| for V <sup>+</sup> <5.5V                                   |

| Current into LV (Note 1)                                   |

| Output Short Duration ( $V_{SUPPLY} \le 5.5V$ ) Continuous |

| Power Dissipation (Note 2)                                 |

| Plastic DIP                                                |

| Operating Temperature Range          |                |

|--------------------------------------|----------------|

| D Suffix                             | 40°C to +85°C  |

| Storage Temperature Range            | 65°C to +150°C |

| Lead Temperature (Soldering, 10 sec) | +300°C         |

Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

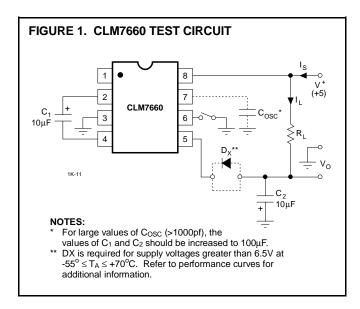

## **ELECTRICAL CHARACTERISTICS** $V^+ = 5V$ , $T_A = +25^{\circ}C$ , $C_{OSC} = 0$ , Test Circuit (Figure 1), unless otherwise indicated.

| SYMBOL            | PARAMETER                                                 | MIN | TYP  | MAX | UNIT | TEST CONDITIONS                                                                |

|-------------------|-----------------------------------------------------------|-----|------|-----|------|--------------------------------------------------------------------------------|

| I <sup>+</sup>    | Supply Current                                            | -   | 80   | 180 | μА   | R <sub>L</sub> = ∞                                                             |

| V <sup>+</sup> H1 | Supply Voltage Range, High                                | 3   | -    | 6.5 | V    | $0^{o}C \le T_{A} \le +70^{o}C$ , $R_{L} = 10k\Omega$ , LV Open                |

|                   |                                                           | 3   | -    | 5   | V    | -55°C ≤ T <sub>A</sub> ≤ +125°C, 10kΩ, LV Open                                 |

| V <sup>+</sup> L1 | Supply Voltage Range, Low (D <sub>X</sub> Out of Circuit) | 1.5 | -    | 3.5 | V    | $Min \leq T_A \leq Max, \ R_L = 10k\Omega, \ LV \ to \ GND$                    |

| V <sup>+</sup> H2 | Supply Voltage Range, High (D <sub>X</sub> In Circuit)    | 3   | -    | 10  | V    | $Min \leq T_A \leq Max, \ R_L = 10k\Omega, \ LV \ Open$                        |

| V <sup>+</sup> L2 | Supply Voltage Range, Low (D <sub>X</sub> In Circuit)     | 1.5 | -    | 3.5 | V    | $Min \leq T_A \leq Max, \ R_L = 10k\Omega, \ LV \ to \ GND$                    |

| Rout              | Output Source Resistance                                  | -   | 55   | 100 | Ω    | I <sub>OUT</sub> = 20mA, T <sub>A</sub> = 25°C                                 |

|                   |                                                           | -   | -    | 120 | Ω    | $I_{OUT} = 20$ mA, $0$ °C $\leq T_A \leq +70$ °C (C Device)                    |

|                   |                                                           | -   | -    | 300 | Ω    | $V^+ = 2V$ , $I_{OUT} = 3mA$ , LV to GND $0^{\circ}C \le T_A \le +70^{\circ}C$ |

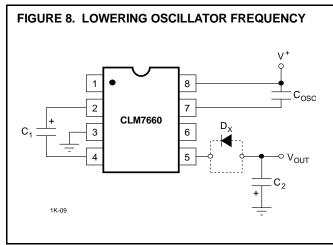

| fosc              | Oscillator Frequency                                      | -   | 10   | -   | kHz  |                                                                                |

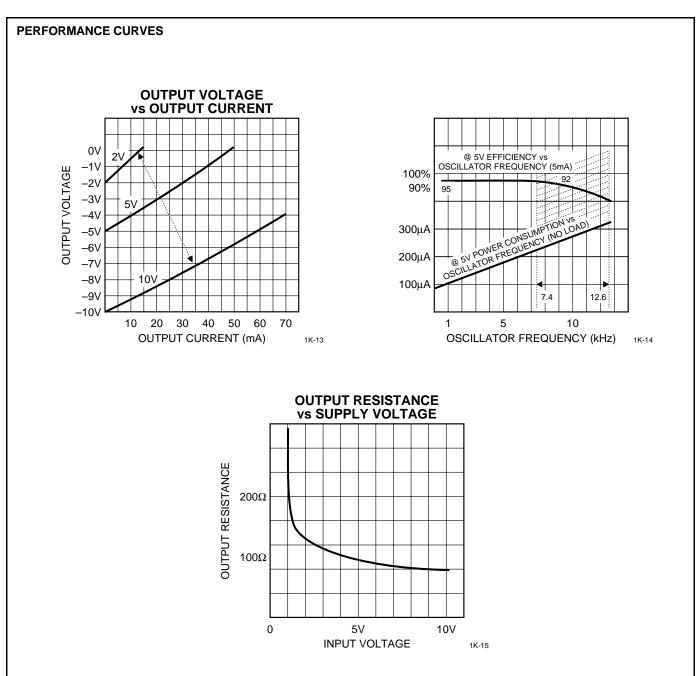

| PEF               | Power Efficiency                                          | 95  | 98   | -   | %    | $R_L = 5k\Omega$                                                               |

| Vout ef           | Voltage Conversion Efficiency                             | 97  | 99.9 | -   | %    | R <sub>L</sub> = ∞                                                             |

| Zosc              | Oscillator Impedance                                      | -   | 1    | -   | МΩ   | V <sup>+</sup> = 2V                                                            |

|                   |                                                           | -   | 100  | -   | kΩ   | V <sup>+</sup> = 5V                                                            |

## NOTES:

- 1. Connecting any input terminal to voltages greater than C+ or less than GND may cause destructive latch-up. It is recommended that no inputs from sources operating from external supplies be applied prior to "power up" of the CLM7660.

- 2. Derate linearly above 50°C by 5.5mW/°C.

## **CIRCUIT DESCRIPTION**

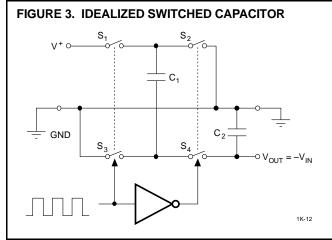

The CLM7660 is an excellent voltage doubler, the device has all the characteristic with the exception of two inexpensive  $10\mu F$  polarized electrolytic external capacitors. Figure 3 demonstrates the most effective means of using the device as a voltage doubler. Capacitor  $C_1$  is charged to a voltage, V+, for the half cycle when switches  $S_1$  and  $S_3$  are closed. (Note Switches  $S_2$  and  $S_4$  are open during this half cycle.) During the second half of the operation, switches  $S_2$  and  $S_4$  are closed, with  $S_1$  and  $S_3$  open, thereby shifting capacitor  $C_1$  negatively by V+ volts. Charge is then transferred from  $C_1$  to  $C_2$ , such that voltage on  $C_2$  is exactly V+, asumming ideal switches and no load on  $C_2$ .

The four switches in Figure 3 are MOS power switches,  $S_1$  is a P-Channel device,  $S_2$ ,  $S_3$  and  $S_4$  are N-Channel devices. The major challenge with this approach while integrating the switches, the substrates of  $S_3$  and  $S_4$  must always remain reversed-biased with respect to their sources, but not so much as to degrade their ON-resistances. In addition, at circuit start-up, and under short circuit conditions ( $V_{OUT}=V^+$ ), the output voltage must be sensed and the substrate bias adjusted accordingly. Failure to accomplish this will result in high power losses and probable device latch-up.

The above problem is eliminated in the CLM7660 by a logic network which senses the output voltage ( $V_{OUT}$ ) together with the level translators, and switches the substrates of  $S_3$  and  $S_4$  to the correct level to maintain necessary reverse bias.

The voltage regulator portion of the CLM7660 is an integral part of the anti-latch-up circuitry. Its inherent voltage drop can degrade operation at low voltages. To improve low-voltage operation, the LV pin should be connected to GND, disabling the regulator. For supply voltages greater than 3.5V, the LV terminal must be left open to ensure latch-up proof operation and prevent device damage.

## THEORETICAL POWER EFFICIENCY CONSIDERATIONS

In theory, a voltage multiplier can approach 100% efficiency if certain conditions are met:

- 1. The drive circuitry consumes minimal power.

- 2. The output switches have extremely low ON-resistance and virtually no offset.

- 3. The impedances of the pump and reservoir capacitors are negligible at the pump frequency.

When larger values of  $C_1$  and  $C_2$  are used, the CLM7660 approaches the above conditions for negative voltage multiplication. Energy is lost only if the transfer of the charge between capacitors if a change in voltage occurs. The energy lost is defined by:

$E=1/2C_1 (V_12-V_22)$

During the pump and transfer cycles  $V_1$  and  $V_2$  are the voltages on  $C_1$ . If the impedances of  $C_1$  and  $C_2$  are high at the pump frequency (see Figure 3), compared to the value of  $R_L$ , there will be a substantial difference in voltages  $V_1$  and  $V_2$ . The most optimum selection would be to make  $C_2$  as large as possible to eliminate output voltage ripple, and to utilize a large value for  $C_1$  to achieve maximum efficiency of operation.

#### **OPERATIONAL RULES:**

Never exceed maximum supply voltages.

Never connect LV terminal to GND for supply voltages over 3.5V.

Never short circuit the output to  $V^+$  supply voltages above 5.5V for extended periods; however, transient conditions including start-up are acceptable.

For polarized capacitors, the + terminal of  $C_1$  must be connected to pin 2 of the CLM7660 and the + terminal to of  $C_2$  must be connected to GND.

For high-voltage, elevated temperature applications add a diode  $D_X$  (reference Figure 1). The 1N914 diode is an appropriate choice.

# CLM7660