# **ML4803**

# 8-Pin PFC and PWM Controller Combo

### **GENERAL DESCRIPTION**

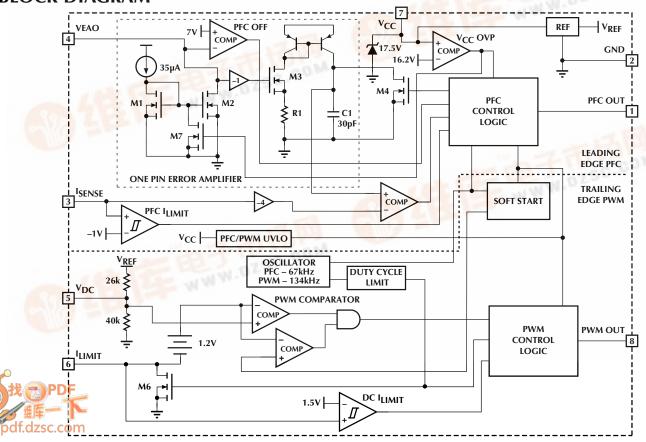

The ML4803 is a space-saving controller for power factor corrected, switched mode power supplies that offers very low start-up and operating currents.

Power Factor Correction (PFC) offers the use of smaller, lower cost bulk capacitors, reduces power line loading and stress on the switching FETs, and results in a power supply fully compliant to IEC1000-3-2 specifications. The ML4803 includes circuits for the implementation of a leading edge, average current "boost" type PFC and a trailing edge, PWM.

The ML4803-1's PFC and PWM operate at the same frequency, 67kHz. The PFC frequency of the ML4803-2 is automatically set at half that of the 134kHz PWM. This higher frequency allows the user to design with smaller PWM components while maintaining the optimum operating frequency for the PFC. An overvoltage comparator shuts down the PFC section in the event of a sudden decrease in load. The PFC section also includes peak current limiting for enhanced system reliability.

### **FEATURES**

- Internally synchronized PFC and PWM in one 8-pin IC

- Patented one-pin voltage error amplifier with advanced input current shaping technique

- Peak or average current, continuous boost, leading edge PFC (Input Current Shaping Technology)

- High efficiency trailing-edge current mode PWM

- Low supply currents; start-up: 150μA typ., operating: 2mA typ.

- Synchronized leading and trailing edge modulation

- Reduces ripple current in the storage capacitor between the PFC and PWM sections

- Overvoltage, UVLO, and brownout protection

- PFC V<sub>CC</sub>OVP with PFC Soft Start

### **BLOCK DIAGRAM**

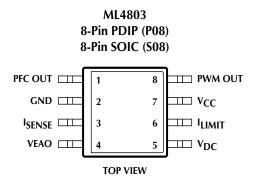

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN | NAME               | FUNCTION                                                | PIN | NAME               | FUNCTION                                                  |

|-----|--------------------|---------------------------------------------------------|-----|--------------------|-----------------------------------------------------------|

| 1   | PFC OUT            | PFC driver output                                       | 5   | $V_{DC}$           | PWM voltage feedback input                                |

| 2   | GND                | Ground                                                  | 6   | I <sub>LIMIT</sub> | PWM current limit comparator input                        |

| 3   | I <sub>SENSE</sub> | Current sense input to the PFC current limit comparator | 7   | $V_{CC}$           | Positive supply (may require an external shunt regulator) |

| 4   | VEAO               | PFC one-pin error amplifier input                       | 8   | PWM OUT            | PWM driver output                                         |

### **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| I <sub>CC</sub> Current (average)        | 40mA            |

|------------------------------------------|-----------------|

| V <sub>CC</sub> MAX                      |                 |

| I <sub>SENSE</sub> Voltage               | -5V to 1V       |

| Voltage on Any Other Pin GND - 0.3V to V | $I_{CC} + 0.3V$ |

| Peak PFC OUT Current, Source or Sink     | 1A              |

| Peak PWM OUT Current, Source or Sink     |                 |

| PFC OUT, PWM OUT Energy Per Cycle        | 1.5µJ           |

|                                          |                 |

| 150°C         |

|---------------|

| 65°C to 150°C |

| 260°C         |

|               |

| 110°C/W       |

| 160°C/W       |

|               |

### **OPERATING CONDITIONS**

| Temperature Range |              |

|-------------------|--------------|

| ML4803CX-X        | 0°C to 70°C  |

| ML4803IX-X        | 40°C to 85°C |

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, V<sub>CC</sub> = 15V, T<sub>A</sub> = Operating Temperature Range (Note 1)

| SYMBOL                  | PARAMETER             | CONDITIONS                                         | MIN      | TYP  | MAX   | UNITS |

|-------------------------|-----------------------|----------------------------------------------------|----------|------|-------|-------|

| ONE-PIN                 | ERROR AMPLIFIER       | ,                                                  | <b>-</b> | •    | 1     |       |

|                         | VEAO Output Current   | $T_A = 25^{\circ}C, V_{EAO} = 6V$                  | 33.5     | 35.0 | 36.5  | μA    |

|                         | Line Regulation       | 10V < V <sub>CC</sub> < 15V, V <sub>EAO</sub> = 6V |          | 0.1  | 0.3   | μΑ    |

| V <sub>CC</sub> OVP     | COMPARATOR            | ·                                                  |          |      |       |       |

|                         | Threshold Voltage     | $T_A = 0$ °C to 70°C                               | 15.5     | 16.0 | 16.5  | V     |

| PFC I <sub>LIMIT</sub>  | COMPARATOR            |                                                    |          |      |       |       |

|                         | Threshold Voltage     |                                                    | -0.9     | -1   | -1.15 | V     |

|                         | Delay to Output       |                                                    |          | 150  | 300   | ns    |

| DC I <sub>LIMIT</sub> ( | COMPARATOR            |                                                    | · ·      | •    | 1     |       |

|                         | Threshold Voltage     |                                                    | 1.4      | 1.5  | 1.6   | V     |

|                         | Delay to Output       |                                                    |          | 150  | 300   | ns    |

| OSCILLAT                | OR                    |                                                    |          |      |       |       |

|                         | Initial Accuracy      | T <sub>A</sub> = 25°C                              | 62       | 67   | 74    | kHz   |

|                         | Voltage Stability     | 10V < V <sub>CC</sub> < 15V                        |          | 1    |       | %     |

|                         | Temperature Stability |                                                    |          | 2    |       | %     |

|                         | Total Variation       | Over Line and Temp                                 | 60       | 67   | 74.5  | kHz   |

|                         | Dead Time             | PFC Only                                           | 0.3      | 0.45 | 0.65  | μs    |

| PFC                     |                       | ·                                                  |          |      |       |       |

|                         | Minimum Duty Cycle    | $V_{EAO} > 7.0V$ , $I_{SENSE} = -0.2V$             |          |      | 0     | %     |

|                         | Maximum Duty Cycle    | $V_{EAO} < 4.0V$ , $I_{SENSE} = 0V$                | 90       | 95   |       | %     |

|                         | Output Low Impedance  |                                                    |          | 8    | 15    | Ω     |

|                         | Output Low Voltage    | I <sub>OUT</sub> = -100mA                          |          | 0.8  | 1.5   | V     |

|                         |                       | I <sub>OUT</sub> = -10mA, V <sub>CC</sub> = 8V     |          | 0.7  | 1.5   | V     |

|                         | 1                     | <u> </u>                                           |          |      | 1     |       |

## **ELECTRICAL CHARACTERISTICS** (Continued)

| SYMBOL     | PARAMETER                                         | CONDITIONS                                      | MIN    | TYP  | MAX  | UNITS |

|------------|---------------------------------------------------|-------------------------------------------------|--------|------|------|-------|

| PFC (Conti | inued)                                            |                                                 |        |      |      |       |

|            | Output High Impedance                             |                                                 |        | 8    | 15   | Ω     |

|            | Output High Voltage                               | I <sub>OUT</sub> = 100mA, V <sub>CC</sub> = 15V | 13.5   | 14.2 |      | V     |

|            | Rise/Fall Time                                    | C <sub>L</sub> = 1000pF                         |        | 50   |      | ns    |

| PWM        |                                                   |                                                 |        |      |      |       |

|            | Duty Cycle Range                                  | TA = 0°C to 70°C, ML4803-2                      | 0-43   | 0-47 | 0-50 | %     |

|            |                                                   | TA = 0°C to 70°C, ML4803-1                      | 0-49.5 |      | 0-50 | %     |

|            | Output Low Impedance                              |                                                 |        | 8    | 15   | Ω     |

|            | Output Low Voltage                                | I <sub>OUT</sub> = -100mA                       |        | 0.8  | 1.5  | V     |

|            |                                                   | $I_{OUT} = -10$ mA, $V_{CC} = 8$ V              |        | 0.7  | 1.5  | V     |

|            | Output High Impedance                             |                                                 |        | 8    | 15   | Ω     |

|            | Output High Voltage                               | I <sub>OUT</sub> = 100mA, V <sub>CC</sub> = 15V | 13.5   | 14.2 |      | V     |

|            | Rise/Fall Time                                    | C <sub>L</sub> = 1000pF                         |        | 50   |      | ns    |

| SUPPLY     |                                                   |                                                 |        | 1    |      |       |

|            | V <sub>CC</sub> Clamp Voltage (V <sub>CCZ</sub> ) | I <sub>CC</sub> = 10mA                          | 16.7   | 17.5 | 18.3 | V     |

|            | Start-up Current                                  | V <sub>CC</sub> = 11V, C <sub>L</sub> = 0       |        | 0.2  | 0.4  | mA    |

|            | Operating Current                                 | V <sub>CC</sub> = 15V, C <sub>L</sub> = 0       |        | 2.5  | 4    | mA    |

|            | Undervoltage Lockout Threshold                    |                                                 | 11.5   | 12   | 12.5 | V     |

|            | Undervoltage Lockout Hysteresis                   |                                                 | 2.4    | 2.9  | 3.4  | V     |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

### **FUNCTIONAL DESCRIPTION**

The ML4803 consists of an average current mode boost Power Factor Corrector (PFC) front end followed by a synchronized Pulse Width Modulation (PWM) controller. It is distinguished from earlier combo controllers by its low pin count, innovative input current shaping technique, and very low start-up and operating currents. The PWM section is dedicated to peak current mode operation. It uses conventional trailing-edge modulation, while the PFC uses leading-edge modulation. This patented Leading Edge/ Trailing Edge (LETE) modulation technique helps to minimize ripple current in the PFC DC buss capacitor.

The ML4803 is offered in two versions. The ML4803-1 operates both PFC and PWM sections at 67kHz, while the ML4803-2 operates the PWM section at twice the frequency (134kHz) of the PFC. This allows the use of smaller PWM magnetics and output filter components, while minimizing switching losses in the PFC stage.

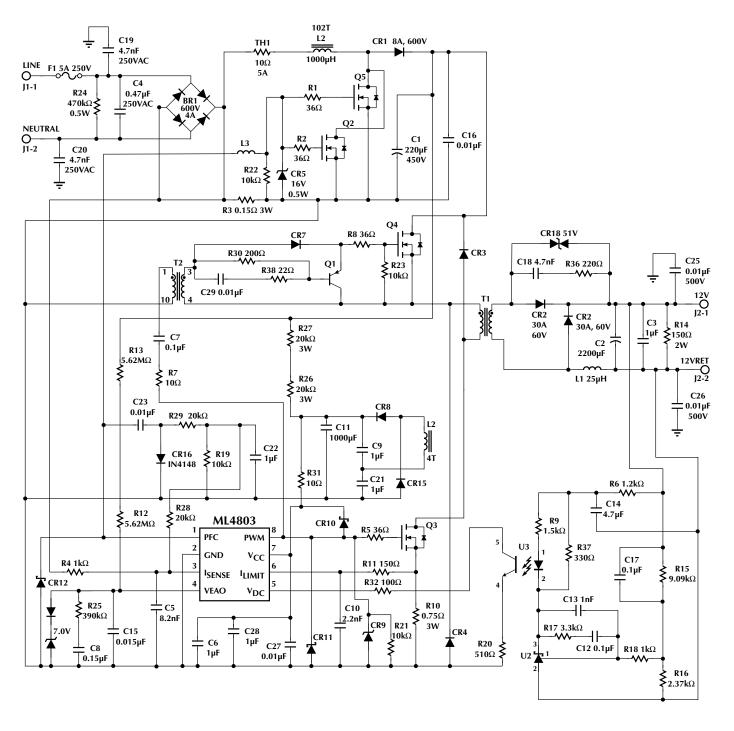

In addition to power factor correction, several protection features have been built into the ML4803. These include soft start, redundant PFC over-voltage protection, peak current limiting, duty cycle limit, and under voltage lockout (UVLO). See Figure 12 for a typical application.

#### **DETAILED PIN DESCRIPTIONS**

#### V<sub>EAO</sub>

This pin provides the feedback path which forces the PFC output to regulate at the programmed value. It connects to programming resistors tied to the PFC output voltage and is shunted by the feedback compensation network.

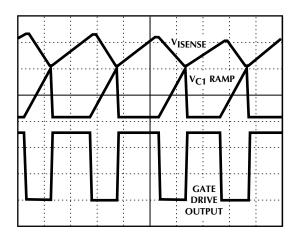

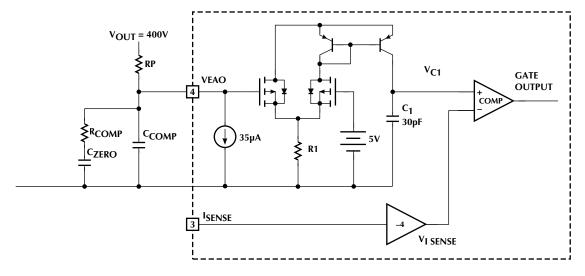

#### **ISENSE**

This pin ties to a resistor or current sense transformer which senses the PFC input current. This signal should be negative with respect to the IC ground. It internally feeds the pulse-by-pulse current limit comparator and the current sense feedback signal. The I<sub>LIMIT</sub> trip level is –1V. The I<sub>SENSE</sub> feedback is internally multiplied by a gain of four and compared against the internal programmed ramp to set the PFC duty cycle. The intersection of the boost inductor current downslope with the internal programming ramp determines the boost off-time.

### $V_{DC}$

This pin is typically tied to the feedback opto-collector. It is tied to the internal 5V reference through a  $26k\Omega$  resistor and to GND through a  $40k\Omega$  resistor.

### I<sub>LIMIT</sub>

This pin is tied to the primary side PWM current sense resistor or transformer. It provides the internal pulse-by pulse-current limit for the PWM stage (which occurs at 1.5V) and the peak current mode feedback path for the current mode control of the PWM stage. The current ramp

is offset internally by 1.2V and then compared against the opto feedback voltage to set the PWM duty cycle.

#### PFC OUT and PWM OUT

PFC OUT and PWM OUT are the high-current power drivers capable of directly driving the gate of a power MOSFET with peak currents up to  $\pm 1A$ . Both outputs are actively held low when  $V_{CC}$  is below the UVLO threshold level.

#### $V_{CC}$

$V_{CC}$  is the power input connection to the IC. The  $V_{CC}$  startup current is 150 $\mu$ A . The no-load I<sub>CC</sub> current is 2mA. V<sub>CC</sub> quiescent current will include both the IC biasing currents and the PFC and PWM output currents. Given the operating frequency and the MOSFET gate charge (Qg), average PFC and PWM output currents can be calculated as  $I_{OLIT} = Qg \times F$ . The average magnetizing current required for any gate drive transformers must also be included. The V<sub>CC</sub> pin is also assumed to be proportional to the PFC output voltage. Internally it is tied to the V<sub>CC</sub>OVP comparator (16.2V) providing redundant highspeed over-voltage protection (OVP) of the PFC stage. V<sub>CC</sub> also ties internally to the UVLO circuitry, enabling the IC at 12V and disabling it at 9.1V. V<sub>CC</sub> must be bypassed with a high quality ceramic bypass capacitor placed as close as possible to the IC. Good bypassing is critical to the proper operation of the ML4803.

$V_{CC}$  is typically produced by an additional winding off the boost inductor or PFC Choke, providing a voltage that is proportional to the PFC output voltage. Since the  $V_{CC}$ OVP max voltage is 16.2V, an internal shunt limits  $V_{CC}$  overvoltage to an acceptable value. An external clamp, such as shown in Figure 1, is desirable but not necessary.

$V_{CC}$  is internally clamped to 16.7V minimum, 18.3V maximum. This limits the maximum  $V_{CC}$  that can be applied to the IC while allowing a  $V_{CC}$  which is high

Figure 1. Optional V<sub>CC</sub> Clamp

### FUNCTIONAL DESCRIPTION (Continued)

enough to trip the  $V_{CC}$ OVP. The max current through this zener is 10mA. External series resistance is required in order to limit the current through this Zener in the case where the  $V_{CC}$  voltage exceeds the zener clamp level.

#### **GND**

GND is the return point for all circuits associated with this part. Note: a high-quality, low impedance ground is critical to the proper operation of the IC. High frequency grounding techniques should be used.

#### POWER FACTOR CORRECTION

Power factor correction makes a nonlinear load look like a resistive load to the AC line. For a resistor, the current drawn from the line is in phase with, and proportional to, the line voltage. This is defined as a unity power factor is (one). A common class of nonlinear load is the input of a most power supplies, which use a bridge rectifier and capacitive input filter fed from the line. Peak-charging effect, which occurs on the input filter capacitor in such a supply, causes brief high-amplitude pulses of current to flow from the power line, rather than a sinusoidal current in phase with the line voltage. Such a supply presents a power factor to the line of less than one (another way to state this is that it causes significant current harmonics to appear at its input). If the input current drawn by such a supply (or any other nonlinear load) can be made to follow the input voltage in instantaneous amplitude, it will appear resistive to the AC line and a unity power factor will be achieved.

To hold the input current draw of a device drawing power from the AC line in phase with, and proportional to, the

input voltage, a way must be found to prevent that device from loading the line except in proportion to the instantaneous line voltage. The PFC section of the ML4803 uses a boost-mode DC-DC converter to accomplish this. The input to the converter is the full wave rectified AC line voltage. No filtering is applied following the bridge rectifier, so the input voltage to the boost converter ranges, at twice line frequency, from zero volts to the peak value of the AC input and back to zero. By forcing the boost converter to meet two simultaneous conditions, it is possible to ensure that the current that the converter draws from the power line matches the instantaneous line voltage. One of these conditions is that the output voltage of the boost converter must be set higher than the peak value of the line voltage. A commonly used value is 385VDC, to allow for a high line of 270VAC<sub>RMS</sub>. The other condition is that the current that the converter is allowed to draw from the line at any given instant must be proportional to the line voltage.

Since the boost converter topology in the ML4803 PFC is of the current-averaging type, no slope compensation is required.

### LEADING/TRAILING MODULATION

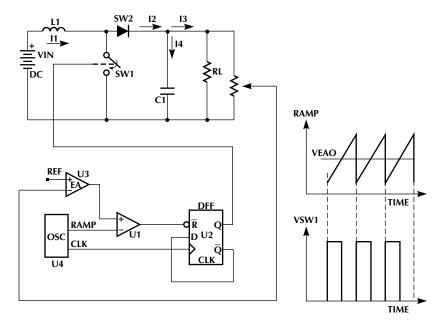

Conventional Pulse Width Modulation (PWM) techniques employ trailing edge modulation in which the switch will turn ON right after the trailing edge of the system clock. The error amplifier output voltage is then compared with the modulating ramp. When the modulating ramp reaches the level of the error amplifier output voltage, the switch will be turned OFF. When the switch is ON, the inductor

Figure 2. Typical Trailing Edge Control Scheme.

### LEADING/TRAILING MODULATION (Continued)

current will ramp up. The effective duty cycle of the trailing edge modulation is determined during the ON time of the switch. Figure 2 shows a typical trailing edge control scheme.

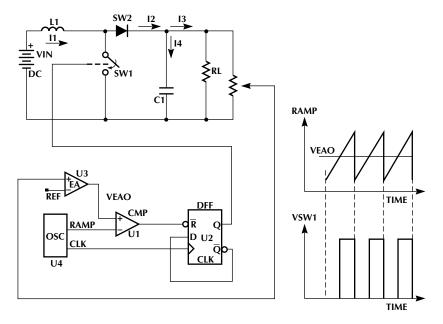

In the case of leading edge modulation, the switch is turned OFF right at the leading edge of the system clock. When the modulating ramp reaches the level of the error amplifier output voltage, the switch will be turned ON. The effective duty-cycle of the leading edge modulation is determined during the OFF time of the switch. Figure 3 shows a leading edge control scheme.

One of the advantages of this control technique is that it requires only one system clock. Switch 1 (SW1) turns OFF and Switch 2 (SW2) turns ON at the same instant to minimize the momentary "no-load" period, thus lowering ripple voltage generated by the switching action. With such synchronized switching, the ripple voltage of the first stage is reduced. Calculation and evaluation have shown that the 120Hz component of the PFC's output ripple voltage can be reduced by as much as 30% using this method, substantially reducing dissipation in the high-voltage PFC capacitor.

### **TYPICAL APPLICATIONS**

#### ONE PIN ERROR AMP

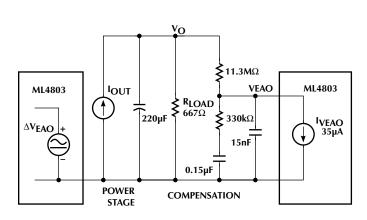

The ML4803 utilizes a one pin voltage error amplifier in the PFC section (VEAO). The error amplifier is in reality a current sink which forces  $35\mu A$  through the output

programming resistor. The nominal voltage at the VEAO pin is 5V. The VEAO voltage range is 4 to 6V. For a  $11.3 M\Omega$  resistor chain to the boost output voltage and 5V steady state at the VEAO, the boost output voltage would be 400 V.

### PROGRAMMING RESISTOR VALUE

Equation 1 calculates the required programming resistor value.

$$Rp = \frac{V_{BOOST} - V_{EAO}}{I_{PGM}} = \frac{400V - 5.0V}{35\mu A} = 11.3M\Omega$$

(1)

#### PFC VOLTAGE LOOP COMPENSATION

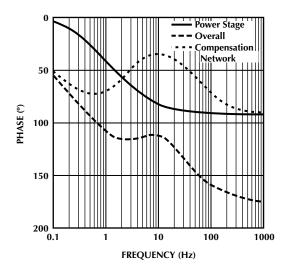

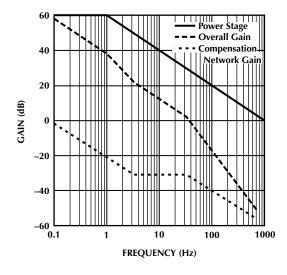

The voltage-loop bandwidth must be set to less than 120Hz to limit the amount of line current harmonic distortion. A typical crossover frequency is 30Hz. Equation 1, for simplicity, assumes that the pole capacitor dominates the error amplifier gain at the loop unity-gain frequency. Equation 2 places a pole at the crossover frequency, providing 45 degrees of phase margin. Equation 3 places a zero one decade prior to the pole. Bode plots showing the overall gain and phase are shown in Figures 5 and 6. Figure 4 displays a simplified model of the voltage loop.

$$C_{COMP} = \frac{Pin}{R_P \times V_{BOOST} \times \Delta VEAO \times C_{OUT} \times (2 \times \pi \times f)^2}$$

(2)

$$C_{COMP} = \frac{300W}{11.3M\Omega \times 400V \times 0.5V \times 220\mu F \times (2 \times \pi \times 30Hz)^2}$$

$$C_{COMP} = 16nF$$

Figure 3. Typical Leading Edge Control Scheme.

### TYPICAL APPLICATIONS (Continued)

$$R_{COMP} = \frac{1}{2 \times \pi \times f \times C_{COMP}}$$

(3)

$$R_{COMP} = \frac{1}{6.28 \times 30 \text{Hz} \times 16 \text{nF}} = 330 \text{k}\Omega$$

$$C_{ZERO} = \frac{1}{2 \times \pi \times \frac{f}{10} \times R_{COMP}}$$

(4)

$$C_{ZERO} = \frac{1}{6.28 \times 3Hz \times 330k\Omega} = 0.16\mu F$$

#### **INTERNAL VOLTAGE RAMP**

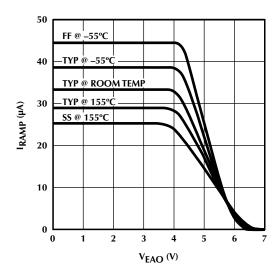

The internal ramp current source is programmed by way of the VEAO pin voltage. Figure 7 displays the internal ramp current vs. the VEAO voltage. This current source is used to develop the internal ramp by charging the internal 30pF +12/–10% capacitor. See Figures 10 and 11. The frequency of the internal programming ramp is set internally to 67kHz.

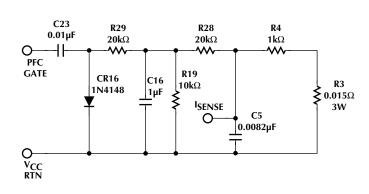

#### PFC CURRENT SENSE FILTERING

In DCM, the input current wave shaping technique used by the ML4803 could cause the input current to run away. In order for this technique to be able to operate properly under DCM, the programming ramp must meet the boost inductor current down-slope at zero amps. Assuming the programming ramp is zero under light load, the OFF-time will be terminated once the inductor current reaches zero. Subsequently the PFC gate drive is initiated, eliminating the necessary dead time needed for the DCM mode. This forces the output to run away until the V<sub>CC</sub> OVP shuts down the PFC. This situation is corrected by adding an

**Figure 4. Voltage Control Loop**

Figure 6. Voltage Loop Phase

Figure 5. Voltage Loop Gain

Figure 7. Internal Ramp Current vs. V<sub>EAO</sub>

### TYPICAL APPLICATIONS (Continued)

offset voltage to the current sense signal, which forces the duty cycle to zero at light loads. This offset prevents the PFC from operating in the DCM and forces pulse-skipping from CCM to no-duty, avoiding DMC operation. External filtering to the current sense signal helps to smooth out the sense signal, expanding the operating range slightly into the DCM range, but this should be done carefully, as this filtering also reduces the bandwidth of the signal feeding the pulse-by-pulse current limit signal. Figure 9 displays a typical circuit for adding offset to I<sub>SENSE</sub> at light loads.

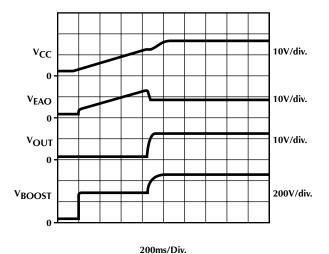

#### **PFC Start-Up and Soft Start**

During steady state operation VEAO draws  $35\mu A$ . At startup the internal current mirror which sinks this current is defeated until  $V_{CC}$  reaches 12V. This forces the PFC error voltage to  $V_{CC}$  at the time that the IC is enabled. With leading edge modulation  $V_{CC}$  on the VEAO pin forces zero duty on the PFC output. When selecting external compensation components and  $V_{CC}$  supply circuits VEAO must not be prevented from reaching 6V prior to  $V_{CC}$  reaching 12V in the turn-on sequence. This will guarantee that the PFC stage will enter soft-start. Once  $V_{CC}$  reaches 12V the  $35\mu A$  VEAO current sink is enabled. VEAO compensation components are then discharged by way of the  $35\mu A$  current sink until the steady state operating point is reached. See Figure 8.

### PFC SOFT RECOVERY FOLLOWING V<sub>CC</sub> OVP

The ML4803 assumes that  $V_{CC}$  is generated from a source that is proportional to the PFC output voltage. Once that source reaches 16.2V the internal current sink tied to the VEAO pin is disabled just as in the soft start turn-on sequence. Once disabled, the VEAO pin charges HIGH by way of the external components until the PFC duty cycle goes to zero, disabling the PFC. The  $V_{CC}$  OVP resets once the VCC discharges below 16.2V, enabling the

VEAO current sink and discharging the VEAO compensation components until the steady state operating point is reached. It should be noted that, as shown in Figure 8, once the VEAO pin exceeds 6.5V, the internal ramp is defeated. Because of this, an external Zener can be installed to reduce the maximum voltage to which the VEAO pin may rise in a shutdown condition. Clamping the VEAO pin externally to 7.4V will reduce the time required for the VEAO pin to recover to its steady state value.

#### **UVLO**

Once  $V_{\text{CC}}$  reaches 12V both the PFC and PWM are enabled. The UVLO threshold is 9.1V providing 2.9V of hysteresis.

#### GENERATING V<sub>CC</sub>

An internal clamp limits overvoltage to  $V_{CC}$ . This clamp circuit ensures that the  $V_{CC}$  OVP circuitry of the ML4803 will function properly over tolerance and temperature while protecting the part from voltage transients. This circuit allows the ML4803 to deliver 15V nominal gate drive at PWM OUT and PFC OUT, sufficient to drive low-cost IGBTs.

It is important to limit the current through the Zener to avoid overheating or destroying it. This can be done with a single resistor in series with the  $V_{CC}$  pin, returned to a bias supply of typically 14V to 18V. The resistor value must be chosen to meet the operating current requirement of the ML4803 itself (4.0mA max) plus the current required by the two gate driver outputs.

### **V<sub>CC</sub>OVP**

$V_{CC}$  is assumed to be a voltage proportional to the PFC output voltage, typically a bootstrap winding off the boost

Figure 8. PFC Soft Start

Figure 9. I<sub>SENSE</sub> Offset for Light Load Conditions

### TYPICAL APPLICATIONS (Continued)

inductor. The V<sub>CC</sub> OVP comparator senses when this voltage exceeds 16V, and terminates the PFC output drive while disabling the VEAO current sink. Once the VEAO current sink is disabled, the VEAO voltage will charge unabated, except for a diode clamp to V<sub>CC</sub>, reducing the PFC pulse width. Once the V<sub>CC</sub> rail has decreased to below 16.2V the VEAO sink will be enabled, discharging external VEAO compensation components until the steady state voltage is reached. Given that 15V on V<sub>CC</sub> corresponds to 400V on the PFC output, 16V on V<sub>CC</sub> corresponds to an OVP level of 426V.

#### **COMPONENT REDUCTION**

Components associated with the  $V_{RMS}$  and  $I_{RMS}$  pins of a typical PFC controller such as the ML4824 have been eliminated. The PFC power limit and bandwidth does vary with line voltage. Double the power can be delivered from a 220 V AC line versus a 110 V AC line. Since this is a combination PFC/PWM, the power to the load is limited by the PWM stage.

Figure 10. Typical Peak Current Mode Waveforms

Figure 11. ML4803 PFC Control

Figure 12. Typical Application Circuit. Universal Input 240W 12V DC Output

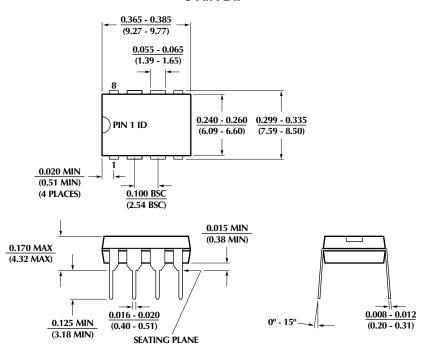

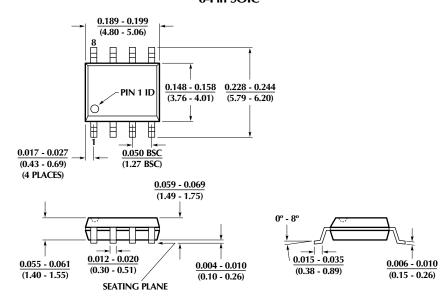

## PHYSICAL DIMENSIONS inches (millimeters)

### Package: P08 8-Pin PDIP

### ORDERING INFORMATION

| PART NUMBER | PFC/PWM FREQUENCY | TEMPERATURE RANGE | PACKAGE          |

|-------------|-------------------|-------------------|------------------|

| ML4803CP-1  | 67kHz / 67kHz     | 0°C to 70°C       | 8-Pin PDIP (P08) |

| ML4803CS-1  | 67kHz / 67kHz     | 0°C to 70°C       | 8-Pin SOIC (S08) |

| ML4803IP-1  | 67kHz / 67kHz     | -40°C to 85°C     | 8-Pin PDIP (P08) |

| ML4803IS-1  | 67kHz / 67kHz     | -40°C to 85°C     | 8-Pin SOIC (S08) |

| ML4803CP-2  | 67kHz / 134kHz    | 0°C to 70°C       | 8-Pin PDIP (P08) |

| ML4803CS-2  | 67kHz / 134kHz    | 0°C to 70°C       | 8-Pin SOIC (S08) |

| ML4803IP-2  | 67kHz / 134kHz    | -40°C to 85°C     | 8-Pin PDIP (P08) |

| ML4803IS-2  | 67kHz / 134kHz    | -40°C to 85°C     | 8-Pin SOIC (S08) |

#### **Micro Linear Corporation**

2092 Concourse Drive San Jose, CA 95131 Tel: (408) 433-5200 Fax: (408) 432-0295 www.microlinear.com

© Micro Linear 1999. Micro Linear is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; 5,777,514; 5,793,168; 5,798,635; 5,804,950; 5,808,455; 5,811,999; 5,818,207; 5,818,669; 5,825,165; 5,825,223; 5,838,723; 5,844,378; 5,844,941. Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending.

Micro Linear makes no representations or warranties with respect to the accuracy, utility, or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, express or implied, by estoppel or otherwise, to any patents or other intellectual property rights is granted by this document. The circuits contained in this document are offered as possible applications only. Particular uses or applications may invalidate some of the specifications and/or product descriptions contained herein. The customer is urged to perform its own engineering review before deciding on a particular application. Micro Linear assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Micro Linear products including liability or warranties relating to merchantability, fitness for a particular purpose, or infringement of any intellectual property right. Micro Linear products are not designed for use in medical, life saving, or life sustaining applications.