## Description

The CS5112 is a dual output power supply integrated circuit. It contains a 5V ±2%, 100mA linear regulator, a watchdog timer, a linear output voltage monitor to provide a Power On Reset (POR) and a 1.4A current mode PWM switching regulator.

The 5V linear regulator is comprised of an error amplifier, reference, and supervisory functions. It has low internal supply current consumption and provides 1.2V (typical) dropout voltage at maximum load current.

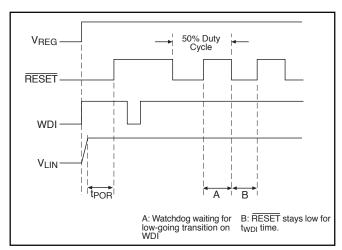

The watchdog timer circuitry monitors an input signal (WDI) from the microprocessor. It responds to the falling edge of this watchdog signal. If a correct watchdog signal is not received within the externally programmable time, a reset signal is issued.

The externally programmable active reset circuit operates correctly for an output voltage (V<sub>LIN</sub>) as low as 1V. During power up, or if the output voltage shifts

below the regulation limit, RESET toggles low and remains low for the duration of the delay after proper output voltage regulation is restored. Additionally a reset pulse is issued if the correct watchdog is not received within the programmed time. Reset pulses continue until the correct watchdog signal is received. The reset pulse width and frequency, as well as the Power On Reset delay, are set by one external RC network.

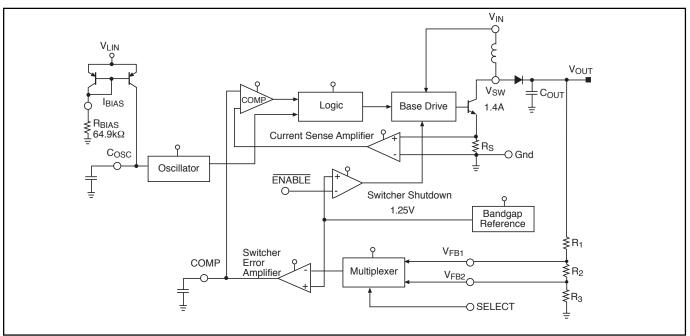

The current mode PWM switching regulator is comprised of an error amplifier with selectable feedback inputs, a current sense amplifier, an adjustable oscillator, and a 1.4A output power switch with anti-saturation control. The switching regulator can be configured in a variety of topologies.

The CS5112 is load dump capable and has protection circuitry which includes current limit on the linear and switcher outputs, and an overtemperature limiter.

## Features

- **Linear Regulator**  $5V \pm 2\%$  @ 100mA

- **Switching Regulator** 1.4A Peak Internal Switch

120kHz Maximum **Switching Frequency**

5V to 26V Operating Supply Range

- **Smart Functions** Watchdog **RESET ENABLE**

- **Protection** Overtemperature **Current Limit**

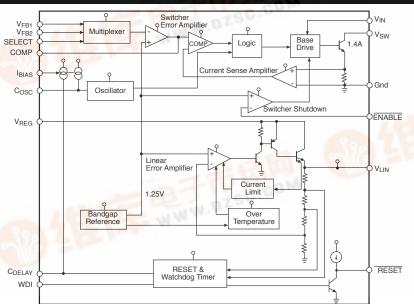

## **Block Diagram**

Semiconductor

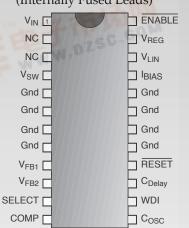

## **Package Options** 24 Lead SO Wide

(Internally Fused Leads)

Cherry Semiconductor Corporation 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885-3600 Fax: (401)885-5786 Email: info@cherry-semi.com Web Site: www.cherry-semi.com

## **Absolute Maximum Ratings**

| Logic Inputs/Outputs ( ENABLE , SELECT, WDI, RESET )          | 0.3V to V <sub>LIN</sub>            |

|---------------------------------------------------------------|-------------------------------------|

| V <sub>IN</sub> , V <sub>REG:</sub>                           |                                     |

| DC Input Voltage                                              | 0.3V to 26V                         |

| Peak Transient Voltage (26V Load Dump @ 14V V <sub>IN</sub> ) | 0.3V to 40V                         |

| V <sub>SW</sub> Peak Transient Voltage                        | 54V                                 |

| V <sub>SW</sub> Peak Transient Voltage                        | 0.3V to V <sub>LIN</sub>            |

| Power Dissipation                                             | Internally Limited                  |

| V <sub>LIN</sub> Output Current                               | Internally Limited                  |

| V <sub>SW</sub> Output CurrentRESET Output Sink Current       | Internally Limited                  |

| RESET Output Sink Current                                     | 5mA                                 |

| ESD Susceptibility (Human Body Model)                         | 2kV                                 |

| ESD Susceptibility (Machine Model)                            | 200V                                |

| ESD Susceptibility (Machine Model)                            | 65 to 150°C                         |

| Lead Temperature Soldering: Reflow (SMD styles only)          | 60 sec. max above 183°C, 230°C peak |

# Electrical Characteristics: $5\text{V} \leq \text{V}_{\text{IN}} \leq 26\text{V}$ and $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}$ , $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C}$ , $C_{\text{OUT}} = 100\mu\text{F}$ (ESR $\leq 8\Omega$ ), $C_{\text{Delay}} = 0.1\mu\text{F}$ , $R_{\text{BIAS}} = 64.9\text{k}\Omega$ , $C_{\text{OSC}} = 390$ pF, $C_{\text{COMP}} = 0.1\mu\text{F}$ ; unless otherwise specified.

| PARAMETER                          | TEST CONDITIONS                                                                                            | MIN                    | TYP  | MAX        | UNIT   |

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------|------|------------|--------|

| ■ General                          |                                                                                                            |                        |      |            |        |

| I <sub>IN</sub> Off Current        | $6.6V \le V_{IN} \le 26V$ , $I_{SW} = 0A$                                                                  |                        |      | 2.0        | mA     |

| I <sub>IN</sub> On Current         | $6.6V \le V_{IN} \le 26V$ , $I_{SW} = 1.4A$                                                                |                        | 30   | 70         | mA     |

| I <sub>REG</sub> Current           | $I_{LIN} = 100 \text{mA}, 6.6 \text{V} \le V_{REG} \le 26 \text{V}$                                        |                        |      | 6          | mA     |

| Thermal Limit                      | Guaranteed by design                                                                                       | 160                    |      | 210        | °C     |

|                                    |                                                                                                            |                        |      |            |        |

| ■ 5V Regulator Section             |                                                                                                            |                        |      |            |        |

| V <sub>LIN</sub> Output Voltage    | $6.6V \leq V_{REG} \leq 26V, \ 1mA \leq I_{LIN} \leq 100mA$                                                | 4.9                    | 5.0  | 5.1        | V      |

| Dropout Voltage                    | $(V_{REG} - V_{LIN}) @ I_{LIN} = 100 mA$                                                                   |                        | 1.2  | 1.5        | V      |

| Line Regulation                    | $6.6V \le V_{REG} \le 26V$ , $I_{LIN} = 5mA$                                                               |                        | 5    | 25         | mV     |

| Load Regulation                    | $V_{REG} = 19V$ , $1mA \le I_{LIN} \le 100mA$                                                              |                        | 5    | 25         | mV     |

| Current Limit                      | $6.6V \le V_{REG} \le 26V$                                                                                 | 120                    |      |            | mA     |

| DC Ripple Rejection                | $14V \le V_{REG} \le 24V$                                                                                  | 60                     | 75   |            | dB     |

| ■ RESET Section                    |                                                                                                            |                        |      |            |        |

| Low Threshold (V <sub>RTL</sub> )  | - V <sub>IJN</sub> Decreasing                                                                              | 4.05                   | 4.25 | 4.45       | V      |

| High Threshold (V <sub>RTH</sub> ) | V <sub>LIN</sub> Increasing                                                                                | 4.20                   | 4.45 | 4.70       | V      |

| Hysteresis                         | $V_{RTH}$ - $V_{RTL}$                                                                                      | 140                    | 190  | 240        | mV     |

| Active High                        | $V_{LIN} > V_{RTH}$ , $I_{RESET} = -25 \mu A$                                                              | V <sub>LIN</sub> - 0.5 |      |            | V      |

| Active Low                         | $V_{LIN}$ = 1V, 10k $\Omega$ pullup from $\overline{RESET}$ to $V_{LIN}$ $V_{LIN}$ = 4V, $I_{RESET}$ = 1mA |                        |      | 0.4<br>0.7 | V<br>V |

| Delay                              | Invalid WDI                                                                                                | 6.25                   | 8.78 | 11.0       | ms     |

| Power On Delay                     | $V_{LIN}$ crossing $V_{RTH}$                                                                               | 6.25                   |      |            | ms     |

# Electrical Characteristics: $5\text{V} \leq \text{V}_{\text{IN}} \leq 26\text{V}$ and $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}$ , $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C}$ , $C_{\text{OUT}} = 100\mu\text{F}$ (ESR≤8Ω), $C_{\text{Delay}} = 0.1\mu\text{F}$ , $R_{\text{BIAS}} = 64.9\text{k}\Omega$ , $C_{\text{OSC}} = 390$ pF, $C_{\text{COMP}} = 0.1\mu\text{F}$ ; unless otherwise specified.

| PARAMETER                                         | TEST CONDITIONS                                                 | MIN   | TYP  | MAX   | UNIT |

|---------------------------------------------------|-----------------------------------------------------------------|-------|------|-------|------|

| Watchdog Input (WDI)                              |                                                                 |       |      |       |      |

| VIH                                               | Peak WDI needed to activate RESET                               |       |      | 2.0   | V    |

| VIL                                               |                                                                 | 0.8   |      |       | V    |

| Hysteresis                                        | Note 1                                                          | 25    | 50   |       | mV   |

| Pull-Up Resistor                                  | WDI=0V                                                          | 20    | 50   | 100   | kΩ   |

| Low Threshold                                     |                                                                 | 6.25  | 8.78 | 11.0  | ms   |

| Floating Input Voltage                            |                                                                 | 3.5   |      |       | V    |

| WDI Pulse Width                                   |                                                                 | _     |      | 5     | μs   |

| Switcher Section                                  |                                                                 |       |      |       |      |

| Minimum Operating<br>Input Voltage                |                                                                 |       |      | 5.0   | V    |

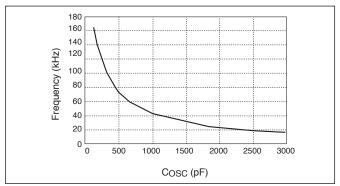

| Switching Frequency                               | Refer to Figure 1d.                                             | 80    | 95   | 110   | kHz  |

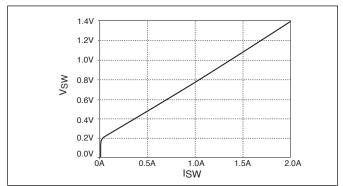

| Switch Saturation Voltage                         | $I_{SW} = 1.4A$                                                 | 0.7   | 1.1  | 1.6   | V    |

| Output Current Limit                              |                                                                 | 1.4   |      | 2.5   | A    |

| Max Switching Frequency                           | $V_{SW} = 7.5V$ with $50\Omega$ load,<br>Refer to Figure 1d.    | 120   |      |       | kHz  |

| V <sub>FB1</sub> Regulation Voltage               | <u> </u>                                                        | 1.206 | 1.25 | 1.294 | V    |

| V <sub>FB2</sub> Regulation Voltage               |                                                                 | 1.206 | 1.25 | 1.294 | V    |

| V <sub>FB1</sub> , V <sub>FB2</sub> Input Current | $V_{FB1} = V_{FB2} = 5V$                                        |       |      | 1     | μΑ   |

| Oscillator Charge Current                         | $C_{OSC} = 0V$                                                  | 35    | 40   | 45    | μΑ   |

| Oscillator Discharge Current                      | $C_{OSC} = 4V$                                                  | 270   | 320  | 370   | μΑ   |

| C <sub>Delay</sub> Charge Current                 | $C_{Delay} = 0V$                                                | 35    | 40   | 45    | μΑ   |

| Switcher Max Duty Cycle                           | $V_{SW} = 5V$ with $50\Omega$ load,<br>$V_{FB1} = V_{FB2} = 1V$ | 72    | 85   | 95    | %    |

| Current Sense Amp Gain                            | $I_{SW} = 2.3A$                                                 |       | 7    |       |      |

| Error Amp DC Gain                                 |                                                                 |       | 67   |       | dB   |

| Error Amp Transconductance                        |                                                                 |       | 2700 |       | μA/V |

| ENABLE Input                                      |                                                                 |       |      |       |      |

| VIL                                               |                                                                 | 0.8   | 1.24 |       | V    |

| VIH                                               |                                                                 |       | 1.30 | 2.0   | V    |

| Hysteresis                                        |                                                                 |       | 60   |       | mV   |

| Input Impedance                                   |                                                                 | 10    | 20   | 40    | kΩ   |

| Select Input                                      |                                                                 |       |      |       |      |

| VIL (Selects V <sub>FB1</sub> )                   | $4.9 \le V_{LIN} \le 5.1$                                       | 0.8   | 1.25 |       | V    |

| VIH (Selects V <sub>FB2</sub> )                   | $4.9 \le V_{LIN} \le 5.1$                                       |       | 1.25 | 2.0   | V    |

| SELECT Pull-Up                                    | SELECT = 0V                                                     | 10    | 24   | 50    | kΩ   |

| Floating Input Voltage                            |                                                                 | 3.5   | 4.5  |       | V    |

| Package Lead Description |             |                                                                                                                                                  |  |  |

|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PACKAGE LEAD #           | LEAD SYMBOL | FUNCTION                                                                                                                                         |  |  |

| 24 Lead SO Wide          |             |                                                                                                                                                  |  |  |

| 1                        | $V_{IN}$    | Supply Voltage.                                                                                                                                  |  |  |

| 2, 3                     | NC          | No connection.                                                                                                                                   |  |  |

| 4                        | $V_{SW}$    | Collector of NPN power switch for switching regulator section.                                                                                   |  |  |

| 5,6,7,8,17,18,19,20      | Gnd         | Connected to the heat removing leads.                                                                                                            |  |  |

| 9                        | $V_{FB1}$   | Feedback input voltage 1 (referenced to 1.25V)                                                                                                   |  |  |

| 10                       | $V_{FB2}$   | Feedback input voltage 2 (referenced to 1.25V)                                                                                                   |  |  |

| 11                       | SELECT      | Logic level input that selects either $V_{FB1}$ or $V_{FB2}$ . An open selects $V_{FB2}$ . Connect to Gnd to select $V_{FB1}$ .                  |  |  |

| 12                       | COMP        | Output of the transconductance error amplifier.                                                                                                  |  |  |

| 13                       | $C_{OSC}$   | A capacitor connected to Gnd sets the switching frequency.<br>Refer to Figure 1d.                                                                |  |  |

| 14                       | WDI         | Watchdog input. Active on falling edge.                                                                                                          |  |  |

| 15                       | $C_{Delay}$ | A capacitor connected to Gnd sets the Power On Reset and Watchdog time.                                                                          |  |  |

| 16                       | RESET       | $\overline{RESET}$ output. Active low if $V_{LIN}$ is below the regulation limit. If watchdog timeout is reached, a reset pulse train is issued. |  |  |

| 21                       | $I_{BIAS}$  | A resistor connected to Gnd sets internal bias currents as well as the $C_{OSC}$ and $C_{Delay}$ charge currents.                                |  |  |

| 22                       | $V_{LIN}$   | Regulated 5V output from the linear regulator section.                                                                                           |  |  |

| 23                       | $V_{REG}$   | Input voltage to the linear regulator and the internal supply circuitry.                                                                         |  |  |

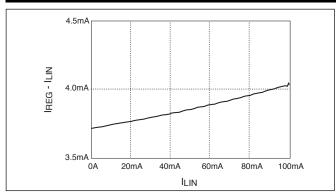

## **Typical Performance Characteristics**

**ENABLE**

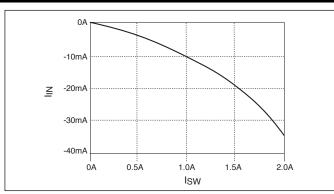

Figure 1a. 5V Regulator Bias Current vs. Load Current.

24

Figure 1c. Switch Saturation Voltage.

Figure 1b. Supply Current vs. Switch Current.

Logic level input to shut down the switching regulator.

Figure 1d. Oscillator Frequency (kHz) vs.  $C_{OSC}$  (pF), assuming  $R_{BIAS}$  = 64.9k $\Omega$ .

#### Circuit Description

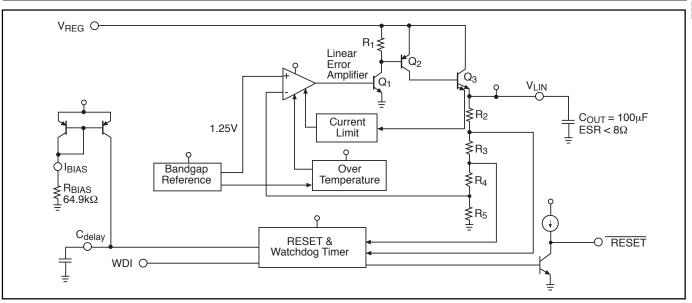

Figure 2. Block diagram of 5V linear regulator portion of the CS5112.

#### **5V Linear Regulator**

The 5V linear regulator consists of an error amplifier, bandgap voltage reference, and a composite pass transistor.

The 5V linear regulator circuitry is shown in Figure 2. When an unregulated voltage greater than 6.6V is applied to the  $V_{REG}$  input, a 5V regulated DC voltage will be present at  $V_{LIN}.$  For proper operation of the 5V linear regulator, the  $I_{BIAS}$  lead must have a 64.9k $\Omega$  pull down resistor to ground. A  $100\mu F$  or larger capacitor with an ESR  $<\!8\Omega$  must be connected between  $V_{LIN}$  and ground. To operate the 5V linear regulator as an independent regulator (i.e. separate from the switching supply), the input voltage must be tied to the  $V_{REG}$  lead.

As the voltage at the  $V_{REG}$  input is increased,  $Q_1$  is turned on.  $Q_1$  provides base drive for  $Q_2$  which in turn provides base current for  $Q_3$ . As  $Q_3$  is turned on, the output voltage, V<sub>LIN</sub>, begins to rise as Q<sub>3</sub>'s output current charges the output capacitor, C<sub>OUT</sub>. Once V<sub>LIN</sub> rises to a certain level, the error amplifier becomes biased and provides the appropriate amount of base current to  $Q_1$ . The error amplifier monitors the scaled output voltage via an internal voltage divider, R<sub>2</sub> through R<sub>5</sub>, and compares it to the bandgap voltage reference. The error amplifier output or error signal is an output current equal to the error amplifier's input differential voltage times the transconductance of the amplifier. Therefore, the error amplifier varies the base current to  $Q_1$ , which provides bias to  $Q_2$  and  $Q_3$ , based on the difference between the reference voltage and the scaled V<sub>LIN</sub> output voltage.

#### **Control Functions**

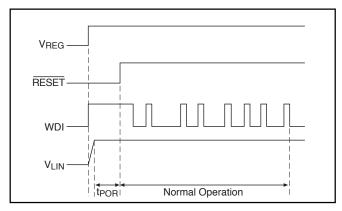

The watchdog timer circuitry monitors an input signal (WDI) from the microprocessor. It responds to the falling edge of this watchdog signal which it expects to see within an externally programmable time (see Figure 3).

The watchdog time is given by:

$$t_{WDI} = 1.353 \times C_{Delay} R_{BIAS}$$

Using  $C_{Delay} = 0.1 \mu F$  and  $R_{BIAS} = 64.9 k\Omega$  gives a time ranging from 6.25ms to 11ms assuming ideal components. Based on this, the software must be written so that the watchdog arrives at least every 6.25ms. In practice, the tolerance of  $C_{Delay}$  and  $R_{BIAS}$  must be taken into account when calculating the minimum watchdog time ( $t_{WDI}$ ).

Figure 3. Timing diagram for normal regulator operation.

Figure 4. Timing diagram when WDI fails to appear within the preset time interval,  $t_{\rm WDI}$ .

#### Circuit Description: continued

If a correct watchdog signal is not received within the specified time a reset pulse train is issued until the correct watchdog signal is received. The nominal reset signal in this case is a 5 volt square wave with a 50% duty cycle as shown in Figure 4.

The RESET signal frequency is given by:  $f_{\rm RESET} = \frac{1}{2({\rm t_{WDI}})} \label{eq:freset}$

$$f_{\text{RESET}} = \frac{1}{2(t_{\text{WDI}})}$$

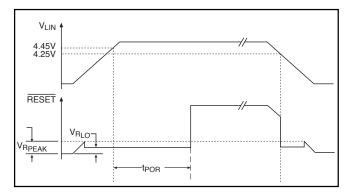

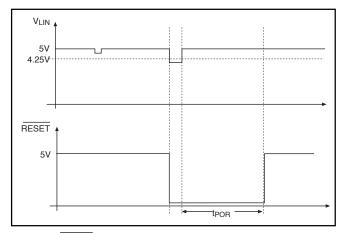

The Power On Reset (POR) and low voltage  $\overline{\text{RESET}}$  use the same circuitry and issue a reset when the linear output voltage is below the regulation limit. After V<sub>LIN</sub> rises above the minimum specified value, RESET remains low for a fixed period  $t_{POR}$  as shown in Figure 5.

The POR delay  $(t_{POR})$  is given by:

$$t_{POR} = 1.353 \times C_{Delay} R_{BIAS}$$

Figure 5a. The power on reset time interval (tPOR) begins when VLIN rises above 4.45V (typical).

Figure 5b.  $\overline{RESET}$  signal is issued whenever  $V_{LIN}$  falls below 4.25V (typical).

#### **Current Mode PWM Switching Circuitry**

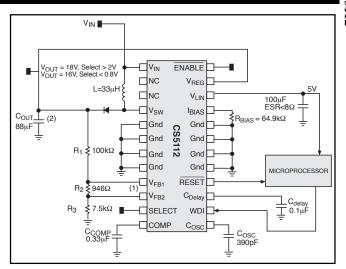

The current mode PWM switching voltage regulator contains an error amplifier with selectable feedback inputs, a current sense amplifier, an adjustable oscillator and a 1.4A output power switch with antisaturation control. The switching regulator and external components, connected in a boost configuration, are shown in Figure 6.

The switching regulator begins operation when V<sub>REG</sub> and  $V_{\rm IN}$  are raised above 5 volts.  $V_{\rm REG}$  is required since the switching supply's control circuitry is powered through  $V_{LIN}$ .  $V_{IN}$  supplies the base drive to the switcher output transistor.

The output transistor turns on when the oscillator starts to charge the capacitor on  $C_{OSC}$ . The output current will develop a voltage drop across the internal sense resistor (R<sub>S</sub>). This voltage drop produces a proportional voltage at the output of the current sense amplifier, which is compared to the output of the error amplifier. The error amplifier generates an output voltage which is proportional to the difference between the scaled down output boost voltage (V<sub>FB1</sub> or V<sub>FB2</sub>) and the internal bandgap voltage reference. Once the current sense amplifier output exceeds the error amplifier's output voltage, the output transistor is turned off.

The energy stored in the inductor during the output transistor on time is transferred to the load when the output transistor is turned off. The output transistor is turned back on at the next rising edge of the oscillator. On a cycle by cycle basis, the current mode controller in a discontinuous mode of operation charges the inductor to the appropriate amount of energy, based on the energy demand of the load. Figure 7 shows the typical current and voltage waveforms for a boost supply operating in the discontinuous mode.

#### NOTES:

- 1. Refer to Figure 1d to determine oscillator frequency.

- 2. The switching regulator can be disabled by providing a logic high at the ENABLE input.

- 3. The boost output voltage can be controlled dynamically by the feedback select input. If select is open, V<sub>FB2</sub> is selected. If select is low, then  $V_{FB1}$  is selected.

#### **Protection Circuitry**

The current out of V<sub>LIN</sub> is sensed in order to limit excessive power dissipation in the linear output transistor over the output range of 0V to regulation. Also, the current into V<sub>SW</sub> is sensed in order to provide the current limit function in the switcher output transistor.

If the die temperature is increased above 160°C, either due to excessive ambient temperature or excessive power dissipation, the drive to the linear output transistor is reduced proportionally with increasing die temperature. Therefore, V<sub>LIN</sub> will decrease with increasing die temperature above 160°C. Since the switcher control circuitry is powered through V<sub>LIN</sub>, the switcher performance, including current limit, will be affected by the decrease in  $V_{LIN}$ .

Figure 6: Block diagram of the 1.4A current mode control switching regulator portion of the CS5112 in a boost configuration.

#### **Application Notes**

#### **Design Procedure for Boost Topology**

This section outlines a procedure for designing a boost switching power supply operating in the discontinuous mode.

#### Step 1

Determine the output power required by the load.

$$P_{OUT} = I_{OUT} V_{OUT}$$

(1)

#### Step 2

Choose  $C_{OSC}$  based on the target oscillator frequency with an external resistor value,  $R_{BIAS}=64.9k\Omega$ . (See Figure 1d).

Figure 7: Voltage and current waveforms for boost topology in CS5112.

#### Step 3

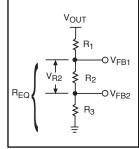

Next select the output voltage feedback sense resistor divider as follows (Figure 8).

For  $V_{FB1}$  active, choose a value for  $R_1$  and then solve for  $R_{EO}$  where:

$$R_{EQ} = \frac{R_1}{\frac{V_{OUT}}{V_{FB1}}} - 1$$

(3a)

For  $V_{FB2}$  active, find:

$$V_{FB1} = V_{OUT} \left( \frac{R_{EQ}}{R_1 + R_{EQ}} \right), (3b)$$

and then calculate  $R_2$  where:

Figure 8. Feedback sense resistor divider connected between  $V_{OUT}$  and ground.

$$R_2 = \frac{V_{R2}}{I_{R2}} = \frac{V_{FB1} - V_{FB2}}{V_{FB1}/R_{EO}} \cdot (3c)$$

Then find R<sub>3</sub>, where:

$$R_3 = R_{EQ} - R_2.$$

(3d)

#### **Application Notes: continued**

#### Step 4

Determine the maximum on time at the minimum oscillator frequency and  $V_{\rm IN}.$  For discontinuous operation, all of the stored energy in the inductor is transferred to the load prior to the next cycle. Since the current through the inductor cannot change instantaneously and the inductance is constant, a volt-second balance exists between the on time and off time. The voltage across the inductor during the on cycle is  $V_{\rm IN}$  and the voltage across the inductor during the off cycle is  $V_{\rm OUT}$ -  $V_{\rm IN}.$  Therefore:

$$V_{IN}t_{on} = (V_{OUT} - V_{IN})t_{off}$$

(4a)

where the maximum on time is:

$$t_{\text{on(max)}} \approx \left[ 1 - \frac{V_{\text{IN(min)}}}{V_{\text{OUT(max)}}} \right] \left[ \frac{1}{f_{\text{SW(min)}}} \right].$$

(4b)

#### Step 5

Calculate the maximum inductance allowed for discontinuous operation:

$$L_{(max)} = \frac{f_{SW(min)} V_{IN}^{2}_{(min)} t_{on}^{2}_{(max)}}{2 P_{OUT}/\eta}$$

(5)

where  $\eta = \text{efficiency}$ .

Usually  $\eta=0.75$  is a good starting point. The IC's power dissipation should be calculated after the peak current has been determined in Step 6. If the efficiency is less than originally assumed, decrease the efficiency and recalculate the maximum inductance and peak current.

#### Step 6

Determine the peak inductor current at the minimum inductance, minimum  $V_{\rm IN}$  and maximum on time to make sure the inductor current doesn't exceed 1.4A.

$$I_{pk} = \frac{V_{IN(min)} t_{on(max)}}{L_{(min)}}$$

(6)

#### Step 7

Determine the minimum output capacitance and maximum ESR based on the allowable output voltage ripple.

$$C_{OUT(min)} = \frac{I_{pk}}{8f\Delta V_{ripple}}$$

(7a)

$$ESR_{(min)} = \frac{\Delta V_{ripple}}{I_{pk}}$$

(7b)

In practice, it is normally necessary to use a larger capacitance value to obtain a low ESR. By placing capacitors in parallel, the equivalent ESR can be reduced.

#### Step 8

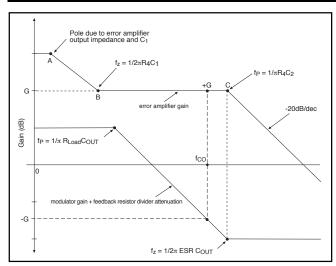

Compensate the feedback loop to guarantee stability under all operating conditions. To do this, we calculate the modulator gain and the feedback resistor network attenuation and set the gain of the error amplifier so that the

overall loop gain is 0dB at the crossover frequency,  $f_{CO}$ . In addition, the gain slope should be -20dB/decade at the crossover frequency.

The low frequency gain of the modulator (i.e. error amplifier output to output voltage) is:

$$\frac{\Delta V_{OUT}}{\Delta V_{EA}} = \frac{I_{pk(max)}}{V_{EA(max)}} \sqrt{\frac{R_{Load} L f}{2}}, \quad (8a)$$

where

$$I_{pk(max)} = \frac{V_{EA(max)}/G_{CSA}}{R_S} = \frac{(2.4V)/(7)}{150m\Omega} = 2.3A.$$

The  $V_{\text{OUT}}/V_{\text{EA}}$  transfer function has a pole at:

$$f_p = 1/(\pi R_{Load} C_{OUT}), \qquad (8b)$$

and a zero due to the output capacitor's ESR at:

$$f_z = 1/(2\pi ESR C_{OUT}). \tag{8c}$$

Since the error amplifier reference voltage is 1.25V, the output voltage must be divided down or attenuated before being applied to the input of the error amplifier. The feedback resistor divider attenuation is:

$$\frac{1.25V}{V_{OUT}}$$

.

The error amplifier in the CS5112 is an operational transconductance amplifier (OTA), with a gain given by:

$$G_{OTA} = gmZ_{OUT}$$

(8d)

where:

$$gm = \frac{\Delta I_{OUT}}{\Delta V_{IN}}.$$

(8e)

For the CS5112, gm =  $2700\mu A/V$  typical.

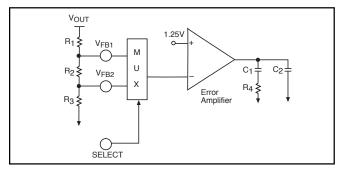

One possible error amplifier compensation scheme is shown in Figure 9. This gives the error amplifier a gain plot as shown in Figure 10.

For the error amplifier gain shown in Figure 10, a low frequency pole is generated by the error amplifier output impedance and  $C_1$ . This is shown by the line AB with a - 20dB/decade slope in Figure 12. The slope changes to zero at point B due to the zero at:

$$f_z = 1/(2\pi R_4 C_1).$$

(8f)

Figure 9. RC network used to compensate the error amplifier (OTA).

#### **Application Notes: continued**

Figure 10. Bode plot of error amplifier (OTA) gain and modulator gain added to the feedback resistor divider attenuation.

A pole at point C:

$$f_p = 1/(\pi R_4 C_2),$$

(8g)

offsets the zero set by the ESR of the output capacitors.

An alternative scheme uses a single capacitor as shown in Figure 11, to roll the gain off at a relatively low frequency.

Figure 11. A typical application diagram with external components configured in a boost topology.

#### Step 9

Finally the watchdog timer period and Power on Reset time is determined by:

$$t_{Delay} = 1.353 \times C_{Delay} R_{BIAS}. \tag{9}$$

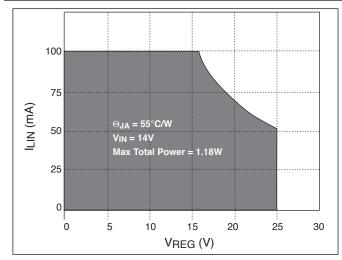

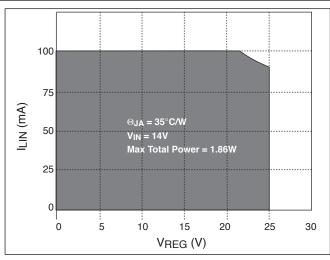

## Linear Regulator Output Current vs. Input Voltage

Figure 12: The shaded area shows the safe operating area of the CS5112 as a function of  $I_{LIN}$ ,  $V_{REG}$ , and  $\Theta_{JA}$ . Refer to the table below for typical loads and voltages.

|                  |          |                  | Linear Power | Worst Case Switcher<br>Power Available | Worst Case Switcher<br>Power Available |

|------------------|----------|------------------|--------------|----------------------------------------|----------------------------------------|

| V <sub>REG</sub> | $V_{IN}$ | I <sub>LIN</sub> | Dissipation  | $(\Theta_{JA} = 55^{\circ}C/W)$        | $(\Theta_{JA} = 35^{\circ}C/W)$        |

| (V)              | (V)      | (mA)             | (W)          | (W)                                    | (W)                                    |

| 20               | 14       | 25               | 0.44         | 0.74                                   | 1.42                                   |

| 20               | 14       | 50               | 0.83         | 0.35                                   | 1.03                                   |

| 20               | 14       | 75               | 1.22         | *                                      | 0.64                                   |

| 20               | 14       | 100              | 1.60         | *                                      | 0.26                                   |

| 25               | 14       | 25               | 0.60         | 0.58                                   | 1.26                                   |

| 25               | 14       | 50               | 1.11         | 0.07                                   | 0.75                                   |

| 25               | 14       | 75               | 1.62         | *                                      | 0.24                                   |

| 25               | 14       | 100              | 2.14         | *                                      | *                                      |

<sup>\*</sup> Subjecting the CS5112 to these conditions will exceed the maximum total power that the part can handle, thereby forcing it into thermal limit.

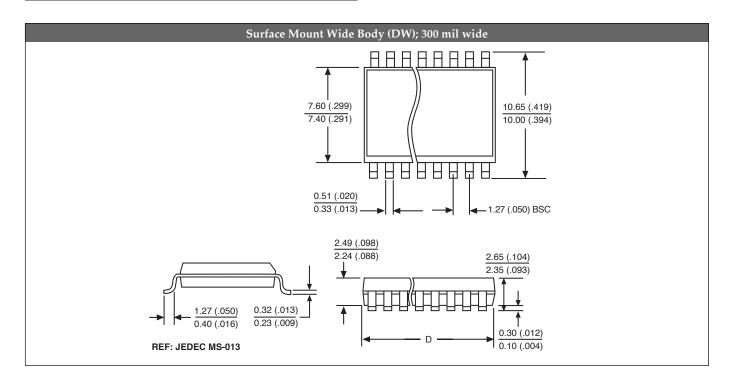

### **Package Specification**

### PACKAGE DIMENSIONS IN mm (INCHES)

|                                          | D     |       |      |       |

|------------------------------------------|-------|-------|------|-------|

| Lead Count                               | Met   | tric  | Eng  | glish |

|                                          | Max   | Min   | Max  | Min   |

| 24 Lead SO Wide (internally fused leads) | 15.60 | 15.20 | .614 | .598  |

| PACKAGE THERMAL DATA |     |                                          |      |

|----------------------|-----|------------------------------------------|------|

| Thermal<br>Data      |     | 24 Lead SO Wide (internally fused leads) |      |

| $R_{\Theta JC}$      | typ | 9                                        | °C/W |

| $R_{\Theta JA}$      | typ | 55                                       | °C/W |

| Ordering Information |                                                        |  |

|----------------------|--------------------------------------------------------|--|

| Part Number          | Description                                            |  |

| CS5112EDWF24         | 24 Lead SO Wide (internally fused leads)               |  |

| CS5112EDWFR24        | 24 Lead SO Wide (internally fused leads) (tape & reel) |  |

Cherry Semiconductor Corporation reserves the right to make changes to the specifications without notice. Please contact Cherry Semiconductor Corporation for the latest available information.