# SONY

# **CXD1176Q**

# 8-bit 20MSPS Video A/D Converter with Clamp Function

# Description

The CXD1176Q is an 8-bit CMOS A/D converter for video use that features a sync clamp function. The adoption of a 2 step-parallel method realizes low power consumption and a maximum conversion speed of 20MSPS.

#### **Features**

- Resolution power: 8-bit ± 1/2LSB (DL)

- Maximum sampling frequency: 20MSPS

- Low power consumption: 60mW (at 20MSPS typ.)

(Reference current excluded)

- Built-in sync type clamp function

- Built-in monostable multivibrator for clamp pulse generation

- Built-in sync pulse polarity selection function

- Clamp pulse direct input possible

- Built-in clamp ON/OFF function

- Built-in reference voltage self-bias circuit

- Input CMOS compatible

- 3-state TTL compatible output

- Single 5 V power supply

- Low input capacity: 11 pF

- Reference impedance: 330  $\Omega$  (typ.)

#### **Applications**

TV and VCR digital systems and a wide range of applications where high-speed A/D conversion is required.

#### Structure

Silicon gate CMOS IC

#### **Absolute Maximum Ratings** (Ta=25 °C)

| <ul> <li>Supply voltage</li> </ul> | Vdd | 7 | V |

|------------------------------------|-----|---|---|

|------------------------------------|-----|---|---|

Reference voltage

VRT, VRB VDD + 0.5 to Vss - 0.5 V

• Input voltage VIN VDD + 0.5 to Vss – 0.5 V (Analog)

Input voltage V<sub>I</sub> V<sub>DD</sub> + 0.5 to Vss – 0.5 V (Digital)

Output voltage Vo VDD + 0.5 to Vss – 0.5 V

(Digital)

Storage temperature

Tstg -55 to +150 °C

#### **Recommended Operating Conditions**

• Supply voltage AVDD, AVss 4.75 to 5.25 V

DVDD, DVss

| DVss - AVss | 0 to 100 mV

Reference input voltage

VRB 0 to V VRT to 2.7 V

Analog input VIN 1.8Vp-p above

· Clock pulse width

Tpw<sub>1</sub>, Tpw<sub>0</sub> 22.5 ns (min) to 1.1 µs (max)

Operating ambient temperature

Topr -40 to +85 °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

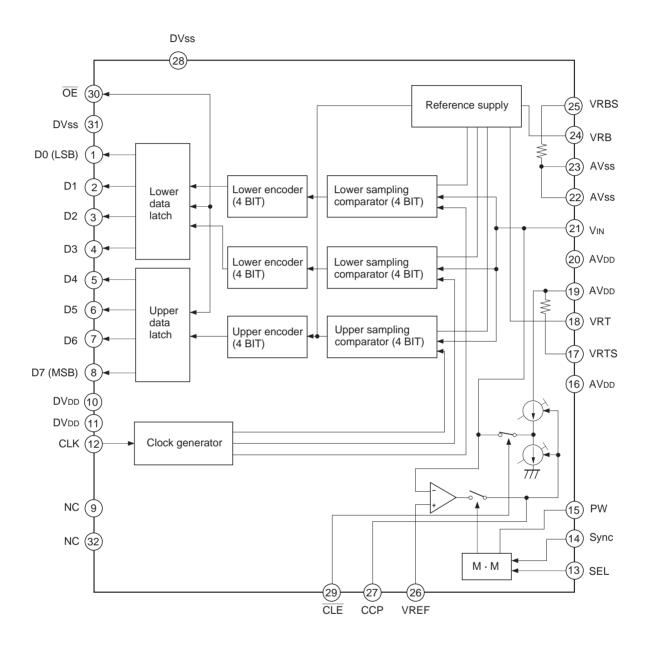

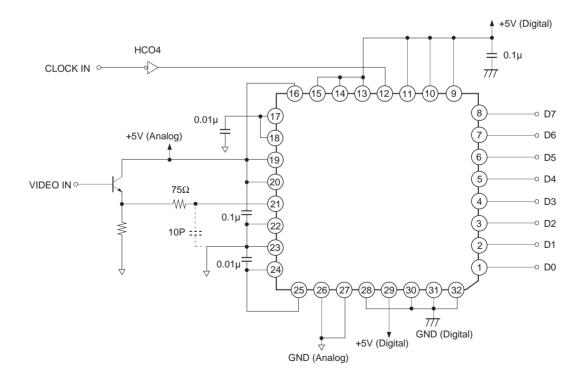

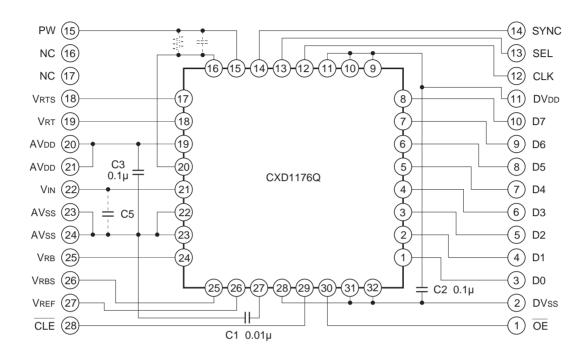

# **Block Diagram and Pin Configuration**

# **Pin Description**

| Pin No. | Symbol   | Equivalent circuit     | Description                                                                                                                                                                                                                   |

|---------|----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 8  | D0 to D7 | Di O                   | D0 (LSB) to D7 (MSB) output                                                                                                                                                                                                   |

| 9, 32   | NC       |                        | NC pin                                                                                                                                                                                                                        |

| 10, 11  | DVDD     |                        | Digital +5 V                                                                                                                                                                                                                  |

| 12      | CLK      | DVDD  DVSS             | Clock input                                                                                                                                                                                                                   |

| 13      | SEL      | DVDD  DVSS             | When SEL is at low, with the falling edge of Pin 14 (sync) as trigger, the monostable multivibrator generates clamp pulses. When SEL is at high, with the rising edge of Pin 14 (sync) as trigger, it generates clamp pulses. |

| 14      | Sync     | DVDD  OTHER DVDD  DVSS | Trigger pulse input to the monostable multivibrator. Trigger polarity can be selected through Pin 13 (SEL).                                                                                                                   |

| Pin No.    | Symbol | Equivalent circuit                          | Description                                                                                                                                                                                                                                                                                        |

|------------|--------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | PW     | DVDD<br>DVss                                | When a clamp pulse is generated at the monostable multivibrator, the pulse width is determined by the external R and C. When the clamp pulse is directly input, it is input to Pin 15 (PW). The signal voltage of the low period is clamped. (Here, Pin 14 (sync) is fixed to either low or high.) |

| 16, 19, 20 | AVDD   |                                             | Analog +5 V                                                                                                                                                                                                                                                                                        |

| 17         | VRTS   | AVDD  O  T  T  T  T  T  T  T  T  T  T  T  T | When shorted with VRT, generates approx. +2.6 V.                                                                                                                                                                                                                                                   |

| 18         | VRT    | AVDD   p                                    | Reference voltage (top)                                                                                                                                                                                                                                                                            |

| 24         | VRB    | (18) (24)<br>AVss                           | Reference voltage (bottom)                                                                                                                                                                                                                                                                         |

| 21         | Vin    | AVDD<br>AVSS                                | Analog input                                                                                                                                                                                                                                                                                       |

| 22, 23     | AVss   |                                             | Analog ground                                                                                                                                                                                                                                                                                      |

| 25         | VRBS   | AVss<br>25                                  | When shorted with VRB, generates approx. +0.5 V.                                                                                                                                                                                                                                                   |

| Pin No. | Symbol | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                          |  |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 26      | VREF   | AVDD  26  AVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Clamp reference voltage input. Clamps to provide a clamp period input signal equal to the reference voltage.                                                                                                                                                                                                         |  |

| 27      | CCP    | AVDD<br>27<br>AVss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Integrates the voltage for clamp control. CCP and VIN voltage changes are in positive phase.                                                                                                                                                                                                                         |  |

| 28, 31  | DVss   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital ground.                                                                                                                                                                                                                                                                                                      |  |

| 29      | CLE    | DVDD  29  CLAMP PULSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | When $\overline{\text{CLE}}$ is at low, clamp function is activated. When $\overline{\text{CLE}}$ is at high, clamp function is OFF and only the usual A/D converter function is active. By connecting $\overline{\text{CLE}}$ pin to DVpd via a several hundred $\Omega$ resistance, the clamp pulse can be tested. |  |

| 30      | ŌĒ     | DVDD  OVDD  OVDD | When $\overline{OE}$ is at low, Data is output.<br>When $\overline{OE}$ ia at high, D0 to D7 pins<br>turn to high impedance.                                                                                                                                                                                         |  |

# **Digital Output**

Correspondence between the analog input voltage and the digital output code is indicated in the chart below.

| Input signal voltage                     | Step                             | Digital output code<br>MSB LSB        |

|------------------------------------------|----------------------------------|---------------------------------------|

| VRT<br>:<br>:<br>:<br>:<br>:<br>:<br>VRB | 0<br>:<br>127<br>128<br>:<br>255 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

o : Points where analog signals are sampled.

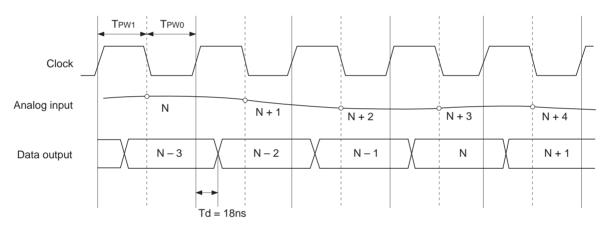

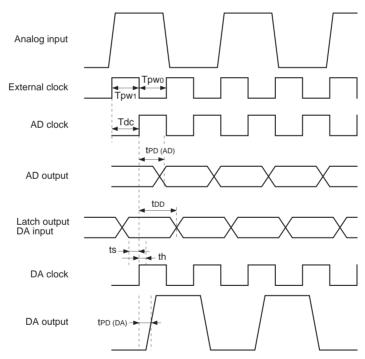

Timing Chart. I

Timing Chart. II

#### **Electrical Characteristics**

# **Analog characteristics**

$(Fc = 20 \text{ MSPS}, VDD = 5 \text{ V}, VRB = 0.5 \text{ V}, VRT = 2.5 \text{ V}, Ta = 25 ^{\circ}C)$

| Item                               | Symbol | Cond                                                                                 | ditions      | Min. | Тур. | Max. | Unit |

|------------------------------------|--------|--------------------------------------------------------------------------------------|--------------|------|------|------|------|

| Conversion speed                   | Fc     | VDD = 4.75 to 5.25 V<br>Ta = -40 to +85 °C<br>VIN = 0.5 to 2.5 V<br>fIN = 1 kHz ramp |              | 0.5  |      | 20   | MSPS |

| Analog input band width (–1dB)     | BW     | Envelope                                                                             |              |      | 18   |      | MHz  |

| Offeet voltage*1                   | Еот    | Potential differ                                                                     | ence to VRT  | -60  | -40  | -20  | mV   |

| Offset voltage*1                   | Еов    | Potential difference to VRB                                                          |              | +20  | +40  | +60  | 1117 |

| Integral non-linearity error       | EL     | End point                                                                            |              |      | +0.5 | +1.3 | LSB  |

| Differential non-linearity error   | Ed     |                                                                                      |              |      | ±0.3 | ±0.5 |      |

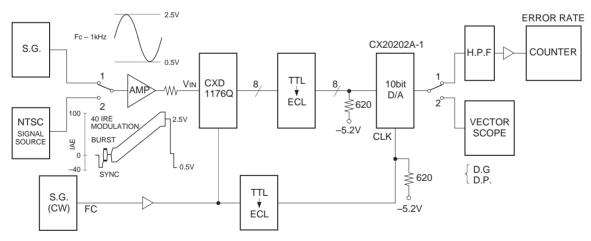

| Differential gain error            | DG     | NTSC 40 IRE                                                                          | mod ramp     |      | 1.0  |      | %    |

| Differential phase error           | DP     | Fc = 14.3 MSP                                                                        | S            |      | 0.5  |      | deg  |

| Aperture jitter                    | taj    |                                                                                      |              |      | 30   |      | ps   |

| Sampling delay                     | tsd    |                                                                                      |              |      | 4    |      | ns   |

| Clamp offeet valte se*2            | Гаа    | VIN = DC,                                                                            | VREF = 0.5 V | 0    | +20  | +40  | mV   |

| Clamp offset voltage*2             | Eoc    | PWS = 3 µs                                                                           | VREF = 2.5 V | -50  | -30  | -10  | IIIV |

| Clamp pulse width (Sync pin input) | tcpw   | C = 100  pF,<br>$R = 130 \text{ k}\Omega \text{ (15 PIN)}$                           |              | 1.75 | 2.75 | 3.75 | μs   |

| Clamp pulse delay                  | tcpd   |                                                                                      |              |      | 25   |      | ns   |

<sup>\*1</sup> The offset voltage EOB is a potential difference between VRB and a point of position where the voltage drops equivalent to 1/2 LSB of the voltage when the output data changes from "00000000" to "00000001". EOT is a potential difference between VRT and a potential of point where the voltage rises equivalent to 1/2LSB of the voltage when the output data changes from "111111111" to "11111110".

<sup>\*2</sup> Clamp offset voltage varies individually. When using with R, G, B 3 channels, color sliding may be generated.

### **DC** characteristics

$(Fc = 20 \text{ MSPS}, Vdd = 5 \text{ V}, VRB = 0.5 \text{ V}, VRT = 2.5 \text{ V}, Ta = 25 ^{\circ}C)$

| Item                                 |                  | C                                      | onditions         | Min. | Тур. | Max. | Unit      |

|--------------------------------------|------------------|----------------------------------------|-------------------|------|------|------|-----------|

| Supply current                       | IDD              | Fc = 20 MSPS<br>NTSC ramp wave input   |                   |      | 12   | 18   | mA        |

| Reference pin current                | IREF             |                                        |                   | 4.5  | 6.6  | 8.7  | mA        |

| Analog input capacitance             | Cin              | VIN = 1.5 V -                          | + 0.07 Vrms       |      | 11   |      | pF        |

| Reference resistance<br>(VRT to VRB) | RREF             |                                        |                   | 230  | 300  | 450  | Ω         |

| Calf hissa I                         | VRB <sub>1</sub> | VRB and VF                             | RBS are shorted   | 0.48 | 0.52 | 0.56 | V         |

| Self-bias I                          | VRT1 to VRB1     | VRT and VRTS are shorted               |                   | 1.96 | 2.08 | 2.22 | \ \ \ \ \ |

| Self-bias II                         | VRT2             | VRB = AGND<br>VRT and VRTS are shorted |                   |      | 2.32 |      | V         |

| Digital input valtage                | ViH              | VDD = 4.75 t                           | to 5.25 V         | 4.0  |      |      | V         |

| Digital input voltage                | VIL              | Ta = $-40 \text{ to}$                  | +85 °C            |      |      | 1.0  | V         |

| Digital input assurant               | Іін              | \/ may                                 | VIH = VDD         |      |      | 5    |           |

| Digital input current                | lıL              | V <sub>DD</sub> = max                  | VIL = 0V          |      |      | 5    | μA        |

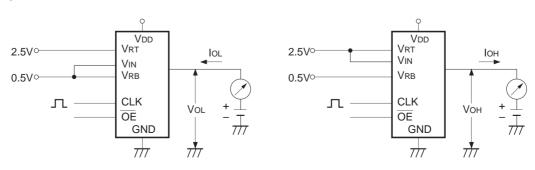

|                                      | Іон              | OE = Vss                               | Voh = Vdd - 0.5 V | -1.1 |      |      | mA        |

| Digital autout aurrent               | loL              | VDD = min                              | VoL = 0.4V        | 3.7  |      |      | IIIA      |

| Digital output current               | lozн             | OE = VDD                               | Voh = Vdd         |      |      | 16   |           |

|                                      | lozL             | V <sub>DD</sub> = max                  | Vol = 0V          |      |      | 16   | μA        |

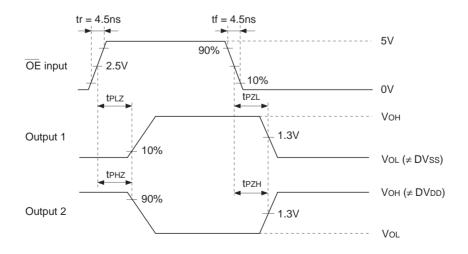

# **Timing** (Fc = 20 MSPS, VDD = 4.75 to 5.25 V, VRB = 0.5 V, VRT = 2.5 V, Ta = -40 to +85 °C)

| Item                          | Symbol                               | Conditions                                                                                                     | Min. | Тур. | Max. | Unit |

|-------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Output data delay             | TDL                                  | with TTL 1 gate and 10pF load                                                                                  |      | 18   | 30   | ns   |

| Tri-state output enable time  | tpzh<br>tpzl                         | $\frac{R_L = 1k\Omega, C_L = 20 \text{ pF}}{\overline{OE} = 3 \text{ V} \rightarrow 0 \text{ V}}$              | 2.5  | 6    | 10   | ns   |

| Tri-state output disable time | t <sub>PHZ</sub><br>t <sub>PLZ</sub> | $R_L = 1 \text{ k}\Omega, C_L = 20 \text{ pF}$<br>$\overline{\text{OE}} = 0 \text{ V} \rightarrow 3 \text{ V}$ | 8    | 18   | 30   | ns   |

#### **Electrical Characteristics Measurement Circuit**

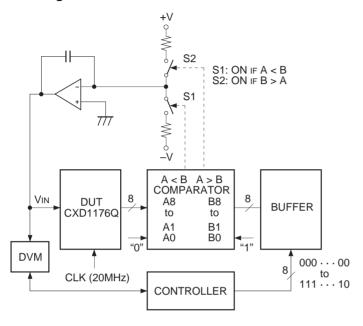

# Integral non-linearity error Differential non-linearity error Offset voltage

# measurement circuit

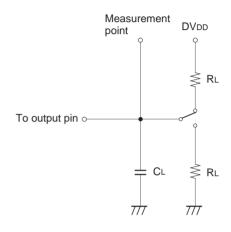

# Tri-state output measurement circuit

Note) CL includes capacitance of the probe and others.

# Maximum operational speed Differential gain error Differential phase error

# measurement circuit

Digital output current measurement circuit

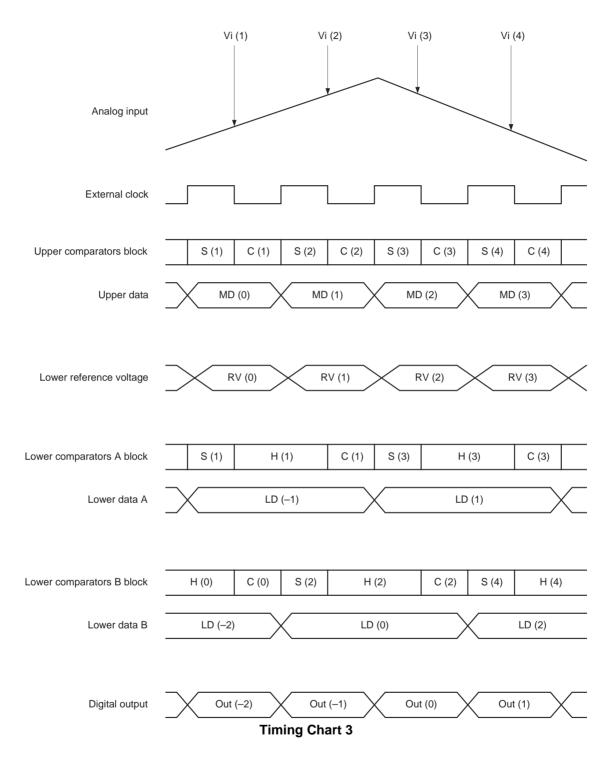

### **Operation** (See Block Diagram and Timing Chart 3)

1. The CXD1176Q is a 2-step parallel system A/D converter featuring a 4-bit upper comparators group and 2 lower comparators groups of 4-bit each. The reference voltage that is equal to the voltage between VRT – VRB/16 is constantly applied to the upper 4-bit comparator block. Voltage that corresponded to the upper data is fed through the reference supply to the lower data. VRTS and VRBS pins serve for the self generation of VRT (Reference voltage top) and VRB (Reference voltage bottom).

2. This IC uses an offset cancel type comparator and operates synchronously with an external clock. It features the following operating modes which are respectively indicated on the timing chart with S, H, C symbols. That is input sampling (auto zero) mode, input hold mode and comparison mode.

The operation of respective parts is as indicated in the chart. For instance input voltage Vi (1) is sampled with the falling edge of the first clock by means of the upper comparator block and the lower comparator A block.

The upper comparators block finalizes comparison data MD (1) with the rising edge of the first clock. Simultaneously the reference supply generates the lower reference voltage RV (1) that corresponded to the upper results. The lower comparator block finalizes comparison data LD (1) with the rising edge of the second clock. MD (1) and LD (1) are combined and output as Out (1) with the rising edge of the 3rd clock. Accordingly there is a 2.5 clock delay from the analog input sampling point to the digital data output.

### **Operation Notes**

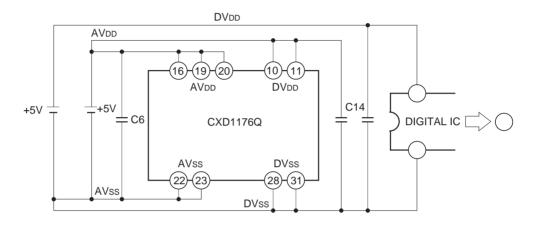

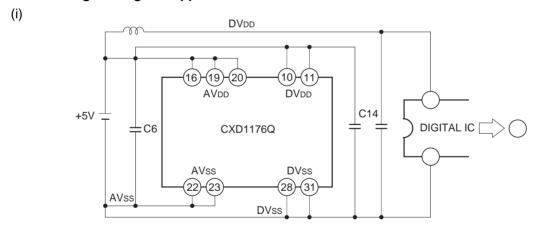

#### 1. VDD, Vss

To reduce noise effects, separate the analog and digital systems close to the device. For both the digital and analog  $V_{DD}$  pins, use a ceramic capacitor of about 0.1  $\mu F$  set as close as possible to the pin to bypass to the respective GND's.

#### 2. Analog input

Compared with the flash type A/D converter, the input capacitance of the analog input is rather small. However it is necessary to conduct the drive with an amplifier featuring sufficient band and drive capability. When driving with an amplifier of low output impedance, parasite oscillation may occur. That may be prevented by inserting a resistance of about 100  $\Omega$  in series between the amplifier output and A/D input.

### 3. Clock input

The clock line wiring should be as short as possible also, to avoid any interference with other signals, separate it from other circuits.

#### 4. Reference input

Voltage between VRT to VRB is compatible with the dynamic range of the analog input. Bypassing VRT and VRB pins to GND, by means of a capacitor about 0.1  $\mu$ F, stable characteristics are obtained. By shorting VRT and VRTS, VRB and VRBS, the self-bias function that generates VRT = 2.6 V and VRB = 0.6 V, is activated.

#### 5. Timing

Analog input is sampled with the falling edge of CLK and output as digital data with a delay of 2.5 clocks and with the following rising edge. The delay from the clock rising edge to the data output is about 18 ns.

# 6. $\overline{\text{OE}}$ pin

By connecting OE to GND output mode is obtained. By connecting to VDD high impedance is obtained.

#### 7. About latch up

It is necessary that AVDD and DVDD pins be the common source of power supply.

This is to avoid latch up due to the voltage difference between AVDD and DVDD pins when power is ON.

#### **Application Circuit**

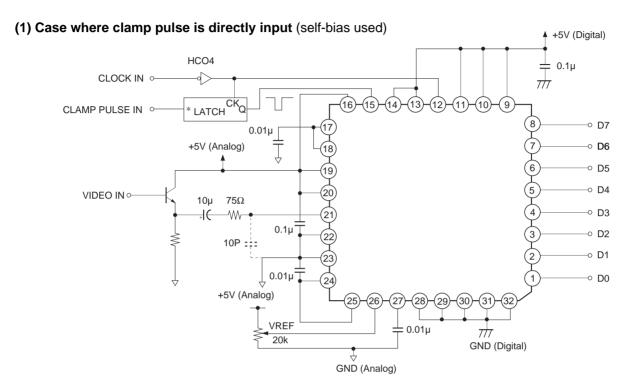

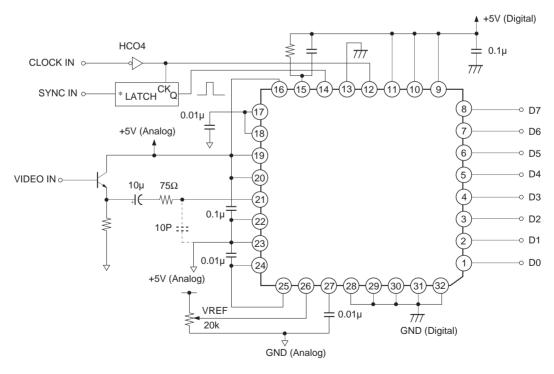

# (2) Example where pedestal clamp is executed by sync pulse (self-bias used)

<sup>\*</sup> The clamp pulse is latched by the ADC sampling clock, but that is not necessary for clamp basic operation.

However, slight beat may be generated as vertical sag according to the relation between the sampling frequency and clamp pulse frequency.

At such time, the latch circuit is effective. (See page 20 Notes on Operation 5.)

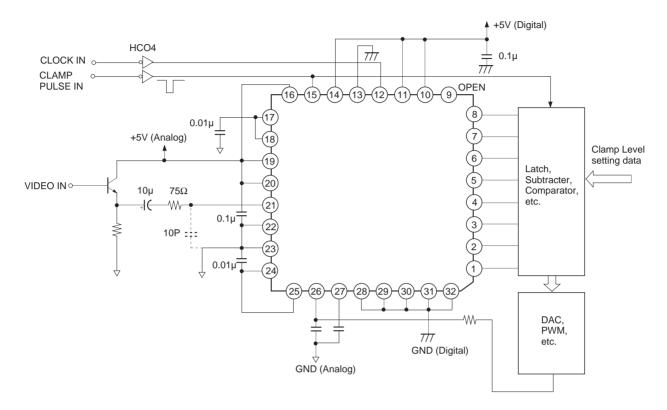

### (3) Digital clamp (self-bias used)

# (4) When clamp is not used (self-bias used)

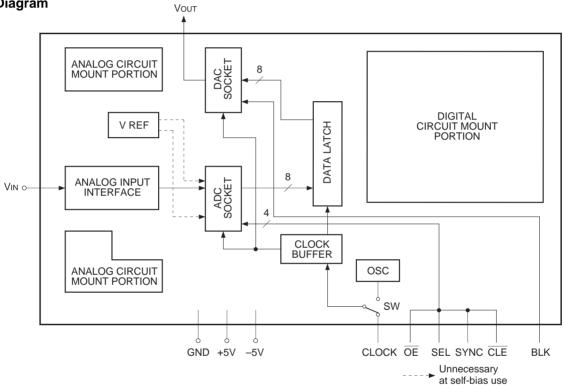

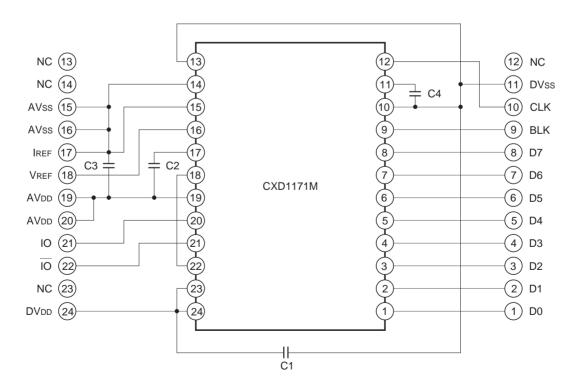

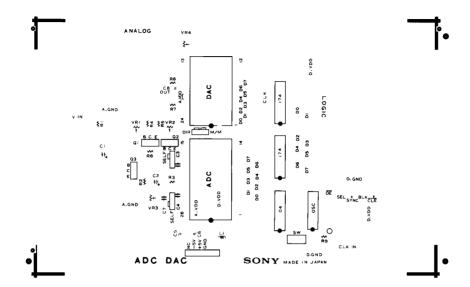

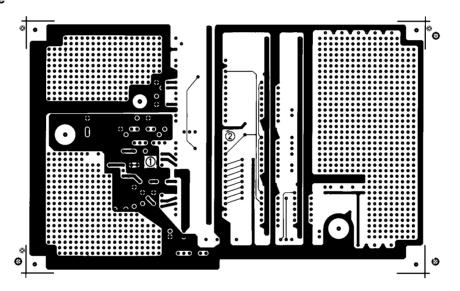

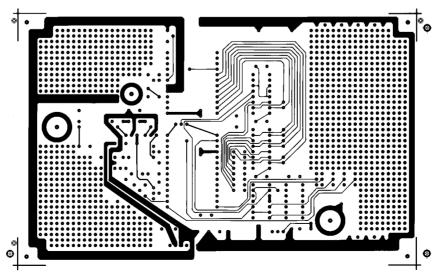

#### 8-bit 20MSPS ADC and DAC Evaluation Board

Evaluation boards are available for the high speed, low power consumption CMOS converters, CXD1176Q (8-bit 20MHz A/D) and CXD1171M (8-bit 40MHz D/A).

The evaluation board is composed of a main board common to either type, to which is added sub board CXD1176Q or sub board CXD1171M. The junction is made through a socket.

To the main board are mounted an input interface, clock buffer and latch. To each of the sub boards is mounted CXD1176Q and CXD1171M respectively. Those IC's are mounted according to recommended print patterns designed to provide maximum performance to the A/D and D/A converters.

#### **Block Diagram**

#### Characteristics

Resolution

Maximum conversion rate

Digital input level

B bit

20 MHz

CMOS level

• Supply voltage ±5.0 V (Single +5 V power supply possible at self bias use)

## Supply voltage

| Item         | Min. | Тур. | Max.      | Unit |

|--------------|------|------|-----------|------|

| +5 V<br>-5 V |      |      | 150<br>20 | mA   |

#### **Clock input**

CMOS compatible

Pulse width Tcw1 22.5 ns (min)

Tcwo 22.5 ns (min)

# **Analog Output (CXD1171M)**

$(RL > 10 \text{ k}\Omega)$

| Item          | Min. | Тур. | Max. | Unit |

|---------------|------|------|------|------|

| Analog output | 1.9  | 2.0  | 2.1  | ٧    |

# Output Format (CXD1176Q)

The table shows the output format of AD Converter.

| Analog input voltage | Step     | Digital output co | ode<br>LSB |

|----------------------|----------|-------------------|------------|

| Vrt<br>:             | 0        | 1 1 1 1 1 1       | 1 1        |

| :                    | 127      | 100000            | 0 0        |

|                      | 128<br>: | 0 1 1 1 1 1       | 1 1        |

| VRB                  | 255      | 0 0 0 0 0         | 0 0        |

# **Timing Chart**

| Item               | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------|------------------|------|------|------|------|

| Clock High time    | T <sub>PW1</sub> | 25   |      |      | ns   |

| Clock Low time     | T <sub>PW0</sub> | 25   |      |      | ns   |

| Clock Delay        | Tdc              |      |      | 24   | ns   |

| Data delay AD      | tPD (AD)         |      | 18   | 30   | ns   |

| Data delay (latch) | <b>t</b> DD      |      |      | 5    | ns   |

| Set up time        | <b>t</b> s       | 5    |      |      | ns   |

| Hold time          | th               | 10   |      |      | ns   |

| Data delay DA      | tPD (DA)         |      | 10   |      | ns   |

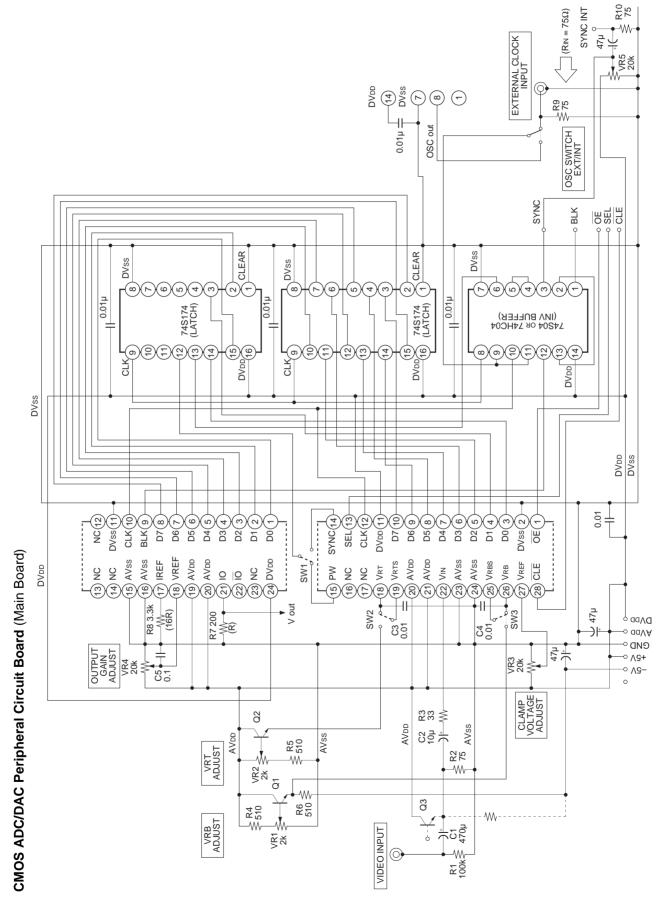

## CMOS ADC/DAC Peripheral Circuit Board (Sub Board)

#### **List of Parts**

| resistance |                          | transistor |         |

|------------|--------------------------|------------|---------|

| R1         | 100 kΩ                   | Q1         | 2SC2785 |

| R2         | 75 Ω                     | Q2         | 2SC2785 |

| R3         | 75 Ω                     | Q3         | 2SC2785 |

| R4         | 510 Ω                    |            |         |

| R5         | 510 Ω                    | IC         |         |

| R6         | 510 Ω                    | ĪC1        | 74S174  |

| R7         | $R = 200 \Omega$         | IC2        | 74S174  |

| R8         | $18R\approx 3.3~k\Omega$ | IC3        | 74S04   |

| R9         | 75 Ω                     |            |         |

| R10        | 75 Ω                     | oscillator |         |

| VR1        | 2 kΩ                     | OSC        |         |

| VR2        | 2 kΩ                     |            |         |

| VR3        | 20 kΩ                    | others     |         |

| VR4        | 20 kΩ                    | connector  | BNC071  |

| VR5        | 20 kΩ                    | SW         | AT1D2M3 |

|            |                          |            |         |

| capacitano | ce                      |

|------------|-------------------------|

| C1         | 470 µF/6.3 V (chemical) |

| C2         | 10 µF/16 V (chemical)   |

| C3         | 0.01 μF                 |

| C4         | 0.01 μF                 |

| C5         | 0.1 μF                  |

| C6         | 0.1 μF                  |

| C7         | 0.1 μF                  |

| C8         | 0.1 μF                  |

| C9         | 0.1 μF                  |

| C10        | 0.1 μF                  |

| C11        | 47 µF/10 V (chemical)   |

| C12        | 47 µF/10 V (chemical)   |

| C13        | 47 µF/10 V (chemical)   |

| C14        | 0.1 μF                  |

# Adjustment

1. Vref adjustment (VR1, VR2)

Adjustment of A/D converter reference voltage. VRB is adjusted through VR1 and VRT through VR2. When self-bias is used, there is no need for adjustment. Reference voltage is set through self-bias delivery.

2. Setting of clamp reference voltage (VR3)

Clamp reference voltage is set.

3. DAC output full-scale adjustment (VR4)

Full-scale voltage of D/A converter output is adjusted at the PCB shipment, the full-scale voltage is adjusted to approx. 2 V.

4. Sync (clamp) pulse interface (VR5)

This adjustment enables interface with the signal generator and others at the PCB shipment, adjustment is performed to obtain a threshold of approx. 2.5 V to an H sync of 0 to 5 V.

5. OE, SEL, Sync, BLK, CLE, Sync INT

The following pins are set on the main board:  $\overline{OE}$ , SEL, Sync,  $\overline{CLE}$ , Sync INT (CXD1176Q) and BLK (CXD1171M). For the pins function, refer to the specifications. The difference between Sync pin and Sync INT pin is that you input a horizontal synchronizing signal above 3.5 Vp-p Sync INT pin. The pulse threshold is set through VR5. For input through Sync pin, pulse is input at TTL or CMOS level. In this case cut off the junction line between Sync and Sync INT pin.

At the PCB shipment the main board pins are set as follows.

- OE ... Low (A/D output ON)

- SEL ... Low (Pulse generated with Sync falling edge as trigger)

- Sync ... Line junction with Sync INT pin

- CLE ... Low (Clamp function ON)

- BLK ... Low (Blanking OFF)

### 6. Clamp pulse input method

One method, as shown in Application Circuit examples (1) and (2), is to directly input the clamp pulse. The other is to use the built-in monostable multivibrator. The method is selected through SW1. At the PCB shipment it is set to direct input. To use the built-in monostable multivibrator, it is necessary to mount on the CXD1176Q sub board, R and C that determine pulse width.

(Ex. R = 130 k, C = 100 p, Tpw =

$$2.75 \mu s$$

Typ.)

#### Points on the PCB Pattern Layout

- 1. Set the layout not to have Digital current flow into Analog GND (Part 1). (For 1, See p. 23 Component side diagram.)

- 2. At CXD1176Q sub board, C2 and C3 capacitors serve the important role of bringing out CXD1176Q's full performance.

There are over 0.1  $\mu$ F (ceramic) capacitors with good high frequency characteristics. Layout as close to the IC as possible.

- Analog GND (AVss) and Digital GND (DVss) are on a common voltage and power source. Keeping ADC's DVss (Part 2) as close as possible to the voltage supply source will provide better results. That is, a layout where ADC is close to the voltage supply source, is recommended. (For 2, see p. 23 Component side diagram.)

- 4. ADC samples analog signals at the clock falling edge point. Accordingly clocks supplied to ADC should not have any jitter.

- 5. The PCB layout shows ADC and DAC's Analog GND independently from the voltage generating source. On this PCB, the layout aims at providing an independent evaluation of ADC and DAC, as much as possible. On the actual board, common use will not cause any problems.

## **Notes on Operation**

#### 1. Reference voltage

Shorting VRT and VRTS, VRB and VRBS will activate the self-bias function that generates VRT = 2.6 V and VRB = 0.5 V. On the PCB, either self-bias or the external reference voltage can be selected depending on the junction method of the jumper line. At shipment from the factory, reference voltage is provided in self-bias. Also, to provide external reference voltage, adjust the dynamic range (VRT - VRB) to above 1.8 Vp-p.

#### 2. Clock input

There are 2 modes for the PCB clock input

- 1) Provided from the external signal generator. (External clock)

- 2) Using the crystal oscillator (built-in clock driver). (Internal clock)

The 2 modes are selected using the switch on the PCB.

3. The 2 Latch IC's (74S174) are not absolutely necessary for the evaluation of ADC and DAC. That is, operation will still be normal if ADC output data is directly input to DAC input. However, as ADC output data is hardly ever D/A converted without executing Digital signal processing, it was mounted to indicate an example layout of Digital signal processing IC.

#### 4. When clamp is not used

Turning CLE to H will set OFF the clamp function. In this case, the DC element is cut off by means of  $C_2$  on the main board and DC voltage on the ADC side of  $C_2$  turns to about 1/2 ( $V_{RT} + V_{RB}$ ). To transfer DC elements of input signals, short  $C_2$ . At that time, it is necessary to bias input signals, but keeping  $R_2$  open,  $Q_3$  can also be used as buffer. Use the open space for the bias circuit.

#### 5. Clamp pulse latch

On the evaluation board, the clamp pulse is latched with ADC sampling CLK and then input to either PW pin or Sync pin. This is to minimize Vsag due the synchronizing of noise and clamp pulse beat elements with GND sampling clock around ADC. If there are no problems with Vsag, latch is not necessary.

#### 6. Peripheral through hole

There is a group of through holes on the Analog input, output and Logic. There are to be used when mounting additional circuits to the PCB. Use when necessary.

The connector hole on DAC part is used to mount the test chassis and the mount jack.

## **Latch Up Prevention**

The CXD1176Q is a CMOS IC which requires latch up precautions. Latch up is mainly generated by the lag in the voltage rising time of AVDD (Pins 16, 19 and 20) and DVDD (Pin 10 and 11), when power supply is ON.

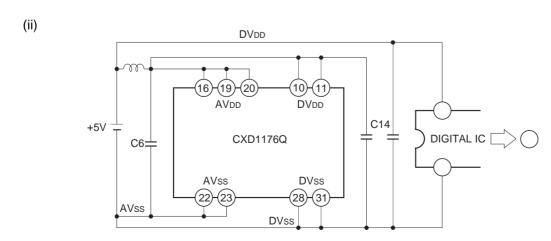

# 1. Correct usage

# a. When analog and digital supplies are from different sources

### b. When analog and digital supplies are from a common source

SONY

CXD1176Q

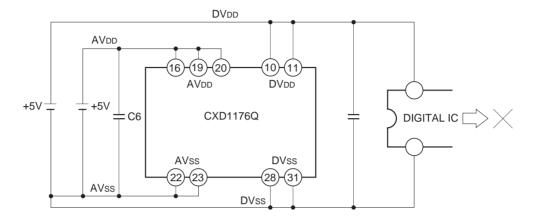

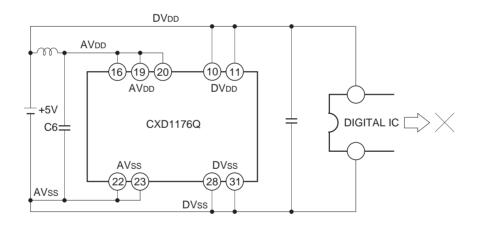

## 2. Example when latch up easily occurs

a. When analog and digital supplies are from different sources

# b. When analog and digital supplies are from a common source

(i)

(ii)

Silk Side

# **Component Side**

**Soldering Side** (Diagram seen from the component side)

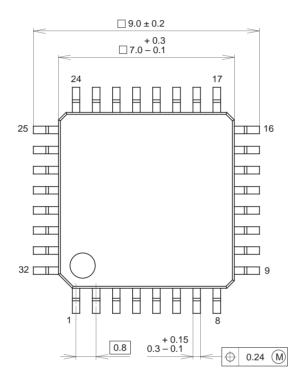

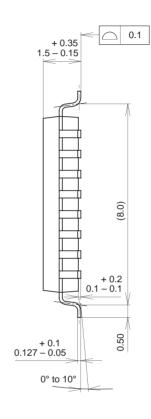

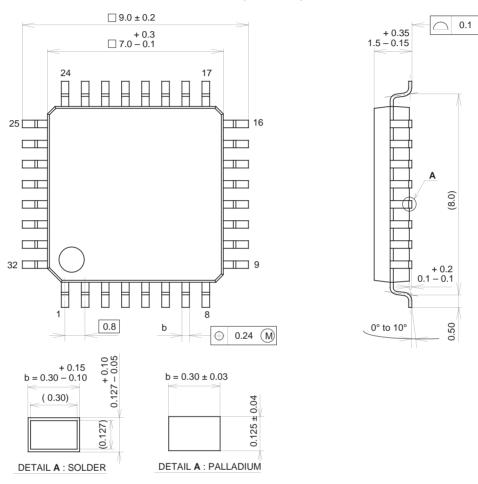

# Package Outline Unit: mm

# 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE MASS     | 0.2g           |

### Package Outline Unit: mm

# 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN                   |

|------------------|-------------------------------|

| LEAD TREATMENT   | SOLDER / PALLADIUM<br>PLATING |

| LEAD MATERIAL    | 42 / COPPER ALLOY             |

| PACKAGE MASS     | 0.2g                          |

NOTE: PALLADIUM PLATING

This product uses S. PdPPE (Serv. Spec. Polladium

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).