# SONY

# **CXD2452R**

# Timing Generator for Progressive Scan CCD Image Sensor

#### Description

The CXD2452R is a timing generator which generates the timing pulses for performing progressive scan readout for digital still cameras and personal computer image input applications using the ICX098AK CCD image sensor.

#### **Features**

- Base oscillation frequency 36.81MHz (2340fн)

- Monitoring readout allowed

- High-speed/low-speed electronic shutter function

- Horizontal driver for CCD image sensor

- Signal processor IC system clock generation 1170fн, 780fн

- · Vertical/horizontal sync (SSG) timing generation

#### **Applications**

- · Digital still cameras

- Personal computer image input

#### Structure

Silicon gate CMOS IC

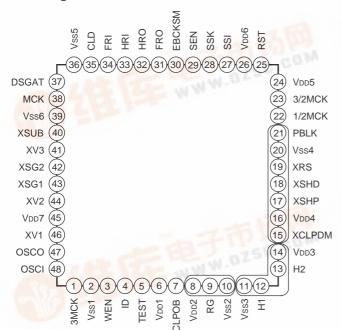

#### **Pin Configuration**

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul> | Vdd  | Vss - 0.5 to +7.0        | V  |  |  |  |  |  |  |

|------------------------------------|------|--------------------------|----|--|--|--|--|--|--|

| <ul> <li>Input voltage</li> </ul>  | Vı   | Vss - 0.5 to $Vdd + 0.5$ | V  |  |  |  |  |  |  |

| <ul> <li>Output voltage</li> </ul> | Vo   | Vss - 0.5 to VDD + 0.5   | V  |  |  |  |  |  |  |

| Operating temperature              |      |                          |    |  |  |  |  |  |  |

|                                    | Topr | -20 to +75               | °C |  |  |  |  |  |  |

| Storage temperature                |      |                          |    |  |  |  |  |  |  |

|                                    | Tstg | -55 to +150              | °C |  |  |  |  |  |  |

|                                    |      |                          |    |  |  |  |  |  |  |

#### **Recommended Operating Conditions**

Supply voltage

VDDA, VDDB, VDDC, VDDD

3.0 to 3.6

Operating temperature

Topr

-20 to +75

#### Applicable CCD Image Sensors

ICX098AK (Type 1/4 CCD)

\*Groups of pins enclosed in the fingure indicate sections for which power supply separationis possible.

reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the peration of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

\_ \_\_\_\_

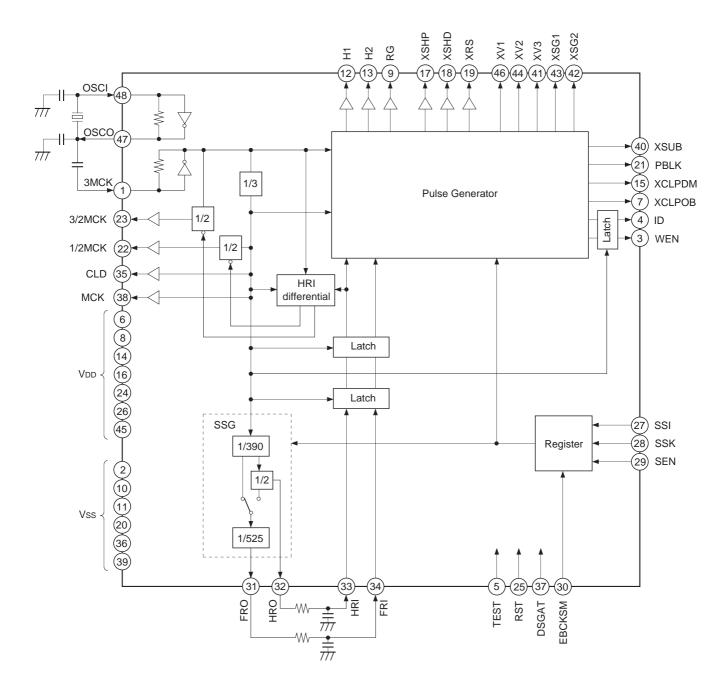

# **Block Diagram**

# **Pin Description**

| Pin<br>No. | Symbol            | I/O | Description                                                                                                      |

|------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------|

| 1          | змск              | ı   | Internal main clock. (2340fн)                                                                                    |

| 2          | Vss1              | _   | GND                                                                                                              |

| 3          | WEN               | 0   | Memory write timing. Stop control possible using the serial interface data.                                      |

| 4          | ID                | 0   | Vertical direction line identification pulse output. Stop control possible using the serial interface data.      |

| 5          | TEST              | I   | IC test pin; normally fixed to GND. (With pull-down resistor)                                                    |

| 6          | VDD1              | _   | 3.3V power supply. (Power supply for common logic block)                                                         |

| 7          | XCLPOB            | 0   | CCD optical black signal clamp pulse output. Stop control possible using the serial interface data.              |

| 8          | VDD2              | _   | 3.3V power supply. (Power supply for RG)                                                                         |

| 9          | RG                | 0   | CCD reset gate pulse output. (780fн)                                                                             |

| 10         | Vss2              | _   | GND                                                                                                              |

| 11         | Vss3              | _   | GND                                                                                                              |

| 12         | H1                | 0   | CCD horizontal register drive clock output. (780fн)                                                              |

| 13         | H2                | 0   | CCD horizontal register drive clock output. (780fн)                                                              |

| 14         | VDD3              | _   | 3.3V power supply. (Power supply for H1/H2)                                                                      |

| 15         | XCLPDM            | 0   | Pulse output for dummy bit block clamp .                                                                         |

| 16         | V <sub>DD</sub> 4 | _   | 3.3V power supply. (Power supply for CDS system)                                                                 |

| 17         | XSHP              | 0   | Precharge level sample-and-hold pulse output. (780fн)                                                            |

| 18         | XSHD              | 0   | Data level sample-and-hold pulse output. (780fн)                                                                 |

| 19         | XRS               | 0   | Sample-and-hold pulse output for analog/digital conversion phase alignment. (780fн)                              |

| 20         | Vss4              | _   | GND                                                                                                              |

| 21         | PBLK              | 0   | Pulse output for horizontal and vertical blanking interval pulse cleaning.                                       |

| 22         | 1/2MCK            | 0   | Horizontal direction pixel identification pulse output. Stop control possible using the serial interface data.   |

| 23         | 3/2MCK            | _   | System clock output for signal processing IC (1170fн). Stop control possible using the serial interface data.    |

| 24         | VDD5              | _   | 3.3V power supply. (Power supply for common logic block)                                                         |

| 25         | RST               | I   | Internal system reset input. High: Normal status, Low: Reset status Always input one reset pulse after power-on. |

| 26         | VDD6              | _   | 3.3V power supply. (Power supply for common logic block)                                                         |

| 27         | SSI               | ı   | Serial interface data input for internal mode settings.                                                          |

| 28         | SSK               | ı   | Serial interface clock input for internal mode settings.                                                         |

| 29         | SEN               | ı   | Serial interface strobe input for internal mode settings.                                                        |

| 30         | EBCKSM            | I   | CHKSUM enable. (With pull-down resistor) High: Sum check invalid, Low: Sum check valid                           |

| 31         | FRO               | 0   | Vertical sync signal output. Stop control possible using the serial interface data.                              |

| Pin<br>No. | Symbol | I/O | Description                                                                                                                                                                                                                   |

|------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32         | HRO    | 0   | Horizontal sync signal output. Stop control possible using the serial interface data.                                                                                                                                         |

| 33         | HRI    | I   | Horizontal sync signal input.                                                                                                                                                                                                 |

| 34         | FRI    | I   | Vertical sync signal input.                                                                                                                                                                                                   |

| 35         | CLD    | 0   | Clock output for analog/digital conversion IC. (780fн) Phase adjustment in 60° units possible using the serial interface data.                                                                                                |

| 36         | Vss5   | _   | GND                                                                                                                                                                                                                           |

| 37         | DSGAT  | I   | Control input used to stop pulse generation for CCD image sensor, sample-and-hold IC and analog/digital conversion IC. High: Normal status, Low: Stop status Controlled pulse can be changed using the serial interface data. |

| 38         | MCK    | 0   | System clock output for signal processor IC. (780fн)                                                                                                                                                                          |

| 39         | Vss6   | _   | GND                                                                                                                                                                                                                           |

| 40         | XSUB   | 0   | Pulse output for electronic shutter.                                                                                                                                                                                          |

| 41         | XV3    | 0   | CCD vertical register drive pulse output.                                                                                                                                                                                     |

| 42         | XSG2   | 0   | CCD sensor readout pulse output.                                                                                                                                                                                              |

| 43         | XSG1   | 0   | CCD sensor readout pulse output.                                                                                                                                                                                              |

| 44         | XV2    | 0   | CCD vertical register drive pulse output.                                                                                                                                                                                     |

| 45         | VDD7   | _   | 3.3V power supply. (Power supply for common logic block)                                                                                                                                                                      |

| 46         | XV1    | 0   | CCD vertical register drive pulse output.                                                                                                                                                                                     |

| 47         | osco   | 0   | Inverter output for oscillation.                                                                                                                                                                                              |

| 48         | OSCI   | I   | Inverter input for oscillation.                                                                                                                                                                                               |

#### **Electrical Characteristics**

# **DC Characteristics**

| Item              | Pins                          | Symbol | Conditions                        | Min.       | Тур. | Max.    | Unit |

|-------------------|-------------------------------|--------|-----------------------------------|------------|------|---------|------|

| Supply voltage 1  | V <sub>DD</sub> 2             | Vdda   |                                   | 3.0        | 3.3  | 3.6     | V    |

| Supply voltage 2  | VDD3                          | Voob   |                                   | 3.0        | 3.3  | 3.6     | V    |

| Supply voltage 3  | V <sub>DD</sub> 4             | VDDC   |                                   | 3.0        | 3.3  | 3.6     | V    |

| Supply voltage 4  | VDD1, VDD5,<br>VDD6, VDD7     | VDDd   |                                   | 3.0        | 3.3  | 3.6     | V    |

| Input voltage 1*1 | RST, DSGAT,                   | VIH1   |                                   | 0.8VDDd    |      |         | V    |

| input voitage 1 1 | SSI, SSK, SEN,<br>FRI, HRI    | VIL1   |                                   |            |      | 0.2VDDd | V    |

| Input             | EBCKSM                        | VIH2   |                                   | 0.8VDDd    |      |         | V    |

| voltage 2*1 *2    | EBCKSW                        | VIL2   |                                   |            |      | 0.2Vppd | V    |

| Input             | TEST                          | VIH3   |                                   | 0.7VDDd    |      |         | V    |

| voltage 3*2       | 1231                          | VIL3   |                                   |            |      | 0.3Vppd | V    |

| Output            | RG                            | Voн1   | Feed current where IoH = -3.3mA   | VDDa - 0.8 |      |         | V    |

| voltage 1         | NG                            | Vol1   | Pull-in current where IoL = 2.4mA |            |      | 0.4     | V    |

| Output            | H1, H2                        | Voh2   | Feed current where IoH = -10.4mA  | VDDb - 0.8 |      |         | V    |

| voltage 2         | N I, NZ                       | VOL2   | Pull-in current where IoL = 7.2mA |            |      | 0.4     | V    |

| Output            | XSHP, XSHD,<br>XRS, PBLK,     | Vонз   | Feed current where IoH = -3.3mA   | VDDC - 0.8 |      |         | V    |

| voltage 3         | XCLPDM                        | Vol3   | Pull-in current where IoL = 2.4mA |            |      | 0.4     | V    |

| Output            | 3/2MCK, MCK,                  | Voн4   | Feed current where IoH = -10.4mA  | VDDd - 0.8 |      |         | V    |

| voltage 4         | CLD                           | Vol4   | Pull-in current where IoL = 7.2mA |            |      | 0.4     | V    |

| Output            | 1/2MCK                        | Voн5   | Feed current where IoH = -3.3mA   | VDDd - 0.8 |      |         | V    |

| voltage 5         | 1/ZIVIOR                      | Vol5   | Pull-in current where IoL = 2.4mA |            |      | 0.4     | V    |

| Output            | XV1, XV2, XV3,<br>XSUB, XSG1, | Vон6   | Feed current where IoH = -2.4mA   | VDDd - 0.8 |      |         | V    |

| voltage 6         | XSG2, XCLPOB,<br>ID, WEN      | Vol6   | Pull-in current where IoL = 4.8mA |            |      | 0.4     | V    |

| Output            | FRO, HRO                      | Voн7   | Feed current where IoH = -3.6mA   | VDDd - 0.8 |      |         | V    |

| voltage 7         | TINO, TINO                    | Vol7   | Pull-in current where IoL = 7.2mA |            |      | 0.4     | V    |

<sup>\*1</sup> These input pins do not have protective diodes on the internal power supply side.

<sup>\*2</sup> These input pins have internal pull-down resistors.

<sup>\*3</sup> The above table indicates the condition for 3.3V drive.

#### Inverter I/O Characteristics for Oscillation

(Within the recommended operating conditions)

| Item                  | Pins       | Symbol | Conditions                        | Min.    | Тур.   | Max.    | Unit |

|-----------------------|------------|--------|-----------------------------------|---------|--------|---------|------|

| Logical Vth           | OSCI       | LVth   |                                   |         | VDDd/2 |         | V    |

| Input voltage         | OSCI       | ViH    |                                   | 0.7VDDd |        |         | V    |

|                       | USCI       | VIL    |                                   |         |        | 0.3VDDd | V    |

| Output voltage        | osco       | Vон    | Feed current where Іон = -6.0mA   | VDDd/2  |        |         | V    |

|                       |            | Vol    | Pull-in current where IoL = 6.0mA |         |        | VDDd/2  | V    |

| Feedback resistor     | OSCI, OSCO | RFB    | VIN = VDDd or Vss                 | 500k    | 2M     | 5M      | Ω    |

| Oscillation frequency | OSCI, OSCO | f      |                                   | 20      |        | 50      | MHz  |

# Inverter Input Characteristics for Base Oscillation Clock Duty Adjustment

| Item            | Pins | Symbol | Conditions              | Min.    | Тур.   | Max.    | Unit |

|-----------------|------|--------|-------------------------|---------|--------|---------|------|

| Logical Vth     |      | LVth   |                         |         | VDDd/2 |         | V    |

| Input voltage   |      | ViH    |                         | 0.7VDDd |        |         | V    |

|                 | змск | VIL    |                         |         |        | 0.3VDDd | V    |

| Input amplitude |      | Vin    | fmax 50MHz sine<br>wave | 0.3     |        |         | Vp-p |

<sup>\*1</sup> Input voltage is the input voltage characteristics for direct input from an external source. Input amplitude is the input amplitude characteristics in the case of input through capacitor.

SONY

CXD2452R

#### **AC Characteristics**

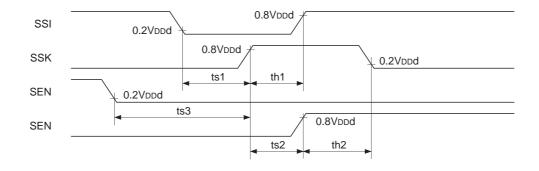

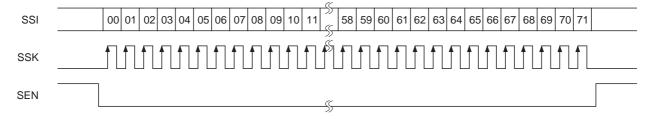

#### 1) AC characteristics between the serial interface clocks

#### (Within the recommended operating conditions)

| Symbol | Definition                                          | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------------------------|------|------|------|------|

| ts1    | SSI setup time, activated by the rising edge of SSK | 20   |      |      | ns   |

| th1    | SSI hold time, activated by the rising edge of SSK  | 20   |      |      | ns   |

| ts2    | SSK setup time, activated by the rising edge of SEN | 20   |      |      | ns   |

| th2    | SSK hold time, activated by the rising edge of SEN  | 20   |      |      | ns   |

| ts3    | SEN setup time, activated by the rising edge of SSK | 20   |      |      | ns   |

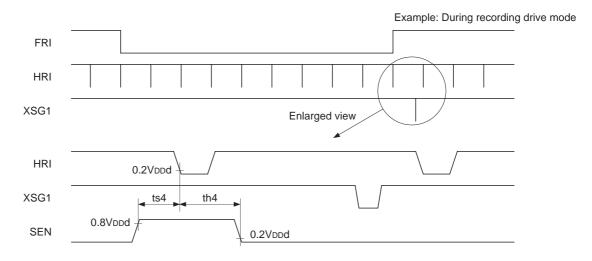

#### 2) Serial interface clock internal loading characteristics

**Note)** Be sure to maintain a constantly high SEN logic level near the HRI fall immediately before XSG1 generation.

| Symbol | Definition                                           | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------------|------|------|------|------|

| ts4    | SEN setup time, activated by the falling edge of HRI | 0    |      |      | ns   |

| th4    | SEN hold time, activated by the falling edge of HRI  | 0    |      |      | ns   |

SONY CXD2452R

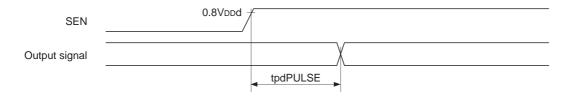

#### 3) Serial interface clock output variation characteristics

Normally, the serial interface data is loaded to the CXD2452R at the timing shown in 2) above. However, one exception to this is when the data such as SSGSEL and STB is loaded to the CXD2452R and controlled at the rising edge of SEN. For STB, see control data  $\boxed{D62}$  to  $\boxed{D63}$  STB in "Description of Operation".

(Within the recommended operating conditions)

| Symbol   | Definition                                               | Min. | Тур. | Max. | Unit |

|----------|----------------------------------------------------------|------|------|------|------|

| tpdPULSE | Output signal delay, activated by the rising edge of SEN | 5    |      | 100  | ns   |

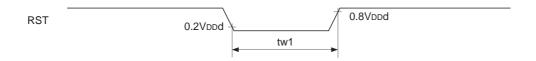

#### 4) RST loading characteristics

#### (Within the recommended operating conditions)

| Symbol | Definition      | Min. | Тур. | Max. | Unit |

|--------|-----------------|------|------|------|------|

| tw1    | RST pulse width | 35   |      |      | ns   |

#### 5) Phase identification characteristics using FRI and HRI input

When the HRI logic level is low tpd1 after the falling edge of FRI

FRI 0.2VDDd tpd1

The field is identified as an ODD field .

When the HRI logic level is high tpd1 after the falling edge of FRI

The field is identified as an EVEN field .

|        | ·                                                                      |      | •    | -    | •    |

|--------|------------------------------------------------------------------------|------|------|------|------|

| Symbol | Definition                                                             | Min. | Тур. | Max. | Unit |

| tpd1   | Field identification clock phase, activated by the falling edge of FRI | 1100 |      | 1300 | ns   |

SONY CXD2452R

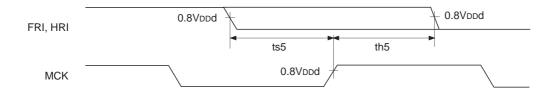

#### 6) FRI and HRI loading characteristics

MCK load capacitance = 10pF

(Within the recommended operating conditions)

| Symbol | Definition                                                  | Miin. | Тур. | Min. | Unit |

|--------|-------------------------------------------------------------|-------|------|------|------|

| ts5    | FRI and HRI setup time, activated by the rising edge of MCK | 10    |      |      | ns   |

| th5    | FRI and HRI hold time, activated by the rising edge of MCK  | 0     |      |      | ns   |

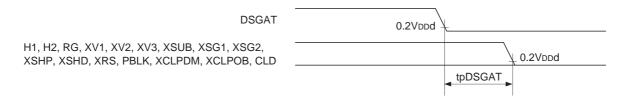

#### 7) Output timing characteristics using DSGAT

H1 and H2 load capacitance = 100pF, RG load capacitance = 20pF, XV1, XV2, XV3, XSG1, XSG2, XSUB, XSHP, XSHD, XRS, PBLK, XCLPDM, XCLPOB and CLD load capacitance = 10pF

(Within the recommended operating conditions)

| Symbol  | Definition                                                  | Min. | Тур. | Max. | Unit |

|---------|-------------------------------------------------------------|------|------|------|------|

| tpDSGAT | Time until the above outputs go low after the fall of DSGAT |      |      | 100  | ns   |

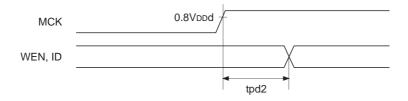

#### 8) Output variation characteristics

WEN and ID load capacitance = 10pF

| Symbol | Definition                                                | Miin. | Тур. | Min. | Unit |

|--------|-----------------------------------------------------------|-------|------|------|------|

| tpd2   | Time until the above outputs change after the rise of MCK | 20    |      | 40   | ns   |

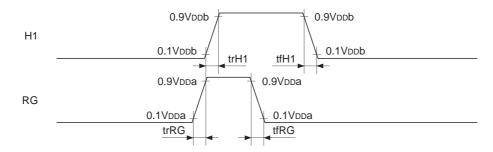

# 9) H1 and RG waveform characteristics

VDDb = 3.3V, Topr = 25°C, H1 and H2 load capacitance = 100pF, RG load capacitance = 20pF (Within the recommended operating conditions)

| Symbol | Definition   | Min. | Тур. | Max. | Unit |

|--------|--------------|------|------|------|------|

| trH1   | H1 rise time |      | 10   |      | ns   |

| tfH1   | H1 fall time |      | 10   |      | ns   |

| trRG   | RG rise time |      | 3    |      | ns   |

| tfRG   | RG fall time |      | 3    |      | ns   |

# 10) I/O pin capacitance

| Symbol | Definition             | Min. | Тур. | Max. | Unit |

|--------|------------------------|------|------|------|------|

| CIN    | Input pin capacitance  |      |      | 9    | pF   |

| Соит   | Output pin capacitance |      |      | 11   | pF   |

| CI/O   | I/O pin capacitance    |      |      | 11   | pF   |

#### **Description of Operation**

All pulses output from the CXD2452R are controlled by the RST and DSGAT pins and by the serial interface data shown below. The details of control by the serial interface data and a description of operation are as follows.

The CXD2452R basically loads and reflects the serial interface data sent in the above format in the readout portion at the falling edge of HRI. Here, readout portion specifies the horizontal interval during which XSG1 rises.

There are two types of serial interface data: drive control data and phase adjustment data. Hereafter, these data are distinguished by referring to the former as control data and the latter as adjustment data.

An example of the initialization data for the CXD2452R control data is shown below. This data is based on the Application Circuit Block Diagram, so care should be taken as there are some differences from the RST pin initialization data. Concretely, the internal SSG operates, the XCLPOB and ID pulses are generated, and the 3/2 MCK pulse is stopped. This data shows the values when the EBCKSM pin is low and D64 to D71 CHKSUM is valid.

| MSB |     |     |     |     |     |     |     |     |     |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D71 | D70 | D69 | D68 | D67 | D66 | D65 | D64 | D63 | D62 | D61 | D60 | D59 | D58 | D57 | D56 |

| 1   | 0   | 1   | 0   | 1   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| MSB |     |     |     |     |     |     |     |     |     |     |     |     |     |     | LSB |

| D55 | D54 | D53 | D52 | D51 | D50 | D49 | D48 | D47 | D46 | D45 | D44 | D43 | D42 | D41 | D40 |

| 1   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| MSB |     |     |     |     |     |     |     |     |     |     |     |     |     |     | LSB |

| D39 | D38 | D37 | D36 | D35 | D34 | D33 | D32 | D31 | D30 | D29 | D28 | D27 | D26 | D25 | D24 |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| MSB |     |     |     |     |     |     |     |     |     |     |     |     |     |     | LSB |

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D09 | D08 |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| MSB |     |     |     |     |     |     | LSB |     |     |     |     |     |     |     |     |

| D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 |     |     |     |     |     |     |     |     |

| 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |     |     |     |     |     |     |     |     |

The adjustment data does not normally need to be set. However, when adjustment is difficult due to the system configuration or for other reasons, the data considered most appropriate at that time should be set as the initialization data.

#### **Control Data**

| Data             | Symbol   | Function                                       | Data = 0                        | Data = 1          | When a reset |

|------------------|----------|------------------------------------------------|---------------------------------|-------------------|--------------|

| D00<br>to<br>D07 | CHIP     | Chip switching                                 | See D00 to D0                   | OT CHIP.          | All 0        |

| D08<br>to<br>D15 | CTGRY    | Category switching                             | See D08 to D                    | 15 CTGRY.         | All 0        |

| D16<br>to<br>D17 | SMD      | Electronic shutter mode setting                | See D16 to D3 Electronic shutte |                   | All 0        |

| D18<br>to<br>D25 | Shut.FRM | Electronic shutter vertical interval setting   | See D16 to D3 Electronic shutte | All 0             |              |

| D26<br>to<br>D35 | Shut.HD  | Electronic shutter horizontal interval setting | See D16 to D3                   |                   | All 0        |

| D36<br>to<br>D47 | _        | _                                              | _                               | _                 | All 0        |

| D48              | EXPOSE   | Recording exposure setting switching           | OFF                             | ON                | 0            |

| D49<br>to<br>D50 | _        | _                                              | _                               | _                 | All 0        |

| D51              | PSMT     | Drive mode switching                           | Monitoring                      | Recording         | 0            |

| D52              | SSGSEL   | Internal SSG operation switching               | OFF                             | ON                | 0            |

| D53              | WENSEL   | WEN pulse operation switching                  | ON                              | OFF               | 0            |

| D54              | CLPSEL   | XCLPOB pulse operation switching               | OFF                             | ON                | 0            |

| D55              | IDSEL    | ID pulse operation switching                   | OFF                             | ON                | 0            |

| D56              | HMCKSEL  | 1/2MCK pulse operation switching               | OFF                             | ON                | 0            |

| D57              | TMCKSEL  | 3/2MCK pulse operation switching               | ON                              | OFF               | 0            |

| D58              | HMCKREV  | 1/2MCK pulse reset polarity switching          | Positive polarity               | Negative polarity | 0            |

| D59              | TMCKREV  | 2/3MCK pulse reset polarity switching          | Negative polarity               | Positive polarity | 0            |

| D60<br>to<br>D61 | DSG      | Pulse generation control                       | See D60 to D6                   | DSG table.        | All 0        |

| D62<br>to<br>D63 | STB      | IC pin status control                          | See D62 to D6                   | STB table.        | All 0        |

| D64<br>to<br>D71 | CHKSUM   | Check sum bit                                  | See D64 to D7                   | 71 CHKSUM.        | All 0        |

SONY CXD2452R

#### **Detailed Description of Each Data**

# D00 to D07 CHIP

The serial interface data is loaded to the CXD2452R when  $\boxed{D00}$  and  $\boxed{D07}$  are 1. However, this assumes that either the EBCKSM pin is low and  $\boxed{D64}$  to  $\boxed{D71}$  CHKSUM is satisfied or the EBCKSM pin is high.

| MSB |     |     |     |     |     |     | LSB | Function                |  |

|-----|-----|-----|-----|-----|-----|-----|-----|-------------------------|--|

| D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 | Function                |  |

| 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Loading to the CXD2452R |  |

Note that when SEN is shared with other ICs and indentification is performed using CHIP-ID, the CXD2452R data must be positioned immeditately before the load timing, that is to say at the very end.

# D08 to D15 CTGRY

Of the data provided to the CXD2452R by the serial interface, the CXD2452R loads D16 and subsequent data to the control register side when D08 is 0, and to the adjustment register side when D08 is 1. However, this assumes that the CXD2452R is selected by CHIP and that either the EBCKSM pin is low and D64 to D71 CHKSUM is satisfied or the EBCKSM pin is high.

| MSB |     |     |     |     |     |     | LSB | E with a                                |  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----------------------------------------|--|

| D15 | D14 | D13 | D12 | D11 | D10 | D09 | D08 | Function                                |  |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Loading to the control register side    |  |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Loading to the adjustment register side |  |

Note that the CXD2452R cannot apply both categories simultaneously during the same vertical interval. Also, care should be taken as the data is overwritten even if the same category is applied.

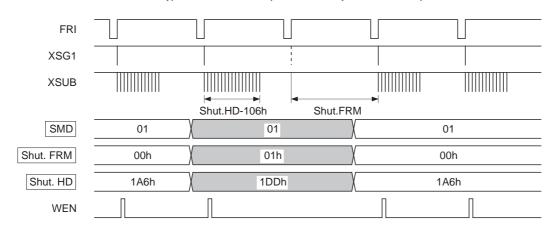

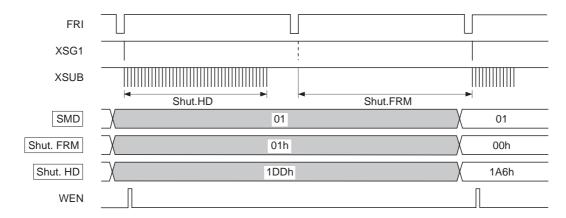

# D16 to D35 Electronic shutter mode

The CXD2452R's electronic shutter mode can be switched as follows by SMD  $\boxed{D16}$  to  $\boxed{D17}$ . Handling of the data from  $\boxed{D18}$  to  $\boxed{D35}$  differs according to the mode, and is explained in detail below.

| D17 | D16 | Description of operation          |

|-----|-----|-----------------------------------|

| Х   | 0   | XSUB stopped mode                 |

| 0   | 1   | High-speed/low-speed shutter mode |

| 1   | 1   | HTSG control mode                 |

The electronic shutter data is expressed as shown in the table below using Shut.HD as an example.

| MSB |     |     |     |     |     |     |     |     | LSB |  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| D35 | D34 | D33 | D32 | D31 | D30 | D29 | D28 | D27 | D26 |  |

| 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 1   | 1   |  |

|     | 1   |     | (   | C   |     | 3   |     |     |     |  |

Shut.HD is expressed as 1C3h

#### [XSUB stopped mode]

During this mode, the data from D18 to D35 is invalid. The shutter speed is 1/60s during monitoring drive mode, and 1/30s during recording drive mode.

#### [High-speed/low-speed shutter mode]

During this mode, the data has the following meanings.

| Symbol   | Data       | Description                                                       |

|----------|------------|-------------------------------------------------------------------|

| Shut.FRM | D18 to D25 | Shutter speed data (number of vertical intervals) specification   |

| Shut.HD  | D26 to D35 | Shutter speed data (number of horizontal intervals) specification |

The CXD2452R does not distinguish between the high-speed shutter and low-speed shutter modes. The interval during which Shut.FRM and Shut.HD are specified together is the shutter speed. At this time, Shut.FRM controls the XSG1, XSG2 output, and Shut.HD controls the XSUB output. Concretely, when specifying high-speed shutter, Shut.FRM is set to 00h. (See the figure.) During low-speed shutter, or in other words when Shut.FRM is set to 01h or higher, the serial interface data is not loaded until this interval is finished.

However, care should be taken as the vertical interval indicated here is set in 1/60s units when the drive mode is monitoring drive mode and 1/30s units during recording drive mode.

For monitoring drive mode, care should be taken that shut.HD value is offset. This is because the same exposure time can be obtained for the same shut.HD data without depending on drive mode basically for high-speed shutter.

Formula for calculating the electronic shutter speed: [Shut.FRM/Shut.HD] (unit: µs)

#### Monitoring drive mode:

$T = Shut.FRM*1.66834*10^4 + \{(20Ch - Shut.HD)*780 + 447\} *81.5*10^{-3} (107h \le Shut.HD \le 20Ch)$

During monitoring drive mode/low-speed shutter mode

#### Recording drive mode:

T = Shut.FRM\*3.33667\*10<sup>4</sup> + {(20Ch - Shut.HD)\*780 + 447} \*81.5\*10<sup>-3</sup> (000h  $\leq$  Shut.HD  $\leq$  20Ch)

During recording drive mode/low-speed shutter mode

#### Electronic shutter speed table [Shut.FRM/Shut.HD]

| Shut.FRM | Shut.HD | Shutter speed (s) | Calculation results (s) | Shut.FRM | Shut.HD | Shutter speed (s) | Calculation results (s) |

|----------|---------|-------------------|-------------------------|----------|---------|-------------------|-------------------------|

| 00h      | 20Ch    | 1/27000           | 1/27450                 | 00h      | 107h*1  | 1/60              | 1/60                    |

| 00h      | 20Bh    | 1/10000           | 1/10000                 | 01h      | 20Ch    | 1/60*2            | 1/60                    |

| 00h      | 209h    | 1/4500            | 1/4403                  | 01h      | 1D8h    | 1/50*2            | 1/50                    |

| 00h      | 205h    | 1/2000            | 1/2077                  | 02h      | 20Ch    | 1/30*2            | 1/30                    |

| 00h      | 1FDh    | 1/1000            | 1/1010                  | 07h      | 18Bh    | 1/8*²             | 1/8                     |

| 00h      | 1EDh    | 1/500             | 1/498                   | 09h      | 109h    | 1/6*²             | 1/6                     |

| 00h      | 1CEh    | 1/250             | 1/251                   | 00h      | 0D2h    | 1/50*3            | 1/50                    |

| 00h      | 18Fh    | 1/125             | 1/125                   | 00h      | 083h    | 1/40*3            | 1/40                    |

| 00h      | 16Fh    | 1/100             | 1/100                   | 00h      | 000h    | 1/30*3            | 1/30                    |

<sup>\*1</sup> One XSUB pulse is generated for odd fields and two for even fields.

# Note) Input prohibited data:

Monitoring drive mode

Recording drive mode and monitoring drive mode

000h to 106h

20Dh to 3FFh

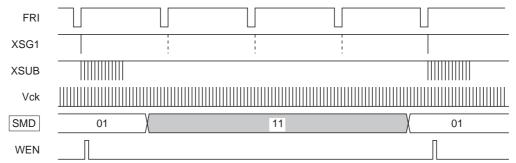

# [HTSG control mode]

During this mode, the data from D18 to D35 is invalid. The shutter speed is the value obtained by adding the shutter speed specified in the preceding vertical interval to the vertical period during which XSG1 (and XSG2) is stopped as shown in the figure.

**During HTSG control mode**

<sup>\*2</sup> These are the settings during monitoring drive mode.

<sup>\*3</sup> These can only be specified during recording drive mode.

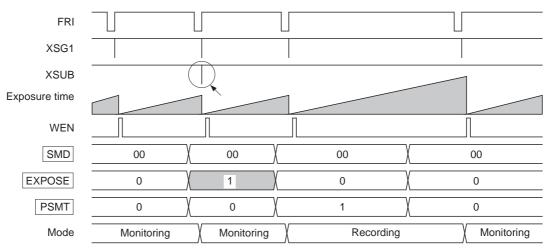

#### D48 EXPOSE

- 0: No operation

- 1: XSUB for recording exposure is generated.

This control specification is such that one XSUB pulse is always generated during the horizontal interval immediately following the readout portion even if the electronic shutter speed is set to 1/60s (SMD = 00). This mode is closely related to 1/60s (SMD = 00). This regarding the control.

#### D51 PSMT

- 0: Driving is controlled in accordance with monitoring drive mode under the assumption that vertical/horizontal sync signals are input.

- 1: Driving is controlled in accordance with recording drive mode under the assumption that vertical/horizontal sync signals are input.

See the timing charts for the vertical/horizontal sync signals in accordance with each mode.

Note that when switching from monitoring drive to recording drive mode, the pixels decimated thus far must be cleaned.

Concretely, this operation is supported by generating XSUB, but the CXD2452R facilitates this control by using D48 EXPOSE. (See the figure.)

Image of switching from monitoring drive mode to recording drive mode

#### D52 SSGSEL

- 0: Internal SSG functions are stopped.

- 1: Internal SSG functions operate, and FRO and HRO are generated.

When generation is stopped, these pulses are fixed low.

## D53 WENSEL

- 0: WEN is generated.

- 1: WEN generation is stopped.

When generation is stopped, operation is the same as for D52 SSGSEL.

SONY CXD2452R

#### D54 CLPSEL

0: XCPOB generation is stopped.

1: XCPOB is generated.

When generation is stopped, operation is the same as for D52 SSGSEL.

#### D55 IDSEL

0: ID generation is stopped.

1: ID is generated.

When generation is stopped, operation is the same as for D52 SSGSEL.

#### D56 HMCKSEL

0: 1/2MCK generation is stopped.

1: 1/2MCK is generated.

When generation is stopped, operation is the same as for D52 SSGSEL.

# D57 TMCKSEL

0: 3/2MCK is generated.

1: 3/2MCK generation is stopped.

When generation is stopped, operation is the same as for D52 SSGSEL.

#### D58 HMCKREV

0: 1/2MCK reset when positive polarity.

1: 1/2MCK reset when negative polarity.

#### D59 HMCKREV

0: 3/2MCK reset when negative polarity.

1: 3/2MCK reset when positive polarity.

#### |D60 to |D61 |DSG

The CXD2452R can stop control to the CCD pulses and pulses for the sample-and-hold and analog/digital conversion ICs by setting the DSGAT pin low. Conversely, when the DSGAT pin is set high, the controlled pulses can be switched as follows using the serial interface data.

| D61 | D60 | Operating mode                                                               |

|-----|-----|------------------------------------------------------------------------------|

| 0   | 0   | No control performed                                                         |

| 0   | 1   | CCD pulse control                                                            |

| 1   | 0   | Sample-and-hold and analog/digital conversion IC pulse control               |

| 1   | 1   | CCD pulse and sample-and-hold and analog/digital conversion IC pulse control |

Here, CCD pulses refer to the H1, H2, RG, XV1, XV2, XV3, XSUB, XSG1 and XSG2 pulses. Sample-and-hold and analog/digital conversion IC pulses refer to the XSHP, XSHD, XRS, PBLK, XCLPOB, XCLPDM and CLD pulses.

See 7) Output timing characteristics using DSGAT of "AC Characteristics" for the stop control status of each pulse.

SONY

# D62 to D63 STB

This switches the operating mode as shown below. However, the IC pin status control bit is loaded to the CXD2452R and controlled immediately at the rise of the SEN input.

| D63 | D62 | Symbol | Operating mode        |

|-----|-----|--------|-----------------------|

| X   | 0   | CAMERA | Normal operation mode |

| 0   | 1   | SLEEP  | Sleep mode*1          |

| 1   | 1   | STNBY  | Standby mode          |

<sup>\*1</sup> Mode for the status which does not require CCD drive when playing back recorded data within the system.

The pin status during each mode is shown in the table below.

| Pin | Symbol            | CAMERA  | SLEEP | STNBY | Pin | Symbol | CAMERA | SLEEP | STNBY |

|-----|-------------------|---------|-------|-------|-----|--------|--------|-------|-------|

| 1   | змск              | ACT     | ACT   | ACT   | 25  | RST    | ACT    | ACT   | ACT   |

| 2   | Vss1              |         |       |       | 26  | VDD6   | _      |       |       |

| 3   | WEN               | ACT L L |       |       | 27  | SSI    | ACT    | ACT   | ACT   |

| 4   | ID                | ACT     | L     | L     | 28  | SSK    | ACT    | ACT   | ACT   |

| 5   | TEST              |         | _     |       | 29  | SEN    | ACT    | ACT   | ACT   |

| 6   | VDD1              |         | _     |       | 30  | EBCKSM | ACT    | ACT   | ACT   |

| 7   | XCLPOB            | ACT     | L     | L     | 31  | FRO    | ACT    | ACT   | L     |

| 8   | V <sub>DD</sub> 2 |         | _     |       | 32  | HRO    | ACT    | ACT   | L     |

| 9   | RG                | ACT     | L     | L     | 33  | HRI    | ACT    | ACT   | ACT   |

| 10  | Vss2              | _       |       |       |     | FRI    | ACT    | ACT   | ACT   |

| 11  | Vss3              |         | _     |       | 35  | CLD    | ACT    | L     | L     |

| 12  | H1                | ACT L L |       |       | 36  | Vss5   | _      |       |       |

| 13  | H2                | ACT     | L     | L     | 37  | DSGAT  | ACT    | ACT   | ACT   |

| 14  | VDD3              |         | _     |       | 38  | MCK    | ACT    | ACT   | L     |

| 15  | XCLPDM            | ACT L L |       |       | 39  | Vss6   | _      |       |       |

| 16  | VDD4              | _       |       |       | 40  | XSUB   | ACT    | L     | L     |

| 17  | XSHP              | ACT     | L     | L     | 41  | XV3    | ACT    | L     | L     |

| 18  | XSHD              | ACT     | L     | L     | 42  | XSG2   | ACT    | L     | L     |

| 19  | XRS               | ACT L L |       |       | 43  | XSG1   | ACT    | L     | L     |

| 20  | Vss4              | _       |       |       |     | XV2    | ACT    | L     | L     |

| 21  | PBLK              | ACT L L |       |       | 45  | VDD7   | _      |       |       |

| 22  | 1/2MCK            | ACT     | L     | L     | 46  | XV1    | ACT    | L     | L     |

| 23  | 3/2MCK            | ACT     | ACT   | L     | 47  | osco   | ACT    | ACT   | ACT   |

| 24  | VDD5              |         |       |       |     | OSCI   | ACT    | ACT   | ACT   |

Note) ACT means that the circuit is operating. L indicates a low output level in the controlled status.

# D64 to D71 CHKSUM

This is the check sum bit. Apply the data shown below.

|    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | → Reflected when the total is 0. |

|----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------------|

| +) | D71 | D70 | D69 | D68 | D67 | D66 | D65 | D64 | $_{\_}$ $ ightarrow$ CHKSUM      |

|    | D63 | D62 | D61 | D60 | D59 | D58 | D57 | D56 |                                  |

|    | D55 | D54 | D53 | D52 | D51 | D50 | D49 | D48 |                                  |

|    | D47 | D46 | D45 | D44 | D43 | D42 | D41 | D40 |                                  |

|    | D39 | D38 | D37 | D36 | D35 | D34 | D33 | D32 |                                  |

|    | D31 | D30 | D29 | D28 | D27 | D26 | D25 | D24 |                                  |

|    | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |                                  |

|    | D15 | D14 | D13 | D12 | D11 | D10 | D09 | D08 |                                  |

|    | D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 |                                  |

|    | MSB |     |     |     |     |     |     | LSB |                                  |

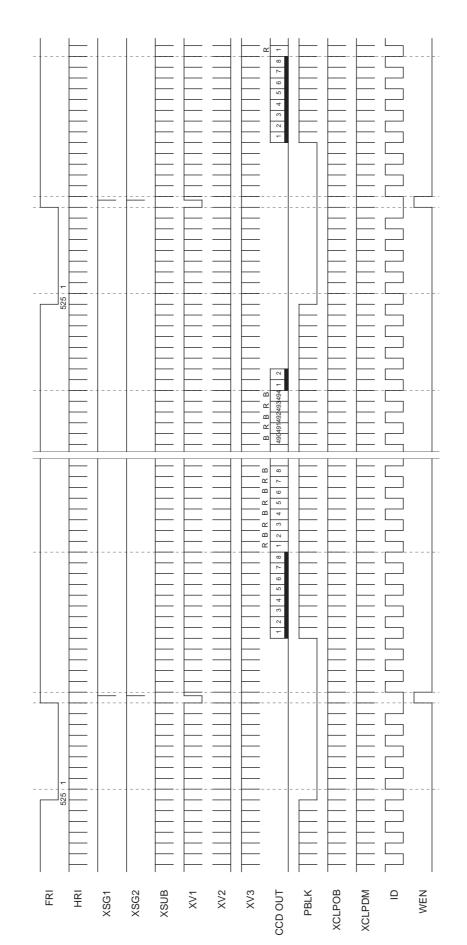

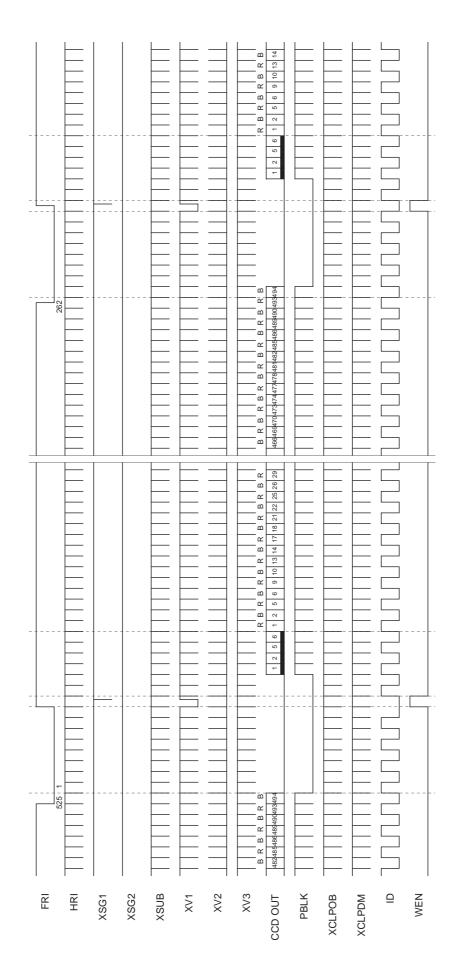

\* In addition to the phase relationship between FRI and HRI shown above, the phases may also be offset by 1/2 horizontal interval. In any case, the readout interval is the 9th HRI fall counted \* The number of XSUB pulses is determined by the serial interface data. This chart shows the case where Shut.HD = 20Ch and XSUB pulses are generated over the entire horizontal interval.

from the fall of FRI. \*Note that R and B of CCDOUT indicate lines containing these components, and do not mean the lead pixel component of that line.

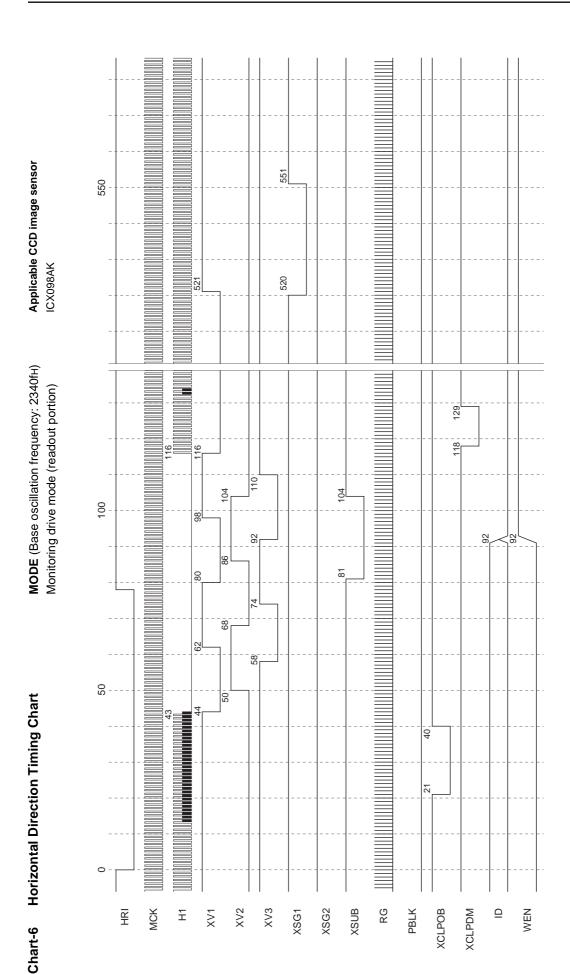

Monitoring drive mode

Applicable CCD image sensor ICX098AK

\* The number of XSUB pulses is determined by the serial interface data. This chart shows the case where Shut. HD = 20Ch and XSUB pulses are generated over the entire horizontal interval.

\* Note that R and B of CCDOUT indicate lines containing these component, and do not mean the lead pixel component of that line.

\* The HRI of this chart is equivalent to HRI' of Chart-7. This HRI indicates a timing that the CXD2452R takes in actually.

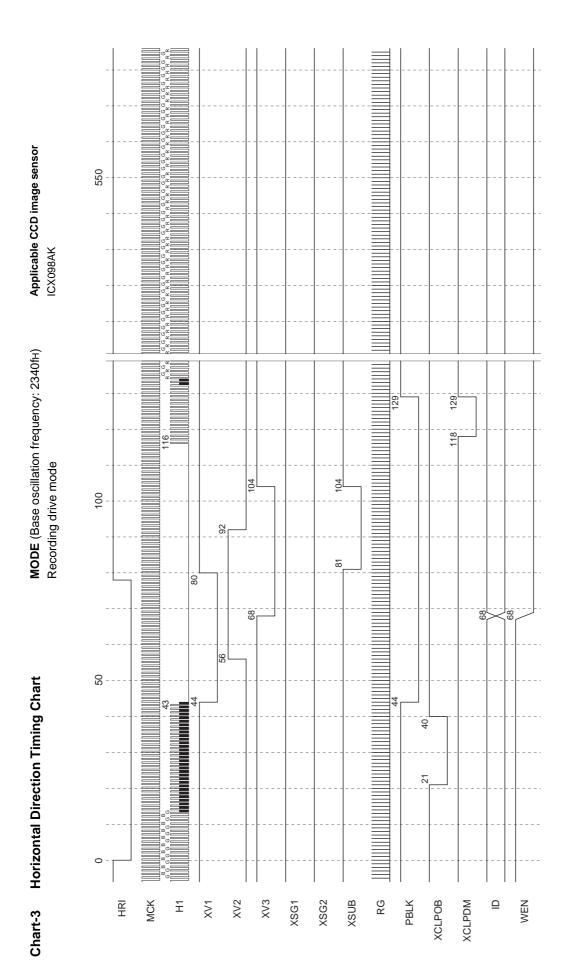

The numbers at the output pulse transition points indicate the count at the MCK (780fH) rise from the fall of HRI.

$<sup>^*</sup>$  The HRI fall interval should be between 3.6 to 9.4 $\mu s$ . This chart shows an interval of 78ck (6.3 $\mu s$ ).

<sup>\*</sup> XSUB is output at the timing shown above when specified by the serial interface data.

\* The ID transition timing is synchronized with the fall of XV3.

<sup>\*</sup> WEN is output during the horizontal interval shown in Chart-1. The transition timing is the same as that for ID.

R, G and B of H1 indicate the output pixel color. In addition to the lines starting from R and G shown above, there are also lines starting from G and B.

The HRI of this chart is equivalent to HRI' of Chart-7. This HRI indicates a timing that the CXD2452R takes in actually.

<sup>\*</sup> The numbers at the output pulse transition points indicate the count at the MCK (780fH) rise from the fall of HRI.

$<sup>^*</sup>$  The HRI fall interval should be between 3.6 to 9.4 $\mu$ s. This chart shows an interval of 78ck (6.3 $\mu$ s).  $^*$  XSUB is output at the timing shown above when specified by the serial interface data.

<sup>\*</sup> The ID transition timing is synchronized with the fall of XV3. ID is reset low at this timing during the readout horizontal interval.

<sup>\*</sup> WEN is output during the horizontal interval shown in Chart-1. The transition timing is the same as that for ID.

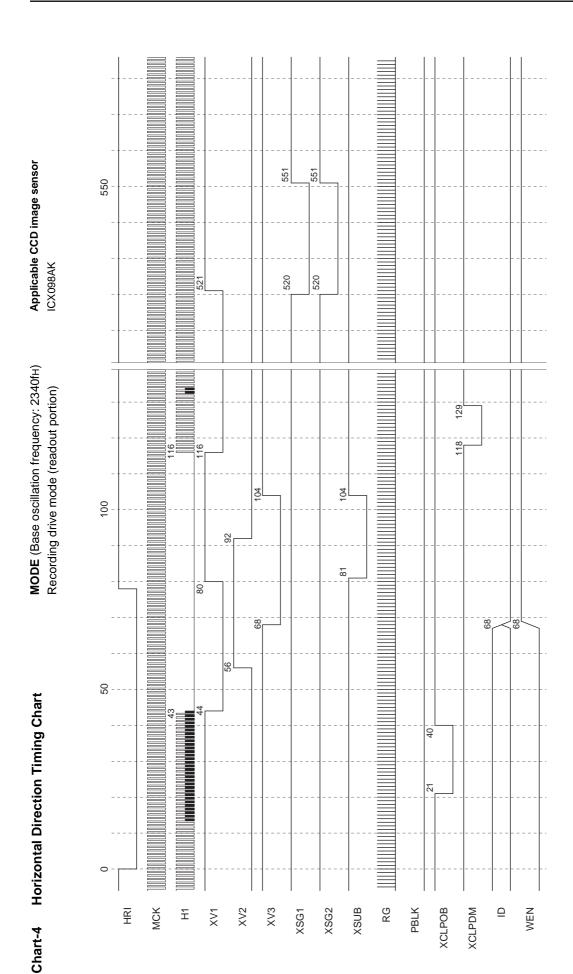

\*The HRI of this chart is equivalent to HRI' of Chart-7. This HRI indicates a timing that the CXD2452R takes in actually.

<sup>\*</sup> The numbers at the output pulse transition points indicate the count at the MCK (780fH) rise from the fall of HRI.

The HRI fall interval should be between 3.6 to 9.4 µs. This chart shows an interval of 78ck (6.3 µs).

XSUB is output at the timing shown above when specified by the serial interface data.

<sup>&</sup>lt;sup>†</sup> The ID transition timing is synchronized with the fall of XV3.

<sup>\*</sup> WEN is output during the horizontal interval shown in Chart-2. The transition timing is the same as that for ID.

R, G and B of H1 indicate the output pixel color. In addition to the lines starting from R and G shown above, there are also lines starting from G and B.

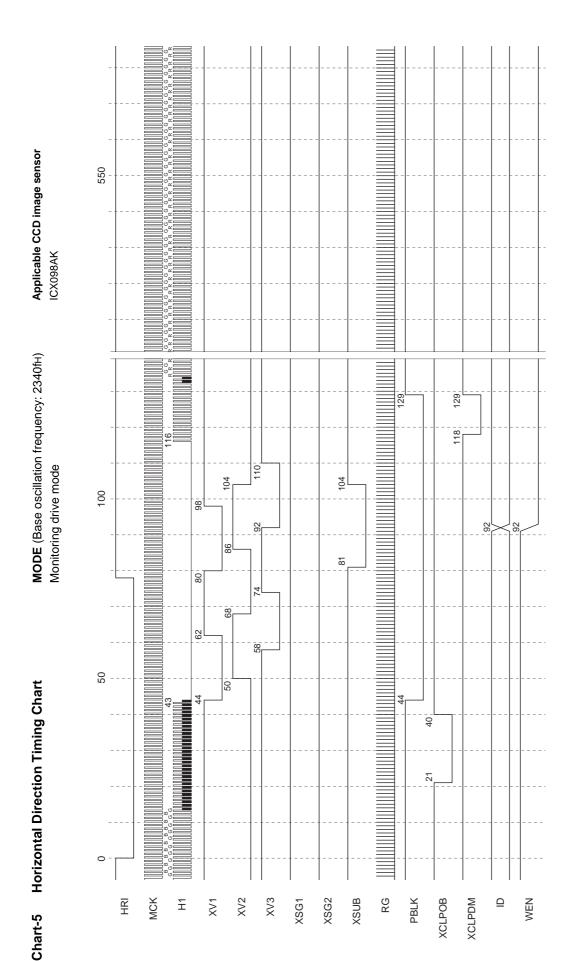

\* The HRI of this chart is equivalent to HRI' of Chart-7. This HRI indicates a timing that the CXD2452R takes in actually.

<sup>\*</sup> The numbers at the output pulse transition points indicate the count at the MCK (780fH) rise from the fall of HRI.

<sup>\*</sup> The HRI fall interval should be between 3.6 to 9.4µs. This chart shows an interval of 78ck (6.3µs). \* YSTIB is outsuit at the timing should should should should be the social interface data.

<sup>\*</sup> XSUB is output at the timing shown above when specified by the serial interface data.

<sup>\*</sup> The ID transition timing is synchronized with the fall of XV3. ID is reset low at this timing during the readout horizontal interval. \* WEN is output during the horizontal interval shown in Chart-2. The transition timing is the same as that for ID.

Applicable CCD image sensor

MODE (Base oscillation frequency: 2340fH)

ICX098AK

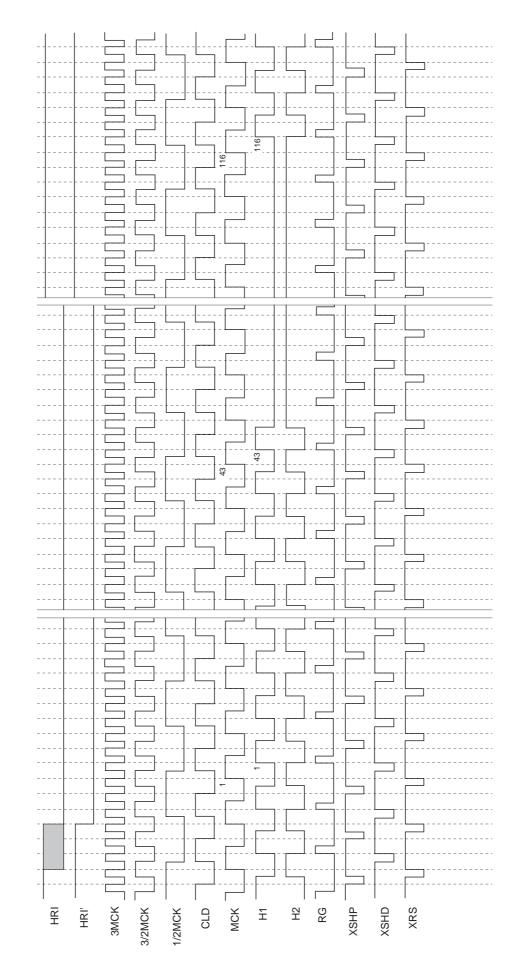

Chart-7

\* The phase relationship of each pulse indicates logical position. For actual output waveform, delay is added respectively.

<sup>\*</sup> HRI' indicates the HRI, which is a timing that taken in actually.

<sup>\* 3/2</sup>MCK and 1/2MCK can inverse polarity according to each serial interface data. This chart indicates that 3/2 MCK is negative polarity; 1/2 MCK is positive polarity.

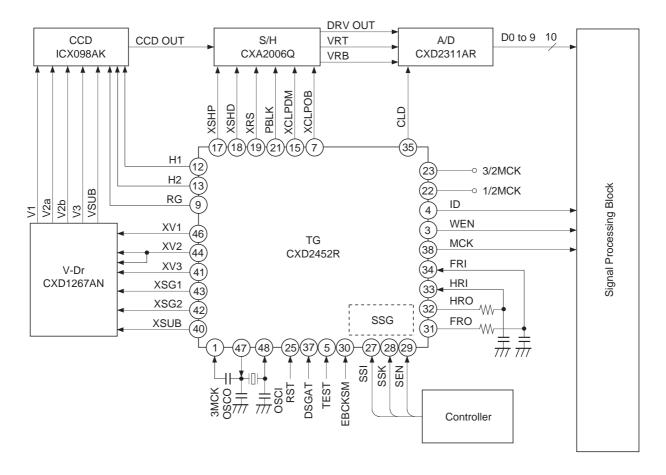

#### **Application Circuit Block Diagram**

Note) When the CXD2311AR is used as A/D converter, CLD must be inversed.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

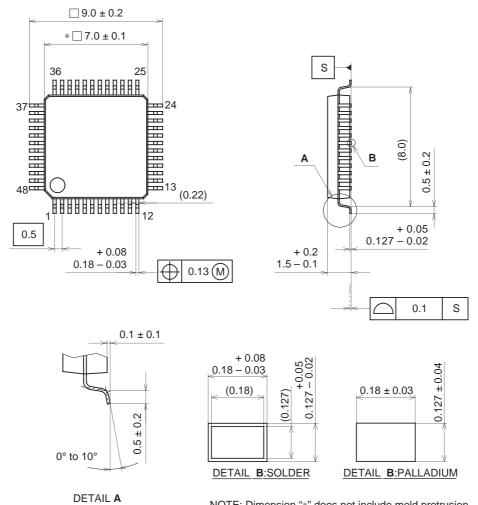

#### **Package Outline**

Unit: mm

# 48PIN LQFP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

#### PACKAGE STRUCTURE

| SONY CODE  | LQFP-48P-L01   |

|------------|----------------|

| EIAJ CODE  | LQFP048-P-0707 |

| JEDEC CODE |                |

| PACKAGE MATERIAL | EPOXY RESIN                 |

|------------------|-----------------------------|

| LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |

| LEAD MATERIAL    | 42/COPPER ALLOY             |

| PACKAGE MASS     | 0.2g                        |