**CXD3503R**

# Color Shading Correction IC for Liquid Crystal Projectors

#### Description

The CXD3503R is a color shading correction IC for Sony data projectors. Used together with the Sony LCD driver CXA2111R or CXA2112R, this IC corrects color shading caused by the LCD panel structure or the optical system. This IC has a built-in SRAM and D/A converter, and 16 horizontal and 13 vertical correction points can be set via a serial interface.

#### **Functions**

- Generates the color shading correction signals for the high-temperature polysilicon TFT LCD panels used in Sony projectors

- Supports various SVGA, XGA and SXGA signals using 1/2 dot clock input

- Vertical output signal interpolation using an internal arithmetic circuit

- Automatic determination of eliminated lines during pulse eliminator display when used together with the Sony timing generator ICs CXD2464R or CXD3500R

- Supports up/down and/or right/left inversion

- Supports LCD panel display area switching conversion functions

- Standby and correction OFF functions

#### Applications

Liquid crystal projectors, etc.

#### Structure

Silicon gate CMOS IC

#### Absolute Maximum Ratings (Vss = 0V)

| <ul> <li>Supply voltage</li> </ul>        | Vdd     | Vss – 0.3 to +7.0      | V  |

|-------------------------------------------|---------|------------------------|----|

| <ul> <li>Input voltage</li> </ul>         | Vı      | Vss - 0.3 to Vpp + 0.3 | V  |

| <ul> <li>Output voltage</li> </ul>        | Vo      | Vss - 0.3 to Vpp + 0.3 | V  |

| Storage temperative                       | ature   |                        |    |

|                                           | Tstg    | -55 to +125            | °C |

| <ul> <li>Operating temperating</li> </ul> | erature | )                      |    |

|                                           | Topr    | -40 to +85             | °C |

#### **Recommended Operating Conditions**

$(Ta = -20 \text{ to } +75^{\circ}\text{C}, \text{ Vss} = 0\text{V})$

Supply voltage VDD 4.5 to 5.5

**Note)** Company names and product names, etc. contained in these materials are trademarks or registered trademarks of the respective companies.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

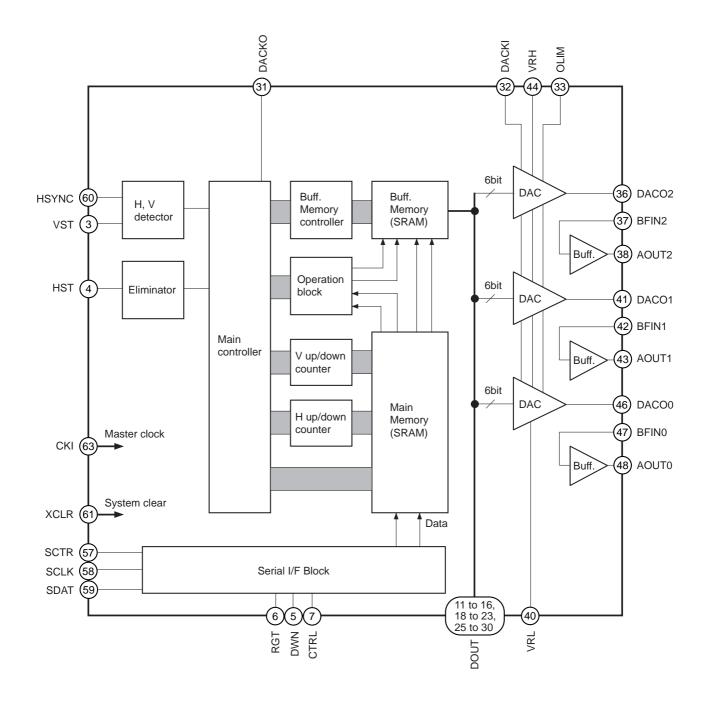

#### **Block Diagram**

#### **Pin Description**

| Pin<br>No. | Symbol | I/O | Description                                                                           | Processing for internal input |

|------------|--------|-----|---------------------------------------------------------------------------------------|-------------------------------|

| 1          | NC     | —   | Not connected                                                                         | —                             |

| 2          | NC     | —   | Not connected                                                                         | —                             |

| 3          | VST    | Ι   | VST pulse input                                                                       | —                             |

| 4          | HST    | I   | HST pulse input                                                                       | —                             |

| 5          | DWN    | Ι   | Up/down inversion control input (H: down scan, L: up scan)                            | —                             |

| 6          | RGT    | Ι   | Right/left inversion control input (H: normal scan, L: reverse scan)                  | —                             |

| 7          | CTRL   | Ι   | Up/down and/or right/left inversion control signal (Serial settings selected when L.) | —                             |

| 8          | TEST0  | Ι   | Test (Leave open.)                                                                    | L                             |

| 9          | TEST1  | Ι   | Test (Leave open.)                                                                    | L                             |

| 10         | TEST2  | Ι   | Test (Leave open.)                                                                    | L                             |

| 11         | DOUT00 | 0   | Digital data output 00                                                                | _                             |

| 12         | DOUT01 | 0   | Digital data output 01                                                                | _                             |

| 13         | DOUT02 | 0   | Digital data output 02                                                                | _                             |

| 14         | DOUT03 | 0   | Digital data output 03                                                                | _                             |

| 15         | DOUT04 | 0   | Digital data output 04                                                                | _                             |

| 16         | DOUT05 | 0   | Digital data output 05                                                                | _                             |

| 17         | DVss0  | —   | Digital GND                                                                           | _                             |

| 18         | DOUT10 | 0   | Digital data output 10                                                                | _                             |

| 19         | DOUT11 | 0   | Digital data output 11                                                                | _                             |

| 20         | DOUT12 | 0   | Digital data output 12                                                                | _                             |

| 21         | DOUT13 | 0   | Digital data output 13                                                                | _                             |

| 22         | DOUT14 | 0   | Digital data output 14                                                                | _                             |

| 23         | DOUT15 | 0   | Digital data output 15                                                                | _                             |

| 24         | DVdd0  | —   | Digital VDD (5V)                                                                      | _                             |

| 25         | DOUT20 | 0   | Digital data output 20                                                                | _                             |

| 26         | DOUT21 | 0   | Digital data output 21                                                                | _                             |

| 27         | DOUT22 | 0   | Digital data output 22                                                                | _                             |

| 28         | DOUT23 | 0   | Digital data output 23                                                                | _                             |

| 29         | DOUT24 | 0   | Digital data output 24                                                                | _                             |

| 30         | DOUT25 | 0   | Digital data output 25                                                                | _                             |

| 31         | DACKO  | 0   | DAC clock output (Connect to DACKI.)                                                  | _                             |

| 32         | DACKI  | Ι   | DAC clock input (Connect to DACKO.)                                                   | —                             |

| 33         | OLIM   | Ι   | Digital data output limiter (H: Hi-Z, L: digital data output)                         | —                             |

| 34         | DVpd1  | _   | Digital VDD (5V)                                                                      | _                             |

| Pin<br>No. | Symbol | I/O | Description                                               | Processing for internal input |

|------------|--------|-----|-----------------------------------------------------------|-------------------------------|

| 35         | DVss1  | —   | Digital GND                                               | _                             |

| 36         | DACO2  | 0   | DAC output 2                                              | _                             |

| 37         | BFIN2  | I   | Buffer input 2                                            | _                             |

| 38         | AOUT2  | 0   | Correction signal output 2                                | _                             |

| 39         | AVss   | —   | Analog GND                                                | _                             |

| 40         | VRL    | I   | DAC output low reference voltage input                    | _                             |

| 41         | DACO1  | 0   | DAC output 1                                              | _                             |

| 42         | BFIN1  | I   | Buffer input 1                                            | _                             |

| 43         | AOUT1  | 0   | Correction signal output 1                                | _                             |

| 44         | VRH    | I   | DAC output high reference voltage input                   | _                             |

| 45         | AVdd   | —   | Analog power supply                                       | _                             |

| 46         | DACO0  | 0   | DAC output 0                                              | _                             |

| 47         | BFIN0  | I   | Buffer input 0                                            | _                             |

| 48         | AOUT0  | 0   | Correction signal output 0                                | _                             |

| 49         | DVss2  | —   | Digital GND                                               | _                             |

| 50         | NC     | —   | Not connected                                             | _                             |

| 51         | NC     | —   | Not connected                                             | _                             |

| 52         | NC     | —   | Not connected                                             | _                             |

| 53         | NC     | —   | Not connected                                             | _                             |

| 54         | NC     | —   | Not connected                                             | _                             |

| 55         | NC     | —   | Not connected                                             | _                             |

| 56         | DVdd2  | —   | Digital Vod (5V)                                          | _                             |

| 57         | SCTR   | I   | Serial chip select input (serial transfer block)          | _                             |

| 58         | SCLK   | I   | Serial clock input (serial transfer block)                | _                             |

| 59         | SDAT   | I   | Serial data input (serial transfer block)                 | _                             |

| 60         | HSYNC  | Ι   | HSYNC input                                               |                               |

| 61         | XCLR   | I   | Clear (L: system clear)                                   | Н                             |

| 62         | DVss3  | —   | Digital GND                                               |                               |

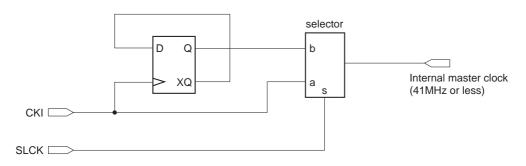

| 63         | СКІ    | I   | Master clock input                                        |                               |

| 64         | SLCK   | I   | Clock switching (H: Internal 1/2 frequency divider used.) | _                             |

#### **Electrical Characteristics**

#### **DC Characteristics**

#### $(V_{DD} = 5.0 \pm 0.5V, V_{SS} = 0V, T_{OPT} = -40 \text{ to } +85^{\circ}C)$

| Item                   | Symbol | Conditions                   | Min.      | Тур. | Max.   | Unit | Applicable pins |  |

|------------------------|--------|------------------------------|-----------|------|--------|------|-----------------|--|

| Supply voltage         | Vdd    |                              | 4.5       | 5.0  | 5.5    | V    |                 |  |

| Input, output voltage  | Vı, Vo |                              | Vss       |      | Vdd    | V    |                 |  |

| lanut volto do 1       | Vih    |                              | 0.7Vdd    |      |        | V    | . the d         |  |

| Input voltage 1        | Vil    | CMOS input                   |           |      | 0.3Vdd |      | *1              |  |

| Input voltage 2        | Vih    | CMOS input                   | 0.7Vdd    |      |        | V    | *4              |  |

| Input voltage 2        | Vil    | With pull-up resistor        |           |      | 0.3Vdd |      | *4              |  |

| Innut volto do 2       | Vih    | CMOS input                   | 0.7Vdd    |      |        | V    | *2              |  |

| Input voltage 3        | Vil    | With pull-down resistor      |           |      | 0.3Vdd |      |                 |  |

| lanut volto so 4       | Vih    | TTL input                    | 2.2       |      |        |      | *5              |  |

| Input voltage 4        | Vil    |                              |           |      | 0.8    | V    |                 |  |

|                        | Vih    | TTL Schmitt input            | 2.5       |      |        | V    | . the           |  |

| Input voltage 5        | Vil    |                              |           |      | 0.6    |      | *3              |  |

| Output voltage 1       | Vон    | Іон = —4mA                   | Vdd - 2.1 |      |        | V    |                 |  |

| Output voltage 1       | Vol    | lo∟ = 4mA                    |           |      | 0.4    |      | *6, *7          |  |

| Input leak current     | lı∟    | VI = VDD, VSS                | -10       |      | 10     | μA   | *1, *3, *5      |  |

| Output leak<br>current | loz    | During high impedance output | -10       |      | 10     | μA   | *7              |  |

| Pull-up resistor       | Rup    |                              | 60        | 120  | 240    | kΩ   | *4              |  |

| Pull-down resistor     | Rdn    |                              | 45        | 90   | 180    | kΩ   | *2              |  |

| Current consumption    | ldd    | During 41MHz operation       |           | 60   |        | mA   |                 |  |

#### (INPUT)

- \*1 CTRL, DACKI, DWN, HST, OLIM, RGT, SLCK, VST

- \*2 TEST0, 1, 2

- \*3 HSYNC, SCLK, SCTR, SDAT

- \*4 XCLR

- \*5 CKI

# (OUTPUT)

\*6 DACKO

\*7 DOUT00 to 05, DOUT10 to 15, DOUT20 to 25

Note) AOUT0, 1 and 2, DACO0, 1 and 2, BFIN0, 1 and 2, VRH and VRL are not included in the DC characteristics.

CXD3503R

#### **AC Characteristics**

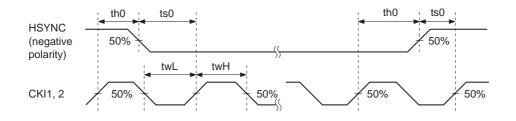

#### **External Clock Input AC Characteristics**

$(V_{DD} = 5.0 \pm 0.5V, V_{SS} = 0V, T_{OPT} = -40 \text{ to } +85^{\circ}C)$

| Symbol  | Item                                                  | Min. | Тур. | Max. | Unit |

|---------|-------------------------------------------------------|------|------|------|------|

| ts0     | HSYNC setup time, activated by the rising edge of CKI | 12   | _    | _    | 200  |

| th0     | HSYNC hold time, activated by the rising edge of CKI  | 0.5  | _    | _    | ns   |

| twL/twH | CKI L/H level pulse width                             | _    | 50   | _    | %    |

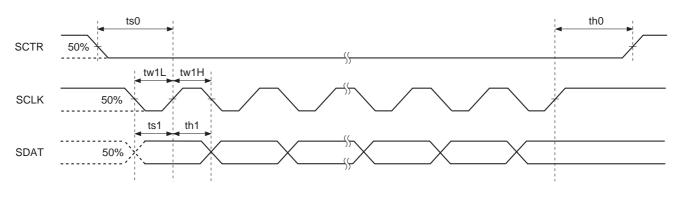

#### **Serial Transfer AC Characteristics**

$(V_{DD} = 5.0 \pm 0.5V, V_{SS} = 0V, T_{OPT} = -40 \text{ to } +85^{\circ}C)$

| Symbol | Item                                                  | Min. | Тур. | Max. |

|--------|-------------------------------------------------------|------|------|------|

| ts0    | SCTR setup time, activated by the rising edge of SCLK | 8Tns | _    | —    |

| ts1    | SDAT setup time, activated by the rising edge of SCLK | 4Tns | _    | —    |

| th0    | SCTR hold time, activated by the rising edge of SCLK  | 8Tns | _    | —    |

| th1    | SDAT hold time, activated by the rising edge of SCLK  | 4Tns | _    | —    |

| tw1L   | SCLK L level pulse width                              | 4Tns | —    | —    |

| tw1H   | SCLK H level pulse width                              | 4Tns | _    | —    |

T: Input clock cycle

#### **Timing Definition**

#### **External Clock Input AC Characteristics**

### **Serial Transfer AC Characteristics**

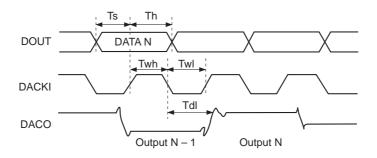

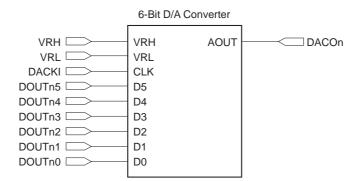

#### 6-bit D/A Converter part

**Electrical Characteristics (Analog Block)**

#### (Ta = 25°C, VDD = 5.0V, Vss = 0V, VRH – VRL = 1.0V)

| Item                         | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------|--------|------|------|------|------|

| Resolution                   | RES    |      | —    | 6    | Bits |

| Conversion rate              | Fs     |      | —    | 30   | MPS  |

| Linearity error              | EL     |      | —    | ±0.5 | LSB  |

| Differential linearity error | ED     |      |      | ±0.5 | LSB  |

| Output resistance            | Ro     | 140  | 213  | 286  | Ω    |

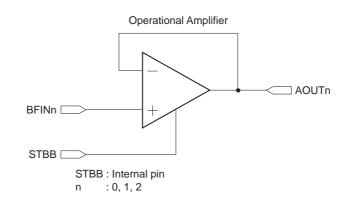

## **Operational Amplifier part (Operating Temperature variation)**

(VDD = 5.0V, Vss = 0V)

| Item                              | Symbol | Min.       | Тур.       | Max.       | Unit |

|-----------------------------------|--------|------------|------------|------------|------|

| Operating temperature             | Та     | -40        | 25         | 85         | °C   |

| Input offset voltage              | Vio    | 5          | 5          | 5          | mV   |

| Current consumption               | Icc    | 2.4        | 1.8        | 1.6        | mA   |

| Maximum output saturation voltage | Vopp   | 0 to 4.95  | 0 to 4.95  | 0 to 4.95  | V    |

| Input voltage range               | Vin    | 1.5 to 5.0 | 1.7 to 5.0 | 1.8 to 5.0 | V    |

| Slew rate                         | SR     | 39         | 31         | 28         | V/µs |

# **Operational Amplifier part (Supply Voltage variation)**

(Ta = 25°C, Vss = 0V)

| Item                              | Symbol | Min.       | Тур.       | Max.       | Unit |

|-----------------------------------|--------|------------|------------|------------|------|

| Operating voltage                 | Vio    | 4.5        | 5.0        | 5.5        | V    |

| Input offset voltage              | Vio    | 5          | 5          | 5          | mV   |

| Current consumption               | lcc    | 1.4        | 1.8        | 2.4        | mA   |

| Maximum output saturation voltage | Vopp   | 0 to 4.45  | 0 to 4.95  | 0 to 5.43  | V    |

| Input voltage range               | VIN    | 1.7 to 4.5 | 1.7 to 5.0 | 1.9 to 5.5 | V    |

| Slew rate                         | SR     | 24         | 31         | 40         | V/µs |

#### **AC Characteristics**

#### **External Clock Input AC Characteristics**

#### 6-Bit D/A Converter

(Ta = 25°C, VDD = 5.0V, Vss = 0V, VRH - VRL = 1.0V, CL = 30pF)

| Item                | Symbol | Min. | Тур. | Max. | Unit |

|---------------------|--------|------|------|------|------|

| Clock H level width | Twh    | 17   | _    |      |      |

| Clock L level width | Twl    | 17   |      | _    |      |

| Data setup time     | Ts     | 10   |      | _    | ns   |

| Data hold time      | Th     | 10   |      | _    |      |

| Output delay time   | Tdl    | _    | 35   | _    | 1    |

#### **Timing Definition**

#### **Internal Structure**

# I/O Pin Description

| Pin No.                            | Symbol              | Description                                                                                                                                                                                                                                                            |  |  |

|------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3                                  | VST                 | This pin is a reference of vertical output timing.<br>Inputs the VST pulse from the timing generator IC.                                                                                                                                                               |  |  |

| 4                                  | HST                 | Inputs the HST pulse from the timing generator IC.<br>When not rising pulse eliminator, connect to DVpp and use it.                                                                                                                                                    |  |  |

| 5                                  | DWN                 | Up/down and/or right/left inversion control external input                                                                                                                                                                                                             |  |  |

| 6                                  | RGT                 | (H: normal scan, L: reverse scan)<br>This setting is invalid when the internal register is used.                                                                                                                                                                       |  |  |

| 7                                  | CTRL                | Up/down and/or right/left inversion control signal selection setting.<br>(For the DWN and RGT control signals, Pins 5 and 6 are selected when CTRL<br>is H, and the settings from the internal register made via the serial interface are<br>selected when CTRL is L.) |  |  |

| 11 to 16,<br>18 to 23,<br>25 to 30 | DOUT00<br>to DOUT25 | Digital data outputs. The data input to the DAC is output as is when OLIM (Pin 33) is L. Normally, output is not performed. Set OLIM to H and leave these open.                                                                                                        |  |  |

| 31                                 | DACKO               | Internal DAC clock input/output. DAC clock generated inside the IC is output                                                                                                                                                                                           |  |  |

| 32                                 | DACKI               | from DACKO. Normally, input this DACKO output to DACKI.                                                                                                                                                                                                                |  |  |

| 33                                 | OLIM                | Digital data output limiter. When OLIM is L, the data input to the DAC is output from the DOUT00 to DOUT25 output pins. When OLIM is H, these output pins go to high impedance state.                                                                                  |  |  |

| 36, 41, 46                         | DACO2, 1, 0         | Analog outputs from the internal DAC. The output impedance varies from several ten to several thousand $\Omega$ depending on the output voltage level, so connect these pins to BFIN2, 1 and 0 (buffer inputs), respectively.                                          |  |  |

| 37, 42, 47                         | BFIN2, 1, 0         | Internal operational amplifier buffer inputs. Connect to DACO2, 1 and 0, respectively.                                                                                                                                                                                 |  |  |

| 38, 43, 48                         | AOUT2, 1, 0         | Analog correction signal outputs                                                                                                                                                                                                                                       |  |  |

| 40                                 | VRL                 | DAC L side reference voltage input (Input via buffer.)                                                                                                                                                                                                                 |  |  |

| 44                                 | VRH                 | DAC H side reference voltage input (Input via buffer.)                                                                                                                                                                                                                 |  |  |

| 57                                 | SCTR                |                                                                                                                                                                                                                                                                        |  |  |

| 58                                 | SCLK                | Serial control inputs. Timing control and correction point data are all set by these pins. For details, see page 12 "Serial Transfer Operation".                                                                                                                       |  |  |

| 59                                 | SDAT                |                                                                                                                                                                                                                                                                        |  |  |

| 60                                 | HSYNC               | This pin is a reference of horizontal output timing. Normally, input horizontal sync signal.                                                                                                                                                                           |  |  |

| 61                                 | XCLR                | System clear. Internal register is initialized by setting to L. Input pins are pulled up to H internally.                                                                                                                                                              |  |  |

| 63                                 | СКІ                 | Master clock input. Input level is TTL.                                                                                                                                                                                                                                |  |  |

| 64                                 | SLCK                | Clock switching (H: Clock obtained by 1/2 frequency-dividing CKI using the internal frequency divider is selected. L: CKI input is selected. The selected clock is an internal master clock.)                                                                          |  |  |

| 17, 35, 49, 62                     | DVss                |                                                                                                                                                                                                                                                                        |  |  |

| 24, 34, 56                         | DVdd                | Power supply inputs. Do not raise either analog power supply or digital power                                                                                                                                                                                          |  |  |

| 39                                 | AVss                | supply.                                                                                                                                                                                                                                                                |  |  |

| 45                                 | AVdd                |                                                                                                                                                                                                                                                                        |  |  |

#### Clock input (CKI: Pin 63)

The master clock input (CKI: Pin 63) of this IC supports TTL level input.

In addition, two modes can be set: a mode in which the CKI is used as is for the internal master clock (SLCK (Pin 64): L) and a mode in which CKI is halved using the internal frequency divider (SLCK: H). In the latter mode, all internal operation is at 1/2 clock, so "clock" in the description below refers to this 1/2 clock when SLCK is H. Internal operation is at a frequency up to 41 MHz, so when inputting a clock faster than this to CKI1, be sure to set SLCK to H.

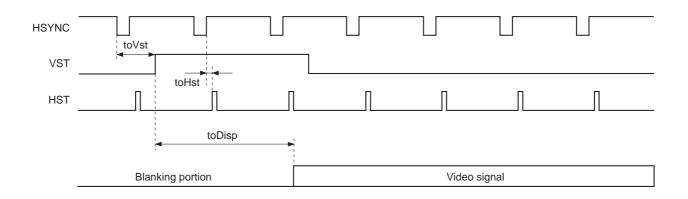

#### HSYNC, VST, HST

Input a standard horizontal sync signal to the input HSYNC (Pin 60).

At this time, the input polarity is not fixed and is set by the serial data setting HSYNCPOL. In addition, make sure the VST and HST pulses satisfy the following phase relationship. However, when not using pulse eliminator display, HST (Pin 4) can be fixed to H level.

Normally input the VST pulse to the LCD panel for the VST input.

toVst: VST shall rise 20 clocks or more after the front edge of HSYNC, and after the HST pulse.

toHst: The front edge of HST shall follow the rear edge of HSYNC

toDisp: There shall be 1.5H or more from the rise of VST to the start of the video signal.

The Sony timing generator ICs (CXD2464R, CXD3500R) pulses of the same name satisfy the above conditions.

#### System clear pin input

Set the system clear pin (XCLR: Pin 61) to L and apply a forced reset in order to initialize the internal circuits during power-on.

#### **Description of Output Correction Signal Operation**

#### **Horizontal direction**

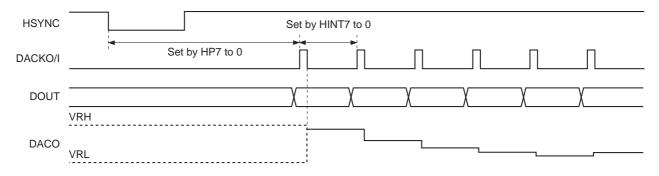

The correction data set in the SRAM by serial transfer is arithmetically processed inside the IC to determine the output position corresponding to the value set by serial register HP7 to 0 using the front edge of HSYNC as the reference. Interpolation is not performed for the horizontal direction, and interpolated data is output at the cycle set by serial register HINT7 to 0 for the vertical direction. In addition, the maximum amplitude of the correction signal output voltage is determined by VRH (Pin 44) and VRL (Pin 40). The internal DAC outputs at the resistive potential division (VRH to VRL:  $213\Omega$  typ.), so be sure to input to VRH and VRL via buffers having current capacity.

The internally generated digital data DOUT is input to the internal D/A converter, latched by the D/A converter clock input from DACKI, and output from DACO2, 1 and 0 as an analog signal.

**Note)** If edges remain, these level differences may appear as vertical stripes. Therefore, when using this as a correction signal, be sure to eliminate the edges using an LPF, etc. before input to the CXA2111R or CXA2112R.

#### Vertical direction

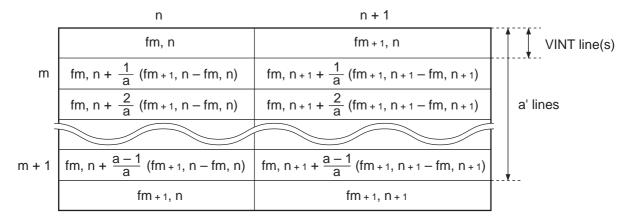

The vertical correction points set in the SRAM are arithmetically processed inside the IC to output interpolated data for the lines other than correction points.

fm, n: Correction data for point (m, n)

Vertical correction point interval Set by VINT4 to 0 and ANM5 to 0 Assuming ANM5 to 0 = a,  $a' = VINT \times a$

#### **Serial Transfer Operation**

#### **Control method**

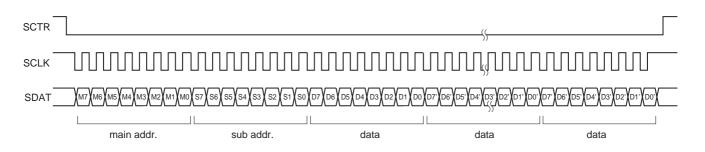

The operation timing of this IC is controlled by serial data.

The control data is divided into 8-bit units. The first 8 bits are the main address, the next 8 bits are the sub address, and the subsequent data is 8-bit data blocks.

The main address specifies which of the blocks in the table below are to be set. Data is set in the blocks indicated by "1", so if the main address is set to "0F", the subsequent data is set in all data blocks.

In addition, the value set in the sub address sets the initial write address in the block specified by the main address. Thereafter, the write address is incremented by +1 while SCTR is L for each 8 bits of data from the address set by the sub address.

This makes it possible to set only the necessary data from an optional address.

The data set by serial register INIT5 to 0 is output in place of the correction data during serial transfer.

#### Main address table

| Main address | Setting block                   |

|--------------|---------------------------------|

| 01h          | Correction point data 0 (SRAM0) |

| 02h          | Correction point data 1 (SRAM1) |

| 04h          | Correction point data 2 (SRAM2) |

| 08h          | Timing control data             |

The SRAM numbers 0, 1 and 2 correspond to the DAC output DACO numbers 0, 1 and 2. The correction point data set in the SRAM is reflected to the outputs of the corresponding numbers.

#### Correction point data 0, 1 and 2

Correction point data is set in the 6-bit  $\times$  208 words (16 horizontal points, 13 vertical points) SRAM. The set correction data undergoes vertical interpolation and other arithmetic processing, and is then reflected to the DACO0, 1 and 2 outputs, respectively. The correction point data is 6 bits, and is set in D5, 4, 3, 2, 1 and 0. Setting to D7 and 6 is invalid.

See the figure on page 13 for the relationship between the correction point data position and the SRAM address.

Example) When the main address is set to 04 and the sub address is set to 08, data is written from address 08 of correction point data 2 (SRAM2), then the address is automatically incremented and written to the SRAM.

#### **Timing control data**

#### Main address 08h

| Sub address | D7    | D6    | D5    | D4    | D3    | D2     | D1     | D0     |

|-------------|-------|-------|-------|-------|-------|--------|--------|--------|

| 00h         | HB3   | HB2   | HB1   | HB0   | HE3   | HE2    | HE1    | HE0    |

| 01h         | VB3   | VB2   | VB1   | VB0   | VE3   | VE2    | VE1    | VE0    |

| 02h         | HP7   | HP6   | HP5   | HP4   | HP3   | HP2    | HP1    | HP0    |

| 03h         | HINT7 | HINT6 | HINT5 | HINT4 | HINT3 | HINT2  | HINT1  | HINT0  |

| 04h         |       | _     | _     | _     | VP3   | VP2    | VP1    | VP0    |

| 05h         |       | _     | _     | VINT4 | VINT3 | VINT2  | VINT1  | VINT0  |

| 06h         |       | _     | ANM5  | ANM4  | ANM3  | ANM2   | ANM1   | ANM0   |

| 07h         |       | 1/A6  | 1/A5  | 1/A4  | 1/A3  | 1/A2   | 1/A1   | 1/A0   |

| 08h         | HSOFF | HPOL  | VSPOL | DWN   | RGT   | DACKP2 | DACKP1 | DACKP0 |

| 09h         | STBY1 | STBY0 | INIT5 | INIT4 | INIT3 | INIT2  | INIT1  | INIT0  |

-: Setting invalid

#### **Data settings**

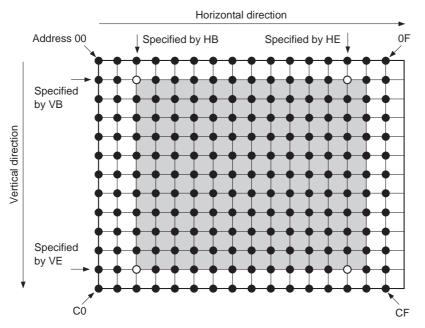

#### HB3 to 0, HE3 to 0, VB3 to 0, VE3 to 0

These set the range of the correction point data to be used.

Expressed in model format, the correction points appear as shown in the figure below. To use only the shaded area, set HB: 2, HE: D, VB: 1 and VE: B.

Normally set HB: 0, HE: F, VB: 0 and VE: D (16  $\times$  13).

Dots in the lattice above represent correction points, and the white circles are the data settings.

#### HP7 to 0

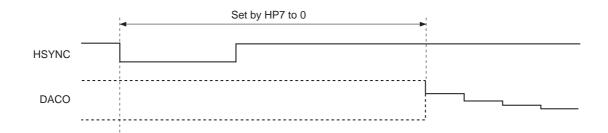

This sets the correction signal output start position in the horizontal direction. The timing until the start of correction signal output is set using the front edge of HSYNC as the reference. However, do not set HP7 to 0 to a value of 54 or less, as the arithmetically processed correction signal may not be output correctly in this case. In addition, the waveform may be disturbed by the HP and HINT values and the VST phase. In these cases, eliminate the disturbance by adjusting the HP and DACKO phase.

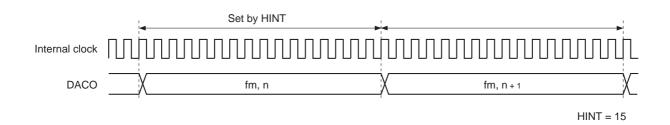

#### HINT7 to 0

This sets the correction point interval in the horizontal direction. Normally, when using 16 points in the horizontal direction, calculate the number of clocks at which the horizontal period can be divided into 16 sections taking into account the input clock and the system clock speed, and then set this value – 1. However, do not input a value of 11 or less to HINT7 to 0, as the internal arithmetic processing may not be able to keep up and the correct value may not be output in this case.

Example 1) Inputting a dot clock 40MHz signal to a SVGA panel (800 × 600) If 1/2 the dot clock is input as the master clock and the mode without internal 1/2 frequency division (SLCK: L) is used: HINT = (800 ÷ 16 ÷ 2) - 1 = 24

Example 2) Inputting a dot clock 65MHz signal to a XGA panel (1024 × 768) If 1/2 the dot clock is input as the master clock and the mode with internal 1/2 frequency division (SLCK: H) is used: HINT = (1024 ÷ 16 ÷ 4) - 1 = 15

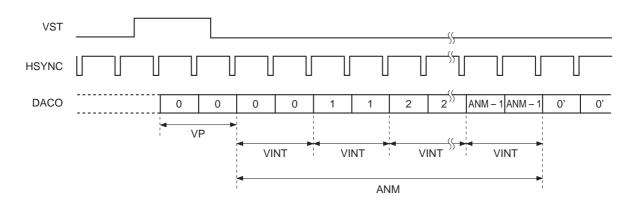

#### VP3 to 0

This sets the correction signal output start position in the vertical direction. The number of line counted from the front edge of the VST pulse at which vertical arithmetic processing of the correction signal starts is set. The correction data for the initial line is output continuously only for the number of lines set by VP.

#### VINT4 to 0

This sets the arithmetic processing interval for vertical correction. Vertical correction arithmetic processing is performed every number of lines set by VINT. Normally set arithmetic processing for each line (VINT = 1).

#### ANM5 to 0

This sets the correction point interval in the vertical direction. There are 13 vertical correction points with respect to the actual panel display area switching, so this sets the number of lines at which correction points are spaced for the internal arithmetic processing.

# **Example)** To use the full correction point data in the vertical direction, set the correction point interval ANM as follows.

SVGA panels: ANM = 600 ÷ 12 = 50 (110010) XGA panels: ANM = 76 ÷ 12 = 64 (00000)

#### 1/A6 to 0

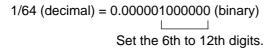

This sets the inverse of ANM. Set the 6th to 12th digits below the decimal point in binary format with 7 bits. Linear interpolation with an accuracy of 1 bit is performed using this setting value.

#### Example) ANM = 50:

1/50 (decimal) = 0.000001010010 (binary)

#### Example) ANM = 64:

#### HSOFF

This is the correction ON/OFF setting. When H, correction is on; when L, correction is off and the INIT5 to 0 data is output constantly. Normally set HSOFF to H.

#### HPOL

This sets the HSYNC input signal polarity. Set HPOL to H for positive polarity, and to L for negative polarity. Be sure to set the polarity correctly in accordance with the input signal.

#### VSPOL

This sets the VST input signal polarity. Set VSPOL to H for positive polarity, and to L for negative polarity. Be sure to set the polarity correctly in accordance with the input signal. The Sony timing generator ICs CXD2464R and CXD3500R output an inverse polarity VST pulse for up/down inverse drive of a SVGA panel. Therefore, take special care for the VST polarity when using this IC with a SVGA panel.

#### DWN, RGT

DWN and RGT set up/down and right/left inversion, respectively. Normal scan is supported when DWN is H and RGT is H, and up/down and/or right/left inversion of the panel is supported by reading the correction data set in the RAM in the reverse order when these are set to L, respectively. These settings can be controlled from the external pins of the same name DWN (Pin 5) and RGT (Pin 6) by setting CTRL (Pin 7) to H. In this case these serial settings are invalid.

#### DACKP2 to 0

This sets the DAC clock phase. Normally set to "2" to satisfy the internal DAC clock and data setup/hold specifications.

#### STBY1 and 0

This is the standby setting. Standby mode results when STBY1, 0 are set to H, L. At this time, the internal clock is supplied only to the serial interface block, and operation of all other blocks is stopped. Buffer outputs AOUT2, 1 and 0 and digital outputs DOUT25 to 20, 15 to 10 and 05 to 00 are all high impedance at this time.

#### INIT5 to 0

This sets the DACO output level when correction is off. When serial data HSOFF is set to L, the data for this setting is output regardless of the correction data set in the RAM.

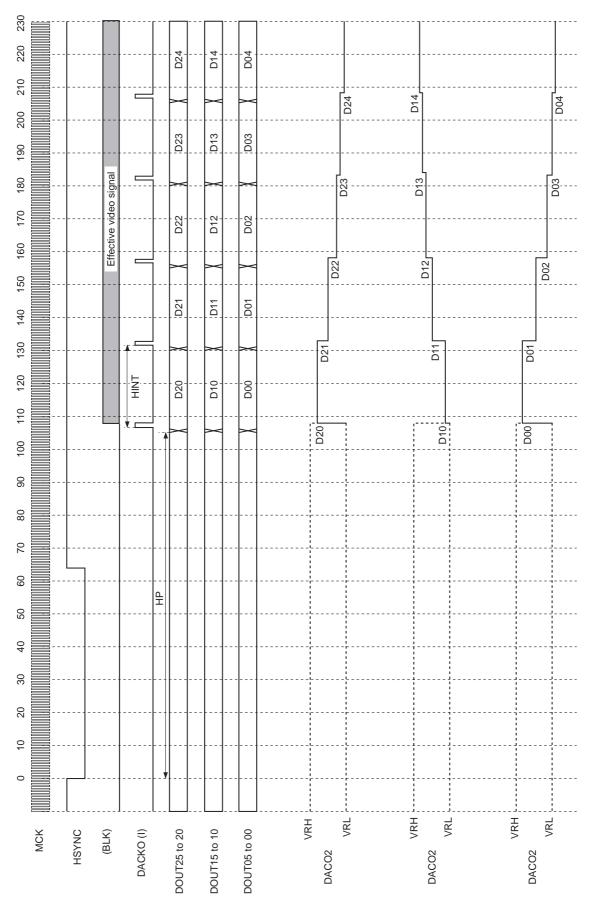

**Timing Chart**

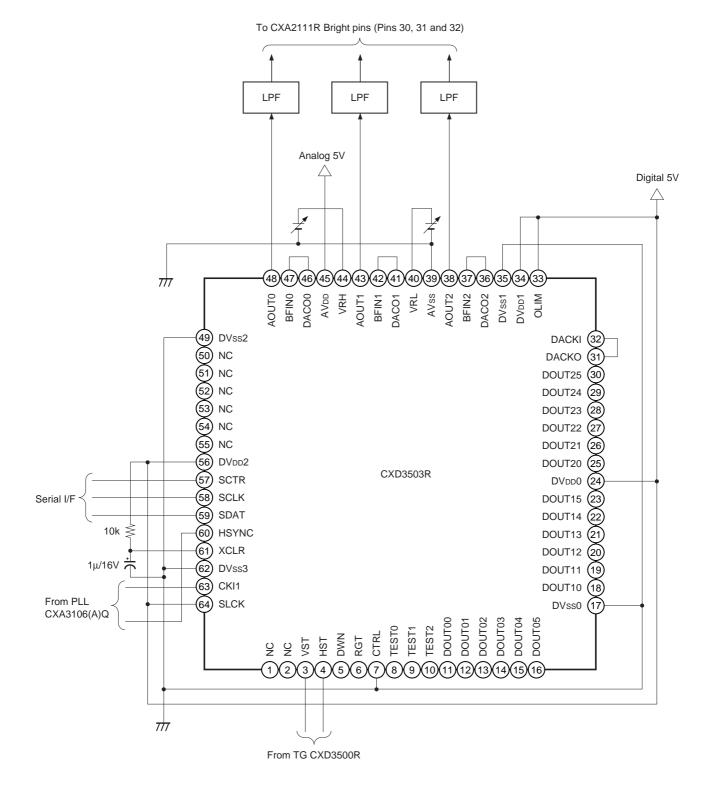

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

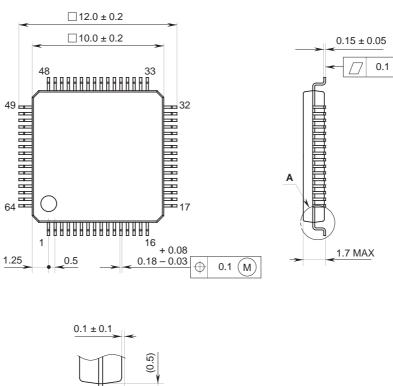

64PIN LQFP (PLASTIC)

| 0.1 ± 0.1 |               |

|-----------|---------------|

|           | (0.5)         |

| 0° to 10° | $0.5 \pm 0.2$ |

| DETAIL A  | 1             |

| SONY CODE  | LQFP-64P-L061     |

|------------|-------------------|

| EIAJ CODE  | LQFP064-P-1010-AY |

| JEDEC CODE |                   |

#### PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN    |  |  |

|------------------|----------------|--|--|

| LEAD TREATMENT   | SOLDER PLATING |  |  |

| LEAD MATERIAL    | 42 ALLOY       |  |  |

| PACKAGE WEIGHT   | 0.3g           |  |  |