# PRELIMINARY

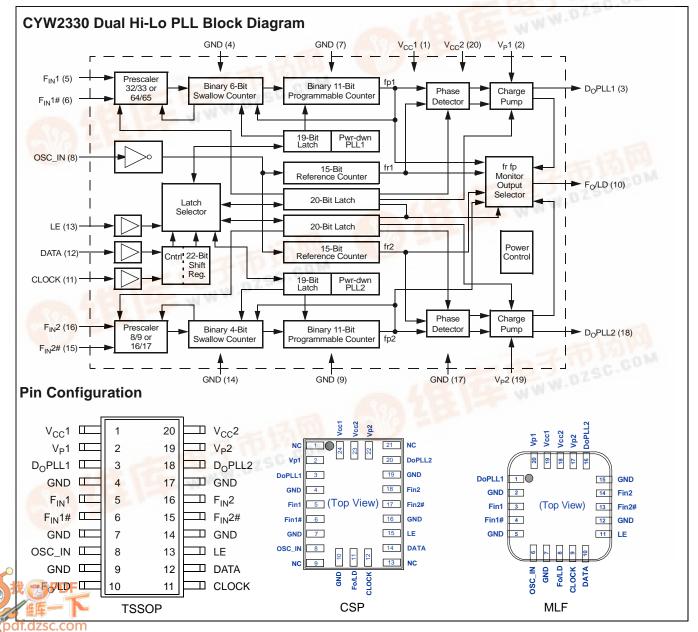

CYW2330

# Dual Serial Input PLL with 2.5-GHz and 600-MHz Prescalers

#### **Features**

- Operating voltage: 2.7 V to 5.5 V

- PLL1 operating frequency:

- -2.5 GHz with prescaler ratios of 32/33 and 64/65

- PLL2 operating frequency:

- 600 MHz with prescaler ratios of 8/9 and 16/17

- Lock detect feature

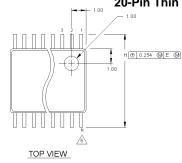

- Available in a 20-pin TSSOP (Thin Shrink Small Outline Package)

- Available in a 24-pin CSP (Chip Scale Package)

- Available in a 20-pin MLF (Mirco Lead Frame Package)

### **Applications**

The Cypress CYW2330 is a dual serial input PLL frequency synthesizer which includes a 2.5-GHz RF and a 600-MHz IF dual modulus prescaler to combine the RF and IF mixer frequency sections of wireless communication systems. The synthesizer is designed for cordless/cellular telephone systems, cable TV tuners, WLANs and other wireless communication systems. The device operates from 2.7 V and dissipates only 24 mW.

# **Pin Definitions**

| Pin Name            | Pin<br>No.<br>(TSSOP) | Pin<br>No.<br>(CSP)    | Pin<br>No.<br>(MLF) | Pin<br>Type | Pin Description                                                                                                                                                                                                                  |

|---------------------|-----------------------|------------------------|---------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> 1   | 1                     | 24                     | 19                  | Р           | <b>Power Supply Connection for PLL1 and PLL2:</b> When power is removed from both the $V_{CC}1$ and $V_{CC}2$ pins, all latched data is lost.                                                                                    |

| V <sub>P</sub> 1    | 2                     | 2                      | 20                  | Р           | <b>PLL1 Charge Pump Rail Voltage:</b> This voltage accommodates VCO circuits with tuning voltages higher than the V <sub>CC</sub> of PLL1.                                                                                       |

| D <sub>O</sub> PLL1 | 3                     | 3                      | 1                   | 0           | PLL1 Charge Pump Output: The phase detector gain is $I_P/2\pi$ . Sense polarity can be reversed by setting the FC bit in software (via the Shift Register).                                                                      |

| F <sub>IN</sub> 1   | 5                     | 5                      | 3                   | I           | Input to PLL1 Prescaler: Maximum frequency 2.5 GHz.                                                                                                                                                                              |

| F <sub>IN</sub> 1#  | 6                     | 6                      | 4                   | I           | Complementary Input to PLL1 Prescaler: A bypass capacitor should be placed as close as possible to this pin and must be connected directly to the ground plane.                                                                  |

| OSC_IN              | 8                     | 8                      | 6                   | I           | Oscillator Input: This input has a V <sub>CC</sub> /2 threshold and CMOS logic level sensitivity.                                                                                                                                |

| F <sub>O</sub> /LD  | 10                    | 11                     | 8                   | 0           | Lock Detect Pin of PLL1 Section: This output is HIGH when the loop is locked. It is multiplexed to the output of the programmable counters or reference dividers in the test program mode. (Refer to Table 3 for configuration.) |

| CLOCK               | 11                    | 12                     | 9                   | I           | <b>Data Clock Input:</b> One bit of data is loaded into the Shift Register on the rising edge of this signal.                                                                                                                    |

| DATA                | 12                    | 14                     | 10                  | I           | Serial Data Input                                                                                                                                                                                                                |

| LE                  | 13                    | 15                     | 11                  | I           | Load Enable: On the rising edge of this signal, the data stored in the Shift Register is latched into the reference counter and configuration controls, PLL1 or PLL2 depending on the state of the control bits.                 |

| F <sub>IN</sub> 2#  | 15                    | 17                     | 13                  | I           | Complementary Input to PLL2 Prescaler: A bypass capacitor should be placed as close as possible to this pin and must be connected directly to the ground plane.                                                                  |

| F <sub>IN</sub> 2   | 16                    | 18                     | 14                  | I           | Input to PLL2 Prescaler: Maximum frequency 600 MHz.                                                                                                                                                                              |

| D <sub>O</sub> PLL2 | 18                    | 20                     | 16                  | 0           | PLL2 Charge Pump Output: The phase detector gain is $I_P/2\pi$ . Sense polarity can be reversed by setting the FC bit in software (via the Shift Register).                                                                      |

| V <sub>P</sub> 2    | 19                    | 22                     | 17                  | Р           | <b>PLL2 Charge Pump Rail Voltage:</b> This voltage accommodates VCO circuits with tuning voltages higher than the V <sub>CC</sub> of PLL2.                                                                                       |

| V <sub>CC</sub> 2   | 20                    | 23                     | 18                  | Р           | <b>Power Supply Connections for PLL1 and PLL2:</b> When power is removed from both the $\rm V_{CC}1$ and $\rm V_{CC}2$ pins, all latched data is lost.                                                                           |

| GND                 | 4, 7, 9,<br>14, 17    | 4, 7,<br>10,<br>16, 19 | 2, 5, 7,<br>12, 15  | G           | Analog and Digital Ground Connections: This pin must be grounded.                                                                                                                                                                |

| N/C                 | N/A                   | 1, 9,<br>13, 21        | N/A                 | N/C         | No Connect.                                                                                                                                                                                                                      |

### **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating

only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description          | Rating                       | Unit |

|-----------------------------------|----------------------|------------------------------|------|

| V <sub>CC</sub> or V <sub>P</sub> | Power Supply Voltage | -0.5 to +6.5                 | V    |

| V <sub>OUT</sub>                  | Output Voltage       | -0.5 to V <sub>CC</sub> +0.5 | V    |

| I <sub>OUT</sub>                  | Output Current       | ±15                          | mA   |

| TL                                | Lead Temperature     | +260                         | °C   |

| T <sub>STG</sub>                  | Storage Temperature  | -55 to +150                  | °C   |

### **Handling Precautions**

Devices should be transported and stored in antistatic containers.

These devices are static sensitive. Ensure that equipment and personnel contacting the devices are properly grounded.

Cover workbenches with grounded conductive mats.

Always turn off power before adding or removing devices from system.

Protect leads with a conductive sheet when handling or transporting PC boards with devices.

If devices are removed from the moisture protective bags for more than 36 hours, they should be baked at 85°C in a moisture free environment for 24 hours prior to assembly in less than 24 hours.

#### **Recommended Operating Conditions**

| Parameter                              | Description           | Test Condition            | Rating                  | Unit |

|----------------------------------------|-----------------------|---------------------------|-------------------------|------|

| V <sub>CC1</sub> ,<br>V <sub>CC2</sub> | Power Supply Voltage  |                           | 2.7 to 5.5              | V    |

| V <sub>P</sub>                         | Charge Pump Voltage   |                           | V <sub>CC</sub> to +5.5 | V    |

| T <sub>A</sub>                         | Operating Temperature | Ambient air at 0 CFM flow | -40 to +85              | °C   |

# **Electrical Characteristics:** $V_{CC} = V_P = 2.7 V$ to 5.5V, $T_A = -40 \, ^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$ , Unless otherwise specified

| Parame-<br>ter                    | Description                                             | Test Condition                                                                                                                          | Pin                                     | Min.                  | Тур. | Max.                  | Unit             |

|-----------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------|------|-----------------------|------------------|

| I <sub>CC</sub>                   | Power Supply Current<br>PLL1 + PLL2                     | $V_{CC}1 = V_{CC}2 = 3.0V$                                                                                                              | V <sub>CC</sub> 1,<br>V <sub>CC</sub> 2 |                       | 8.5  |                       | mA               |

| I <sub>PD</sub>                   | Power-down Current                                      | Power-down, V <sub>CC</sub> = 3.0V                                                                                                      | V <sub>CC</sub> 1,<br>V <sub>CC</sub> 2 |                       | 1    | 25                    | μA               |

| F <sub>IN</sub> 1                 | Operating Frequency                                     | PLL1                                                                                                                                    | F <sub>IN</sub> 1                       | 100                   |      | 2500                  | MHz              |

| F <sub>IN</sub> 2                 |                                                         | PLL2                                                                                                                                    | F <sub>IN</sub> 2                       | 45                    |      | 600                   | MHz              |

| Fosc                              | Oscillator Input Frequency                              |                                                                                                                                         | OSC_IN                                  | 5                     |      | 45                    | MHz              |

| Fφ                                | Phase Detector Frequency                                |                                                                                                                                         |                                         |                       |      | 10                    | MHz              |

| PF <sub>IN</sub> 1                | Input Sensitivity                                       | V <sub>CC</sub> = 2.7V                                                                                                                  | F <sub>IN</sub> 1                       | -15                   |      | 4                     | dBm              |

|                                   |                                                         | V <sub>CC</sub> = 5.5V                                                                                                                  |                                         | -10                   |      | 4                     | dBm              |

| PF <sub>IN</sub> 2                |                                                         | V <sub>CC</sub> = 2.7V to 5.5V                                                                                                          | F <sub>IN</sub> 2                       | -10                   |      | 4                     | dBm              |

| Vosc                              | Oscillator Input Sensitivity                            | V <sub>CC</sub> = 3.0V                                                                                                                  | OSC_IN                                  | 0.5                   |      |                       | V <sub>P-P</sub> |

| I <sub>IH</sub> , I <sub>IL</sub> | High/Low Level Input<br>Current                         |                                                                                                                                         |                                         | -100                  |      | 100                   | μA               |

| V <sub>IH</sub>                   | High Level Input Voltage                                | V <sub>CC</sub> = 3.0V                                                                                                                  | DATA,                                   | V <sub>CC</sub> * 0.8 |      |                       | V                |

| V <sub>IL</sub>                   | Low Level Input Voltage                                 |                                                                                                                                         | CLOCK,<br>LE                            |                       |      | V <sub>CC</sub> * 0.2 | V                |

| I <sub>IH</sub>                   | High Level Input Current                                |                                                                                                                                         |                                         | -10                   | 0.5  | 10                    | μA               |

| I <sub>IL</sub>                   | Low Level Input Current                                 |                                                                                                                                         |                                         | -10                   | 0.5  | 10                    | μA               |

| V <sub>OH</sub>                   | High level Output Voltage                               | $V_{CC} = 3.0V, I_{OH} = -1 \text{ mA}$                                                                                                 | F <sub>O</sub> /LD                      | V <sub>CC</sub> * 0.8 |      |                       | V                |

| V <sub>OL</sub>                   | Low Level Output Voltage                                | $V_{CC} = 3.0V, I_{OL} = 1 \text{ mA}$                                                                                                  |                                         |                       |      | V <sub>CC</sub> * 0.2 | V                |

| ID <sub>OH(SO)</sub>              | IDO High, Source Current                                | $V_{CC} = V_P = 3.0V,$                                                                                                                  | D <sub>O</sub> PLL1                     |                       | -3.8 |                       | mA               |

| ID <sub>OL(SO)</sub>              | IDO Low, Source Current                                 | $D_0 = V_P/2$                                                                                                                           | D <sub>O</sub> PLL2                     |                       | -1   |                       | mA               |

| ID <sub>OH(SI)</sub>              | IDO High, Sink Current                                  |                                                                                                                                         |                                         |                       | 3.8  |                       | mA               |

| ID <sub>OL(SI)</sub>              | IDO Low, Sink Current                                   |                                                                                                                                         |                                         |                       | 1    |                       | mA               |

| $\Delta ID_O$                     | ID <sub>O</sub> Charge Pump Sink and<br>Source Mismatch | $\begin{split} &V_{CC} = V_P = 3.0V, \\ &[IID_{O(SI)}I - IID_{O(SO)}I]/\\ &[1/2^*\{IID_{O(SI)}]I + IID_{O(SO)}I\}\}^*100\% \end{split}$ |                                         |                       | 3    | 15                    | %                |

| ID <sub>O</sub> vs T              | Charge Pump Current<br>Variation vs. Temperature        | $-40^{\circ}\text{C} < \text{T} < 85^{\circ}\text{C}$ $V_{DO} = V_P/2^{[1]}$                                                            |                                         |                       | 5    |                       | %                |

| I <sub>OFF</sub>                  | Charge Pump High-Impedance Leakage Current              | $V_{CC} = V_P = 3.0V,$                                                                                                                  |                                         |                       | ±2.5 |                       | nA               |

<sup>1.</sup> ID<sub>O</sub>vs T; Charge pump current variation vs. temperature. [IID<sub>O(SI)@T</sub>I - IID<sub>O(SI)@25°C</sub>I]/IID<sub>O(SI)@25°C</sub>I \* 100% and [IID<sub>O(SO)@T</sub>I - IID<sub>O(SO)@25°C</sub>I]/IID<sub>O(SO)@25°C</sub>I \*100%.

# **Timing Waveforms**

Key:

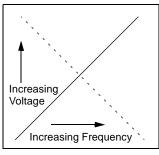

VCO Characteristics

| FC Bit HIGH                               |  |

|-------------------------------------------|--|

| FC Bit LOW                                |  |

| (Refer to Table 2 for meaning of FC bit.) |  |

Phase Comparator Sense

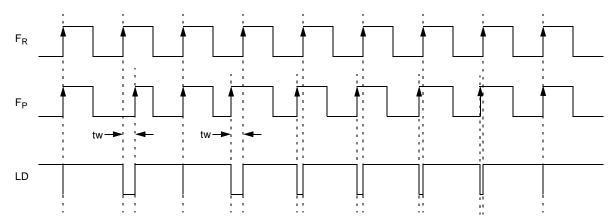

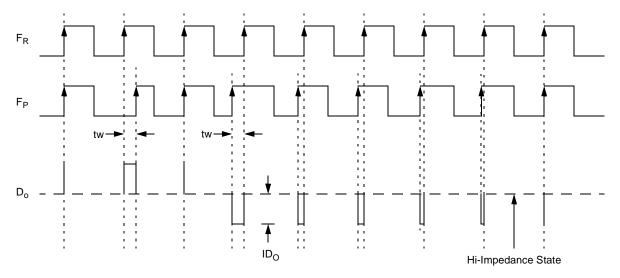

### **Phase Detector Output Waveform**

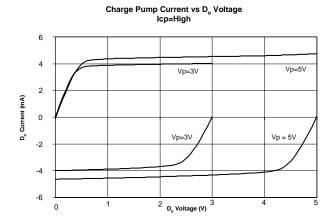

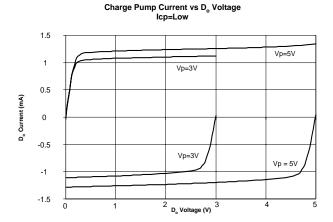

# **D<sub>O</sub> Charge Pump Output Current Waveform**

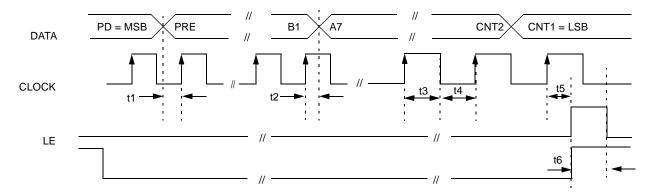

# Timing Waveforms (continued) Serial Data Input Timing Waveform<sup>[2, 3, 4, 5]</sup>

## **Serial Data Input**

Data is input serially using the DATA, CLOCK, and LE pins. Two control bits direct data as described in Table 1.

**Table 1. Control Configuration**

| CNT1 | CNT2 | Function                                                                                                                                                                          |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | <b>Program Reference 2</b> : R = 3 to 32767, set PLL2 (low frequency) phase detector polarity, set current in PLL2, set PLL2 to Hi-Impedance state, set monitor selector to PLL2. |

| 0    | 1    | <b>Program Reference 1:</b> R = 3 to 32767, set PLL1 (high frequency) phase detector polarity, set current in PLL1, set PLL1 to Hi-Impedance state, set monitor selector to PLL1  |

| 1    | 0    | <b>Program Counter for PLL2:</b> A = 0 to 15, B = 3 to 2047, set PLL2 prescaler ratio, set PLL2 to power-down.                                                                    |

| 1    | 1    | <b>Program Counter for PLL1:</b> A = 0 to 63, B = 3 to 2047, set PLL1 prescaler ratio, set PLL1 to power-down.                                                                    |

#### Notes:

- t1-t6 = t > 50 ns.

CLOCK may remain HIGH after latching in data.

DATA is shifted in with the MSB first.

For DATA definitions, refer to *Table 2*.

# Table 2. Shift Register Configuration<sup>[6]</sup>

|        | 2. 011 |        | 9               |                                                                                                                                                                                                                                                                                                                                                                                           | 9       |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

|--------|--------|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------------------|--------------------|---------|---------|--------------------|-------------------|---------|--------------------|---------|----------|---------|---------|---------|--------|

| 1      | 2      | 3      | 4               | 5                                                                                                                                                                                                                                                                                                                                                                                         | 6       | 7       | 8       | 9                 | 10                 | 11      | 12      | 13                 | 14                | 15      | 16                 | 17      | 18       | 19      | 20      | 21      | 22     |

| Refe   | rence  | Coun   | ter an          | d Co                                                                                                                                                                                                                                                                                                                                                                                      | nfigur  | ation   | Bits    |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| CNT1   | CNT2   | R1     | R2              | R3                                                                                                                                                                                                                                                                                                                                                                                        | R4      | R5      | R6      | R7                | R8                 | R9      | R10     | R11                | R12               | R13     | R14                | R15     | FC       | IDO     | TS      | LD      | FO     |

|        |        |        |                 |                                                                                                                                                                                                                                                                                                                                                                                           |         |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| Prog   | ramma  | able ( | Count           | er bits                                                                                                                                                                                                                                                                                                                                                                                   | S       |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| CNT1   | CNT2   | A1     | A2              | А3                                                                                                                                                                                                                                                                                                                                                                                        | A4      | A5      | A6      | A7                | B1                 | B2      | В3      | B4                 | B5                | B6      | B7                 | B8      | В9       | B10     | B11     | PRE     | PD     |

|        |        |        |                 |                                                                                                                                                                                                                                                                                                                                                                                           |         |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| Bit(s) | ) Name | е      | Func            | tion                                                                                                                                                                                                                                                                                                                                                                                      |         |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| CNT′   | I, CNT | 2      | Cont            | rol Bi                                                                                                                                                                                                                                                                                                                                                                                    | ts: Dir | rects p | orogra  | ımmin             | g data             | to Pl   | L1 (h   | igh fre            | equen             | cy) or  | PLL2               | (low f  | reque    | ency).  |         |         |        |

| R1–R   | R15    |        | Refe            | rence                                                                                                                                                                                                                                                                                                                                                                                     | Cour    | iter S  | etting  | Bits:             | 15 bit             | ts, R = | = 3 to  | 32767              | 7. <sup>[7]</sup> |         |                    |         |          |         |         |         |        |

| FC     |        |        | Phas            | e Ser                                                                                                                                                                                                                                                                                                                                                                                     | se of   | the P   | hase    | Dete              | ctor: S            | Set to  | match   | the V              | /CO p             | olarity | , H = ·            | + (Pos  | sitive \ | VCO tı  | ransfe  | r func  | tion). |

| IDO    |        |        | Char            | ge Pu                                                                                                                                                                                                                                                                                                                                                                                     | ımp S   | etting  | Bit:    | ID <sub>O</sub> H | IGH =              | 3.8 m   | nA, ID  | O LOV              | N = 1             | mA at   | : V <sub>P</sub> = | 3V.     |          |         |         |         |        |

| TS     |        |        | Hi-Im           | peda                                                                                                                                                                                                                                                                                                                                                                                      | nce S   | tate E  | Bit: Ma | akes [            | O <sub>O</sub> Hi- | Imped   | dance   | for PL             | _L1 ar            | nd PLI  | 2 whe              | en HIC  | ЭH.      |         |         |         |        |

| LD     |        |        |                 |                                                                                                                                                                                                                                                                                                                                                                                           |         |         |         |                   | ect sig            |         | ource   | oin 10             | . Pin ′           | 10 is H | IIGH v             | with na | arrow    | low ex  | xcursi  | ons w   | hen    |

| FO     |        |        | Frequency purpo | -                                                                                                                                                                                                                                                                                                                                                                                         | Out:    | This I  | oit car | n be s            | et to re           | ead o   | ut refe | rence              | or pr             | ogram   | mable              | e divid | er at    | the LD  | ) pin f | or test |        |

| PRE    |        |        | Pres            | caler                                                                                                                                                                                                                                                                                                                                                                                     | Divide  | e Bit:  | For P   | LL1: L            | OW =               | 32/3    | 3 and   | HIGH               | l = 64/           | 65. F   | or PLL             | 2: LO   | W = 8    | 3/9 and | d HIG   | H = 16  | 6/17.  |

| PD     |        |        | count           | <b>Power-down:</b> LOW = power-up and HIGH = power-down. F <sub>IN</sub> is at a high-impedance state, respective B counter is disabled, forces D <sub>O</sub> outputs to Hi-Impedance and phase comparators are disabled. The reference counter is disabled and the OSC input is high-impedance after both PLLs are powered down. Data can be input and latched in the power-down state. |         |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| A1–A   | .7     |        | Swal            | Swallow Counter Divide Ratio: A = 0 to 63 for PLL1 and 0 to 15 for PLL2.                                                                                                                                                                                                                                                                                                                  |         |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

| B1-B   | 11     |        | Prog            | ramm                                                                                                                                                                                                                                                                                                                                                                                      | able    | Coun    | ter Di  | vide l            | Ratio:             | B = 3   | to 20   | 47. <sup>[7]</sup> |                   |         |                    |         |          |         |         |         |        |

|        |        |        |                 |                                                                                                                                                                                                                                                                                                                                                                                           |         |         |         |                   |                    |         |         |                    |                   |         |                    |         |          |         |         |         |        |

Table 3. F<sub>O</sub>/LD Pin Truth Table

| FO ( | Bit 22) | LD (I | Bit 21) |                                     |

|------|---------|-------|---------|-------------------------------------|

| PLL1 | PLL2    | PLL1  | PLL2    | F <sub>O</sub> /LD Pin Output State |

| 0    | 0       | 0     | 0       | Disable                             |

| 0    | 0       | 0     | 1       | PLL2 Lock Detect                    |

| 0    | 0       | 1     | 0       | PLL1 Lock Detect                    |

| 0    | 0       | 1     | 1       | PLL1/PLL2 Lock Detect               |

| 0    | 1       | Х     | 0       | PLL2 Reference Divider Output       |

| 1    | 0       | Х     | 0       | PLL1 Reference Divider Output       |

| 0    | 1       | Х     | 1       | PLL2 Programmable Divider Output    |

| 1    | 0       | Х     | 1       | PLL1 Programmable Divider Output    |

| 1    | 1       | 0     | 1       | PLL2 Counter Reset                  |

| 1    | 1       | 1     | 0       | PLL1 Counter Reset                  |

| 1    | 1       | 1     | 1       | PLL1/PLL2 Counter Reset             |

Document #: 38-07239 Rev \*\*

The MSB is loaded in first.

Low count ratios may violate frequency limits of the phase detector.

### Table 4. 6-Bit Swallow Counter (A) Truth Table<sup>[8]</sup>

| Divide Ratio A    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

|-------------------|-------|-----|-----|-----|-----|-----|-----|

| PLL1 (High Freque | ency) | •   | 4   | -1  | •   | •   |     |

| 0                 | Х     | 0   | 0   | 0   | 0   | 0   | 0   |

| 1                 | Х     | 0   | 0   | 0   | 0   | 0   | 1   |

| :::               | :::   | ::: | ::: | ::: | ::: | ::: | ::: |

| 62                | Х     | 1   | 1   | 1   | 1   | 1   | 0   |

| 63                | Х     | 1   | 1   | 1   | 1   | 1   | 1   |

| PLL2 (Low Freque  | ency) |     | •   |     |     |     |     |

| 0                 | Х     | Х   | Х   | 0   | 0   | 0   | 0   |

| 1                 | Х     | Х   | Х   | 0   | 0   | 0   | 1   |

| :::               | :::   | ::: | ::: | ::: | ::: | ::: | ::: |

| 14                | Х     | Х   | Х   | 1   | 1   | 1   | 0   |

| 15                | Х     | Х   | Х   | 1   | 1   | 1   | 1   |

# Table 5. 11-Bit Programmable Counter (B) Truth Table [9]

| Divide Ratio B | B11 | B10 | В9  | B8  | B7  | В6  | B5  | B4  | В3  | B2  | B1  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 3              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 4              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| :::            | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: |

| 2046           | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

| 2047           | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

# Table 6. 15-Bit Programmable Reference Counter (for PLL1 and PLL2) Truth Table<sup>[10]</sup>

| Divide Ratio R | R15 | R14 | R13 | R12 | R11 | R10 | R9  | R8  | R7  | R6  | R5  | R4  | R3  | R2  | R1  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 3              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 4              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| :::            | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: |

| 32766          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

| 32767          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

# Ordering Information<sup>[11]</sup>

| Ordering Code | Package<br>Name  | Package Type                                                                                                                                   | Tape and Reel Option |

|---------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| CYW2330       | ZI<br>BCI<br>LFI | 20-pin Thin Shrink Small Outline Package (0.173" wide)<br>24-pin Chip Scale Package (3.5 mm X 4.5 mm)<br>20-pin Micro Lead Frame (4 mm x 4 mm) | TR                   |

#### Notes:

- 8. B is greater than or equal to A.

9. Divide ratio less than 3 is prohibited. (See equation below.)

10. Divide ratio less than 3 is prohibited. The divide ratio can be calculated using the following equation:

$\mathsf{fvco} = \{(\mathsf{P} \ ^\star \mathsf{B}) + \mathsf{A}\} \ ^\star \, \mathsf{fosc} \, / \; \mathsf{R} \; \mathsf{where} \; (\mathsf{A} \leq \mathsf{B})$

fvco: Output frequency of the external VCO. fosc: The crystal reference oscillator frequency.

- A: Preset divide ratio of the 6-bit swallow counter (0 to 63) and the 4-bit swallow counter (0 to 15).

- B: Preset ratio of the 11-bit programmable counter (3 to 2047).

- P: Preset divide ratio of the dual modulus prescaler.

- R: Preset ratio of the 15-bit programmable reference counter (3 to 32767).

The divide ratio N = (P \* B) + A.

11. Operating temperature range: -40°C to +85°C.

Document #: 38-07239 Rev \*\*

Page 8 of 13

# **Typical Performance Characteristics**

**Figure 1.**Do Output Current High Mode

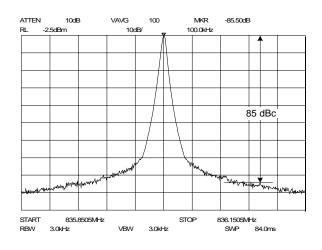

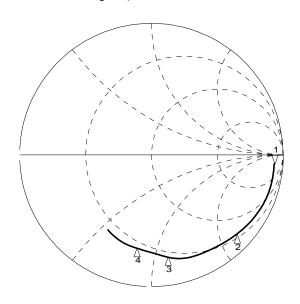

Figure 3. PLL Reference Spurs

PLL Reference Spurious Level is -85.5 dBc

**Figure 3.**Do Output Current Low Mode

| Marker Reference<br>Number | Real | Imaginar y | Input<br>Frequency |

|----------------------------|------|------------|--------------------|

| Marker 1                   | 623  | -823       | 100 MHz            |

| Marker 2                   | 21   | -120       | 1 GHz              |

| Marker 3                   | 14   | -55        | 1.8 GHz            |

| Marker 4                   | 13   | -39        | 2.2 GHz            |

$\label{eq:Figure 4.} Figure \ 4.$  Input Impedance  $F_{IN}1,F_{IN}2$   $VCC = 2.7 \ to \ 5.5V, F_{IN} = 75 \ MHz \ to \ 2.6 \ GHz$

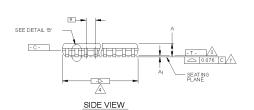

# **Package Diagram**

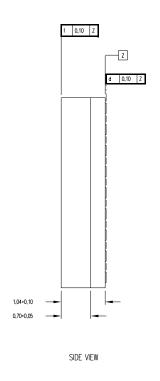

# 20-Pin Thin Shrink Small Outline Package (TSSOP, 0.173" wide)

#### END VIEW

#### NOTES:

- 1. DIE THICKNESS ALLOWABLE IS 0, 279±0, 0127 (,0110±,0005 INCHES)

2. DIMENSIONING & TOLERANCES PER ANSI, Y14.5M-1982.

1. "T" IS A REFERENCE DATUM.

- ↑ "T" IS A REFERENCE DATUM.

↑ "T" 'S "E" ARE REFERENCE DATUMS AND DO NOT INCLUDE MULD FLASH OF PROTRUSIONS, AND ARE MEASURED AT THE PARTING LINE MOLD FLASH OR DEPOSITION AND THE PARTING LINE FASTER OF SOLDERING TO A SUBSTRATE.

↑ TERMINAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

↑ FORMED LEADS SHALL BE PLANHAR WITH RESPECT TO ONE ANOTHER WITHIN 10 ORTHOR HAT PROTRUSION SHALL BE DAMBAR PROTRUSION SHALL BE DAMBAR PROTRUSION ALLO WELD FAME AND THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLO WAS LEED AND AND THE LEAD WIDTH DIMENSION AT MADAMAM MATERIAL CONTION. DAMBAR CANNOT BE SECONDAY. OF A PARTING THE PARTING SHALL BE DAMBAR PROTRUSION SHALL BE DAMBAR PROTRUSION SHALL BE DAMBAR PROTRUSION. AND AN ADJACENT LEAD TO BE 0 14mm SEE DETAILS SHAND:

↑ TO 12 SM PROTRUSIONS AND AN ADJACENT LEAD TO 10 10 CONTROLLING DIMENSION MILLIMETERS.

1. THIS PART IS COMPLIANT WITH JEDES SPECIFICATION MO-153. VARIATIONS AA, AS, AC, AD AND AE.

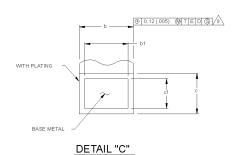

DETAIL "B"

#### THIS TABLE IN MILLIMETERS

| S      | COMMON           |           |       |                  | NOTE           | 4    |      |      | 6  |

|--------|------------------|-----------|-------|------------------|----------------|------|------|------|----|

| M<br>B | DI               | MENSIO    | NS    | N <sub>OTE</sub> | ∾。   VARI-   D |      |      |      | N  |

| 2      | MIN.             | NOM.      | MAX.  | T <sub>E</sub>   | ATIONS         | MIN. | NOM. | MAX. |    |

| Α      |                  |           | 1.10  |                  | AA             | 2.90 | 3.00 | 3.10 | 8  |

| Aı     | 0.05             | 0.10      | 0.15  |                  | AB             | 4.90 | 5.00 | 5.10 | 14 |

| A2     | 0.85             | 0.90      | 0.95  |                  | AC             | 4.90 | 5.00 | 5.10 | 16 |

| b      | 0.19             | -         | 0.30  | 8                | AD             | 6.40 | 6.50 | 6.60 | 20 |

| b1     | 0.19             | 0.22      | 0.25  |                  | AE             | 7.70 | 7.80 | 7.90 | 24 |

| С      | 0.090            | -         | 0.20  |                  | AF             | 9.60 | 9.70 | 9.80 | 28 |

| c1     | 0.090            | 0.127     | 0.135 |                  |                |      |      |      |    |

| D      | SEE              | VARIATION | IS    | 4                |                |      |      |      |    |

| E      | 4.30             | 4.40      | 4.50  | 4                |                |      |      |      |    |

| е      | 0.65 BSC         |           |       |                  |                |      |      |      |    |

| Н      | 6.25             | 6.40      | 6.50  |                  |                |      |      |      |    |

| L      | 0.50             | 0.60      | 0.70  | 5                |                |      |      |      |    |

| Ŋ      | N SEE VARIATIONS |           |       | 6                |                |      |      |      |    |

| č      | 0° 4° 8°         |           |       |                  |                |      |      |      |    |

#### THIS TABLE IN INCHES

| S              | COMMON           |           |                |                | NOTE   | 4    |      |      | 6  |

|----------------|------------------|-----------|----------------|----------------|--------|------|------|------|----|

|                | M DIMENSIONS     |           | N <sub>O</sub> | VARI- D        |        |      | N    |      |    |

| 2              | MIN.             | NOM.      | MAX.           | T <sub>E</sub> | ATIONS | MIN. | NOM. | MAX. |    |

| Α              |                  |           | .0433          |                | AA     | .114 | .118 | .122 | 8  |

| A <sub>1</sub> | .002             | .004      | .006           |                | AB     | .193 | .197 | .201 | 14 |

| A <sub>2</sub> | .0335            | .0354     | .0374          |                | AC     | .193 | .197 | .201 | 16 |

| b              | .0075            | -         | .0118          | 8              | AD     | .252 | .256 | .260 | 20 |

| b1             | .0075            | .0087     | .0098          |                | AE     | .303 | .307 | .311 | 24 |

| С              | .0035            | -         | .0079          |                | AF     | .378 | .382 | .386 | 28 |

| c1             | .0035            | .0050     | .0053          |                |        |      |      |      |    |

| D              | SEE              | VARIATION | is             | 4              |        |      |      |      |    |

| Е              | .169             | .173      | .177           | 4              |        |      |      |      |    |

| е              | e .0256 BSC      |           |                |                |        |      |      |      |    |

| Н              | .246             | .252      | .256           |                |        |      |      |      |    |

| L              | .020             | .024      | .028           | 5              |        |      |      |      |    |

| Ŋ              | N SEE VARIATIONS |           |                | 6              |        |      |      |      |    |

| 68             | 0°               | 4°        | 8°             |                |        |      |      |      |    |

\*VARIATION AF IS DESIGNED BUT NOT TOOLED\*

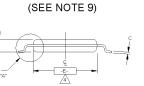

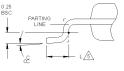

# **Package Diagram**

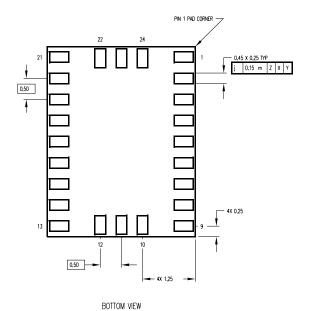

### 24-Pin Chip Scale Package (CSP 3.5 mm X 4.5 mm)

ALL DIMENSIONS AND TOLERANCES CONFORM TO ASME Y14,5M-1994, UNLESS OTHERWISE SPECIFIED

5011011111

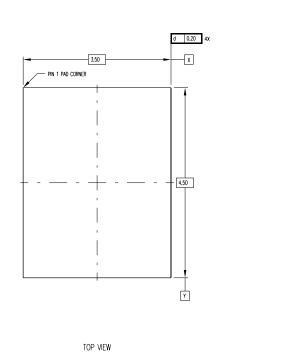

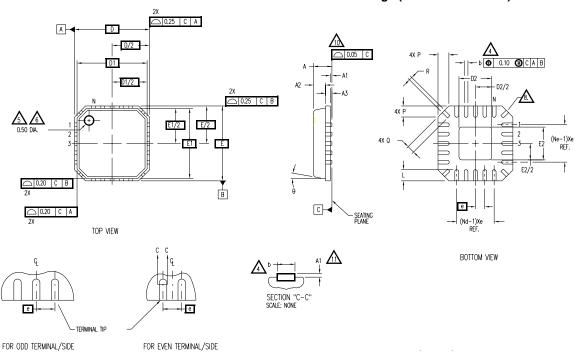

### **Package Diagram**

#### 20-Pin Micro Lead Frame Package (MLF 4 mm X 4 mm)

| S<br>Y<br>8<br>0 | COMMON     |              |      |                  |  |  |  |  |

|------------------|------------|--------------|------|------------------|--|--|--|--|

| N.               | DIMENSIONS |              |      |                  |  |  |  |  |

|                  | MIN.       | NOM.         | MAX. | N <sub>0</sub> , |  |  |  |  |

| A<br>A1          | -          | 0.85         | 1.00 |                  |  |  |  |  |

| A1               | 0.00       | 0.01         | 0.05 | 11               |  |  |  |  |

| A2<br>A3         | -          | 0.65         | 0.80 |                  |  |  |  |  |

| A3               |            | 0.20 REF.    |      |                  |  |  |  |  |

| D                |            | 4.00 BSC     |      |                  |  |  |  |  |

| D1               |            | 3.75 BSC     |      |                  |  |  |  |  |

| Ε                |            | 4.00 BSC     |      |                  |  |  |  |  |

| E1               |            | 3.75 BSC     |      |                  |  |  |  |  |

| θ                |            | 12           |      |                  |  |  |  |  |

| Р                | 0.24       | 0.42         | 0.60 |                  |  |  |  |  |

| R                | 0.13       | 0.17         | 0.23 |                  |  |  |  |  |

| e                |            | 0.50 BSC     |      |                  |  |  |  |  |

| N                | 20         |              |      |                  |  |  |  |  |

| Nd               | 5<br>5     |              |      |                  |  |  |  |  |

| Ne               |            |              |      |                  |  |  |  |  |

| L                | 0.50       | 0.60         | 0.75 |                  |  |  |  |  |

| b                | 0.18       | 0.23         | 0.30 | 4                |  |  |  |  |

| Q                | 0.30       | 0.40<br>1.70 | 0.65 |                  |  |  |  |  |

| D2               | 1.55       | 1.85<br>1.85 |      |                  |  |  |  |  |

| E2               | 1.55       |              |      |                  |  |  |  |  |

NOTES:

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm  $\operatorname{MAXIMUM}(.012\ \operatorname{INCHES}\ \operatorname{MAXIMUM})$

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

3. N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

4. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED

BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

7. ALL DIMENSIONS ARE IN MILLIMETERS.

8. THE SHAPE SHOWN ON FOUR CORNERS ARE NOT ACTUAL I/O.

PACKAGE WARPAGE MAX 0.05mm,

APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDING PART OF EXPOSED

PAD FROM MEASURING.

APPLIED ONLY FOR TERMINALS.

CYW2330

| Document Title: CYW2330 Dual Serial Input PLL with 2.5 GHz and 600 MHz Prescalers Document Number: 38-07239 |                                                |          |     |                                               |  |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------|-----|-----------------------------------------------|--|

| REV.                                                                                                        | REV. ECN NO. Date Change Description of Change |          |     |                                               |  |

| **                                                                                                          | 110504                                         | 01/07/02 | SZV | Change from Spec number: 38-00966 to 38-07239 |  |