**NEC** NEC Electronic U.S.A. Inc.

Electronic Arrays Division

**NMOS**

**μPD2364**

## READ ONLY MEMORY 8192 WORDS, 8 BITS/WORD

### FEATURES:

- Three Fast Access Times

- 450nsec

- 350nsec

- 300nsec

- All Inputs and Outputs TTL Compatible

- Single +5V  $\pm$  10% Power Supply

- One Programmable Chip Select

- Three-State Outputs for Direct Bus Compatibility

- Pin Compatible to 2716, 2732, and 2564 EPROMS

- Fully Static Operation

- All Inputs Protected Against Static Charge

- 100% Burned-In

### GENERAL DESCRIPTION:

The μPD2364 is a 65,536 bit Read Only Memory utilizing MOS N-Channel silicon gate technology. The device is completely static in operation, organized as 8192 words by 8 bits and operates from a single +5V power supply. All inputs and outputs are fully TTL compatible. It has one programmable chip select input and three-state outputs that allow memory expansion to 16,384 words by 8 bits without the use of external logic. Programming of the device is accomplished by a custom mask during fabrication. Pinout is compatible with 2716, 2732, and 2564 EPROMs.

### PIN CONFIGURATION (TOP VIEW)

|                |    |    |                 |

|----------------|----|----|-----------------|

| A <sub>7</sub> | 1  | 24 | V <sub>CC</sub> |

| A <sub>6</sub> | 2  | 23 | A <sub>8</sub>  |

| A <sub>5</sub> | 3  | 22 | A <sub>9</sub>  |

| A <sub>4</sub> | 4  | 21 | A <sub>12</sub> |

| A <sub>3</sub> | 5  | 20 | CS <sub>1</sub> |

| A <sub>2</sub> | 6  | 19 | A <sub>10</sub> |

| A <sub>1</sub> | 7  | 18 | A <sub>11</sub> |

| A <sub>0</sub> | 8  | 17 | O <sub>7</sub>  |

| O <sub>0</sub> | 9  | 16 | O <sub>6</sub>  |

| O <sub>1</sub> | 10 | 15 | O <sub>5</sub>  |

| O <sub>2</sub> | 11 | 14 | O <sub>4</sub>  |

| GND            | 12 | 13 | O <sub>3</sub>  |

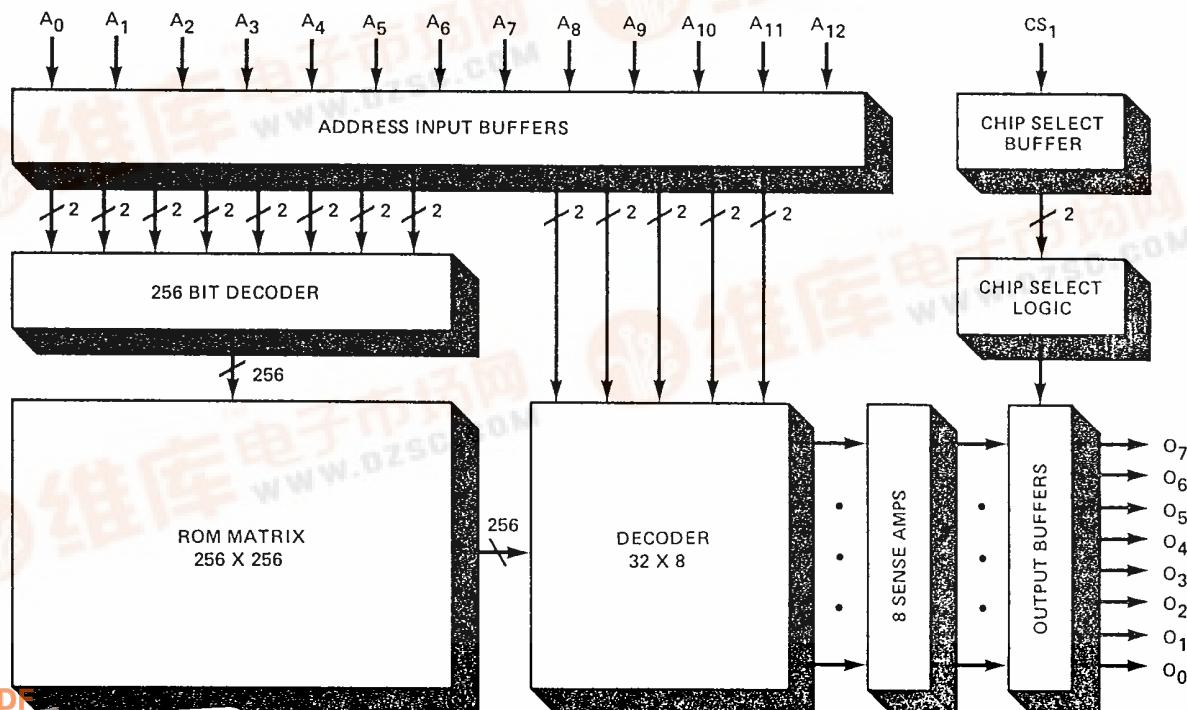

### BLOCK DIAGRAM

## ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter             | Ratings     | Unit |

|------------------|-----------------------|-------------|------|

| V <sub>CC</sub>  | Supply Voltage        | -0.5 to +7  | V    |

| V <sub>I</sub>   | Input Voltage         | -0.5 to +7  | V    |

| V <sub>O</sub>   | Output Voltage        | -0.5 to +7  | V    |

| T <sub>opt</sub> | Operating Temperature | -0 to +70   | °C   |

| T <sub>stg</sub> | Storage Temperature   | -65 to +125 | °C   |

Stresses more severe than those listed here may cause permanent damage to the device. This is a stress rating only, and operation of the device at any condition above those indicated in the operational sections of this specification is not implied.

## D.C. CHARACTERISTICS (T<sub>a</sub> = 0° to +70°C, V<sub>CC</sub> = +5 ± 10%)

| Symbol          | Parameter              | Test Condition                                            | Min. | Typ. | Max.                | Unit |

|-----------------|------------------------|-----------------------------------------------------------|------|------|---------------------|------|

| V <sub>IL</sub> | Input "Low" Voltage    |                                                           | -0.5 |      | 0.8                 | V    |

| V <sub>IH</sub> | Input "High" Voltage   |                                                           | 2.0  |      | V <sub>CC</sub> + 1 | V    |

| I <sub>IL</sub> | Input Load Current     | V <sub>IN</sub> = 0 to 5.5V                               |      |      | 10                  | μA   |

| V <sub>OL</sub> | Output "Low" Voltage   | I <sub>OL</sub> = +2.1mA                                  |      |      | 0.4                 | V    |

| V <sub>OH</sub> | Output "High" Voltage  | I <sub>OH</sub> = -400μA                                  | 2.4  |      |                     | V    |

| I <sub>LO</sub> | Output Leakage Current | Chip Disabled V <sub>OUT</sub> = +0.4V to V <sub>CC</sub> |      |      | 10                  | μA   |

| I <sub>CC</sub> | Power Supply Current   | All inputs +5.5V Output Disabled                          |      | 80   | 140                 | mA   |

## A.C. CHARACTERISTICS (T<sub>a</sub> = 0° to +70°C, V<sub>CC</sub> = +5 ± 10%)

| Symbol           | Parameter           | μPD2364-30 |      | μPD2364-35 |      | μPD2364-45 |      | Unit |

|------------------|---------------------|------------|------|------------|------|------------|------|------|

|                  |                     | Min.       | Max. | Min.       | Max. | Min.       | Max. |      |

| t <sub>ACC</sub> | Access Time         |            | 300  |            | 350  |            | 450  | nsec |

| t <sub>CO</sub>  | Output Enable Time  |            | 120  |            | 150  |            | 150  | nsec |

| t <sub>DF</sub>  | Output Disable Time |            | 120  |            | 150  |            | 150  | nsec |

| t <sub>OH</sub>  | Output Hold Delay   | 20         |      | 20         |      | 20         |      | nsec |

| C <sub>I</sub>   | Input Capacitance   |            | 10   |            | 10   |            | 10   | pf   |

| C <sub>O</sub>   | Output Capacitance  |            | 15   |            | 15   |            | 15   | pf   |

## A.C. TEST CONDITIONS

Input rise and fall times (t<sub>r</sub>, t<sub>f</sub>) = 20 nsec

Timing Measurement Reference Levels:

Input and output high levels (V<sub>IH</sub>, V<sub>OH</sub>) = 2.0 Volts

Input and output low levels (V<sub>IL</sub>, V<sub>OL</sub>) = 0.8 Volts

Output load = 1 series 74 TTL + 100 pf

7

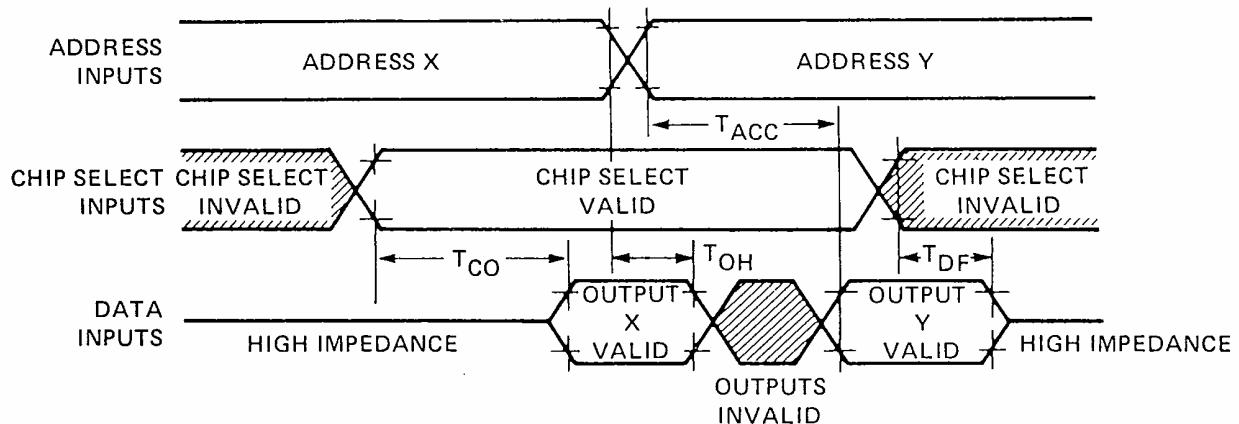

## TIMING DIAGRAM

## DEFINITIONS

### Access Time, $t_{ACC}$

Access time is the maximum time between the application of a valid Address and the corresponding valid Data Out.

### Output Hold Delay, $t_{OH}$

Output hold delay is the minimum time after an Address change that the previous data remains valid.

### Output Enable Time, $t_{CO}$

Output enable time is the maximum delay between Chip Selects becoming true and Output Data becoming valid.

### Output Disable Time, $t_{DF}$

Output disable time is the delay between Chip Selects becoming false and output stages going to the high impedance state.

## CUSTOM PROGRAMMING INSTRUCTIONS

### BIT PATTERN SUBMITTAL OPTIONS:

The customer's unique bit pattern can be submitted in several convenient methods that are easy for the ROM customer, and readily verifiable for accuracy. The bit pattern can be delivered to NEC contained within:

1. One programmed 2764 EPROM

2. Two programmed 2732 EPROMs

### BIT PATTERN VERIFICATIONS:

For customer verification of the submitted bit patterns, several alternatives are also available. The following are those found to be most expeditious.

| CUSTOM PATTERN SUBMITTED VIA: | VERIFICATION ROUTINE                                                                                                                                              |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. One programmed 2764 EPROM  | Customer sends NEC one additional erased 2764. NEC programs the spare 2764 with the data from the programmed 2764, and returns to customer for verification.      |

| 2. Two programmed 2732 EPROMs | Customer sends NEC two additional erased 2732's. NEC programs the spare 2732's with the data from the programmed EPROMs and returns to customer for verification. |

## ORDERING INFORMATION

| PART NUMBER<br><b>INDUSTRIAL</b> | ACCESS TIME | PACKAGE    |

|----------------------------------|-------------|------------|

| $\mu$ PD 2364-45PC               | 450nsec     | Molded DIP |

| $\mu$ PD 2364-35PC               | 350nsec     | Molded DIP |

| $\mu$ PD 2364-30PC               | 300nsec     | Molded DIP |

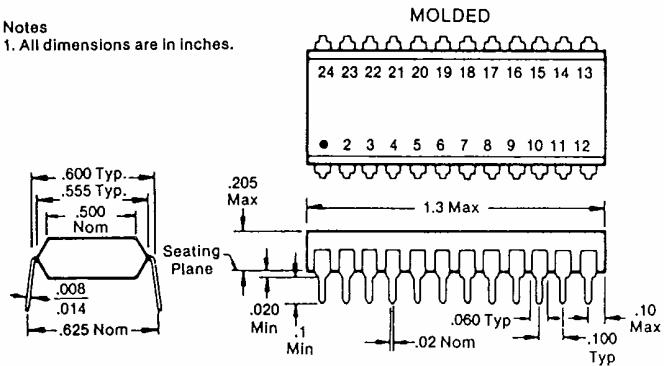

## PHYSICAL DIMENSIONS

**Notes**

1. All dimensions are in inches.

Device also available in ceramic package.

NEC RESERVES THE RIGHT TO MAKE CHANGES IN THESE SPECIFICATIONS AT ANY TIME

NEC

Electronic Arrays Division, 550 East Middlefield Road, Mountain View, CA 94043, Telephone (415) 964-4321. TWX 910-379-6985