# LC<sup>2</sup>MOS 20-Bit A/D Converter

AD7703

#### **FEATURES**

Monolithic 20-Bit ADC

0.0003% Linearity Error

20-Bit No Missed Codes

On-Chip Self-Calibration Circuitry

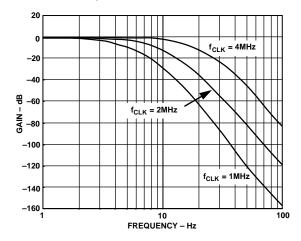

Programmable Low-Pass Filter

0.1 Hz to 10 Hz Corner Frequency

0 to +2.5 V or +2.5 V Analog Input Range

4 kSPS Output Data Rate

Flexible Serial Interface

Ultralow Power

APPLICATIONS

Industrial Process Control

Weigh Scales

Portable Instrumentation

Remote Data Acquisition

#### GENERAL DESCRIPTION

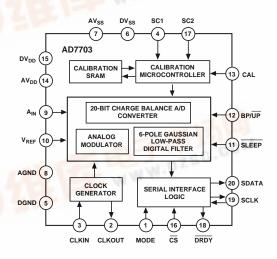

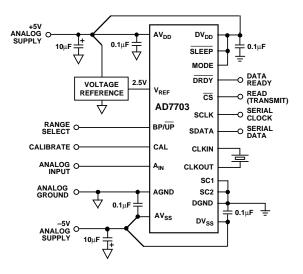

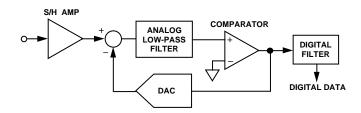

The AD7703 is a 20-bit ADC which uses a sigma delta conversion technique. The analog input is continuously sampled by an analog modulator whose mean output duty cycle is proportional to the input signal. The modulator output is processed by an on-chip digital filter with a six-pole Gaussian response, which updates the output data register with 20-bit binary words at word rates up to 4 kHz. The sampling rate, filter corner frequency and output word rate are set by a master clock input that may be supplied externally, or by an on-chip gate oscillator.

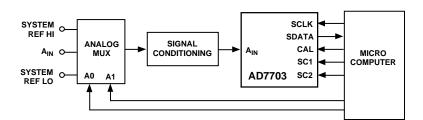

The inherent linearity of the ADC is excellent, and endpoint accuracy is ensured by self-calibration of zero and full scale which may be initiated at any time. The self-calibration scheme can also be extended to null system offset and gain errors in the input channel.

The output data is accessed through a serial port, which has two synchronous modes suitable for interfacing to shift registers or the serial ports of industry standard microcontrollers.

CMOS construction ensures low power dissipation, and a power down mode reduces the idle power consumption to only 10  $\mu$ W.

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **PRODUCT HIGHLIGHTS**

- 1. The AD7703 offers 20-bit resolution coupled with outstanding 0.0003% accuracy.

- 2. No missing codes ensures true, usable, 20-bit dynamic range, removing the need for programmable gain and level-setting circuitry.

- 3. The effects of temperature drift are eliminated by on-chip self-calibration, which removes zero and gain error. External circuits can also be included in the calibration loop to remove system offsets and gain errors.

- A flexible synchronization allows the AD7703 to interface directly to the serial ports of industry standard microcontrollers and DSP processors.

- 5. Low operating power consumption and an ultralow power standby mode make the AD7703 ideal for loop powered remote sensing applications, or battery-powered portable instruments.

## $\begin{array}{l} \textbf{AD7703-SPECIFICATIONS} \text{ ($T_A=+25^{\circ}$C$; $AV_{DD}=DV_{DD}=+5$ V$; $AV_{SS}=DV_{SS}=-5$ V$; $V_{REF}=+2.5$ V$; $f_{CLKIN}=4.096$ MHz$; \\ BP/\overline{\textbf{UP}}=+5$ V$; $MODE=+5$ V$; $A_{IN}$ Source Resistance=1 k$\Omega^{1}$ with 1 nF to AGND at $A_{IN}$ unless otherwise noted.) \\ \end{array}$

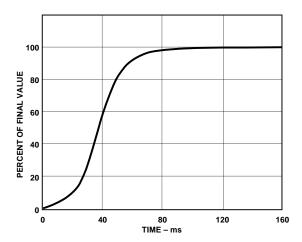

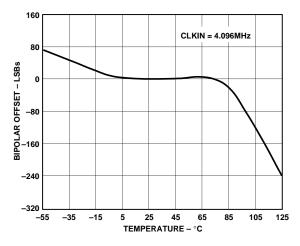

B Version<sup>2</sup> A/S Versions<sup>2</sup> C Version<sup>2</sup> Units **Test Conditions/Comments** Parameter STATIC PERFORMANCE 20 20 Resolution Bits Integral Nonlinearity,  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$  $\pm 0.0015$  $\pm 0.0007$  $\pm 0.0003$ % FSR typ  $\pm 0.003$ ±0.0015  $\pm 0.0008$ % FSR max +25°C  $T_{MIN}$  to  $T_{MAX}$  Differential Nonlinearity,  $T_{MIN}$  to  $T_{MAX}$  $\pm 0.0012$  $\pm 0.003$  $\pm 0.0015$ % FSR max  $\pm 0.5$  $\pm 0.5$  $\pm 0.5$ LSB typ Guaranteed No Missing Codes Positive Full-Scale Error<sup>3</sup>  $\pm 4$  $\pm 4$  $\pm\,4$ LSB typ LSB max  $\pm 16$  $\pm 16$  $\pm 16$ Full-Scale Drift<sup>4</sup>  $\pm 19/\pm 37$  $\pm\,19$ LSB typ  $\pm 19$ Unipolar Offset Error<sup>3</sup> LSB typ  $\pm 4$  $\pm 4$  $\pm 4$  $\pm\,16$  $\pm\,16$ LSB max  $\pm 16$ Unipolar Offset Drift<sup>4</sup> Temp Range: 0°C to +70°C  $\pm 26$  $\pm 26$  $\pm\,26$ LSB typ  $\pm 67 + 48/-400$  $\pm 67$  $\pm 67$ LSB typ Specified Temp Range Bipolar Zero Error<sup>3</sup> LSB typ  $\pm 4$  $\pm 4$  $\pm 4$  $\pm\,16$ LSB max  $\pm 16$  $\pm 16$ LSB typ Bipolar Zero Drift<sup>4</sup>  $\pm 13$  $\pm 13$  $\pm 13$ Temp Range: 0°C to +70°C  $\pm 34 + 24/-200$  $\pm 34$  $\pm 34$ LSB typ Specified Temp Range Bipolar Negative Full-Scale Errors<sup>3</sup> ±8  $\pm 8$ LSB typ  $\pm 8$ LSB max  $\pm 32$  $\pm 32$  $\pm 32$ Bipolar Negative Full-Scale Drift<sup>4</sup>  $\pm\,10/\pm\,20$ LSB typ  $\pm 10$  $\pm\,10$ Noise (Referred to Output) 1.6 1.6 1.6 LSB rms typ DYNAMIC PERFORMANCE  $f_{CLKIN}/256\,$  $f_{CLKIN}/256$  $f_{CLKIN}/256\,$ Hz Sampling Frequency, f<sub>S</sub> Output Update Rate, f<sub>OUT</sub>  $f_{CLKIN}/1024$  $f_{CLKIN}/1024$  $f_{CLKIN}/1024$ Hzf<sub>CLKIN</sub>/409,600  $f_{\text{CLKIN}}/409,600$  $f_{CLKIN}/409,600$ Filter Corner Frequency, f-3 dB Hz Settling Time to  $\pm 0.0007\%$  FS  $507904/f_{CLKIN}$  $507904/f_{CLKIN}$  $507904/f_{CLKIN}$ For Full-Scale Input Step sec SYSTEM CALIBRATION Positive Full-Scale Calibration Range  $V_{REF} + 0.1$  $V_{REF} + 0.1$  $V_{REF} + 0.1$ V max System Calibration Applies to Positive Full-Scale Overrange  $V_{REF} + 0.1$  $V_{REF} + 0.1$  $V_{REF} + 0.1$ Unipolar and Bipolar Ranges. V max Negative Full-Scale Overrange  $-(V_{RFF} + 0.1)$  $-(V_{RFF} + 0.1)$  $-(V_{RFF} + 0.1)$ V max After Calibration, if  $A_{IN} > V_{RFF}$ , Maximum Offset Calibration Ranges<sup>5, 1</sup> the Device Will Output All 1s. Unipolar Input Range  $-(V_{REF} + 0.1)$  $-(V_{REF} + 0.1)$  $-(V_{REF} + 0.1)$ V max If  $A_{IN} < 0$  (Unipolar) or  $-V_{REF}$ Bipolar Input Range -0.4 V<sub>REF</sub> to +0.4 V<sub>REF</sub>  $-0.4~V_{REF}$  to  $+0.4~V_{REF}$ –0.4  $V_{REF}$  to +0.4  $V_{REF}$ (Bipolar), the Device Will V max Input Span<sup>7</sup>  $0.8 V_{REF}$  $0.8 V_{REF}$  $0.8\;V_{\text{REF}}$ V min Output all 0s  $2 V_{REF} + 0.2$  $2 V_{REF} + 0.2$  $2\ V_{REF}+0.2$ V max ANALOG INPUT 0 to +2.5 0 to +2.5 0 to +2.5 Volts Unipolar Input Range Bipolar Input Range  $\pm 2.5$  $\pm 2.5$ Volts  $\pm 2.5$ Input Capacitance 20 20 20 pF typ Input Bias Current1 1 1 1 nA typ LOGIC INPUTS All Inputs except CLKIN 0.8 V max VINL, Input Low Voltage 0.8 0.8 V<sub>INH</sub>, Input High Voltage 2.0 2.0 2.0 V min CLKIN V<sub>INL</sub>, Input Low Voltage 0.8 0.8 0.8 V max V<sub>INH</sub>, Input High Voltage 3.5 3.5 3.5 V min I<sub>IN</sub>, Input Current 10 10 10 μA max LOGIC OUTPUTS V<sub>OL</sub>, Output Low Voltage 0.40.4 0.4V max  $I_{SINK} = 1.6 \text{ mA}$ V<sub>OH</sub>, Output High Voltage DV<sub>DD</sub> -1  $DV_{DD} - 1$  $DV_{DD} - 1$ V min  $I_{SOURCE} = 100 \mu A$ Floating State Leakage Current  $\pm 10$  $\pm 10$  $\pm 10$ μA max Floating State Output Capacitance pF typ POWER REQUIREMENTS Power Supply Voltages V min/V max | For Specified Performance Analog Positive Supply (AV<sub>DD</sub>) 4.5/5.5 4.5/5.54.5/5.5 Digital Positive Supply (DV<sub>DD</sub>)  $4.5/AV_{\rm DD}$  $4.5/AV_{\rm DD}$  $4.5/AV_{\rm DD}$ V min/V max Analog Negative Supply (AV<sub>SS</sub>) -4.5/-5.5-4.5/-5.5-4.5/-5.5V min/V max -4.5/-5.5Digital Negative Supply (DV<sub>SS</sub>) -4.5/-5.5-4.5/-5.5V min/V max Calibration Memory Retention

2.0

2.0

2.0

V min

Power Supply Voltage

| Parameter                                   | A/S Versions <sup>2</sup> | B Version <sup>2</sup> | C Version <sup>2</sup> | Units   | <b>Test Conditions/Comments</b>              |

|---------------------------------------------|---------------------------|------------------------|------------------------|---------|----------------------------------------------|

| STATIC PERFORMANCE                          |                           |                        |                        |         |                                              |

| DC Power Supply Currents <sup>8</sup>       |                           |                        |                        |         |                                              |

| Analog Positive Supply (AI <sub>DD</sub> )  | 3.2                       | 3.2                    | 3.2                    | mA max  | Typically 2 mA                               |

| Digital Positive Supply (DI <sub>DD</sub> ) | 1.5                       | 1.5                    | 1.5                    | mA max  | Typically 1 mA                               |

| Analog Negative Supply (AI <sub>SS</sub> )  | 3.2                       | 3.2                    | 3.2                    | mA max  | Typically 2 mA                               |

| Digital Negative Supply (DI <sub>SS</sub> ) | 0.1                       | 0.1                    | 0.1                    | mA max  | Typically 0.03 mA                            |

| Power Supply Rejection <sup>9</sup>         |                           |                        |                        |         |                                              |

| Positive Supplies                           | 70                        | 70                     | 70                     | dB typ  |                                              |

| Negative Supplies                           | 75                        | 75                     | 75                     | dB typ  |                                              |

| Power Dissipation                           |                           |                        |                        | 31      |                                              |

| Normal Operation                            | 40                        | 40                     | 40                     | mW rnax | $\overline{\text{SLEEP}} = \text{Logic } 1,$ |

| •                                           |                           |                        |                        |         | Typically 25 mW                              |

| Standby Operations <sup>10</sup>            |                           |                        |                        |         | $\overline{\text{SLEEP}}$ = Logic 0,         |

| A, B, C                                     | 20                        | 20                     | 20                     | μW max  | Typically 10 µW                              |

| S                                           | 40                        | 40                     | 40                     | μW max  |                                              |

#### NOTES

#### ABSOLUTE MAXIMUM RATINGS\*

| $(T_A =$ | +25°C | unless otherwise noted) |

|----------|-------|-------------------------|

| DI       |       | CNID                    |

| DV ACND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathrm{DV}_{\mathrm{DD}}$ to AGND0.3 V to +6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $DV_{DD}$ to $AV_{DD}$ 0.3 V to +0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $DV_{SS}$ to AGND $$ +0.3 V to -6 V $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $AV_{DD}$ to $AGND$ 0.3 V to +6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AV <sub>SS</sub> to AGND+0.3 V to -6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AGND to DGND0.3 V to +0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Digital Input Voltage to DGND $\dots$ -0.3 V to DV <sub>DD</sub> + 0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Analog Input Voltage to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Current to Any Pin Except Supplies $1 	cdots 	cdots$ |

| Operating Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Industrial (A, B, C Versions)40°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Extended (S Version)55°C to +125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Storage Temperature Range65°C to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Lead Temperature (Soldering, 10 secs) +300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power Dissipation (DIP Package) to +75°C 450 mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Derates above +75°C by 10 mW/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power Dissipation (SOIC Package) to +75°C 250 mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Derates above +75°C by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Nomes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### NOTES

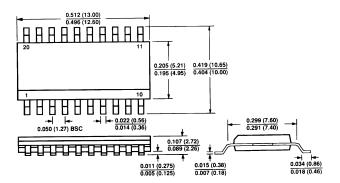

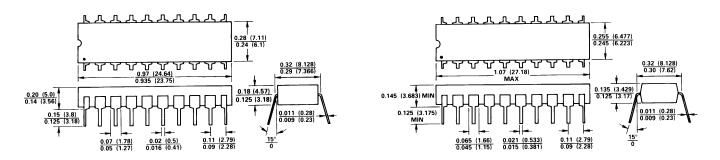

ORDERING GUIDE

| Model    | Temperature<br>Range | Linearity<br>Error<br>(% FSR) | Package<br>Options* |

|----------|----------------------|-------------------------------|---------------------|

| AD7703AN | -40°C to +85°C       | 0.003                         | N-20                |

| AD7703BN | -40°C to +85°C       | 0.0015                        | N-20                |

| AD7703CN | -40°C to +85°C       | 0.0012                        | N-20                |

| AD7703AR | -40°C to +85°C       | 0.003                         | R-20                |

| AD7703BR | -40°C to +85°C       | 0.0015                        | R-20                |

| AD7703CR | -40°C to +85°C       | 0.0012                        | R-20                |

| AD7703AQ | -40°C to +85°C       | 0.003                         | Q-20                |

| AD7703BQ | -40°C to +85°C       | 0.0015                        | Q-20                |

| AD7703CQ | -40°C to +85°C       | 0.0012                        | Q-20                |

| AD7703SQ | -55°C to +125°C      | 0.003                         | Q-20                |

<sup>\*</sup>N = Plastic DIP; R = SOIC; Q = Cerdip.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this device features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

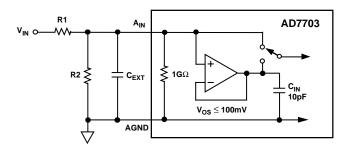

<sup>&</sup>lt;sup>1</sup>The  $A_{IN}$  pin presents a very high impedance dynamic load which varies with clock frequency. A ceramic 1 nF capacitor from the  $A_{IN}$  to AGND is necessary. Source resistance should be 750 Ω or less.

<sup>&</sup>lt;sup>2</sup>Temperature Ranges are as follows: A, B, C Versions: -40°C to +85°C; S Version: -55°C to +125°C.

<sup>&</sup>lt;sup>3</sup>Applies after calibration at the temperature of interest. Full-Scale Error applies for both unipolar and bipolar input ranges.

<sup>&</sup>lt;sup>4</sup>Total drift over the specified temperature range after calibration at power-up at +25 °C. This is guaranteed by design and/or characterization. Recalibration at any temperature will remove these errors.

$<sup>^{5}</sup>$ In unipolar mode the offset can have a negative value ( $-V_{REF}$ ) such that the unipolar mode can mimic bipolar mode operation.

<sup>&</sup>lt;sup>6</sup>The specifications for input overrange and for input span apply additional constraints on the offset calibration range.

<sup>&</sup>lt;sup>7</sup>For unipolar mode, input span is the difference between full scale and zero scale. For bipolar mode, input span is the difference between positive and negative full-scale points. When using less than the maximum input span, the span range may be placed anywhere within the range of  $\pm (V_{REF} + 0.1)$ .

<sup>&</sup>lt;sup>8</sup>All digital outputs unloaded. All digital inputs at 5 V CMOS levels.

<sup>&</sup>lt;sup>9</sup>Applies in 0.1 Hz to 10 Hz bandwidth. PSRR at 60 Hz will exceed 120 dB due to the digital filter.

<sup>&</sup>lt;sup>10</sup>CLKIN is stopped. All digital inputs are grounded.

Specifications subject to change without notice.

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1</sup>Transient currents of up to 100 mA will not cause SCR latch-up.

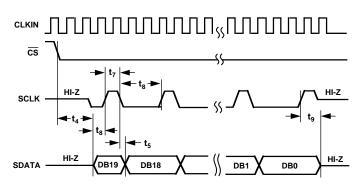

## TIMING CHARACTERISTICS<sup>1</sup>, 2 (AV<sub>DD</sub> = DV<sub>DD</sub> = +5 V $\pm$ 10%; AV<sub>SS</sub> = DV<sub>SS</sub> = -5 V $\pm$ 10%; AGND = DGND = 0 V; f<sub>CLKIN</sub> = 4.096 MHz; Input Levels: Logic 0 = 0 V, Logic 1 = DV<sub>DD</sub>; unless otherwise noted.)

| Parameter                                     | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (A, B, C Versions) | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (S Version) | Units   | Conditions/Comment <sup>6</sup>                                    |

|-----------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|---------|--------------------------------------------------------------------|

| f <sub>CLKIN</sub> <sup>3, 4</sup>            | 200                                                             | 200                                                      | kHz min | Master Clock Frequency: Internal Gate Oscillator                   |

|                                               | 5                                                               | 5                                                        | MHz max | Typically 4096 kHz                                                 |

|                                               | 200                                                             | 200                                                      | kHz min | Master Clock Frequency: Externally Supplied                        |

|                                               | 5                                                               | 5                                                        | MHz max |                                                                    |

| $t_{\mathrm{r}}^{5} \ t_{\mathrm{f}}^{5}$     | 50                                                              | 50                                                       | ns max  | Digital Output Rise Time. Typically 20 ns                          |

| $t_f^5$                                       | 50                                                              | 50                                                       | ns max  | Digital Output Fall Time. Typically 20 ns                          |

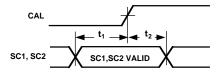

| $t_1$                                         | 0                                                               | 0                                                        | ns min  | SC1, SC2 to CAL High Setup Time                                    |

| $t_2$                                         | 50                                                              | 50                                                       | ns min  | SC1, SC2 Hold Time After CAL Goes High                             |

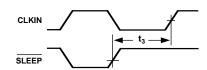

| t <sub>2</sub><br>t <sub>3</sub> <sup>6</sup> | 1000                                                            | 1000                                                     | ns min  | SLEEP High to CLKIN High Setup Time                                |

| SSC MODE                                      |                                                                 |                                                          |         |                                                                    |

| ${\mathsf t_4}^7$                             | 3/f <sub>CLKIN</sub>                                            | 3/f <sub>CLKIN</sub>                                     | ns max  | Data Access Time (CS Low to Data Valid)                            |

| $t_5$                                         | 100                                                             | 100                                                      | ns max  | SCLK Falling Edge to Data Valid Delay (25 ns typ)                  |

| $t_6$                                         | 250                                                             | 250                                                      | ns min  | MSB Data Setup Time. Typically 380 ns                              |

| $t_7$                                         | 300                                                             | 300                                                      | ns max  | SCLK High Pulse Width. Typically 240 ns                            |

| t <sub>8</sub>                                | 790                                                             | 790                                                      | ns max  | SCLK Low Pulse Width. Typically 730 ns                             |

| $t_9$                                         | $1/f_{CLKIN} + 200$                                             | $l/f_{CLKIN} + 200$                                      | ns max  | SCLK Rising Edge to Hi-Z Delay (1/f <sub>CLKIN</sub> + 100 ns typ) |

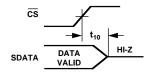

| t <sub>10</sub> 8, 9                          | $4/f_{CLKIN} + 200$                                             | $4/f_{\text{CLKIN}} + 200$                               | ns max  | CS High to Hi-Z Delay                                              |

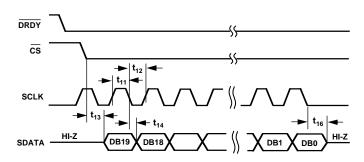

| SEC MODE                                      |                                                                 |                                                          |         |                                                                    |

| $f_{SCLK}$                                    | 5                                                               | 5                                                        | MHz max | Serial Clock Input Frequency                                       |

| t <sub>11</sub>                               | 35                                                              | 35                                                       | ns min  | SCLK High Pulse Width                                              |

| t12                                           | 160                                                             | 160                                                      | ns min  | SCLK Low Pulse Width                                               |

| $t_{13}^{7, 10}$                              | 160                                                             | 160                                                      | ns max  | Data Access Time (CS Low to Data Valid). Typically 80 ns           |

| $t_{14}^{11}$                                 | 150                                                             | 150                                                      | ns max  | SCLK Falling Edge to Data Valid Delay. Typically 75 ns             |

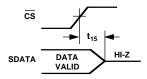

| t <sub>15</sub> 8                             | 250                                                             | 250                                                      | ns max  | S High to Hi-Z Delay                                               |

| $t_{16}^{8}$                                  | 200                                                             | 200                                                      | ns max  | SCLK Falling Edge to Hi-Z Delay. Typically 100 ns                  |

#### NOTES

<sup>&</sup>lt;sup>11</sup>SDATA is clocked out on the falling edge of the SCLK input.

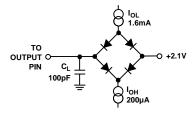

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

Figure 2. Calibration Control Timing

Figure 3. Sleep Mode Timing

<sup>&</sup>lt;sup>1</sup>Sample tested at  $+25^{\circ}$ C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V. <sup>2</sup>See Figures 1 to 6.

<sup>&</sup>lt;sup>3</sup>CLKIN duty cycle range is 20% to 80%. CLKIN must be supplied whenever the AD7703 is not in SLEEP mode. If no clock is present in this case, the device can draw higher current than specified and possibly become uncalibrated.

$<sup>^4</sup>$ The AD7703 is production tested with  $f_{CLKIN}$  at 4.096 MHz. It is guaranteed by characterization to operate at 200 kHz.

<sup>&</sup>lt;sup>5</sup>Specified using 10% and 90% points on waveform of interest.

<sup>&</sup>lt;sup>6</sup>In order to synchronize several AD7703s together using the SLEEP pin, this specification must be met.

$<sup>^{7}</sup>$ t<sub>4</sub> and t<sub>13</sub> are measured with the load circuit of Figure 1 and defined as the time required for an output to cross 0.8 V or 2.4 V.

<sup>&</sup>lt;sup>8</sup>t<sub>9</sub>, t<sub>10</sub>, t<sub>15</sub> and t<sub>16</sub> are derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the tune quoted in the Timing Characteristics is the true bus relinquish time of the part and as such is independent of external bus loading capacitances.

<sup>9</sup>If CS is returned high before all 20 bits are output, the SDATA and SCLK outputs will complete the current data bit and then go to high impedance.

$<sup>^{10}</sup>$ If  $\overline{\text{CS}}$  is activated asynchronously to  $\overline{\text{DRDY}}$ ,  $\overline{\text{CS}}$  will not be recognized if it occurs when  $\overline{\text{DRDY}}$  is high for four clock cycles. The propagation delay time may be as great as 4 CLKIN cycles plus 160 ns. To guarantee proper clocking of SDATA when using asynchronous  $\overline{\text{CS}}$ , the SCLK input should not be taken high sooner than 4 CLKIN cycles plus 160 ns after  $\overline{\text{CS}}$  goes low.

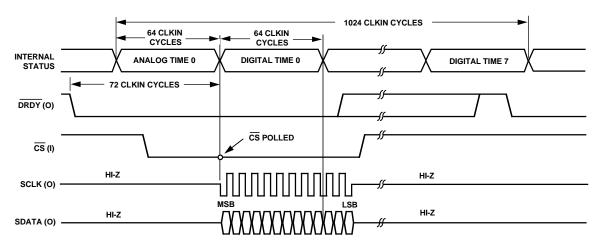

Figure 4. SSC Mode Data Hold Time

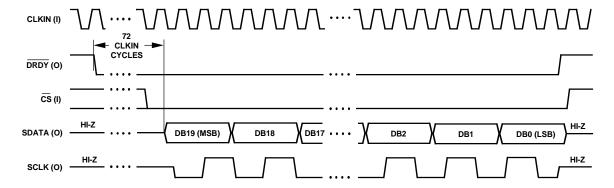

Figure 5b. SEC Mode Timing Diagram

#### TERMINOLOGY LINEARITY ERROR

This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero-scale (not to be confused with bipolar zero), a point 0.5 LSB below the first code transition  $(000\dots000\ to\ 000\dots001)$  and full scale, a point 1.5 LSB above the last code transition  $(111\dots110\ to\ 111\dots111)$ . The error is expressed as a percentage of full scale.

#### DIFFERENTIAL LINEARITY ERROR

This is the difference between any code's actual width and the ideal (1 LSB) width. Differential linearity error is expressed in LSBs. A differential linearity specification of  $\pm 1$  LSB or less guarantees monotonicity.

#### POSITIVE FULL-SCALE ERROR

Positive full-scale error is the deviation of the last code transition (111 . . . 110 to 111 . . . 111) from the ideal ( $V_{REF}$  –3/2 LSBs). It applies to both positive and negative analog input ranges.

#### UNIPOLAR OFFSET ERROR

Unipolar offset error is the deviation of the first code transition from the ideal (AGND  $\pm$  0.5 LSB) when operating in the unipolar mode.

#### **BIPOLAR ZERO ERROR**

This is the deviation of the midscale transition (0111  $\dots$  111 to 1000  $\dots$  000) from the ideal (AGND – 0.5 LSB) when operating in the bipolar mode.

#### BIPOLAR NEGATIVE FULL-SCALE ERROR

This is the deviation of the first code transition from the ideal  $(-V_{REF} + 0.5 \text{ LSB})$ , when operating in the bipolar mode.

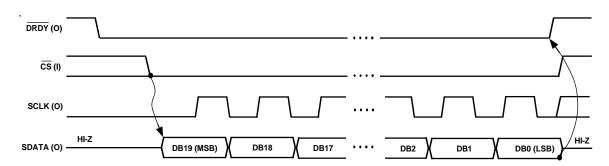

Figure 5a. SEC Mode Data Hold Time

Figure 6. SSC Mode Timing Diagram

#### POSITIVE FULL-SCALE OVERRANGE

Positive full-scale overrange is the amount of overhead available to handle input voltages greater than  $+V_{\rm REF}$  (for example, noise peaks or excess voltages due to system gain errors in system calibration routines) without introducing errors due to overloading the analog modulator or overflowing the digital filter.

#### **NEGATIVE FULL-SCALE OVERRANGE**

This is the amount of overhead available to handle voltages below  $-V_{\rm REF}$  without overloading the analog modulator or overflowing the digital filter. Note that the analog input will accept negative voltage peaks even in the unipolar mode.

#### OFFSET CALIBRATION RANGE

In the system calibration modes (SC2 Low) the AD7703 calibrates its offset with respect to the  $A_{\rm IN}$  pin. The offset calibration range specification defines the range of voltages that the AD7701 can accept and still calibrate offset accurately.

#### FULL-SCALE CALIBRATION RANGE

This is the range of voltages that the AD7703 can accept in the system calibration mode and still calibrate full scale correctly.

#### **INPUT SPAN**

In system calibration schemes, two voltages applied in sequence to the AD7703's analog input define the analog input range. The input span specification defines the minimum and maximum input voltages from zero to full scale that the AD7703 can accept and still calibrate gain accurately.

#### PIN FUNCTION DESCRIPTION

| Pin   | Mnemonic                    | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | MODE                        | Selects the Serial Interface Mode. If MODE is tied to DGND, the Synchronous External Clocking (SEC) mode is selected. SCLK is configured as an input, and the output appears without formatting, the MSB coming first. If MODE is tied to $+5$ V, the AD7703 operates in the Synchronous Self-Clocking (SSC) mode. SCLK is configured as an output, with a clock frequency for $f_{CLKIN}/4$ and 25% duty cycle. |

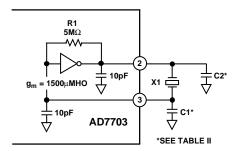

| 2     | CLKOUT                      | Clock Output to generate an Internal Master Clock by connecting a crystal between CLKOUT and CLKIN. If an external clock is used, CLKOUT is not connected.                                                                                                                                                                                                                                                       |

| 3     | CLKIN                       | Clock Input for External Clock.                                                                                                                                                                                                                                                                                                                                                                                  |

| 4, 17 | SC1, SC2                    | System Calibration Pins. The state of these pins, when CAL is taken high, determines the type of calibration performed.                                                                                                                                                                                                                                                                                          |

| 5     | DGND                        | Digital Ground. Ground reference for all digital signals.                                                                                                                                                                                                                                                                                                                                                        |

| 6     | $DV_{SS}$                   | Digital Negative Supply, -5 V nominal.                                                                                                                                                                                                                                                                                                                                                                           |

| 7     | $AV_{SS}$                   | Analog Negative Supply, -5 V nominal.                                                                                                                                                                                                                                                                                                                                                                            |

| 8     | AGND                        | Analog Ground. Ground reference for all analog signals.                                                                                                                                                                                                                                                                                                                                                          |

| 9     | $A_{\rm IN}$                | Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10    | $ m V_{REF}$                | Voltage Reference Input, +2.5 V nominal. This determines the value of positive full-scale in the unipolar mode and of both positive and negative full-scale in the Bipolar Mode.                                                                                                                                                                                                                                 |

| 11    | SLEEP                       | Sleep mode pin. When this pin is taken low, the AD7703 goes into a low-power mode with typically $10\mu\text{W}$ power consumption.                                                                                                                                                                                                                                                                              |

| 12    | BP/ <del>UP</del>           | Bipolar/Unipolar mode pin. When this pin is Low, the AD7703 is configured for a unipolar input range going from AGND to $V_{REF}$ . When Pin 12 is High, the AD7703 is configured for a bipolar input range, $\pm V_{REF}$ .                                                                                                                                                                                     |

| 13    | CAL                         | Calibration mode pin. When CAL is taken High for more than 4 cycles, the AD7703 is reset and performs a calibration cycle when CAL is brought Low again. The CAL pin can also be used as a strobe to synchronize the operation of several AD7703s.                                                                                                                                                               |

| 14    | $AV_{DD}$                   | Analog Positive Supply, +5 V nominal.                                                                                                                                                                                                                                                                                                                                                                            |

| 15    | $\mathrm{DV}_{\mathrm{DD}}$ | Digital Positive Supply, +5 V nominal.                                                                                                                                                                                                                                                                                                                                                                           |

| 16    | CS                          | Chip Select Input. When $\overline{\text{CS}}$ is brought low, the AD7703 will begin to transmit serial data in a format determined by the state of the MODE pin.                                                                                                                                                                                                                                                |

| 18    | DRDY                        | Data Ready Output. $\overline{DRDY}$ is low when valid data is available in the output register. It goes high after transmission of a word is completed. It also goes high for four clock cycles when a new data word is being loaded into the output register, to indicate that valid data is not available, irrespective of whether data transmission is complete or not.                                      |

| 19    | SCLK                        | Serial Clock Input/Output. The SCLK pin in configured as an input or output, dependent on the type of serial data transmission that has been selected by the MODE pin. When configured as an output in the Synchronous Self-Clocking mode, it has a frequency of $f_{CLKIN}/4$ and a duty cycle of 25%.                                                                                                          |