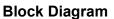

- Fast rise and fall times for frequencies up to 2 MHz

- Capable of sinking more than 4 A peak current for lowest switching losses

- Charges the High Side and Low Side MOSFET's gate to 6..12 V according to PVCC setting.

- Adjustable High Side and Low Side MOSFET gate drive voltage via PVCC pin for optimizing ON losses and gate drive losses

- Integrates the bootstrap diode for reducing the part count

- Prevents from cross-conducting by adaptive gate drive control

- High voltage rating on Phase node

- Supports shut-down mode for very low quiescent current through three-state input

- Compatible to standard PWM controller ICs (Intersil, Analog Devices)

- Floating High Side MOSFET drive

- Ideal for multi-phase Desktop CPU supplies on motherboards and VRM's

| Туре     | Package    | Marking | Ordering Code |

|----------|------------|---------|---------------|

| TDA21102 | P-DSO-14-3 | 21102   | Q67042-S4244  |

|                            |          |                                    | Number | Name                | Description                                                                                                                                                  |

|----------------------------|----------|------------------------------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Discut   |                                    | 1      | PWM1                | Input for the PWM1 controller signal                                                                                                                         |

|                            | Pinout   |                                    | 2      | PWM2                | Input for the PWM2 controller signal                                                                                                                         |

|                            |          |                                    | 3      | GND                 | Ground                                                                                                                                                       |

|                            |          |                                    | 4      | GATE <sub>LS1</sub> | Gate drive output for the N-Channel Low Side MOSFET 1.                                                                                                       |

|                            | Top View |                                    | 5      | PVCC                | Input to adjust the High Side gate drive                                                                                                                     |

|                            |          |                                    | 6      | PGND                | Power ground return for the Low Side Drivers                                                                                                                 |

| PWM1                       |          | 14 VCC                             | 7      | GATE <sub>LS2</sub> | Gate drive output for the N-Channel Low Side MOSFET 2.                                                                                                       |

|                            |          | E .                                | 8      | PHASE2              | To be connected to the junction of the High<br>Side and the Low Side MOSFET 2                                                                                |

| PWM2                       | 2        | 13PHASE1                           | 9      | GATE <sub>HS2</sub> | Gate drive output for the N-Channel High Side<br>MOSFET 2.                                                                                                   |

| GND<br>GATE <sub>LS1</sub> | 3        | 12 GATE <sub>HS1</sub><br>11 BOOT1 | 10     | BOOT2               | Floating bootstrap pin. To be connected to the<br>external bootstrap capacitor to generate the<br>gate drive voltage for the High Side N-Channe<br>MOSFET 2. |

| PVCC<br>PGND               | 5        | 10 BOOT2                           | 11     | BOOT1               | Floating bootstrap pin. To be connected to the<br>external bootstrap capacitor to generate the<br>gate drive voltage for the High Side N-Channe<br>MOSFET 1. |

| )                          |          |                                    | 12     | GATE <sub>HS1</sub> | Gate drive output for the N-Channel High Side<br>MOSFET 1.                                                                                                   |

| tt GATEBY                  |          | 8 PHASE2                           | 13     | PHASE1              | To be connected to the junction of the High Side and the Low Side MOSFET 1                                                                                   |

| / KE-                      |          |                                    | 14     | VCC                 | Supply Voltage                                                                                                                                               |

Rev. 1.0

#### **General Description**

The dual high speed driver is designed to drive a wide range of N-Channel low side and N-Channel high side MOSFETs with varying gate charges. It has a small propagation delay from input to output, short rise and fall times and the same pin configuration as the HIP6602B. In addition it provides several protection features as well as a shut down mode for efficiency reasons. The high breakdown voltage makes it suitable for mobile applications.

#### **Target application**

The dual high speed driver is designed to work well in half-bridge type circuits where dual N-Channel MOSFETs are utilized. A circuit designer can fully take advantage of the driver's capabilities in high-efficiency, high-density synchronous DC/DC converters that operate at high switching frequencies, e.g. in multi-phase converters for CPU supplies on motherboards and VRM's but also in motor drive and class-D amplifier type applications.

# Absolute Maximum Ratings At Tj = 25 °C, unless otherwise specified

| Parameter                                                                           | Symbol                                    | Va   | lue   | Unit |

|-------------------------------------------------------------------------------------|-------------------------------------------|------|-------|------|

|                                                                                     |                                           | Min. | Max.  |      |

| Voltage supplied to 'VCC' pin                                                       | V <sub>VCC</sub>                          | -0.3 | 25    |      |

| Voltage supplied to 'PVCC' pin                                                      | V <sub>PVCC</sub>                         | -0.3 | 25    | V    |

| Voltage supplied to 'PWM' pin                                                       | V <sub>PWM</sub>                          | -0.3 | 5.5   |      |

| Voltage supplied to 'BOOT' pin referenced to 'PHASE'                                | V <sub>BOOT</sub> –<br>V <sub>PHASE</sub> | -0.3 | 25    |      |

| Voltage rating at 'PHASE' pin, DC                                                   | $V_{PHASE}$                               | -1   | 25    |      |

| Voltage rating at 'PHASE' pin, t <sub>pulse_max</sub> =500ns<br>Max Duty Cycle = 2% |                                           | -20  | 30    |      |

| Junction temperature                                                                | TJ                                        | -25  | 150   | °C   |

| Storage temperature                                                                 | Ts                                        | -55  | 150   |      |

| ESD Rating; Human Body Model                                                        |                                           |      | 4     | kV   |

| IEC climatic category; DIN EN 60068-1                                               |                                           | 55/1 | 50/56 | -    |

#### **Thermal Characteristic**

| Parameter                            | Symbol | Values |       | Unit |     |

|--------------------------------------|--------|--------|-------|------|-----|

|                                      |        | Min.   | Тур.  | Max. |     |

| Thermal resistance, junction-case    | Rth-JC |        | 44,7  |      | K/W |

| Thermal resistance, junction-ambient | Rth-JA |        | 116,2 |      |     |

#### **Electrical Characteristic**

At Tj = 25 °C, unless otherwise specified

| Parameter             | Symbol                       | Conditions                         |      | Values | 5    | Unit |

|-----------------------|------------------------------|------------------------------------|------|--------|------|------|

|                       | -                            |                                    | Min. | Тур.   | Max. |      |

| Supply Characteristic | ;                            |                                    |      |        |      |      |

| Bias supply current   | I <sub>VCC</sub>             | f = 1 MHz,                         |      |        |      |      |

|                       |                              | NO LOAD                            |      | 0.95   | 1.65 |      |

|                       |                              | $V_{PVCC} = V_{VCC} = 12 V$        |      |        |      |      |

| Quiescent current     | Ivccq                        | $1.8~V \leq V_{PWM} \leq 3.0~V$    |      | 0.75   | 3    | mA   |

| Power supply current  | I <sub>PVCC</sub>            | f = 1 MHz,                         |      |        |      |      |

|                       |                              | NO LOAD                            |      | 26     |      |      |

|                       |                              | $V_{PVCC} = V_{VCC} = 12 V$        |      |        |      |      |

| Under-voltage lockout |                              | V <sub>VCC</sub> rising threshold  | 9.7  | 10.1   | 10.5 | V    |

| Under-voltage lockout |                              | V <sub>VCC</sub> falling threshold | 7.3  | 7.6    | 8.0  | V    |

| Input Characteristic  |                              |                                    |      |        |      |      |

| Current in 'PWM' pin  | I <sub>PWM L</sub>           | V <sub>PWM</sub> = 0.4 V           | -80  | 115    | -150 | μA   |

| Current in 'PWM' pin  | I <sub>PWM_H</sub>           | V_PWM = 4.5 V                      | 120  | 180    | 250  |      |

| Shut down window      | $V_{\text{IN}\_\text{SHUT}}$ | t_ <sub>SHUT</sub> > 320 ns        | 1.7  |        | 3.1  | V    |

| Shut down hold-off    | t_ <sub>SHUT</sub>           | $1.7 V \le V_{PWM} \le 3.1 V$      | 100  | 230    | 350  | ns   |

| time                  |                              |                                    |      |        |      |      |

| PWM pin open          | V <sub>PWM O</sub>           |                                    | 1.8  | 2.0    | 2.2  |      |

## TDA21102

| PWM Low level<br>threshold (falling) | $V_{PWM\_L}$       |                         | 1.45 | 1.55 |     | V  |

|--------------------------------------|--------------------|-------------------------|------|------|-----|----|

| PWM High level                       | V <sub>PWM H</sub> |                         |      | 3.45 | 3.6 | v  |

| threshold (rising)                   |                    |                         |      |      |     |    |

| Pulse Width High                     | t_p                | = Pulse with on PWM pin | 40   |      |     | ns |

| Side                                 |                    |                         |      |      |     |    |

At Tj = 25 °C, unless otherwise specified

| Dynamic Characteristic |                       |                             |  |    |    |    |  |

|------------------------|-----------------------|-----------------------------|--|----|----|----|--|

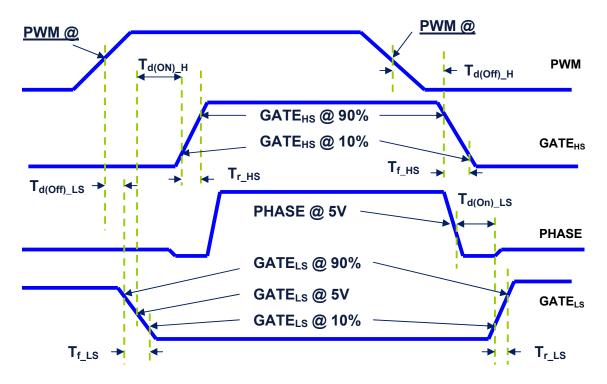

| Turn-on propagation    | t <sub>d(ON)_HS</sub> |                             |  | 27 | 35 |    |  |

| Delay High Side*       |                       |                             |  |    |    |    |  |

| Turn-off propagation   | $t_{d(OFF)_HS}$       |                             |  | 16 | 21 |    |  |

| delay High Side        |                       |                             |  |    |    |    |  |

| Rise time High Side    | t <sub>r_HS</sub>     |                             |  | 20 | 25 |    |  |

| Fall time High Side    | t <sub>f HS</sub>     | $P_{PVCC} = V_{VCC} = 12 V$ |  | 11 | 20 | ns |  |

| Turn-on propagation    | $t_{d(ON)}$ LS        | C <sub>ISS</sub> = 3000 pF  |  | 20 | 23 |    |  |

| Delay Low Side         |                       |                             |  |    |    |    |  |

| Turn-off propagation   | $t_{d(OFF)_LS}$       |                             |  | 13 | 20 |    |  |

| delay Low Side         |                       |                             |  |    |    |    |  |

| Rise time Low Side     | t <sub>r LS</sub>     |                             |  | 22 | 25 |    |  |

| Fall time Low Side     | t <sub>f LS</sub>     |                             |  | 13 | 20 |    |  |

#### Measurement Timing diagram

**Operating Conditions** At Tj = 25 °C, unless otherwise specified

| Parameter                         | Symbol            | Conditions                                      | Values |      |      | Unit |

|-----------------------------------|-------------------|-------------------------------------------------|--------|------|------|------|

|                                   | _                 |                                                 | Min.   | Тур. | Max. |      |

| Voltage supplied to<br>'VCC' pin  | V <sub>VCC</sub>  |                                                 | 10.8   |      | 13.2 | V    |

| Voltage supplied to<br>'PVCC' pin | V <sub>PVCC</sub> |                                                 | 6      |      | 13.2 | V    |

| Input signal transition frequency | f                 |                                                 | 0.1    |      | 2    | MHz  |

| Power dissipation                 | P <sub>TOT</sub>  | T <sub>A</sub> = 25 °C, T <sub>J</sub> = 125 °C |        | 0.9  |      | W    |

| Junction temperature              | TJ                |                                                 | -25    |      | 150  | °C   |

#### At Tj = 25 °C, unless otherwise specified

| Param                                                   | eter       | Conditions                                   | ,      | Values  | ;      | Unit |

|---------------------------------------------------------|------------|----------------------------------------------|--------|---------|--------|------|

|                                                         |            |                                              | Min.   | Тур.    | Max.   |      |

| Output Characteristic High Side (HS) and Low Side (LS), |            |                                              | ensure | ed by d | lesign |      |

| Output                                                  | HS; Source | $P_{PVCC} = V_{VCC} = 12 V$                  |        | 1.2     |        | Ω    |

| Resistance                                              |            | $I_{HS_{SRC}} = 2 A$                         |        |         |        |      |

|                                                         | HS; Sink   | $P_{PVCC} = V_{VCC} = 12 V$                  |        | 1       | 1.5    | Ω    |

|                                                         | LS; Source | $P_{PVCC} = V_{VCC} = 12 V$                  |        | 1       |        | Ω    |

|                                                         |            | I <sub>HS SRC</sub> = 2 A                    |        |         |        |      |

|                                                         | LS; Sink   | $P_{PVCC} = V_{VCC} = 12 V$                  |        | 1       | 1.3    | Ω    |

|                                                         | HS; Source | $P_{PVCC} = V_{VCC} = 12 V$                  | 4      |         |        |      |

| Peak output-                                            | HS; Sink   | t_ <sub>P_HS</sub> / Pulse < 20 ns           | 4      |         |        | А    |

| current                                                 | LS; Source | t_ <sub>P_LS</sub> / Pulse < 40 ns           | 4      |         |        |      |

|                                                         | LS; Sink   | D_ <sub>HS</sub> < 2%, D_ <sub>LS</sub> < 4% | 4      |         |        |      |

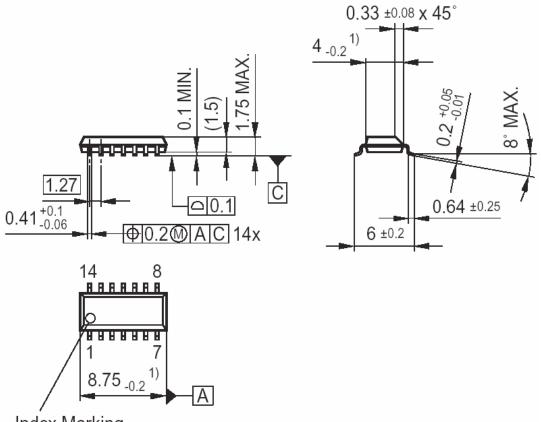

### Package Drawing P-DSO-14-3

Index Marking

<sup>1)</sup> Does not include plastic or metal protrusion of 0.15 max. per side

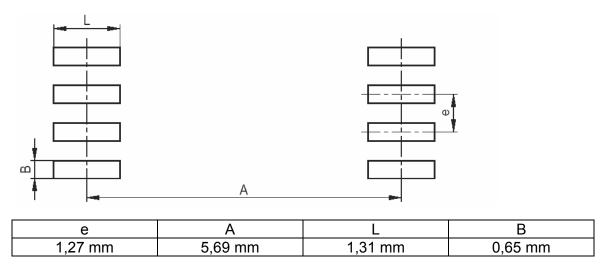

#### **Layout Footprints**

Published by Infineon Technologies AG, Bereichs Kommunikation St.-Martin-Strasse 53, D-81541 München © Infineon Technologies AG 1999 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.