查询DAC8043U供应商

# DAC8043

,24小时加急出货

# CMOS 12-Bit Serial Input Multiplying DIGITAL-TO-ANALOG CONVERTER

### **FEATURES**

- 12-BIT ACCURACY IN 8-PIN SOIC

- FAST 3-WIRE SERIAL INTERFACE

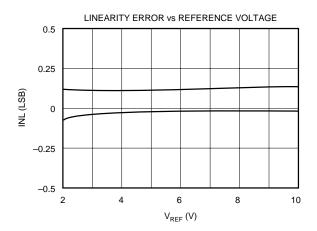

- LOW INL AND DNL: ±1/2 LSB max

- GAIN ACCURACY TO ±1LSB max

- LOW GAIN TEMPCO: 5ppm/°C max

- OPERATES WITH +5V SUPPLY

- TTL/CMOS COMPATIBLE

- ESD PROTECTED

# DESCRIPTION

The DAC8043 is a 12-bit current output multiplying digital-to-analog converter (DAC) that is packaged in a space-saving, surface-mount 8-pin SOIC. Its 3-wire serial interface saves additional circuit board space which results in low power dissipation. When used with micro-processors having a serial port, the DAC8043 minimizes the digital noise feedthrough from its input to output. The serial port can be used as a dedicated analog bus and kept inactive while the DAC8043 is in use. Serial interfacing reduces the complexity of opto or transformer isolation applications.

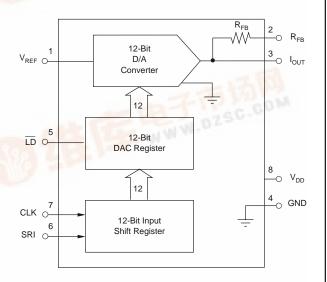

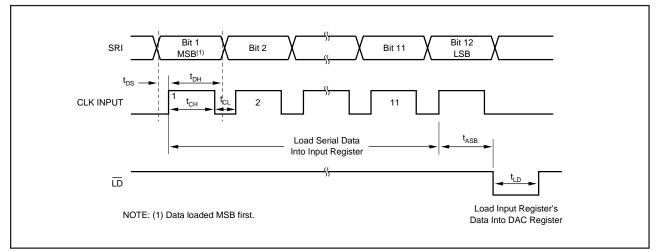

The DAC8043 contains a 12-bit serial-in, parallel-out shift register, a 12-bit DAC register, a 12-bit CMOS DAC, and control logic. Serial input (SRI) data is clocked into the input register on the rising edge of the clock (CLK) pulse. When the new data word had been clocked in, it is loaded into the DAC register by taking the  $\underline{LP}$  input low. Data in the DAC register is converted to an output current by the D/A converter.

The DAC8043 operates from a single +5V power supply which makes the DAC8043 an ideal low power, small size, high performance solution for several applications.

## APPLICATIONS

- AUTOMATIC CALIBRATION

- MOTION CONTROL

捷多邦, 专业PCB打样工厂

- MICROPROCESSOR CONTROL SYSTEMS

- PROGRAMMABLE AMPLIFIER/ ATTENUATORS

- DIGITALLY CONTROLLED FILTERS

nternational Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

#### ELECTRICAL CHARACTERISTICS

At  $V_{DD}$  = +5V;  $V_{REF}$  = +10V;  $I_{OUT}$  = GND = 0V;  $T_A$  = Full Temperature Range specified under Absolute Maximum Ratings, unless otherwise noted.

|                                                                                                                                                                                                                     |                                                                          |                                                                                                                                                                                                          | DAC8043U               |           | DAC8043UC                  |                                   |           |                                               |                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|----------------------------|-----------------------------------|-----------|-----------------------------------------------|----------------------------------|

| PARAMETER                                                                                                                                                                                                           | SYMBOL CONDITIONS                                                        |                                                                                                                                                                                                          | MIN                    | ТҮР       | MAX                        | MIN                               | TYP       | MAX                                           | UNITS                            |

| STATIC PERFORMANCE<br>Resolution                                                                                                                                                                                    | N                                                                        |                                                                                                                                                                                                          | 12                     |           |                            | 12                                |           |                                               | Bits                             |

| Nonlinearity <sup>(1)</sup><br>Differential Nonlinearity <sup>(2)</sup><br>Gain Error <sup>(3)</sup>                                                                                                                | INL<br>DNL<br>FSE                                                        | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp Range                                                                                                                                               |                        |           | ±1<br>±1<br>±2<br>±2       |                                   |           | ±1/2<br>±1/2<br>±1<br>±2                      | LSB<br>LSB<br>LSB<br>LSB         |

| Gain Tempco <sup>(5)</sup><br>Power Supply Rejection Ratio<br>Output Leakage Current <sup>(4)</sup>                                                                                                                 | TC <sub>FSE</sub><br>PSRR<br>I <sub>LKG</sub>                            | $\Delta V_{DD} = \pm 5\%$ $T_{A} = +25^{\circ}C$ $T_{A} = Full Temp Range$                                                                                                                               |                        | ±0.0006   | ±5<br>±0.002<br>±5<br>±100 |                                   | ±0.0006   | $\pm 5$<br>$\pm 0.002$<br>$\pm 5$<br>$\pm 25$ | ppm/°C<br>%/%<br>nA<br>nA        |

| Zero Scale Error <sup>(7, 12)</sup>                                                                                                                                                                                 | I <sub>ZSE</sub>                                                         | $T_A = +25^{\circ}C$<br>$T_A = Full Temp Range$                                                                                                                                                          |                        |           | 0.03<br>0.60               |                                   |           | 0.03<br>0.15                                  | LSB<br>LSB                       |

| Input Resistance <sup>(8)</sup>                                                                                                                                                                                     | R <sub>IN</sub>                                                          |                                                                                                                                                                                                          | 7                      | 11        | 15                         | 7                                 | 11        | 15                                            | kΩ                               |

| AC PERFORMANCE<br>Output Current Settling Time <sup>(5, 6)</sup><br>Digital-to-Analog Glitch                                                                                                                        | t <sub>s</sub>                                                           | $T_A = +25^{\circ}C$<br>$V_{REF} = 0V$                                                                                                                                                                   |                        | 0.25<br>2 | 1<br>20                    |                                   | 0.25<br>2 | 1<br>20                                       | μs<br>nVs                        |

| Energy <sup>(5, 10)</sup>                                                                                                                                                                                           | Q<br>AC Regist                                                           | $I_{OUT} = Load = 100\Omega$<br>$C_{EXT} = 13pF$<br>er Loaded Alternately with all 0                                                                                                                     | )s and all 1           | s         |                            |                                   |           |                                               |                                  |

| Feedthrough Error <sup>(5, 11)</sup> ( $V_{REF}$ to $I_{OUT}$ )                                                                                                                                                     | FT                                                                       | $V_{REF} = 20Vp-p \text{ at } f = 10kHz$<br>Digital Input = 0000 0000 0000<br>$T_{a} = +25^{\circ}C$                                                                                                     | )                      | 0.7       | 1                          |                                   | 0.7       | 1                                             | mVp-p                            |

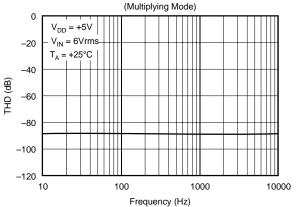

| Total Harmonic Distortion <sup>(5)</sup>                                                                                                                                                                            | THD                                                                      | $V_{REF} = 6V_{RMS}$ at 1kHz<br>DAC Register Loaded with all 1                                                                                                                                           | s                      | -85       |                            |                                   | -85       |                                               | dB                               |

| Output Noise Voltage Density <sup>(5, 13)</sup>                                                                                                                                                                     | e <sub>N</sub>                                                           | 10Hz to 100kHz Between $R_{\mbox{\tiny FB}}$ and $I_{\mbox{\tiny OUT}}$                                                                                                                                  |                        |           | 17                         |                                   |           | 17                                            | nV/√Hz                           |

| DIGITAL INPUTS<br>Digital Input High<br>Digital Input Low<br>Input Leakage Current <sup>(9)</sup><br>Input Capacitance <sup>(5, 11)</sup>                                                                           | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IL</sub><br>C <sub>IN</sub> | $V_{IN} = 0V$ to +5V<br>$V_{IN} = 0V$                                                                                                                                                                    | 2.4                    |           | 0.8<br>±1<br>8             | 2.4                               |           | 0.8<br>±1<br>8                                | ν<br>ν<br>μΑ<br>pF               |

| ANALOG OUTPUTS<br>Output Capacitance <sup>(5)</sup>                                                                                                                                                                 | C <sub>OUT</sub>                                                         | Digital Inputs = V <sub>IH</sub><br>Digital Inputs = V <sub>II</sub>                                                                                                                                     |                        |           | 110<br>80                  |                                   |           | 110<br>80                                     | pF<br>pF                         |

| TIMING CHARACTERISTICS <sup>(5, 14)</sup><br>Data Setup Time<br>Data Hold Time<br>Clock Pulse Width High<br>Clock Pulse Width Low<br>Load Pulse Width<br>LSB Clock into Input Register<br>to Load DAC Register Time |                                                                          | $T_A = Full Temperature Range$<br>$T_A = Full Temperature Range$ | 80<br>90<br>120<br>120 |           |                            | 40<br>80<br>90<br>120<br>120<br>0 |           |                                               | ns<br>ns<br>ns<br>ns<br>ns<br>ns |

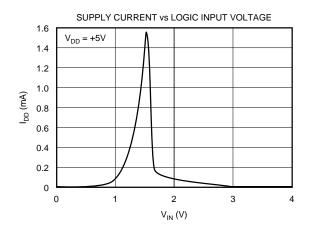

| POWER SUPPLY<br>Supply Voltage<br>Supply Current                                                                                                                                                                    | V <sub>DD</sub><br>I <sub>DD</sub>                                       | Digital Inputs = $V_{IH}$ or $V_{IL}$<br>Digital Inputs = 0V or $V_{DD}$                                                                                                                                 | 4.75                   | 5         | 5.25<br>500<br>100         | 4.75                              | 5         | 5.25<br>500<br>100                            | V<br>μΑ<br>μΑ                    |

NOTES: (1) ±1/2 LSB = ±0.012% of Full Scale. (2) All grades are monotonic to 12-bits over temperature. (3) Using internal feedback resistor. (4) Applies to  $I_{OUT}$ , All digital inputs = 0V. (5) Guaranteed by design and not tested. (6)  $I_{OUT}$  Load = 100 $\Omega$ ,  $C_{EXT}$  = 13pF, digital input = 0V to  $V_{DD}$  or  $V_{DD}$  to 0V. Extrapolated to 1/2 LSB:  $t_s$  = propagation delay ( $t_{PD}$ ) + 9 $\tau$  where  $\tau$  = measured time constant of the final RC decay. (7)  $V_{REF}$  = +10V, all digital inputs = 0V. (8) Absolute temperature coefficient is less than ±50ppm/°C. (9) Digital inputs are CMOS gates:  $I_N$  is typically 1nA at +25°C. (10)  $V_{REF}$  = 0V, all digital inputs = 0V to  $V_{DD}$  or  $V_{DD}$  to 0V. (11) All digital inputs = 0V. (12) Calculated from worst case  $R_{REF}$ :  $I_{ZSE}$  (in LSBs) = ( $R_{REF} \times I_{LKG} \times 4096$ )/ $V_{REF}$ . (13) Calculations from en =  $\sqrt{4K \text{ TRB}}$  where: K = Boltzmann constant, J/°K, R = resistance,  $\Omega$ . T = Resistor temperature, °K, B = bandwidth, Hz. (14) Tested at  $V_{IN}$  = 0V or  $V_{DD}$ .

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### WAFER TEST LIMITS

At  $V_{DD}$  = +5V;  $V_{REF}$  = +10V;  $I_{OUT}$  = GND = 0V;  $T_A$  = +25°C.

| PARAMETER                                                                                | SYMBOL                                                | CONDITIONS                                                                              | LIMIT              | DAC8043<br>UNITS               |

|------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|--------------------------------|

| STATIC ACCURACY<br>Resolution<br>Integral Nonlinearity<br>Differential Nonlinearity      | N<br>INL<br>DNL                                       |                                                                                         | 12<br>±1<br>±1     | Bits min<br>LSB max<br>LSB max |

| Gain Error<br>Power Supply Rejection Ratio<br>Output Leakage Current (I <sub>OUT</sub> ) | G <sub>FSE</sub><br>PSRR<br>I <sub>LKG</sub>          | Using Internal Feedback Resistor $\Delta V_{DD} = \pm 5\%$<br>Digital Inputs = $V_{IL}$ | ±2<br>±0.002<br>±5 | LSB max<br>%/% max<br>nA max   |

| REFERENCE INPUT<br>Input Resistance                                                      | R <sub>IN</sub>                                       |                                                                                         | 7/15               | kΩ min/max                     |

| DIGITAL INPUTS<br>Digital Input HIGH<br>Digital Input LOW<br>Input Leakage Current       | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IL</sub> | $V_{IN} = 0V$ to $V_{DD}$                                                               | 2.4<br>0.8<br>±1   | V min<br>V max<br>µA max       |

| POWER SUPPLY<br>Supply Current                                                           | I <sub>DD</sub>                                       | Digital Inputs = $V_{IH}$ or $V_{IL}$<br>Digital Inputs = 0V to $V_{DD}$                | 500<br>100         | μA max<br>μA max               |

NOTE: Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND 0V, +7V   V <sub>REF</sub> to GND ±25V   V <sub>RFB</sub> to GND ±25V   Digital Input Voltage Range -0.3V to V <sub>DI</sub> Output Voltage (Pin 3) -0.3 V to V <sub>DI</sub> Operating Temperature Range -0.3 V to V <sub>DI</sub> AD    U, UC -40°C to +85°C   Junction Temperature +150°C   Storage Temperature (soldering, 10s) +300°C |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Lead Temperature (soldering, 10s)+300° C                                                                                                                                                                                                                                                                                                                          | С |

| θ <sub>JA</sub> +100°C/M<br>θ <sub>JC</sub> +42°C/M                                                                                                                                                                                                                                                                                                               |   |

**CAUTION:** 1. Do not apply voltages higher than V<sub>DD</sub> or less than GND potential on any terminal except V<sub>REF</sub> (Pin 1) and R<sub>FB</sub> (Pin 2). 2. The digital control inputs are ESD protected: however, permanent damage may occur on unprotected units from high-energy electrostatic fields. Keep units in conductive foam at all times until ready to use. 3. Use proper anti-static handling procedures. 4. Absolute Maximum Ratings apply to both packaged devices. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT   | INL    | TEMPERATURE<br>RANGE | PACKAGE    | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> |  |

|-----------|--------|----------------------|------------|---------------------------------------------|--|

| DAC8043U  | 1LSB   | -40°C to +85°C       | 8-pin SOIC | 182                                         |  |

| DAC8043UC | 1/2LSB | -40°C to +85°C       | 8-pin SOIC | 182                                         |  |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

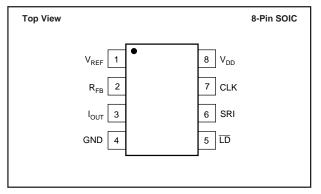

#### **PIN CONFIGURATION**

# ELECTROSTATIC DISCHARGE SENSITIVITY

Any integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

*Digital Inputs:* All digital inputs of the DAC8043 incorporate on-chip ESD protection circuitry. This protection is designed and has been tested to withstand five 2500V positive and negative discharges (100pF in series with 1500 $\Omega$ ) applied to each digital input.

Analog Pins: Each analog pin has been tested to Burr-Brown's analog ESD test consisting of five 1000V positive and negative discharges (100pF in series with 1500 $\Omega$ ) applied to each pin. V<sub>REF</sub> and R<sub>FB</sub> show some sensitivity.

#### WRITE CYCLE TIMING DIAGRAM

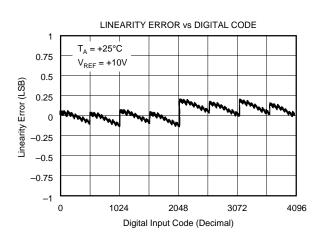

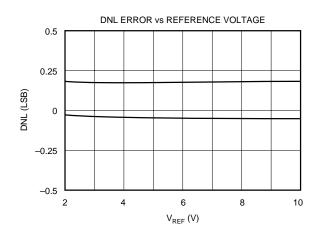

# **TYPICAL PERFORMANCE CURVES**

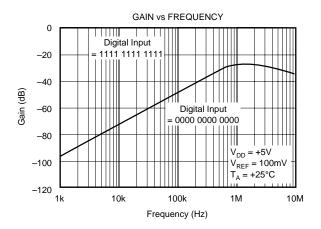

At V<sub>DD</sub> = +5V; V<sub>REF</sub> = +10V; I<sub>OUT</sub> = GND = 0V; T<sub>A</sub> = Full Temperature Range specified under Absolute Maximum Ratings, unless otherwise noted.

TOTAL HARMONIC DISTORTION vs FREQUENCY

# DISCUSSION OF SPECIFICATIONS

#### **RELATIVE ACCURACY**

This term, also known as end point linearity or integral linearity, describes the transfer function of analog output to digital input code. Relative accuracy describes the deviation from a straight line, after zero and full scale errors have been adjusted to zero.

#### DIFFERENTIAL NONLINEARITY

Differential nonlinearity is the deviation from an ideal 1LSB change in the output when the input code changes by 1LSB. A differential nonlinearity specification of 1LSB maximum guarantees monotonicity.

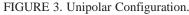

#### GAIN ERROR

Gain error is the difference between the full-scale DAC output and the ideal value. The ideal full scale output value for the DAC8043 is  $-(4095/4096)V_{REF}$ . Gain error may be adjusted to zero using external trims as shown in Figure 4.

#### **OUTPUT LEAKAGE CURRENT**

The current which appears at  $I_{\rm OUT}$  with the DAC loaded with all zeros.

#### **OUTPUT CAPACITANCE**

The parasitic capacitance measured from I<sub>OUT</sub> to GND.

#### FEEDTHROUGH ERROR

The AC output error due to capacitive coupling from  $V_{\text{REF}}$  to  $I_{\text{OUT}}$  with the DAC loaded with all zeros.

#### OUTPUT CURRENT SETTLING TIME

The time required for the output current to settle to within  $\pm 0.01\%$  of final value for a full scale step.

#### DIGITAL-TO-ANALOG GLITCH ENERGY

The integrated area of the glitch pulse measured in nanovoltseconds. The key contributor to digital-to-analog glitch is charge injected by digital logic switching transients.

## **CIRCUIT DESCRIPTION**

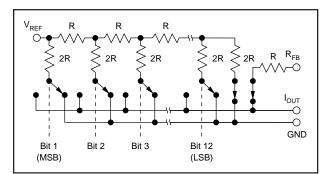

Figure 1 shows a simplified schematic of a DAC8043. The current from the  $V_{REF}$  pin is switched between  $I_{OUT}$  and GND by 12 single-pole double-throw CMOS switches. This main-

FIGURE 1. Simplified Circuit Diagram for the DAC.

tains a constant current in each leg of the ladder regardless of the input code. The input resistance at  $V_{REF}$  is therefore constant and can be driven by either a voltage or current, AC or DC, positive or negative polarity, and have a voltage range up to  $\pm 20V$ .

A CMOS switch transistor, included in series with the ladder terminating resistor and in series with the feedback resistor,  $R_{FB}$ , compensates for the temperature drift of the ON resistance of the ladder switches.

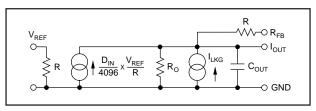

Figure 2 shows an equivalent circuit for the DAC.  $C_{OUT}$  is the output capacitance due to the N-channel switches and varies from about 80pF to 110pF with digital input code. The current source  $I_{LKG}$  is the combination of surface and junction leakages to the substrate.  $I_{LKG}$  approximately doubles every 10°C.  $R_O$  is the equivalent output resistance of the D/A and it varies with input code.

FIGURE 2. Equivalent Circuit for the DAC.

# INSTALLATION

#### ESD PROTECTION

All digital inputs of the DAC8043 incorporate on-chip ESD protection circuitry. This protection is designed to withstand 2.5kV (using the Human Body Model, 100pF and 1500 $\Omega$ ). However, industry standard ESD protection methods should be used when handling or storing these components. When not in use, devices should be stored in conductive foam or rails. The foam or rails should be discharged to the destination socket potential before devices are removed.

#### POWER SUPPLY CONNECTIONS

The DAC8043 is designed to operate on  $V_{DD} = +5V \pm 5\%$ . For optimum performance and noise rejection, power supply decoupling capacitors  $C_D$  should be added as shown in the application circuits. These capacitors (1µF tantalum recommended) should be located close to the D/A. Output op amp analog common (+ input) should be connected as near to the GND pins of the DAC8043 as possible.

#### WIRING PRECAUTIONS

To minimize AC feedthrough when designing a PC board, care should be taken to minimize capacitive coupling between the  $V_{REF}$  lines and the  $I_{OUT}$  lines. Coupling from any of the digital control or data lines might degrade the glitch performance. Solder the DAC8043 directly into the PC board without a socket. Sockets add parasitic capacitance (which can degrade AC performance).

#### AMPLIFIER OFFSET VOLTAGE

The output amplifier used with the DAC8043 should have low input offset voltage to preserve the transfer function linearity. The voltage output of the amplifier has an error component which is the offset voltage of the op amp multiplied by the "noise gain" of the circuit. This "noise gain" is equal to  $(R_F/R_O + 1)$  where  $R_O$  is the output impedance of the D/A  $I_{OUT}$  terminal and  $R_F$  is the feedback network impedance. The nonlinearity occurs due to the output impedance varying with code. If the 0 code case is excluded (where  $R_O =$  infinity), the  $R_O$  will vary from R to 3R providing a "noise gain" variation between 4/3 and 2. In addition, the variation of  $R_O$  is nonlinear with code, and the largest steps in  $R_O$  occur at major code transitions where the worst differential nonlinearity is also likely to be experienced. The nonlinearity seen at the amplifier output is

$$2V_{OS} - 4V_{OS}/3 = 2V_{OS}/3.$$

Thus, to maintain good nonlinearity the op amp offset should be much less than 1/2LSB.

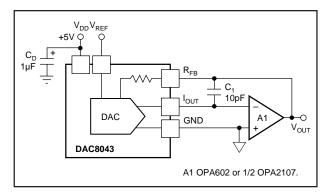

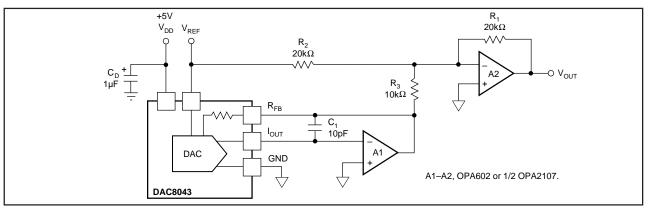

#### UNIPOLAR CONFIGURATION

Figure 3 shows DAC8043 in a typical unipolar (two-quadrant) multiplying configuration. The analog output values

| DATA INPUT                                                                         | ANALOG OUTPUT                                                                                                                  |  |  |  |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MSB↓ ↓ LSB<br>1111 1111 1111<br>1000 0000 0000<br>0000 0000 0001<br>0000 0000 0000 | -V <sub>REF</sub> (4095/4096)<br>-V <sub>REF</sub> (2048/4096) = −1/2V <sub>REF</sub><br>-V <sub>REF</sub> (1/4096)<br>0 Volts |  |  |  |

TABLE I. Unipolar Output Code.

versus digital input code are listed in Table I. The operational amplifiers used in this circuit can be single amplifiers such as the OPA602, or a dual amplifier such as the OPA2107. C1 provides phase compensation to minimize settling time and overshoot when using a high speed operational amplifier.

If an application requires the D/A to have zero gain error, the circuit shown in Figure 4 may be used. Resistor R2 induces a positive gain error greater than worst-case initial negative gain error. Trim resistor R1 provides a variable negative gain error and have sufficient trim range to correct for the worst-case initial positive gain error plus the error produced by R2.

#### **BIPOLAR CONFIGURATION**

Figure 5 shows the DAC8043 in a typical bipolar (fourquadrant) multiplying configuration. The analog output values versus digital input code are listed in Table II.

The operational amplifiers used in this circuit can be single amplifiers such as the OPA602 or a dual amplifier such as the OPA2107. C1 provides phase compensation to minimize settling time and overshoot when using a high speed operational amplifier. The bipolar offset resistors R1–R2 should be ratio-matched to 0.01% to ensure the specified gain error performance.

| DATA INPUT                                                                                            | ANALOG OUTPUT                                                                                                                         |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| MSB ↓ ↓ LSB<br>1111 1111 1111<br>1000 0000 0001<br>1000 0000 0000<br>0111 1111 1111<br>0000 0000 0000 | +V <sub>REF</sub> (2047/2048)<br>+V <sub>REF</sub> (1/2048)<br>0 Volts<br>-V <sub>REF</sub> (1/2048)<br>-V <sub>REF</sub> (2048/2048) |

TABLE II. Bipolar Output Code.

FIGURE 5. Bipolar Configuration.