#### CURRENT MODE PWM CONTROLLER

The DBL3842, high performance current mode controller, provides the necessary features to off-line and DC-DC fixed frequency current control applications offering the designer a cost effective solution with minimal external components

Internally protection circurity includes built-in input and reference under-voltage lockout and current limiting with hysteresis. Also other characteristics of internal circuit provide improved line regulation, enhanced load response, trimmed oscillation for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator and totempole output designed to source and sink high peak current from a capacitive load such as the gate of a power MOSFET.

#### FEATURES

- Optimized for off-line control

- O Low start up and operating current

- Pulse by pulse current limiting

- O Enhanced load response characteristic

- Current mode operation to 500KHz

- O Undervoltage lockout with 6V hysteresis

- O Internally trimmed bandgap reference about 5V

- Automatic feed forward compensation

- O High current totem-pole output

## ☐ MAXIMUM RATINGS(T<sub>a</sub>=25°C)

| Characteristics                      | Symbol   | Rating      | Unit |  |

|--------------------------------------|----------|-------------|------|--|

| Supply Voltage                       | Vcc      | 30          | V    |  |

| Current Sense and Vfb Input          | Vin      | -0.3 to Vcc | ٧    |  |

| Total Power Supply and Zener Current | Icc + Iz | 30          | mA   |  |

| Output Sink of Source Current        | lo       | 1           | А    |  |

| Error Amp Output Sink Current        | leo      | 10          | mA   |  |

| Operating Ambient Temperature        | Та       | 0 to 70     | Ĉ    |  |

| Storage Temperature Range            | Tstg     | -65 to 150  | °.   |  |

| Power Dissipation at Ta≤50°C         | Pd       | 1           | W    |  |

<sup>\*</sup> note) All voltages are with respect to PIN5, and current are positive into the specified pin.

### PIN DESCRIPTION

| PIN NO | FUNCTION     | DESCRIPTION                                                                    |

|--------|--------------|--------------------------------------------------------------------------------|

| 1      | Compensation | Error amplifier output and is made available for loop compensation.            |

| 2      | Voltage      | Inverting input of error amplifier, normally connected to the switching power  |

|        | feedback     | supply output through a resister driver.                                       |

| 3      | Current      | A voltage proportional to inductor current is connected to this input. The PWM |

|        | sense        | uses this information to terminate the output.                                 |

| 4      | Rt/Ct        | The oscillator frequency and maximum output duty cycle are programmed by       |

|        |              | connecting resister Rt to Vref and capacitor Ct to ground.                     |

| 5      | Ground       | This pin is the combined control circuitry and power ground.                   |

| 6      | Output       | This output directly drives the gate of a power MOSFET. Peak currents up to    |

|        |              | 1.0A are sourced and sinked by this pin.                                       |

| 7      | Vcc          | This pin is the positive supply of the control IC.                             |

| 8      | Vref         | This is the reference output, it provides charging current for capacitor Ct    |

|        |              | through resistor Rt.                                                           |

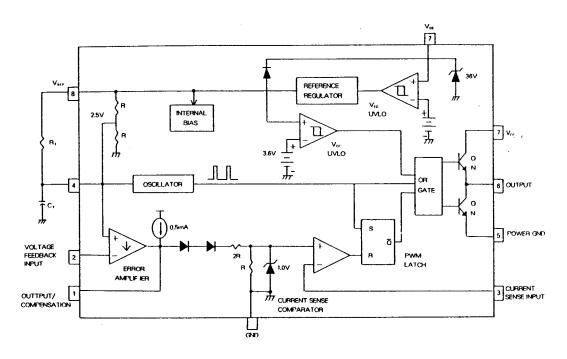

#### ☐ BLOCK DIAGRAM

#### ☐ ELECTRICAL CHARACTERISTICS

(Unless otherwise stated, these specifications apply for  $0 \le T_* \le 70^{\circ}C$ ;  $V_{cc} = 15V(Note 4)$ ,

$R_i = 10K\Omega$ ,  $C_i = 3.3nF$ )

| Characteristics       | Symbol            | Test Condition                                            | Min. | Тур.  | Max.  | Unit |

|-----------------------|-------------------|-----------------------------------------------------------|------|-------|-------|------|

| 1. Reference Section  | <u> </u>          |                                                           |      |       |       |      |

| Output Voltage        | V <sub>ref</sub>  | T_=25℃, I <sub>o</sub> =1mA                               | 4.90 | 5.00  | 5.10  | V    |

| Line Regulation       | △N <sub>ref</sub> | 12V≤V <sub>cc</sub> ≤25V                                  |      | 6     | 20    | mV   |

| Load Regulation       | △N <sub>ref</sub> | 1≤l <sub>0</sub> ≤20mA                                    |      | 6     | 25    | mV   |

| Temperature Stability | ΔN./ΔT            | (Note 1)                                                  |      | 0.2   | 0.4   | mV/℃ |

| Output Noise Voltage  | Vn                | 10H <sub>z</sub> ≤f≤10KHz<br>T <sub>*</sub> =25℃ (Note 1) |      | 50    |       | μV   |

| Long Term Stability   | S                 | T <sub>a</sub> =125℃, 1000Hrs(Note 1)                     |      | 5     |       | mV   |

| Output Short Circuit  | l <sub>sc</sub>   |                                                           | -30  | - 100 | - 180 | mA   |

## ☐ ELECTRICAL CHARACTERISTICS(continued)

| Characteristics          | Symbol          | Test Condition                                   | Min. | Тур. | Max. | Unit     |

|--------------------------|-----------------|--------------------------------------------------|------|------|------|----------|

| 2. Oscillator Section    |                 |                                                  |      |      |      |          |

| Initial Accuracy         | f <sub>sc</sub> | T <sub>a</sub> =25℃                              | 47   | 52   | 57   | KHz      |

| Voltage Stability        | Δt/ΔN           | 12≤V <sub>3</sub> ≤25V                           |      | 0.2  | 1.0  | %        |

| Temperature Stability    | Δt/ΔT           | $T_{min} \le T_a \le T_{max}(Note 1)$            |      | 5    |      | %        |

| Amplitude                | ٧,              | V <sub>pin4</sub> Peak to Peak                   |      | 1,7  |      | V        |

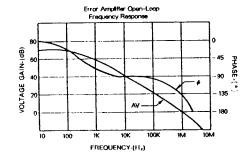

| 3. Error Amp Section     |                 |                                                  |      |      |      |          |

| Input Voltage            | V <sub>2</sub>  | V <sub>pin1</sub> =2.5V                          | 2.42 | 2.50 | 2.58 | ٧        |

| Input Bias Current       | I <sub>b</sub>  |                                                  |      | -0.3 | -2.0 | μА       |

| Open loop Voltage Gain   | Avoi            | 2≤V <sub>0</sub> ≤4V                             | 65   | 90   |      | dB       |

| Supply Voltage Rejection | SVR             | 12≤V <sub>4</sub> ≤25V                           | 60   | 70   |      | dB       |

| Output Sink Current      | l,              | V <sub>pin2</sub> =2.7V, V <sub>pin1</sub> =1.1V | 2    | 6    |      | mA       |

| Output Source Current    | 1,              | V <sub>pin2</sub> =2.3V, V <sub>pin1</sub> =5V   | -0.5 | -0.8 |      | mA       |

| V <sub>vut</sub> High    | V <sub>ch</sub> | V <sub>pin2</sub> =2.3V;                         | _    | 6    |      |          |

|                          |                 | $R_{\rm L}$ = 15K $\Omega$ to Ground             | 5    |      |      | V        |

| Vout LOW                 | Vel             | V <sub>pin2</sub> =2.7V;                         |      | 0.7  |      |          |

|                          |                 | $R_L = 15K \Omega$ to Pin8                       |      |      | 1.1  | V        |

| 4. Current Sense Section |                 |                                                  |      |      |      |          |

| Gain                     | Gv              | (Note 2 & 3)                                     | 2.8  | 3.0  | 3.2  | V/V      |

| Maximum Input Signal     | V <sub>3</sub>  | V <sub>pin 1</sub> =5V(Note 2)                   | 0.9  | 3.0  | 1,1  | ٧        |

| Supply Volt Rejection    | SVR             | 12≤V <sub>a</sub> ≤25V(Note 2)                   |      | 70   |      | dB       |

| Input Bias Current       | lb              |                                                  |      | -2   | - 10 | μА       |

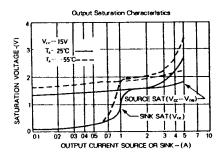

| 5. Output Section        |                 |                                                  |      |      |      |          |

| Output Low Level         | V <sub>ol</sub> | I <sub>sink</sub> =20mA                          |      | 0.1  | 0.4  | ٧        |

|                          |                 | I <sub>sink</sub> =200mA                         |      | 1,5  | 2.2  | ٧        |

| Output High Level        | Voh             | I <sub>source</sub> =20mA                        | 13.0 | 13.5 |      | <b>V</b> |

|                          |                 | I <sub>source</sub> =200mA                       | 12.0 | 13.5 |      | ٧        |

| Rise time                | t,              | T_=25°C CI=1nF(Note 1)                           |      | 50   | 150  | ns       |

| Fall time                | t <sub>f</sub>  | T_=25°C Cl=1nF(Note 1)                           |      | 50   | 150  | ns       |

### ☐ ELECTRICAL CHARACTERISTICS(continued)

| Characteristics              | Symbol   | Test Condition         | Min  | Тур.     | Max  | Unit |

|------------------------------|----------|------------------------|------|----------|------|------|

| 6. Under-Voltage Lockout Sec | tion     |                        |      |          |      |      |

| Start Threshold              | Vth      | Vpin7 where Vpin8≥4.9V | 14.5 | 16.0     | 17.5 | ٧    |

| Min, Operation Voltage After | Vcc(min) | Vpin7 where Vpin8≤1V   | 8.5  | 10.0     | 11,5 | V    |

| 7. PWM Section               |          | <u> </u>               |      | <b>L</b> | L    | 1    |

| Maximum Duty Cycle           | DC max   |                        | 93   | 97       | 100  | ns   |

| 8. Total Standby Section     |          |                        |      |          |      | 1    |

| Start-up Current             | lst      | Vcc=14V after turn on  |      | 0.5      | 1.0  | mA   |

| Operating Supply Current     | lcc      | Vpin2=Vpin3=OV         |      | 11       | 20   | mA   |

| Zener Voltage                | Vz       | lcc=25mA               |      | 36       |      | V    |

NOTE: 1. These parameters, although guaranteed, are not 100% tested in production

- 2. Parameter measured at trip point of latch with Vpin2=0

- 3. Gain defined as:  $A = \Delta V pin1/\Delta V pin3; 0 \le V pin3 \le 0.8V$

- 4. Adjust Vcc above the start threshould before setting at 15V

#### ☐ INFORMATION IN USING IC

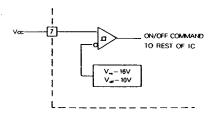

#### 1. UNDERVOLTAGE LOCKOUT

< 17mA < 1mA Voc

To prevent erratic output behavior which activating the power switch with extraneous leakage currents, during under voltage lock-out. Output(pin6) should be shunted to ground with a bleeder resister.

The Vcc comparator upper and lower threshold are 16V/10V. The large hysteresis and low start up currents makes it ideally suited in off-line converter application where efficient bootstrap start-up techniques are required.

#### ☐ INFORMATION IN USING IC(continued)

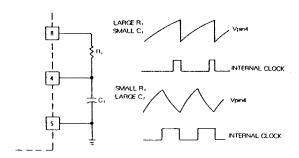

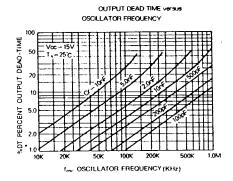

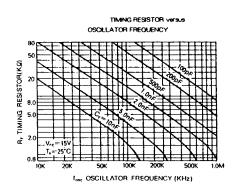

### 2. OSCILLATOR WAVEFORMS AND MAXIMUM DUTY CYCL

The oscillator frequency is programmed by the values selected for the timing components Rt and Ct. Ct is charged from 5V, Vref, through resistor Rt to approximately 2.8V and discharged to 1.2V by an internal current sink.

During the dischare of Ct, the oscillator generates an internal blanking pulse and the center input NOR gate high.

This makes output to be in a low state and control the amount of output dead time.

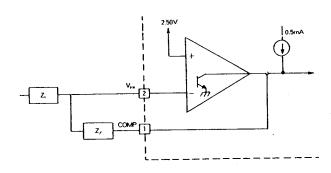

#### 3. ERROR AMP CONFIGURATION

Error amp output (Pin1) is provided for external loop compensation and error amp can source or sink up to 0.5mA. The non—inverting input is internally biased at 2.5V and is not pinned out.

The converter output voltage is typically divided down and monitored by the inverting input (pin2).

## ☐ INFORMATION IN USING IC(continued)

#### 4. CURRENT SENSE CIRCUIT

$$lpeak = \frac{R(Vpin1 - 2Vbe)}{3R \times Rs}$$

A normal operating conditions occurs when the power supply output is overloaded or if output voltage sensing is lost. Under these conditions, the current sense comparator threshold will be internally clamped to 1.0V Therefore the maximum peak switch current is lpk(max) = 1.0V/Rs, and under the normal operating conditious the peak inductor current controlled by the voltage at pin1.

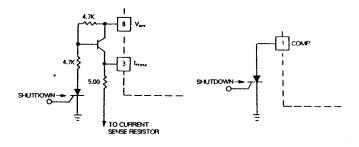

#### 5. SHUTDOWN TECHNIQUES

Shutdown of the DBL3842 can be accomplished by two methods; either raise pin3 above 1V or pull pin1 below a voltage two diodes drops above ground. Either method causes the output of the PWM comparator to be high(refer to

block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pins 1 and/or 3 is removed.

In one example, an externally latched shutdown may be accomplished by adding an SCR which turn off, allowing the SCR to reset

## ☐ INFORMATION IN USING IC(continued)

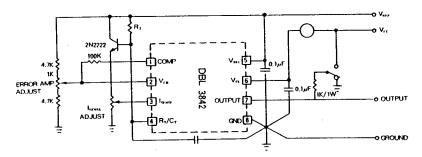

#### 6. OPEN LOOP TEST

High peak currents associated with capacitive leads necessitate careful grounding techniques. Timing and bypass capacitors should be connected close to Pin 5 in a single point ground. The transistor and 5KQpotentiometer are used to sample the oscillator waveform and apply an adjustable ramp to Pin 3.

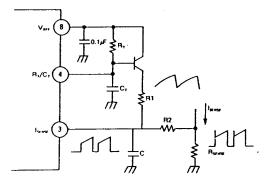

#### 7. SLOPE COMPENSATION

A fration of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for coverters requiring duty cycle over 50%. Note that capacitor C, forms a filter with R2 to supress the leading edge switch spikes.