**DDC101**

### 20-BIT ANALOG-TO-DIGITAL CONVERTER

#### **FEATURES**

- MONOLITHIC CHARGE INPUT ADC

- DIGITAL FILTER NOISE REDUCTION: 0.9ppm, rms

- DIGITAL ERROR CORRECTION: CDS

- CONVERSION RATE: Up to 15kHz

- USER FRIENDLY EVALUATION FIXTURE

#### **APPLICATIONS**

- DIRECT PHOTOSENSOR DIGITIZATION

- PRECISION INSTRUMENTATION

- INFRARED PYROMETRY

- PRECISION PROCESS CONTROL

- CT SCANNER DAS

- CHEMICAL ANALYZERS

#### **DESCRIPTION**

The DDC101 is a precision, wide dynamic range, charge digitizing A/D converter with 20-bit resolution. Low level current output devices, such as photosensors, can be directly connected to its input. The most stringent accuracy requirements of many unipolar output sensor applications occur at low signal levels. To meet this requirement, Burr-Brown developed the adaptive delta modulation architecture of the DDC101 to provide linearly improving noise and linearity errors as the input signal level decreases. The DDC101 combines the functions of current-to-voltage conversion, integration, input programmable gain amplification, A/D conversion, and digital filtering to produce precision, wide dynamic range results. The input signal can be a low level current connected directly into the unit or a voltage connected through a user selected resistor. Although the DDC101 is optimized for unipolar signals, it can also accurately digitize bipolar input signals. The patented delta modula-

tion topology combines charge integration and digitization functions. Oversampling and digital filtering reduce system noise dramatically. Correlated Double Sampling (CDS) captures and eliminates steady state and conversion cycle dependent offset and switching errors that are not eliminated with conventional analog circuits.

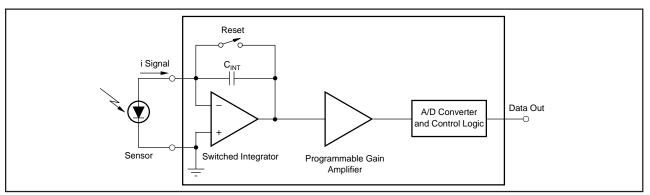

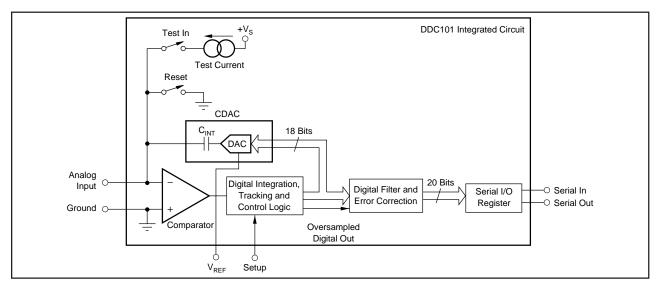

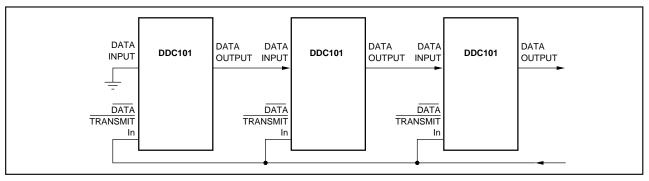

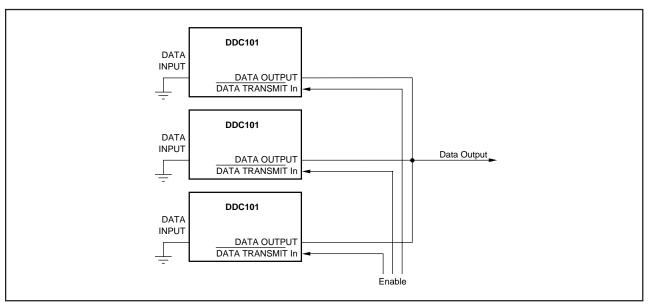

The DDC101 block diagram is shown below. During conversion, the input signal is collected on the internal integration capacitance for a user determined integration period. A high precision, autozeroed comparator samples the analog input node. Tracking logic updates the internal high resolution D/A converter at a 2MHz rate to maintain the analog input at virtual ground. A user programmable digital filter oversamples the tracking logic's output. The digital filter passes a low noise, high resolution digital output to the serial I/O register. The serial outputs of multiple DDC101 units can be easily connected together in series or parallel if desired to minimize interconnections.

nternational Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1993 Burr-Brown Corporation PDS-1211E Printed in U.S.A. March, 19

#### TABLE OF CONTENTS

## SECTION 1 BASIC THEORY OF OPERATION

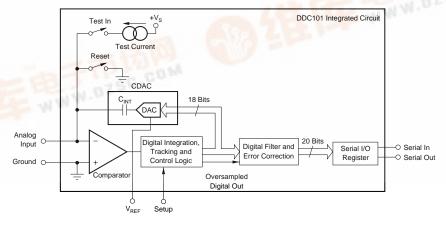

The basic function of the DDC101 is illustrated in the Simplified Equivalent Circuit shown in Figure 1. The operation is equivalent to the functions performed by a very high quality, low bias current switched integrator followed by a precision floating point programmable gain amplifier and ending with a high resolution A/D converter.

The second block diagram, Figure 2, shows the DDC101 circuit architecture which implements these functions monolithically. During each conversion, the input signal current is collected on the internal integration capacitance,  $C_{\rm INT}$ , as charge for a user determined integration period,  $T_{\rm INT}$ . As the integration capacitor collects input charge, the tracking logic updates the internal high resolution D/A converter at a 2MHz rate to maintain the analog input node at virtual ground.

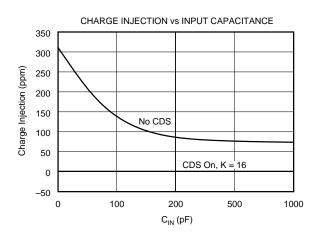

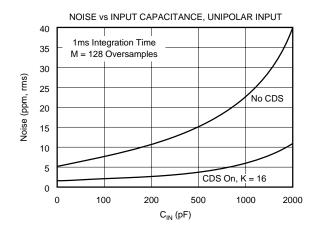

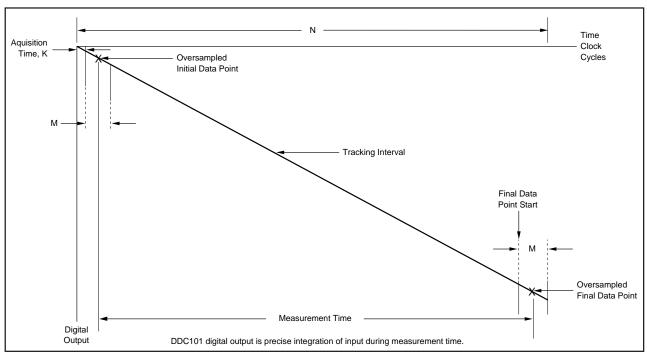

The digital filter oversamples the tracking logic's output at the beginning and end of each integration period to produce two oversampled data points. The DDC101 measures the charge accumulated in the integration and performs correlated double sampling (CDS) by subtracting these two data points. CDS eliminates integration cycle dependent errors such as charge injection, offset voltage, and reset noise since these errors are measured with the signal at each of the two data points. The number of oversamples, and thus the frequency response of the digital filter, is user programmable. The digital filter passes a low noise, high resolution digital output to the serial I/O register. Since the timing control of the serial I/O register is independent of the DDC101 conversion process, the outputs of multiple DDC101 units can be connected together in series or parallel to minimize interconnections.

FIGURE 1. Simplified Equivalent Circuit of DDC101 to Illustrate Function.

FIGURE 2. DDC101 Block Diagram.

BBB DDC101

An internal test current source is provided for basic functionality testing and diagnostics. This approximately 100nA current source is pin activated and sums with the external input current.

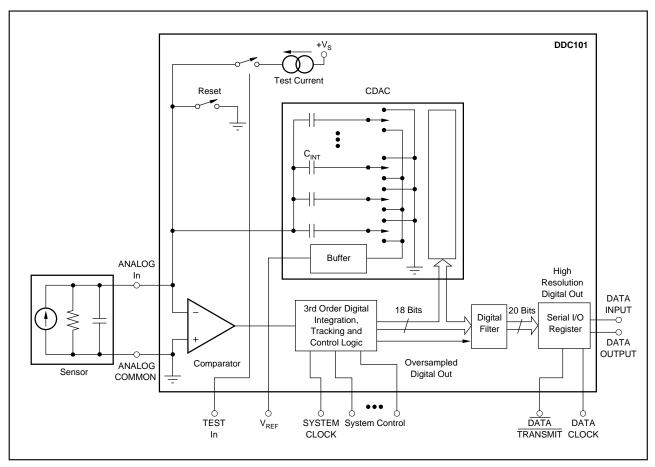

Figure 3 shows a more detailed circuit configuration of the DDC101. The single integration capacitor,  $C_{INT}$ , and the D/A converter have been replaced with a high resolution

Capacitor Digital-to-Analog Converter (CDAC). By switching between ground and  $V_{\text{REF}}$  the binary weighted capacitor array of the CDAC accumulates the input signal's charge to keep the comparator input at virtual ground.

FIGURE 3. DDC101 Detailed Circuit Diagram.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

DDC101 BURR-BROWN®

## **SECTION 2 SPECIFICATIONS**

|                                              |                                          |          | DDC101              |                       | ļ               |

|----------------------------------------------|------------------------------------------|----------|---------------------|-----------------------|-----------------|

| PARAMETER                                    | CONDITIONS                               | MIN      | TYP                 | MAX                   | UNITS           |

| INPUTS                                       |                                          |          |                     |                       |                 |

| Charge Input <sup>(6)</sup>                  |                                          |          |                     |                       |                 |

| Unipolar Input Range                         | BTC Output Code                          | -1.95    |                     | 500                   | pC/Integration  |

| Bipolar Input Range                          | BTC Output Code                          | -251.95  |                     | 250                   | pC/Integration  |

| Input Current                                | Unipolar or Bipolar Range                |          |                     | 7.8                   | μĂ              |

| Current Input Range Examples(10)             | ' '                                      |          |                     |                       | ·               |

| Unipolar Input Range                         | T <sub>INT</sub> = 100μs                 | -0.0195  |                     | 5                     | μА              |

| Unipolar Input Range                         | $T_{INT} = 1 ms$                         | -1.95    |                     | 500                   | nA              |

| Bipolar Input Range                          | $T_{INT} = 100 \mu s$                    | -2.5195  |                     | 2.5                   | μA              |

| Bipolar Input Range                          | $T_{INT} = 100\mu s$<br>$T_{INT} = 1 ms$ | -251.95  |                     | 250                   | nΑ              |

| Voltage Input Examples <sup>(10)</sup>       | T <sub>INT</sub> = TITIS                 | 201.00   |                     | 230                   | 11/4            |

| Unipolar Input Range <sup>(2)</sup>          | B 10MO T 1mg                             | -0.0195  |                     | 5                     | V               |

| Bipolar Input Range <sup>(2)</sup>           | $R_{IN} = 10M\Omega$ , $T_{INT} = 1ms$   | -2.5195  |                     | 2.5                   | V               |

|                                              | $R_{IN} = 10M\Omega, T_{INT} = 1ms$      | -2.5195  |                     | 2.5                   | V               |

| DYNAMIC CHARACTERISTICS                      |                                          | 0.4      |                     | 050 400               |                 |

| Conversion Time                              |                                          | 64       |                     | 256 x 10 <sup>6</sup> | μs              |

| Integration Time                             |                                          | 64       |                     | 106                   | μs              |

| System Clock Input                           |                                          | 0.5      |                     | 2                     | MHz             |

| ACCURACY                                     |                                          |          |                     |                       |                 |

| Unipolar Mode Noise                          |                                          |          |                     |                       |                 |

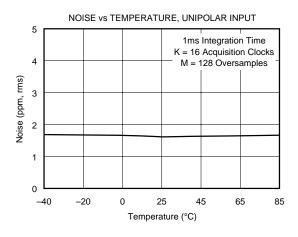

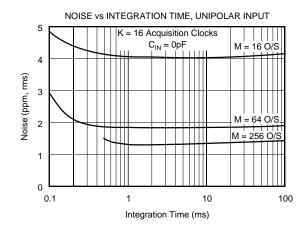

| Noise, Low Level Current Input(1)            | $C_{SENSOR} = 0pF, L = 8$                |          | 0.9                 |                       | ppm of FSR, rms |

| Noise, Low Level Current Input(1)            | $C_{SENSOR} = 0pF, L = 1$                |          | 1.6                 |                       | ppm of FSR, rn  |

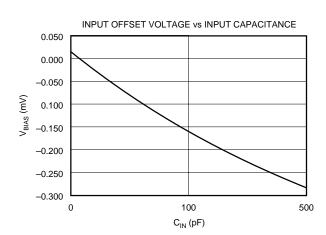

| Noise, Low Level Current Input(1)            | $C_{SENSOR} = 100pF, L = 1$              |          | 2.1                 | 3                     | ppm of FSR, rn  |

| Noise, Low Level Current Input(1)            | C <sub>SENSOR</sub> = 500pF, L = 1       |          | 4.2                 |                       | ppm of FSR, rn  |

| Noise, Voltage Input <sup>(1, 2)</sup>       | $R_{IN} \ge 20M\Omega$                   |          | 1.9                 |                       | ppm of FSR, rn  |

| Differential Linearity Error                 | IN -                                     |          |                     |                       | ' '             |

| Unipolar Input Range                         | Entire Range                             |          | +0.0059             | % Reading ±0.5ppm F   | SR max          |

| ompolar input rango                          | 0.1% FSR Input                           |          |                     | ±0.00006              | \ \ % of FSR    |

|                                              | 1% FSR Input                             |          |                     | ±0.00010              | % of FSR        |

|                                              | 10% FSR Input                            |          |                     | ±0.00055              | % of FSR        |

| Unipolar or Bipolar Input Range              | 10% F3K Iliput                           |          |                     | ±0.00055              | % of FSR        |

|                                              |                                          |          |                     | ±0.0015               | /0 UI F 3 N     |

| Integral Linearity Error                     | 0 to 500 no/letometics                   |          | 10.0044             | <br>                  | CD              |

| Unipolar Input Range(11)                     | 0 to 500 pc/Integration                  |          |                     | % Reading ±2.5ppm F   |                 |

|                                              | -1.95 to 0 pc/Integration                |          | ±0.0244             | % Reading ±3.0ppm F   |                 |

|                                              | 0.1% FSR Input                           |          |                     | ±0.00028              | % of FSR        |

|                                              | 1% FSR Input                             |          |                     | ±0.00050              | % of FSR        |

|                                              | 10% FSR Input                            |          |                     | ±0.0027               | % of FSR        |

| Unipolar or Bipolar Input Range(11)          |                                          |          |                     | ±0.003                | % of FSR        |

| No Missing Codes                             |                                          |          |                     |                       |                 |

| Unipolar Input Range                         |                                          |          | 18                  |                       | Bits            |

| Bipolar Input Range                          |                                          |          | 16                  |                       | Bits            |

| Input Bias Current                           | T <sub>△</sub> = +25°C                   |          | 3                   | 10                    | pA              |

| DC Gain Error                                |                                          |          | ±0.5                | ±2                    | % of FSR        |

| Output Offset Error <sup>(8)</sup>           |                                          |          | ±0.5                |                       | ppm of FSR      |

| Input Offset Voltage(8)                      |                                          |          | ±0.5                | <u>±2</u>             | mV              |

| External Voltage Reference, V <sub>RFF</sub> |                                          |          | -2.5                |                       | VDC             |

| Internal Test Signal                         |                                          |          | 100                 |                       | nA              |

| Internal Test Signal Accuracy                |                                          |          | ±20                 |                       | nA              |

| Gain Sensitivity to V <sub>REF</sub>         | V <sub>REF</sub> = 2.5V ±0.1V            |          | 1:1                 |                       |                 |

| PSRR                                         | REF                                      | 80       | 90                  |                       | dB              |

| PERFORMANCE OVER TEMPERATU                   | RE .                                     | <u> </u> |                     |                       |                 |

| Output Offset Drift <sup>(8)</sup>           | not including bias current drift         |          | 0                   |                       | μV/°C           |

| Input Offset Voltage Drift <sup>(8)</sup>    | morading bias current unit               |          | 1                   |                       | μν/ C<br>μV/°C  |

|                                              | +25°C to +45°C                           |          |                     | 0.5                   |                 |

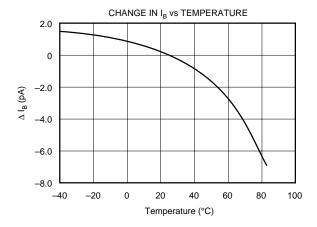

| Input Bias Current Drift                     |                                          |          | 0.1                 | 0.5                   | pA/°C           |

| Input Bias Current                           | T <sub>A</sub> = +85°C                   |          | 8                   | 40                    | pA              |

| Gain Drift <sup>(4)</sup>                    |                                          |          | ±15                 |                       | ppm/°C          |

| DIGITAL INPUT/OUTPUT                         |                                          |          |                     |                       |                 |

| Logic Family                                 |                                          |          | TTL Compatible CMOS |                       |                 |

| Logic Level: V <sub>IH</sub>                 | $I_{IH} = +5\mu A$                       | +2.0     |                     | +V <sub>cc</sub>      | V               |

| V <sub>IL</sub>                              | I <sub>II</sub> = +5μA                   | -0.3     |                     | +0.8                  | V               |

| Vau                                          | I <sub>OH</sub> = 2 TTL Loads            | +2.4     |                     | +V <sub>cc</sub>      | V               |

| V <sub>OL</sub>                              | I <sub>OI</sub> = 2 TTL Loads            | 0.0      |                     | 0.4                   | V               |

| Data Clock                                   | OL SSISIS                                |          |                     | -                     | 1               |

| Data I/O                                     |                                          |          |                     | 8                     | MHz             |

| SETUP Code I/O <sup>(9)</sup>                |                                          |          |                     | 4                     | MHz             |

| Data Format                                  |                                          |          |                     | 7                     | 1711 12         |

| Straight Binary                              | Unipolar or Bipolar Range                |          | 20                  |                       | Bits            |

|                                              |                                          |          |                     |                       |                 |

#### SPECIFICATIONS (CONT)

#### **ELECTRICAL**

All specifications with unipolar current input range,  $T_{INT}$  = 1ms, correlated double sampling enabled, System Clock = 2MHz,  $V_{REF}$  = -2.5V,  $T_A$  = +25°C and  $V_S$  = ±5VDC, unless otherwise noted.

|                                    |                                       |       | DDC101 |       |       |

|------------------------------------|---------------------------------------|-------|--------|-------|-------|

| PARAMETER                          | CONDITIONS                            | MIN   | TYP    | MAX   | UNITS |

| POWER SUPPLY REQUIREMENTS          |                                       |       |        |       |       |

| Operation <sup>(5)</sup>           |                                       | ±4.75 | ±5     | ±5.25 | VDC   |

| Quiescent Current, Positive Supply | $V_{s}$ + = +5VDC, $V_{pp}$ + = +5VDC |       | 15.6   | 19.5  | mA    |

| Analog, V <sub>s</sub> +           |                                       |       | 8.9    |       | mA    |

| Digital, V <sub>DD</sub> +         |                                       |       | 6.7    |       | mA    |

| Quiescent Current, Negative Supply | $V_s - = -5VDC$                       |       | 18.0   | 22.5  | mA    |

| Operating Power                    | ·                                     |       | 170    |       | mW    |

| TEMPERATURE RANGE                  |                                       |       |        |       |       |

| Operating                          |                                       | -40   |        | +85   | °C    |

| Storage                            |                                       | -60   |        | +100  | °C    |

NOTES: (1) Input = low level (less than 1% of Full Scale); Full Scale I<sub>N1</sub> = 500nA; T<sub>N2</sub> = 1ms; Unipolar Input Range; Acquisition Time = 16 clock cycles, Oversampling = 128. (2) Voltage input is converted through user provided input resistor, R<sub>N2</sub>; (3) FSR is Full Scale Range. (4) Gain Drift does not include the drift of the external reference. (5) V<sub>D2</sub> + must be less than or equal to V<sub>S</sub> +. See Section 7 for recommended connections. (6) Straight Binary output code has slightly different Charge Range. See Section 6. (8) Input offset voltage is nulled by autozero circuitry and causes no output error. See Section 6 (Internal Error Correction). (9) This is the maximum clock/frequency at which SETUP codes can be written to and read from the DDC101. (10) For other input current and voltage configurations, see Discussion of Specifications and Detailed Theory of Operation sections. (11) A best-fit straight line method is used to determine linearity. Two different best-fit straight lines are used for the two unipolar integral linearity specifications. Acquisition Time = 16 clock cycles, Oversampling = 128.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT | PACKAGE      | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | THERMAL RESISTANCE $(\theta_{ m JA})$ |

|---------|--------------|---------------------------------------------|---------------------------------------|

| DDC101U | 24-Lead SOIC | 239                                         | 100                                   |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Inputs                |                             |

|------------------------------|-----------------------------|

| Input Current                | 100mA, momentary            |

| Input Current                | 10mA, continuous            |

| Input Voltage                | $V_s$ + +0.5V to $V_s$ 0.5V |

| Power Supply                 |                             |

| V <sub>s</sub> +             | + 7V                        |

| V <sub>s</sub>               | –7V                         |

| V <sub>DD</sub> +            | must be $\leq V_s$ +        |

| Maximum Junction Temperature | +165°C                      |

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

DDC101 BURR-BROWN®

#### **PIN CONFIGURATION**

| Top View |                                 |    |    |   |                         | 24-Lead SOIC |

|----------|---------------------------------|----|----|---|-------------------------|--------------|

|          | V <sub>S</sub> -, ANALOG        | 1  | 24 | 4 | REFERENCE BUFFER BYPASS |              |

|          | ANALOG COMMON                   | 2  | 23 | 3 | $V_{REF}$               |              |

|          | ANALOG In                       | 3  | 22 | 2 | TEST In                 |              |

|          | ANALOG COMMON                   | 4  | 21 | 1 | RESET SETUP In          |              |

|          | V <sub>S</sub> +, ANALOG        | 5  | 20 | 0 | SETUP                   |              |

|          | V <sub>S</sub> +, ANALOG        | 6  | 19 | 9 | READ DATA/SETUP         |              |

|          | RESET SYSTEM In                 | 7  | 18 | 8 | DATA TRANSMIT In        |              |

|          | FDS (Final Data Point Start) In | 8  | 17 | 7 | OVERFLOW + Out          |              |

|          | SYSTEM CLOCK                    | 9  | 16 | 6 | OVERFLOW - Out          |              |

|          | DATA CLOCK                      | 10 | 15 | 5 | DATA VALID Out          |              |

|          | DATA INPUT                      | 11 | 14 | 4 | DATA OUTPUT             |              |

|          | V <sub>DD</sub> +, DIGITAL      | 12 | 13 | 3 | DIGITAL GROUND          |              |

|          |                                 |    |    | _ |                         |              |

## SECTION 3 PIN DESCRIPTIONS

| PIN<br>NUMBER | NAME                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | V <sub>S</sub> -, ANALOG | Negative analog power supply voltage, –5VDC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2             | ANALOG COMMON            | Analog ground point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

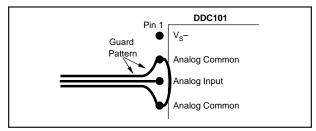

| 3             | ANALOG INPUT             | Input for low level current signal. Photosensor can be directly connected to this input. With a resistor in series, DDC101 will convert a voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4             | ANALOG COMMON            | Analog ground point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5             | V <sub>S</sub> +, ANALOG | Positive analog power supply voltage, +5VDC. Hardwire to pin 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6             | V <sub>S</sub> +, ANALOG | Positive analog power supply voltage, +5VDC. Hardwire to pin 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7             | RESET SYSTEM In          | This input resets DDC101, but does not reset the SETUP register. The DDC101 system is reset when this pir is active; reset action is removed when the pin is inactive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8             | FDS In                   | This is Final Data point Start input. This input is the basic user control of the integration and conversion timing. When it becomes active, the DDC101 starts collection of the M, final data point samples. The beginning of the next integration time is exactly M system clock periods after the Final Data point Start command when operating in the continuous mode.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9             | SYSTEM CLOCK             | This clock input sets the basic sampling rate of the DDC101. The DDC101 is specified with a clock speed of 2MHz. The clock speed can be 0.5MHz to 2.0MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10            | DATA CLOCK               | This clock input controls the data transfer rate for the serial DATA INPUT and DATA OUTPUT ports. The DATA CLOCK is independent of the SYSTEM CLOCK. This allows the DATA CLOCK to be operated at higher or lower speeds than the SYSTEM CLOCK. For best noise performance, data should not be transmitted and the DATA CLOCK should not be active during the initial and final data point collection. If data is being transmitted during the initial and final data point collection periods, the DATA CLOCK should be synchronized to the SYSTEM CLOCK, to minimize added noise. DATA CLOCK can be connected to SYSTEM CLOCK, so that the same clock is used for both; however, for best noise performance, the DATA CLOCK input should be active only when data is transmitted. |

| 11            | DATA INPUT               | This input can be used to "daisy chain" the output of several DDC101s together to minimize wiring. The output register of the DDC101 acts as a shift register to pass through the output of previously connected DDC101 units In this way, multiple DDC101 units can convert simultaneously then sequence the data out serially on the same data line with one common control line and one common data line for all DDC101 units.                                                                                                                                                                                                                                                                                                                                                   |

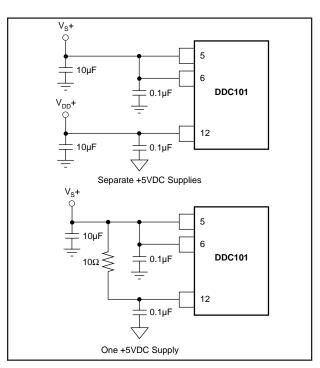

| 12            | $V_{DD}$ +, DIGITAL      | Digital power supply, +5VDC. $V_{DD}$ + must be less than or equal to $V_{S}$ +.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13            | DIGITAL GROUND           | Digital ground point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

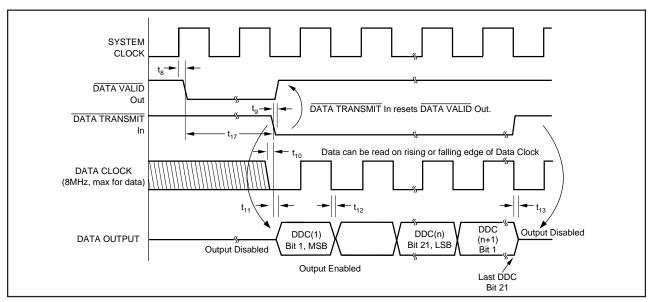

| 14            | DATA OUTPUT              | This output provides serial digital data clocked out at user controlled DATA CLOCK rate. Output data formal is a 21-bit Binary Two's Complement word or a 20-bit Straight Binary word. The data word is transmitted MSE first. When DATA TRANSMIT is not active DATA OUTPUT tri-states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

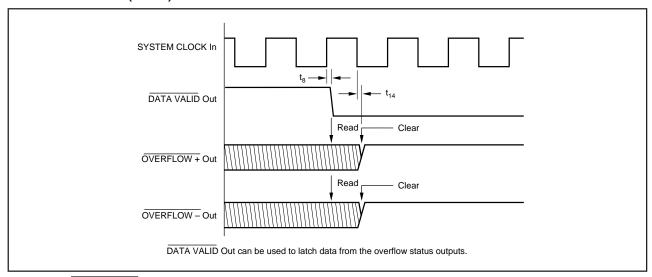

| 15            | DATA VALID               | This output is activated when conversion is complete and remains active until the DATA TRANSMIT input is activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16            | OVERFLOW-                | The OVERFLOW output signals each provide an open collector output so that the overflow outputs from several                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17            | OVERFLOW+                | DDC101s can easily be connected (wire ORed) together to a common pull-up resistor. They are activated when the input is beyond the acceptable range during conversion. Specifically, they are activated when the interna D/A converter input or digital filter exceeds full scale. They are Cleared at the end of conversion 1/2 clock cycle after DATA VALID high. DATA VALID can be used to capture OVERFLOW data into an external register.                                                                                                                                                                                                                                                                                                                                      |

6

### PIN DESCRIPTIONS (CONT)

| PIN<br>NUMBER | NAME                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18            | DATA TRANSMIT In       | This input controls the transmission of data from the serial I/O register of the DDC101. It can be activated anytime after DATA VALID out becomes active. It must remain active until all data has been collected from the serial I/O register(s) of all DDC101s in the data path.                                                                                                                                                                                                                                                                                                                                                                                                |

| 19            | READ DATA/<br>SETUP In | This input can be used to read back the current SETUP data. When this input is held high, the output from DATA OUTPUT is the data collected by the DDC101. When this input is pulled low, an internal shift register is loaded with the current SETUP data on the rising edge of DATA CLOCK. This SETUP data shift register is logically connected between DATA INPUT and DATA OUTPUT pins and can be read in the same way that the data output is read. SETUP data read back does not invalidate data already stored in the DDC101's serial I/O register or data being collected by the DDC101, although digital noise concerns should be considered as discussed in DATA CLOCK. |

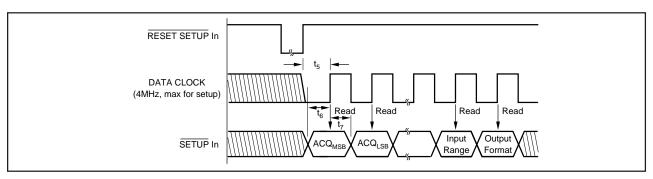

| 20            | SETUP In               | This input pin controls the DDC101 SETUP. A 12-bit digital word transmitted into this pin controls Acquisition Time, K, Oversampling, M, Multiple Integrations, L, Input Range and Output Data Format. The DDC101 reads the SETUP code at this pin after the RESET SETUP input transitions from active to inactive. The SETUP code is read into the SETUP register on the 12 positive data clock transitions following that transition.                                                                                                                                                                                                                                           |

| 21            | RESET SETUP            | Resets SETUP register only, does not reset balance of DDC101. The DDC101 reads SETUP input data after this input transitions from active (reset) to inactive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22            | TEST In                | This is a digital input that controls the connection of an internal DC current source to the DDC101's input. TEST In exercises the DDC101 and is intended to test for functionality only. The typical test input current is 100nA ±20nA. The quiescent current of the DDC101 increases by approximately 1mA when TEST In is active. When TEST is HIGH, the internal current source is ON and current is flowing into the DDC101 input. When TEST is LOW, the current source is disconnected from the input.                                                                                                                                                                       |

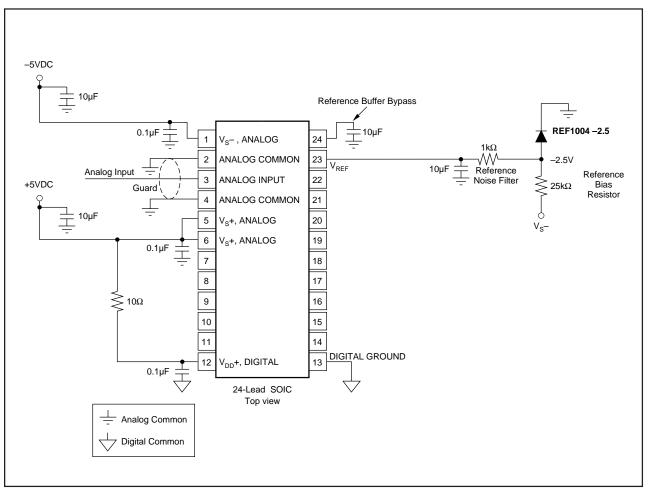

| 23            | $V_REF$                | An external –2.5V reference must be connected to the REFERENCE In pin. Use of an external reference allows multiple DDC101s to use the same system reference for optimum channel matching. The external reference should be filtered to minimize noise contribution (see Figure 24).                                                                                                                                                                                                                                                                                                                                                                                              |

| 24            | REFERENCE              | An external capacitor of 10µF should be connected to this node to provide proper operation of the internal BUFFER BYPASS D/A converter. The REFERENCE In pin is connected to an internal reference buffer amplifier. The internal reference buffer drives the internal CDAC. This buffer output is not intended for external use.                                                                                                                                                                                                                                                                                                                                                 |

# SECTION 4 TIMING CHARACTERISTICS

All specifications with Unipolar input range,  $T_{INT}$  = 1ms, Current Input, Correlated Double Sampling enabled, Sys Clock = 2MHz,  $V_{REF}$  = -2.5V,  $T_A$  = +25°C and  $V_S$  = ±5VDC, unless otherwise noted.

| SYMBOL          | DESCRIPTION                                                            | MIN                     | TYP | MAX                           | UNITS   |

|-----------------|------------------------------------------------------------------------|-------------------------|-----|-------------------------------|---------|

| t <sub>1</sub>  | FDS Setup                                                              | 30                      |     |                               | ns      |

| t <sub>2</sub>  | FDS width, Continuous Conversion                                       | 50                      | (M- | ·1) Clocks+t <sub>1</sub> +10 | 00ns ns |

| t <sub>3</sub>  | FDS width, Asynchronous Conversion                                     | M Clocks+t <sub>1</sub> |     |                               | ns      |

| t <sub>4</sub>  | FDS HIGH to start of next integration, Asynchronous Conversion         |                         | 50  |                               | ns      |

| t <sub>5</sub>  | Setup time for RESET SETUP HIGH to DATA CLOCK HIGH                     | 60                      |     |                               | ns      |

| t <sub>6</sub>  | Setup time for Setup Codes data valid before rising edge of DATA Clock | 30                      |     |                               | ns      |

| t <sub>7</sub>  | Hold time for Setup Codes data valid after rising edge of DATA Clock   | 30                      |     |                               | ns      |

| t <sub>8</sub>  | Propagation delay from rising edge of SYSTEM CLOCK to DATA VALID LOW   |                         | 50  |                               | ns      |

| t <sub>9</sub>  | Propagation delay from DATA TRANSMIT LOW to DATA VALID HIGH            |                         | 35  |                               | ns      |

| t <sub>10</sub> | Setup time for DATA CLOCK LOW to DATA TRANSMIT LOW                     | 30                      |     |                               | ns      |

| t <sub>11</sub> | Propagation delay from DATA TRANSMIT LOW to valid data out             |                         | 30  |                               | ns      |

| t <sub>12</sub> | Hold time that Data output is valid after falling edge of DATA CLOCK   | 10                      |     |                               | ns      |

| t <sub>13</sub> | Propagation delay from DATA TRANSMIT HIGH to Data Output tri-stated    |                         |     | 40                            | ns      |

| t <sub>14</sub> | Propagation delay from falling edge of SYSTEM CLOCK to OVERFLOW+ and   | 25                      |     |                               | ns      |

|                 | OVERFLOW-cleared                                                       |                         |     |                               |         |

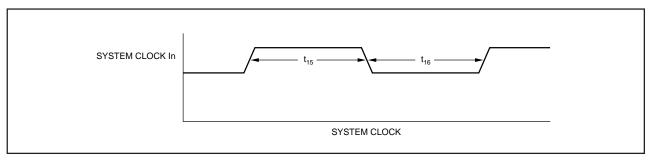

| t <sub>15</sub> | SYSTEM CLOCK pulse width HIGH                                          | 240                     |     |                               | ns      |

| t <sub>16</sub> | SYSTEM CLOCK pulse width LOW                                           | 240                     |     |                               | ns      |

| t <sub>17</sub> | DATA VALID LOW to DATA TRANSMIT LOW, Single DDC101                     | 30                      |     | (LxN-21) Clock                | s ns    |

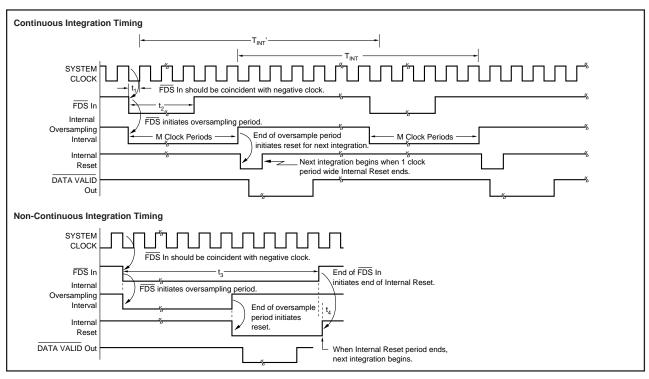

FIGURE 4. Conversion Timing Diagrams.

FIGURE 5. Input/Output Timing Diagram—SETUP Timing Diagram.

FIGURE 6. DATA TRANSMIT Timing Diagram.

#### **TIMING DIAGRAMS (CONT)**

FIGURE 7. OVERFLOW Out Monitoring Timing Diagram.

FIGURE 8. System Clock Timing.

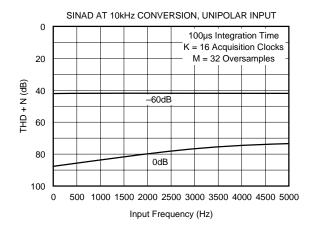

#### **TYPICAL PERFORMANCE CURVES**

#### **ELECTRICAL**

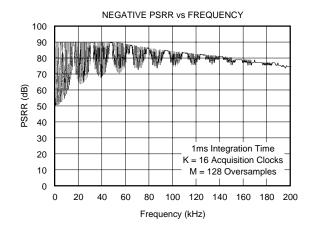

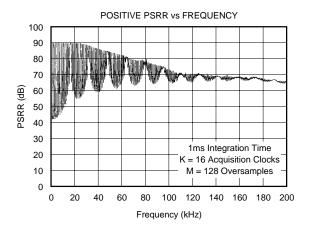

System Clock = 2MHz,  $V_S = \pm 5$ VDC,  $V_{REF} = -2.5$ V, L = 1 Integration/Conversion, and  $T_A = +25$ °C, unless otherwise noted.

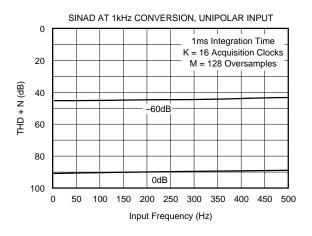

## TYPICAL PERFORMANCE CURVES (CONT)

#### **ELECTRICAL**

System Clock = 2MHz,  $V_S = \pm 5$ VDC,  $V_{REF} = -2.5$ V, L = 1 Integration/Conversion, and  $T_A = +25$ °C, unless otherwise noted.

BURR-BROWN®

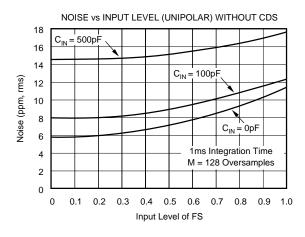

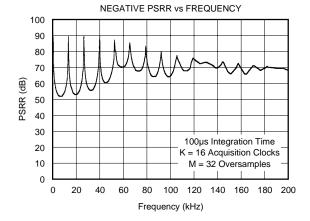

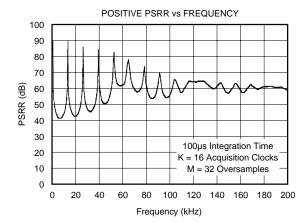

## **TYPICAL PERFORMANCE CURVES (CONT)**

#### **ELECTRICAL**

System Clock = 2MHz,  $V_S = \pm 5$ VDC,  $V_{REF} = -2.5$ V, L = 1 Integration/Conversion, and  $T_A = +25$ °C, unless otherwise noted.

# SECTION 5 DISCUSSION OF SPECIFICATIONS

#### **INPUT**

The DDC101 is a charge digitizing A/D converter. Low level current output sources, such as a photosensors, can be directly connected to its input. The input signal can also be a voltage connected through a user selected resistor.

#### **CHARGE INPUT**

The maximum charge that can be captured in one integration by the DDC101 is 500pC. In the unipolar input range mode, the maximum positive charge that can be collected in one integration is 500pC. The DDC101 has a small negative range in the unipolar mode of –1.95pC. This small negative underrange is included to allow for a small amount of leakage current from the user's PC board and sensor. In the bipolar input range, the maximum positive charge that can be collected is +250pC. The maximum negative charge that can be collected is –251.95pC.

In addition to the normal mode of one integration per conversion, DDC101 can be configured by the user for 1 to 256 integrations per conversion. When the multiple integrations per conversion mode is chosen, the DDC101 DSP circuitry internally averages multiple integration cycles to provide one conversion result. This result has lower noise because it is the average of multiple integrations. In this mode, the maximum total charge that can be captured by the DDC101 in 256 integrations is 128,000pC.

#### **TEST CURRENT INPUT**

An internal DC test current can be connected under user control to the DDC101's input. The test current is nominally 100nA and will be summed with any applied external input signal. It is derived by a resistive network from the positive power supply. The test current is intended to test for functionality only. The TEST In pin of the DDC101 controls the current. When TEST is HIGH, the internal current source is ON and current is flowing into the DDC101 input. When TEST is LOW, the current source is disconnected from the input. With TEST active, positive power supply current increases by approximately 1mA.

#### **FULL SCALE RANGE**

The full scale range (FSR), which is referenced in the specification table, is the difference between the positive full scale charge and the negative full scale charge for the DDC101 in one integration cycle. Specifications such as noise and linearity, which are specified in percent or ppm of FSR, are referring to a value of 500pC for both unipolar and bipolar input ranges.

The full scale input current for a given integration time will result in a full scale input charge. As an example for unipolar

input range, an input current of  $0.5\mu A$  integrated for 1ms will result in the full scale charge of 500pC. For voltage inputs, the input resistor is chosen to achieve the proper full scale input current. As an example, for a 5V full scale input, a  $10M\Omega$  input resistor is selected to achieve a full scale input current of  $0.5\mu A$  (1ms integration time).

Noise of 1.6ppm of FSR is equal to 1.6ppm x 500pC = 0.8fC or 1.6ppm x  $0.5\mu A = 0.8pA$  or 1.6ppm x  $5V = 8\mu V$ . Thus, in this instance, noise is 1.6pA or  $8\mu V$ .

For the unipolar input range, the following table shows the full scale input current required for different integration times to collect 500pC of charge and the equivalent current values for 2 and 5ppm of FSR.

| T <sub>INT</sub> | I <sub>FS</sub> | 2ppm   | 5ppm  |

|------------------|-----------------|--------|-------|

| 50ms             | 10nA            | 0.02pA | 0.5pA |

| 5ms              | 100nA           | 0.2pA  | 1pA   |

| 1ms              | 500nA           | 1pA    | 2.5pA |

| 500μs            | 1μΑ             | 2pA    | 5pA   |

| 100μs            | 5μΑ             | 10pA   | 25pA  |

TABLE I. Integration Time ( $T_{INT}$ ) and Full Scale Current ( $I_{FS}$ ) for Full Scale 500pC Integration.

#### **CURRENT INPUT**

The maximum average input current that can be captured by the DDC101 is  $\pm 7.8 \mu A$ . This current will result in an integration time of  $64 \mu s$  for unipolar input range and  $32 \mu s$  for bipolar input range. For longer integration times, the average input current must be less.

The maximum input current is limited by the slew and update rate of the internal tracking logic and CDAC. The largest input current that the DDC101 can accurately track is 7.8µA. Input currents larger than 7.8µA and high speed current input pulses can be accurately captured and digitized by the DDC101 with an external input or sensor capacitance on the DDC101 input. The average current during a complete integration cycle cannot exceed 7.8µA. Likewise, the total charge input must not exceed 500pC unipolar, 250pC bipolar during the integration time.

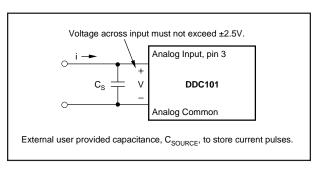

An external user provided input capacitance,  $C_s$ , as shown in Figure 9a, will capture the input signal charge if the input current limit is temporarily exceeded during the integration cycle. The DDC101 will then transfer the charge completely to  $C_{\text{INT}}$  based upon conservation of charge. An additional

FIGURE 9a. Current Pulse Input Capture.

constraint is, the voltage that appears at the DDC101 input, must not exceed 2.5V. If this voltage is exceeded, charge may be lost and the integration result may be invalid. The input voltage can be calculated:

$$i(t) = C_S \frac{dv}{dt}$$

or

$$V = \frac{1}{C_S} \int i(t)dt$$

therefore,

$$V = i \frac{t}{C_S}.$$

As an example, with a user supplied input capacitance of 100pF, a current pulse of 100µA for 2µs could be stored without exceeding 2.5V applied to the input:

$$V = (100\mu A) \bullet \frac{2\mu s}{100pF} = 2V.$$

The current pulse must occur completely during part of one DDC101 integration time, and the DDC101 must still have time to discharge the input capacitance to ground at a maximum rate of 7.8µA before the DDC101 is triggered (through the FDS input) to end the integration. In addition, the total charge integrated must be 500pC or less for the unipolar range. A current pulse of 100µA for 2µs creates 200pC of charge.

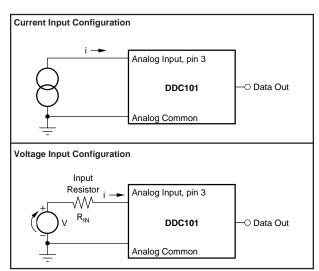

#### **VOLTAGE INPUT SPECIFICATIONS**

The DDC101 is a charge digitizing device. With a user provided input resistor, the DDC101 can digitize voltage inputs. All of the general charge/current input specifications apply to the voltage input situation. The specification table shows the typical noise of the DDC101 including the effects of a 20M $\Omega$  input resistor,  $R_{IN}$ .

The input of the DDC101 is a virtual ground. A voltage input causes a current, i, to flow into the input through R<sub>IN</sub> as shown in Figure 9b. The maximum input current is determined by the integration time selected. Table II shows the

DDC404

BE

FIGURE 9b. DDC101 Input Configurations. Reading Specification.

maximum input voltage based upon several selections of input current and input resistor for unipolar input range. The accuracy of the input resistor will add directly to the DC Gain Error of the DDC101; the drift of the input resistor will add directly to the Gain Drift of the DDC101.

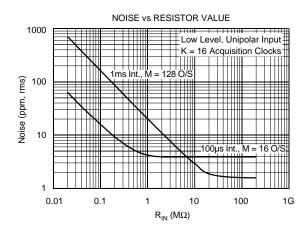

Note that the DDC101 output noise decreases as  $R_{\rm IN}$  increases. This is because the DDC101 noise gain decreases and the input resistance current noise decreases as  $R_{\rm IN}$ increases. This effect is shown in the "Noise vs Resistor Value" typical performance curve.

|                          | INPUT RESISTOR, R <sub>IN</sub> |                       |               |  |  |  |

|--------------------------|---------------------------------|-----------------------|---------------|--|--|--|

| INTEGRATION TIME         | 1ms                             | <b>500</b> μ <b>s</b> | <b>100</b> μs |  |  |  |

| Full Scale Input Current | 0.5μΑ                           | 1μΑ                   | 5μΑ           |  |  |  |

| Full Scale Voltage       |                                 |                       |               |  |  |  |

| 50mV                     | 100kΩ                           | 50kΩ                  | 10kΩ          |  |  |  |

| 500mV                    | 1ΜΩ                             | 500kΩ                 | 100kΩ         |  |  |  |

| 5V                       | 10ΜΩ                            | 5ΜΩ                   | 1ΜΩ           |  |  |  |

| 50V                      | 100ΜΩ                           | 50MΩ                  | 10ΜΩ          |  |  |  |

TABLE II. Example of Input Resistor Values Unipolar Input Range.

#### **UNIPOLAR LINEARITY ERRORS**

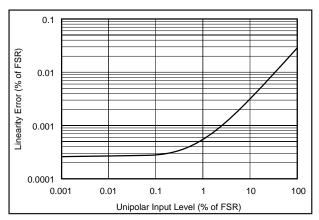

Due to innovative design techniques, the absolute level of linearity error of the DDC101 improves as the input signal level decreases when used in the unipolar input mode. Therefore, in unipolar input mode, the integral linearity of the DDC101 is specified as a small base error plus a percentage of reading error or as a percentage of full scale range. A best-fit straight line method is used to determine integral linearity. Two different best-fit straight lines are used for the two unipolar integral linearity specifications. For bipolar input mode, linearity is specified only as a percentage of full scale range.

To illustrate the improvement in unipolar mode linearity error, Figure 10 shows the maximum unipolar integral linearity error (ILE) of the DDC101 as a function of the input signal level. The maximum integral linearity error is ±0.0244% of reading ±2.5ppm of FSR (ILE max for unipolar input of -1.95 to 0 pc is  $\pm 0.0244\%$  of reading  $\pm 3.0$ ppm of FSR). Thus, the maximum ILE for an input level of 1% of FSR is 0.0005%FSR.

FIGURE 10. Maximum Unipolar Integral Linearity Error Relative to Full-Scale, Converted From % of

#### NOISE

The noise of the DDC101 improves as the input signal level decreases, thus very low level signals can be resolved. Noise is shown in the specification table for low level inputs. For unipolar input range, the DDC101 noise at low level inputs is dominated by comparator noise gained to the output; at full scale inputs, the noise is dominated by D/A converter noise. The noise at low low level inputs is a function of input capacitance; the noise at full scale is relatively independent of input capacitance. For bipolar input operation, the noise is dominated by D/A converter noise and is higher than the full scale unipolar noise.

#### **BIPOLAR INPUT ACCURACY**

Linearity—As a bipolar input device, the linearity of the DDC101 is specified as a percentage of full scale range that does not improve with lower input signal levels. Performance is generally limited by the linearity of the unit when operated in the bipolar input mode.

Noise—In general, noise is not as important as linearity when determining total error. The output noise of the DDC101 in the bipolar mode peaks at midscale (zero input signal level). Output noise is lower for inputs above and below zero.

#### **RESET CHARGE ERROR**

The reset charge error (typically less than 250fC) is an offset error that could result from offset voltage, charge injection and kT/C errors. The DDC101 eliminates the effects of reset charge errors with correlated double sampling.

#### DC BIAS VOLTAGE

The DDC101 generates a small bias voltage (typically  $500\mu V$ ) at the input. This voltage is impressed on any sensor that is connected to the input. The DC bias voltage is the actual virtual ground voltage of the DDC101. The DDC101 input comparator circuitry includes an autozero circuit which eliminates this offset internally so that it does not produce an output error.

#### GAIN SENSITIVITY TO $V_{\rm RFF}$

The DDC101 gain is dependent upon the external reference voltage,  $V_{REF}$ . A change in the value of  $V_{REF}$  will be seen as a directly proportional change in the gain of the DDC101.

#### **FREQUENCY RESPONSE**

The DDC101 is a sampling system whose transfer function has three separate frequency components. These components are multiplied together to make the total frequency characteristic of the DDC101. The three components are:

#### 1. Basic Integration

This is the characteristic  $\sin(x)/x$  response of the basic integration function. This response is controlled by the integration time of the DDC101.

#### 2. Oversampling

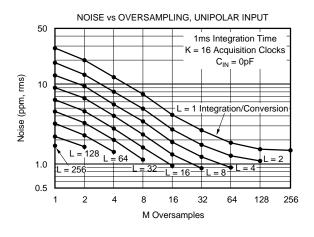

This is the low pass filter characteristic of the digital filter's oversampling. This response reduces the broadband noise in the input signal and the DDC101. Broadband noise decreases as the number of oversamples increases.

#### 3. Multiple Integrations

This is the low pass filter characteristic that results when the digital filter is used to average multiple integrations. This will determine the primary response of the DDC101 if two or more integrations are internally averaged.

See Section 6 for more details.

# SECTION 6 DETAILED THEORY OF OPERATION

#### INTEGRATION CYCLE

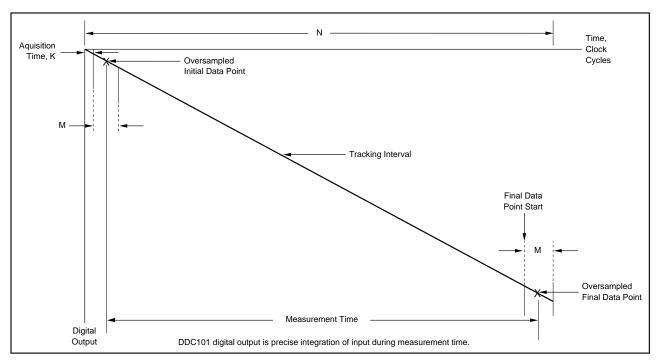

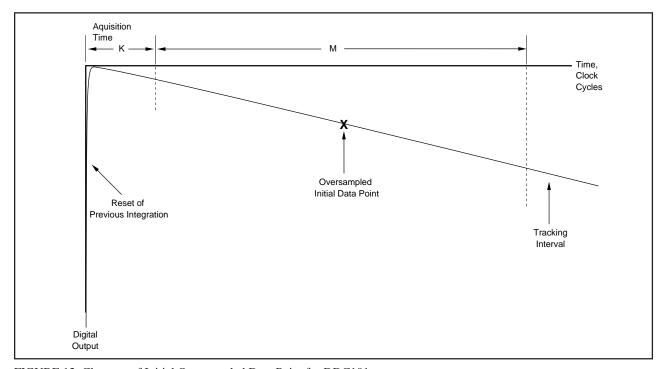

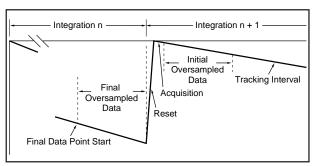

An integration cycle, as illustrated in Figure 11, includes the Acquisition Time, Initial Data Point Sampling, Tracking Interval, and Final Data Point Sampling. The Acquisition Time is K clock periods. The first clock cycle of the Acquisition Time is used to reset the integrating capacitor,  $C_{\rm INT}$ , to zero from the previous integration. The balance of the Acquisition Time insures that the DDC101 system is accurately tracking the input signal prior to initial data point acquisition. Close-ups of the Reset and Acquisition time are shown in Figures 12 and 13.

The Initial Data Point is then sampled M times. The Integration cycle time consists primarily of the Tracking Interval during which time the DDC101 "tracks" the integration of the input signal. The Tracking Interval is followed by the measurement of the Final Data Point with the same user selected number of samples, M. M and K are user selectable. The entire integration cycle consists of N clock periods as controlled by the user.

The DDC101 operates in continuous and non-continuous integration modes. In the continuous mode, one integration follows another with no delay from the end of one integration to the beginning of the next conversion. In the non-continuous mode, each new integration is started separately under user control.

The Final Data point Start (FDS) input is the primary user control of the integration cycle. The FDS input controls the end of one integration cycle and the start of the next integration cycle in both the continuous and non-continuous integration modes. Measurement of the M final data point samples begins when the FDS input is activated.

#### **CONTINUOUS INTEGRATION MODE**

In the continuous integration mode, the "Final Data Point Start" command (using the FDS pin) initiates the measurement of the M final data point samples. The next integration cycle begins immediately after the final data point sampling

FIGURE 11. Equivalent Integrator Output for Single Integration.

FIGURE 12. Close-up of Initial Oversampled Data Point for DDC101.

has been completed; this occurs M clock periods after the FDS transition to "ON". Acquisition, Initial Data Point and Tracking for the next integration follow automatically. The DDC101 continues in the Tracking mode until the next FDS command initiates the measurement of the M final data point samples. An FDS command is needed for each integration cycle. In the continuous integration mode, the FDS pulse width must be less than M clock periods. If the FDS pulse

is held low past this time of M clock periods, the DDC101 will reset as for non-continuous mode (see also Figure 4). In the continuous mode of operation, the tracking logic of the DDC101 "remembers" the integration rate of the previous integration and begins the next integration at the rate of the previous integration. This allows faster acquisition of the signal for the next integration.

FIGURE 13. Close-up of Reset and Acquisition Time for DDC101.

FIGURE 14. Close-up of End of One Integration Cycle and Beginning of Next.

#### NON-CONTINUOUS INTEGRATION MODE

For the non-continuous integration mode, FDS controls the start of the M final data point samples and the end of integration as discussed above. In this mode, however, FDS is also used to control the start of a new integration cycle asynchronously with the end of the previous integration. When FDS transitions to "ON", the collection of the M final data point samples begins. At the end of each integration, the DDC101 automatically resets the integration capacitance. If FDS remains "ON" past the end of integration, the DDC101 will stay in the integration reset state until FDS transitions to "OFF". Holding FDS "ON" past the end of integration will also reset the DDC101's tracking logic to zero integration rate.

In non-continuous integration mode, the initial data point measurement may be less accurate since the DDC101's internal tracking logic is reset at the beginning of the integration and tracking may not be accurate for the initial data point measurement. In this situation, Correlated Double Sampling (CDS) operation may not be advantageous.

#### INTERNAL ERROR CORRECTION

The DDC101 uses CDS techniques to gain optimum performance. CDS removes internal DDC101 errors which occur for a given integration cycle such as, charge injection, kT/C, and DDC101 offset errors. Correlated Double Sampling is user selectable. It is recommended for most continuous measurement applications.

Correlated Double Sampling is implemented in the DDC101 by subtracting the Initial Data Point from the Final Data Point. Thus, the error correction is updated automatically for each integration. When operating in the unipolar input range, CDS functions with either output data format—straight binary or binary two's complement. When operating in the bipolar input range, CDS functions with binary two's complement output data format only.

The errors that CDS removes are charge injection, kT/C and DDC101 input voltage offset. These errors are very difficult to eliminate in equivalent analog circuits. Charge injection errors result from charge that is transferred through the reset switch into the integration capacitor. kT/C errors are switching errors due to the noise of the resistance of the reset switch. DDC101 voltage offset errors are due to input offset of the input comparator. Both initial offset and offset drift with time and temperature are corrected since the correction is performed each integration cycle.

#### SINGLE CYCLE INTEGRATION

The DDC101 acquires charge (q) by integrating input current (i) for a specific time (T). That is,

$$q = \int_{0}^{T} i dt$$

The DDC101 acquires up to 500pC of full scale charge per integration cycle in the unipolar input range, and approximately  $\pm 250$ pC of full scale charge in the bipolar input range. Therefore, for the DDC101, maximum values can be calculated.

$$\begin{array}{ll} \mbox{Unipolar Input Range} & \mbox{Bipolar Input Range} \\ \mbox{500pC} = \mbox{I}_{FS} \ x \ T_{INT} & \pm 250 \mbox{pC} = \pm \mbox{I}_{FS} \ x \ T_{INT} \\ \end{array}$$

Where  $I_{FS}$  is the full scale input current and  $T_{INT}$  is the integration time of the DDC101. Examples of  $I_{FS}$  and  $T_{INT}$  that equal 500pC and  $\pm 250$ pC are shown in the following tables.

The maximum average input current that the DDC101 can integrate is  $7.8\mu A$ . This results in a minimum integration time of  $64\mu s$  for unipolar inputs and  $32\mu s$  for bipolar inputs. Further flexibility is possible with multiple integration cycles per conversion as described in the following text.

#### **INPUT RANGE**

#### **Unipolar Input Range**

For the unipolar input range, the range of charge for each integration cycle is from positive full scale of +500pC to a slightly negative charge of -1/256 (approximately -0.4%) of the positive full scale charge. This is +500pC to -1.95pC. The negative charge measurement capability allows for low level PC board parasitic leakages.

#### **Bipolar Input Range**

For the bipolar input range, the range of charge for each integration cycle is from positive full scale of +250pC to negative full scale of -251.95pC.

| I <sub>FS</sub> | T <sub>INT</sub> |

|-----------------|------------------|

| 1nA             | 500ms            |

| 10nA            | 50ms             |

| 100nA           | 5ms              |

| 1μΑ             | 500μs            |

| 5μΑ             | 100μs            |

| 7.8µA           | 64μs             |

TABLE III. Input Current vs Integration Time Examples for Maximum Charge. Unipolar input range maximum charge = 500pC.

| ±I <sub>FS</sub> | T <sub>INT</sub> |

|------------------|------------------|

| 1nA              | 250ms            |

| 10nA             | 25ms             |

| 100nA            | 2.5ms            |

| 1μΑ              | 250μs            |

| 2.5μΑ            | 100μs            |

| 7.8μΑ            | 32µs             |

TABLE IV. Input Current vs Integration Time Examples for Maximum Charge. Bipolar input range maximum charge = ±250pC.

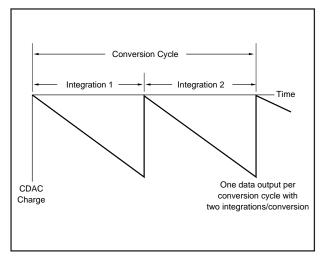

## MULTIPLE INTEGRATIONS PER CONVERSION CYCLE

If more than 500pC, unipolar (or ±250pC, bipolar) of charge must be integrated in one conversion cycle, the DDC101 can be user programmed for multiple integrations per conversion cycle. This feature can be used to provide for longer conversion periods for a specific input current other than shown in the previous table. The integration cycles forming a conversion cycle may be continuous or non-continuous. The number of integrations per conversion cycle, L, can be 1, 2, 4, 8, 16, 32, 64, 128, or 256. The multiple integrations are automatically averaged in the DDC101 so that one conversion result is output per total conversion cycle. Note that each integration requires individual control by the FDS signal. For example, if L = 4, then four FDS signals per conversion are required.

#### FINAL DATA POINT CONFIGURATION LIMITS

In each conversion cycle, the maximum number of final data points which can be collected is 256. This means that at the extremes, the DDC101 can be setup to perform one integration cycle with 256 oversamples, or the DDC101 can be setup to perform 256 integration cycles with one sample per integration cycle. The total number of integrations, L, multiplied by the number of samples per final data point, must be 256 or less. As an example, if 16 integration cycles, L, are used, the number of samples per final data point must be 16 or less.

NOTE: When CDS is used, the initial data points impose no additional conversion sampling limitations.

#### FREQUENCY RESPONSE

The DDC101 charge digitizing A/D Converter is a sampled system whose frequency response has three separate components. These components are multiplied together to make the total frequency characteristic of the DDC101. The three frequency response components are shown below. Each

FIGURE 15. Conversion Cycle with Two Integrations.

| INTEGRATIONS<br>PER CONVERSION | I <sub>FS</sub> | CONVERSION<br>TIME | MAX CHARGE/<br>CONVERSION |

|--------------------------------|-----------------|--------------------|---------------------------|

| L = 1                          | 10nA            | 50ms               | 500pC                     |

| L = 2                          | 10nA            | 100ms              | 1000pC                    |

| L = 4                          | 10nA            | 200ms              | 2000pC                    |

| L = 8                          | 10nA            | 400ms              | 4000pC                    |

| L = 16                         | 10nA            | 800ms              | 8000pC                    |

| L = 32                         | 10nA            | 1.6s               | 16000pC                   |

| L = 64                         | 10nA            | 3.2s               | 32000pC                   |

| L = 128                        | 10nA            | 6.4s               | 64000pC                   |

| L = 256                        | 10nA            | 12.8s              | 128000pC                  |

TABLE V. Integrations/Conversion vs Conversion Time. Example for multiple integrations with unipolar input range.

individual component has a sinc (sinx/x) frequency response function.

#### 1. Basic Integration

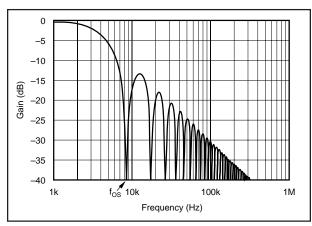

This is the characteristic  $\sin(x)/x$  response of the basic integration function. This response is controlled by the measurement time of the DDC101,  $T_{\text{MEAS}}$ ; see Figure 16.

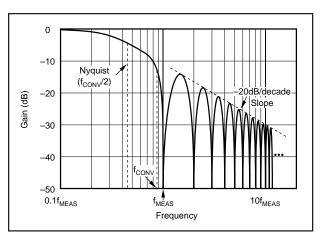

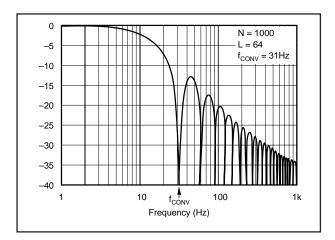

#### 2. Oversampling

This is the low pass filter characteristic of the digital filter's oversampling. This response reduces the broadband noise in the input signal of the DDC101. Broadband noise decreases as the number of oversamples increases. This response is controlled by the number of oversamples, M; see Figure 17.

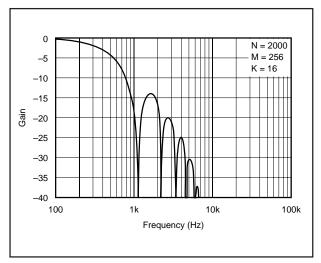

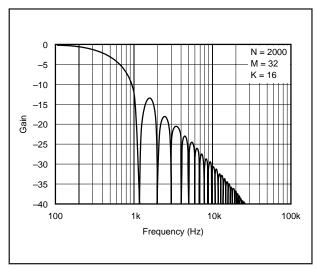

#### 3. Multiple Integrations

This is the low pass filter characteristic that results when the digital filter is used to average multiple integrations. This will determine the primary response of the DDC101 if two or more integrations are internally averaged. This response is controlled by the total conversion time of the DDC101; see Figure 18.

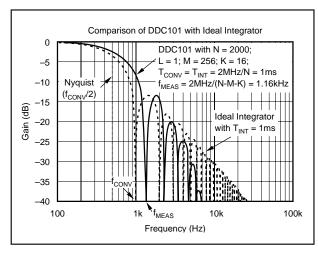

Input frequencies are multiplied by the DDC101 frequency response. The Nyquist frequency is  $f_{CONV}/2$ , where  $f_{CONV}$  is the DDC101 conversion rate. The highest frequency that can be reconstructed from the output data is  $f_{CONV}/2$ . Input frequencies above Nyquist are multiplied by the DDC101 frequency response and are then aliased into DC to  $f_{CONV}/2$ .

#### **Basic Integration Frequency Response**

The  $\sin(x)/x$  basic integration characteristic is controlled by the digital filter's measurement time ( $T_{\rm MEAS}$ ). The measurement frequency,  $f_{\rm MEAS}$  is  $I/T_{\rm MEAS}$ . The input frequency response of the DDC101 is down –3dB at  $f_{\rm MEAS}/2.26$  with a null at  $f_{\rm MEAS}$ . Subsequent nulls are at harmonics  $2f_{\rm MEAS}$ ,  $3f_{\rm MEAS}$ ,  $4f_{\rm MEAS}$ , etc. as shown in the frequency response curve below. This characteristic is often used to eliminate known interference by setting  $f_{\rm MEAS}$  or a harmonic to exactly the frequency of the interference. Table VI illustrates the frequency characteristics of the DDC101 integration function for various measurement times. As an example, for N = 2272, K = 16, and M = 256:  $T_{\rm MEAS} = (N-M-K)/f_{\rm CLK} = (2272-256-16)/2MHz = 1$ ms and  $f_{\rm MEAS} = 1$ kHz.  $T_{\rm INT} = 2272/2$ MHz = 1.14ms;  $f_{\rm CONV} = I/T_{\rm INT} = 880$ Hz.

| MEASUREMENT TIME | -3dB FREQUENCY | f <sub>meas</sub> |

|------------------|----------------|-------------------|

| 100μs            | 4.42kHz        | 10kHz             |

| 1ms              | 442Hz          | 1kHz              |

| 10ms             | 44.2Hz         | 100Hz             |

| 16.66ms          | 26.5Hz         | 60Hz              |

| 20ms             | 22.1Hz         | 50Hz              |

TABLE VI. Basic Integration Frequency Response Examples.

#### **Oversampling Frequency Response**