SBOS229B - DECEMBER 2001 - REVISED JUNE 2003

# **192kHz Digital Audio Transmitter**

# FEATURES

- COMPLIANT WITH AES-3, IEC-60958, AND EIAJ CP1201 INTERFACE STANDARDS

- SUPPORTS SAMPLING RATES UP TO 192kHz

- SUPPORTS MONO-MODE OPERATION

- ON-CHIP DIFFERENTIAL LINE DRIVER

- FLEXIBLE AUDIO SERIAL INTERFACE: -Master or Slave Mode Operation -Supports I<sup>2</sup>S, Left-Justified, and Right-Justified Data Formats

- SOFTWARE MODE VIA SERIAL CONTROL INTERFACE:

Block Sized Buffer for Channel Status Data

Auto Increment Mode for Block Sized Write and Read Operations

- HARDWARE MODE ALLOWS OPERATION WITHOUT A MICROCONTROLLER

- CRC CODE GENERATION FOR PROFESSIONAL MODE

- MASTER CLOCK RATE: 128f<sub>S</sub>, 256f<sub>S</sub>, 384f<sub>S</sub>, or 512f<sub>S</sub>

- +5V CORE SUPPLY (V<sub>DD</sub>)

- +2.7V TO V<sub>DD</sub> LOGIC I/O SUPPLY (V<sub>IO</sub>)

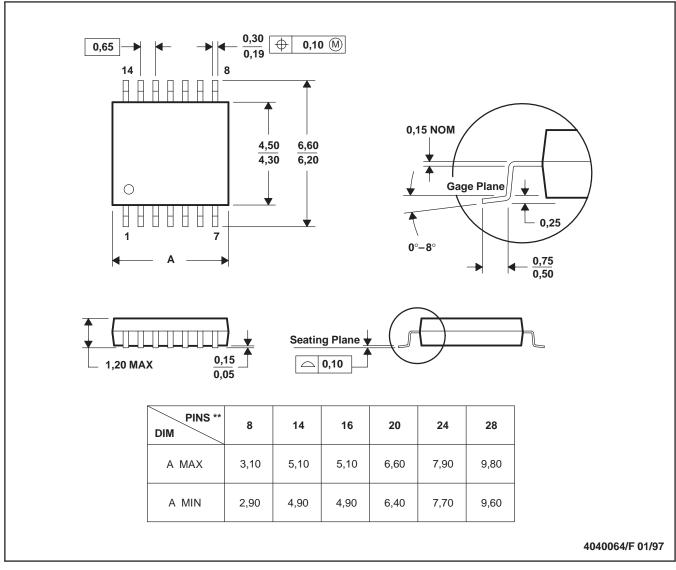

- PACKAGE: TSSOP-28

# **APPLICATIONS**

- DIGITAL MIXING CONSOLES

- DIGITAL MICROPHONES

- DIGITAL AUDIO WORKSTATIONS

- BROADCAST STUDIO EQUIPMENT

- EFFECTS PROCESSORS

- SURROUND-SOUND DECODERS AND ENCODERS

- A/V RECEIVERS

- DVD, CD, DAT, AND MD PLAYERS

- AUDIO TEST EQUIPMENT

# DESCRIPTION

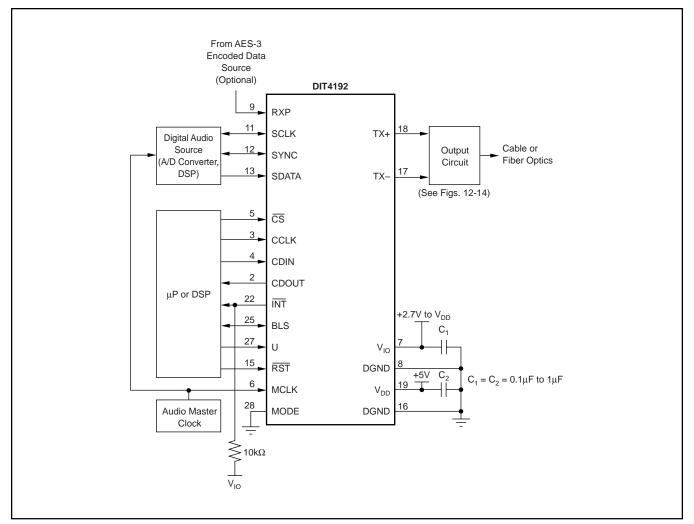

The DIT4192 is a digital audio transmitter designed for use in both professional and consumer audio applications. Transmit data rates up to 192kHz are supported. The DIT4192 supports both software and hardware operation, which makes it suitable for applications with or without a microcontroller. A flexible serial audio interface is provided, supporting standard audio data formats and easy interfacing to audio DSP serial ports.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Power-Supply Voltage, V <sub>DD</sub> | +6.5V                            |

|---------------------------------------|----------------------------------|

| V <sub>IO</sub>                       | +6.5V                            |

| Input Current                         | ±10mA                            |

| Digital Input Voltage                 | 0.2V to +5.5V                    |

| Digital Output Voltage                | 0.2V to (V <sub>DD</sub> + 0.2V) |

| Power Dissipation                     | 300mW                            |

| Operating Temperature Range           | –40°C to + 85°C                  |

| Storage Temperature                   | 55°C to +125°C                   |

| Lead Temperature (soldering, 5s)      | +260°C                           |

| Package Temperature (IR re-flow, 10s) | +235°C                           |

NOTE: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# PACKAGE/ORDERING INFORMATION

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|--------------|--------------------------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| DIT4192 | TSSOP-28     | PW                                   | −40°C to +85°C                    | DIT4192IPW         | DIT4192IPW         | Rails, 50                    |

| "       | "            | "                                    | "                                 | "                  | DIT4192IPWR        | Tape and Reel, 2000          |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

# **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A$  = +25°C,  $V_{DD}$  = +5V, and  $V_{IO}$  = 3.3V unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          | DIT4192IPW                                          |                                                                         |                                                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MIN                                                      | ТҮР                                                 | MAX                                                                     | UNITS                                                            |  |

| DIGITAL CHARACTERISTICS<br>Applies to All Digital I/O Except TX+ and TX–<br>High-Level Input Voltage, V <sub>IH</sub><br>Low-Level Input Voltage, V <sub>IL</sub><br>High-Level Output Voltage, V <sub>OH</sub><br>Low-Level Output Voltage, V <sub>OL</sub><br>Input Leakage Current                                                                                                                                                                                  | I <sub>O</sub> = -4mA<br>I <sub>O</sub> = +4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.7 • V <sub>IO</sub><br>0<br>0.8 • V <sub>IO</sub><br>0 | 1                                                   | V <sub>IO</sub><br>0.2 • V <sub>IO</sub><br>0.1 • V <sub>IO</sub><br>10 | V<br>V<br>V<br>μΑ                                                |  |

| OUTPUT DRIVER CHARACTERISTICS<br>Applies Only to TX+ and TX–<br>High-Level Output Voltage, V <sub>OH</sub><br>Low-Level Output Voltage, V <sub>OL</sub>                                                                                                                                                                                                                                                                                                                | I <sub>O</sub> = -30mA<br>I <sub>O</sub> = +30mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>DD</sub> - 0.7<br>0                               | V <sub>DD</sub> - 0.4<br>0.4                        | V <sub>DD</sub><br>0.7                                                  | V<br>V                                                           |  |

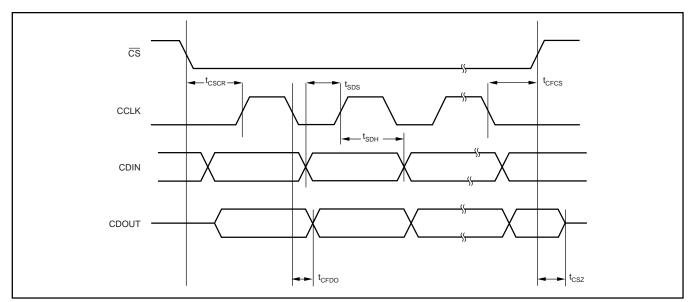

| SWITCHING CHARACTERISTICS<br>Master Clock and Reset<br>Master Clock (MCLK) Frequency<br>Master Clock (MCLK) Duty Cycle<br>Reset (RST) Active Low Pulse Width<br>Serial Control Port Timing                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>500                                                |                                                     | 25<br>60                                                                | MHz<br>%<br>ns                                                   |  |

| CCLK Frequency<br>Stereo Mode<br>Mono Mode<br>Serial Control Data Setup Time, t <sub>SDS</sub><br>Serial Control Data Hold Time, t <sub>SDH</sub><br>CS Falling to CCLK Rising, t <sub>CSCR</sub><br>CCLK Falling to CS Rising, t <sub>CFCS</sub><br>CCLK Falling to CDOUT Data Valid, t <sub>CFDO</sub>                                                                                                                                                               | f <sub>S</sub> = Sampling Frequency<br>f <sub>S</sub> = Sampling Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12<br>8<br>15<br>12                                      |                                                     | 128 • f <sub>S</sub><br>64 • f <sub>S</sub><br>12                       | MHz<br>MHz<br>ns<br>ns<br>ns<br>ns<br>ns                         |  |

| CS Rising to CDOUT High Impedance, t <sub>CSZ</sub> Audio Serial Interface Timing     SYNC Frequency (or Frame Rate)     SYNC Clock Period t <sub>SYNCP</sub> SYNC High/Low Pulse Width, t <sub>SYNCHL</sub> SCLK Frequency     SCLK Clock Period, t <sub>SCLKP</sub> SCLK High/Low Pulse Width, t <sub>SCLKHL</sub> SYNC Edge to SCLK Edge, t <sub>SYSK</sub> Audio Data Setup Time, t <sub>ADS</sub> Audio Data Hold Time, t <sub>ADH</sub> C, U, and V Input Timing |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.12<br>2.56<br>40<br>18<br>15<br>15<br>15<br>15         |                                                     | 10<br>195.3050<br>25                                                    | ns<br>kHz<br>μs<br>MHz<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |  |

| C/U/V Data Setup Time, t <sub>CUVS</sub><br>C/U/V Data Hold Time, t <sub>CUVH</sub>                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15<br>15                                                 |                                                     |                                                                         | ns<br>ns                                                         |  |

| POWER-SUPPLY<br>Operating Voltage<br>V <sub>DD</sub><br>V <sub>IO</sub>                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | +4.5<br>+2.7                                             | +5                                                  | +5.5<br>V <sub>DD</sub>                                                 | V<br>V                                                           |  |

| Supply Current<br>I <sub>DD</sub> , Quiescent<br>I <sub>DD</sub> , Power-Down Mode<br>I <sub>DD</sub> , Dynamic (at 192kHz operation)<br>I <sub>IO</sub> , Quiescent<br>I <sub>IO</sub> , Power-Down Mode<br>I <sub>IO</sub> , Power-Down Mode<br>I <sub>IO</sub> , Quiescent<br>I <sub>IO</sub> , Quiescent<br>I <sub>IO</sub> , Dynamic (at 192kHz operation)                                                                                                        | $V_{DD} = +5V \\ V_{DD} = +5V \\ V_{DD} = +5V \\ V_{IO} = +3.3V \\ V_{IO} = +3.3V \\ V_{IO} = +3.3V \\ V_{IO} = +5V $ |                                                          | 25<br>2<br>30<br>15<br>15<br>1.5<br>250<br>250<br>3 |                                                                         | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ                     |  |

| Power Dissipation<br>PD, Quiescent<br>PD, Power-Down Mode<br>PD, Dynamic (at 192kHz operation)                                                                                                                                                                                                                                                                                                                                                                         | $V_{DD} = +5V$<br>$V_{DD} = +5V$<br>$V_{DD} = +5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          | 100<br>100<br>175                                   |                                                                         | μW<br>μW<br>mW                                                   |  |

| TEMPERATURE RANGE<br>Operating Range<br>Storage Range                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -40<br>-55                                               |                                                     | +85<br>+125                                                             | °C<br>°C                                                         |  |

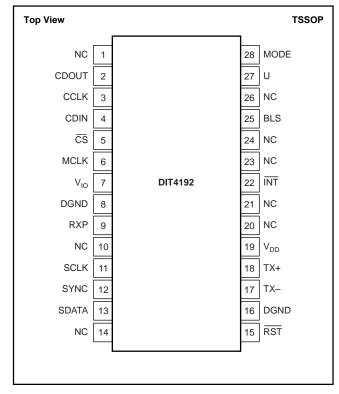

# PIN CONFIGURATION: Software Mode (MODE = 0)

## **PIN DESCRIPTIONS: Software Mode**

| PIN | NAME            | PIN DESCRIPTION                                                                                        |

|-----|-----------------|--------------------------------------------------------------------------------------------------------|

| 1   | NC              | No Connection                                                                                          |

| 2   | CDOUT           | Control Port Data Output, Tri-State                                                                    |

| 3   | CCLK            | Control Port Data Clock Input                                                                          |

| 4   | CDIN            | Control Port Serial Data Input                                                                         |

| 5   | CS              | Control Port Chip Select Input, Active LOW                                                             |

| 6   | MCLK            | Master Clock Input                                                                                     |

| 7   | V <sub>IO</sub> | Digital I/O Power Supply, +2.7V to V <sub>DD</sub><br>Nominal                                          |

| 8   | DGND            | Digital Ground                                                                                         |

| 9   | RXP             | AES-3 Encoded Data Input                                                                               |

| 10  | NC              | No Connection                                                                                          |

| 11  | SCLK            | Audio Serial Port Data Clock I/O                                                                       |

| 12  | SYNC            | Audio Serial Port Frame SYNC Clock I/O                                                                 |

| 13  | SDATA           | Audio Serial Port Data Input                                                                           |

| 14  | NC              | No Connection                                                                                          |

| 15  | RST             | Reset Input, Active LOW                                                                                |

| 16  | DGND            | Digital Ground                                                                                         |

| 17  | TX–             | Transmitter Line Driver Output                                                                         |

| 18  | TX+             | Transmitter Line Driver Output                                                                         |

| 19  | V <sub>DD</sub> | Digital Core Power Supply, +5V Nominal                                                                 |

| 20  | NC              | No Connection                                                                                          |

| 21  | NC              | No Connection                                                                                          |

| 22  | INT             | Open Drain Interrupt Output, Active LOW.<br>Requires $10k\Omega$ pull-up resistor to V <sub>IO</sub> . |

| 23  | NC              | No Connection                                                                                          |

| 24  | NC              | No Connection                                                                                          |

| 25  | BLS             | Block Start I/O                                                                                        |

| 26  | NC              | No Connection                                                                                          |

| 27  | U               | User Data Input                                                                                        |

| 28  | MODE            | Control Mode Input. Set MODE = 0 for Software Mode operation.                                          |

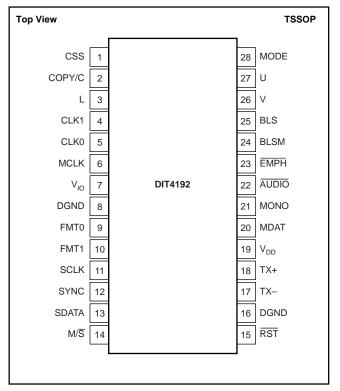

## **PIN DESCRIPTIONS: Hardware Mode**

| PIN | NAME            | PIN DESCRIPTION                                               |

|-----|-----------------|---------------------------------------------------------------|

| 1   | CSS             | Channel Status Data Mode Input                                |

| 2   | COPY/C          | Copy Protect Input or Channel Status Se-                      |

|     |                 | rial Data Input                                               |

| 3   | L               | Generation Status Input                                       |

| 4   | CLK1            | Master Clock Rate Selection Input                             |

| 5   | CLK0            | Master Clock Rate Selection Input                             |

| 6   | MCLK            | Master Clock Input                                            |

| 7   | V <sub>IO</sub> | Digital I/O Power Supply, +2.7V to V <sub>DD</sub>            |

|     |                 | Nominal                                                       |

| 8   | DGND            | Digital Ground                                                |

| 9   | FMT0            | Audio Data Format Control Input                               |

| 10  | FMT1            | Audio Data Format Control Input                               |

| 11  | SCLK            | Audio Serial Port Data Clock I/O                              |

| 12  | SYNC            | Audio Serial Port Frame SYNC Clock I/O                        |

| 13  | SDATA           | Audio Serial Port Data Input                                  |

| 14  | M/S             | Audio Serial Port Master/Slave Control Input                  |

| 15  | RST             | Reset Input, Active LOW                                       |

| 16  | DGND            | Digital Ground                                                |

| 17  | TX–             | Transmitter Line Driver Output                                |

| 18  | TX+             | Transmitter Line Driver Output                                |

| 19  | VDD             | Digital Core Power-Supply, +5V Nominal                        |

| 20  | MDAT            | Mono Mode Channel Data Selection Input                        |

| 21  | MONO            | Mono Mode Enable Input, Active HIGH                           |

| 22  | AUDIO           | Audio Data Valid Control Input, Active LOW                    |

| 23  | EMPH            | Pre-Emphasis Status Input, Active LOW                         |

| 24  | BLSM            | Block Start Mode Control Input                                |

| 25  | BLS             | Block Start I/O                                               |

| 26  | V               | Validity Data Input                                           |

| 27  | U               | User Data Input                                               |

| 28  | MODE            | Control Mode Input. Set MODE = 1 for Hardware Mode Operation. |

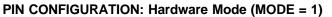

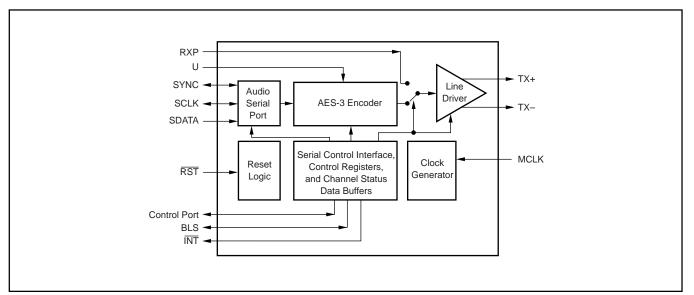

# **GENERAL DESCRIPTION**

The DIT4192 is a complete digital audio transmitter, suitable for both professional and consumer audio applications. Sampling rates up to 192kHz are supported. The DIT4192 complies with the requirements for the AES-3, IEC-60958, and EIAJ CP1201 interface standards.

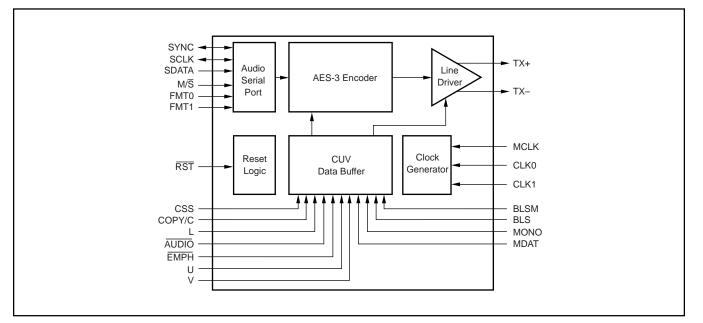

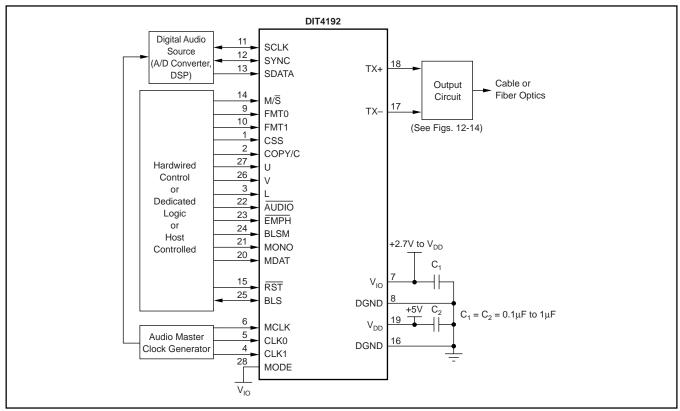

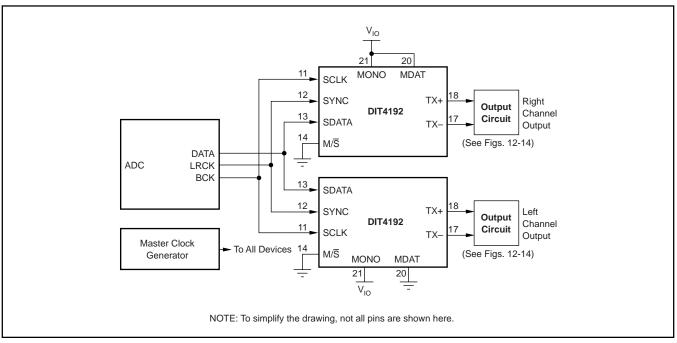

Figures 1 and 2 show the block diagrams for the DIT4192 when used in Software and Hardware control modes. The MODE input (pin 28) determines the control model used to configure the DIT4192 internal functions. In Software mode, a serial control port is used to write and read on-chip control registers and status buffers. In Hardware mode, dedicated control pins are provided for configuration and status inputs.

The DIT4192 includes an audio serial port, which is used to interface to standard digital audio sources, such as

Analog-to-Digital (A/D) converters, Digital Signal Processors (DSPs), and audio decoders. Support for Left-Justified, Right-Justified, and I<sup>2</sup>S data formats is provided.

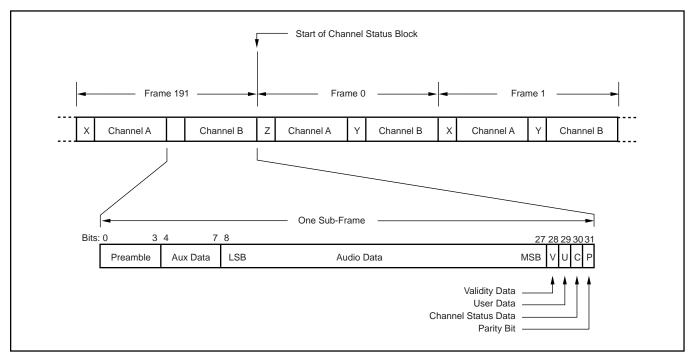

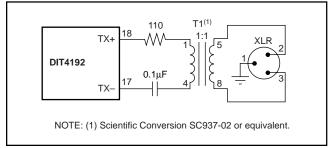

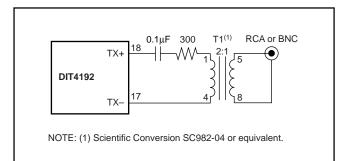

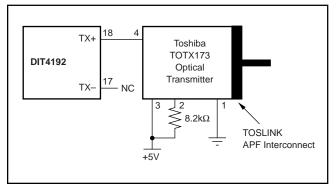

The AES-3 encoder creates a multiplexed bit stream, containing audio, status, and user data. See Figure 3 for the multiplexed data format. The data is then Bi-Phase Mark encoded and output to a differential line driver. The line driver outputs are connected to the transmission medium, be it cable or fiber optics. In the case of twisted-pair or coaxial cable, a transformer is commonly used to couple the driver outputs to the transmission line. This provides both isolation and improved common-mode rejection. For optical transmission, the TX+ (pin 18) driver output is connected to an optical transmitter module. See the Applications Information section of this data sheet for details regarding output driver circuit configurations.

FIGURE 1. Software Mode Block Diagram.

FIGURE 2. Hardware Mode Block Diagram.

FIGURE 3. AES-3 Frame Format.

# **MASTER CLOCK**

The DIT4192 requires a master clock for operation. This clock must be supplied at the MCLK input (pin 6). The maximum master clock frequency that may be supplied to MCLK is 25MHz. Table I shows master clock rates for common input sampling frequencies.

| SAMPLING        | MAST                 | (MHz)                |                      |                      |

|-----------------|----------------------|----------------------|----------------------|----------------------|

| FREQUENCY (kHz) | 128 • f <sub>S</sub> | 256 • f <sub>S</sub> | 384 • f <sub>S</sub> | 512 • f <sub>S</sub> |

| 22.05           | n/a                  | 5.6448               | 8.4672               | 11.2896              |

| 24              | n/a                  | 6.144                | 9.216                | 12.288               |

| 32              | n/a                  | 8.192                | 12.288               | 16.384               |

| 44.1            | n/a                  | 11.2896              | 16.9344              | 22.5792              |

| 48              | n/a                  | 12.288               | 18.432               | 24.576               |

| 88.2            | n/a                  | 22.5792              | n/a                  | n/a                  |

| 96              | n/a                  | 24.576               | n/a                  | n/a                  |

| 176.4           | 22.5792              | n/a                  | n/a                  | n/a                  |

| 192             | 24.576               | n/a                  | n/a                  | n/a                  |

TABLE I. Master Clock Frequencies for Common Sampling Rates.

For Software mode, the master clock frequency selection is programmed using the CLK0 and CLK1 bits in Control Register  $02_{\rm H}$ . For Hardware mode, the CLK0 (pin 5) and CLK1 (pin 4) inputs are used to select the master clock frequency. Table II shows the available MCLK frequency selections.

| CONTROL BITS OR INPUT PINS |   |                               |

|----------------------------|---|-------------------------------|

| CLK1 CLK0                  |   | MASTER CLOCK (MCLK) SELECTION |

| 0                          | 0 | 128 • f <sub>S</sub>          |

| 0 1                        |   | 256 • f <sub>S</sub>          |

| 1 0                        |   | 384 • f <sub>S</sub>          |

| 1                          | 1 | 512 • f <sub>S</sub>          |

TABLE II. Master Clock Rate Selection for Software and Hardware Modes.

# RESET AND POWER-DOWN OPERATION

The DIT4192 includes a reset input,  $\overline{RST}$  (pin 15), which is used to force a reset sequence. When the DIT4192 is first powered up, the user must assert  $\overline{RST}$  low in order to start the reset sequence. The  $\overline{RST}$  input must be low for a minimum of 500ns. The  $\overline{RST}$  input is then forced high to enable normal operation. For software mode, the reset sequence will force all internal registers to their default settings. In addition, the reset sequence will force all channel status bits to 0 in Software mode.

While the  $\overrightarrow{RST}$  input is low, the transmitter outputs, TX- (pin 17) and TX+ (pin 18), are forced to ground.

Upon setting  $\overrightarrow{RST}$  high, the TX– and TX+ outputs will remain low until the rising edge of the SYNC clock is detected at pin 12. Once this occurs, the TX– and TX+ outputs will become active and be driven by the output of the AES-3 encoder.

In Software mode, the DIT4192 also includes software reset and power-down bits, located in control register  $02_{H}$ . The software reset bit,  $\overline{\text{RST}}$ , and the software power-down bit, PDN, are both active high.

# AUDIO SERIAL PORT

The audio serial port is a 3-wire interface used to connect the DIT4192 to an audio source, such as an A/D converter or DSP. The port supports sampling frequencies up to 192kHz. The port signals include SDATA (pin 13), SYNC (pin 12), and SCLK (pin 11). The SDATA pin is the serial data input for the port. The SCLK pin may be either an input or output, and is used to clock serial data into the port. The SYNC pin may be either an input or output, and provides the frame synchroni-

zation clock for the port. The SYNC pin is also used as a data latch clock for the channel status, user, and validity data inputs in Hardware mode, and the user data input in Software mode.

# SLAVE OR MASTER MODE OPERATION

The audio serial port supports both Slave and Master mode operation. In Slave mode, both SYNC and SCLK are configured as inputs. The audio source device must generate both the SYNC and SCLK clocks in Slave mode. In Master mode, both SYNC and SCLK are configured as outputs. The audio serial port generates the SYNC and SCLK clocks in Master mode, deriving both from the master clock (MCLK) input.

In Software mode, Master/Slave mode selection is performed using the  $M/\overline{S}$  bit in Control Register  $03_{\rm H}$  (defaults to Slave mode). In Hardware mode, the M/S input (pin 14) is used to select the audio serial port mode. This is shown in Table III.

| CONTROL BITS OR INPUT PIN |                                              |

|---------------------------|----------------------------------------------|

| M/S                       | MASTER/SLAVE MODE SELECTION                  |

| 0                         | Slave Mode, both SYNC and SCLK are inputs.   |

| 1                         | Master Mode, both SYNC and SCLK are outputs. |

TABLE III. Master/Slave Mode Selection for Software or Hardware Mode.

# SYNC AND SCLK FREQUENCIES

The SYNC clock rate is the same as the sampling frequency, or  $f_S$ . This holds true for both Slave and Master modes. The DIT4192 supports SYNC frequencies up to 192kHz.

The SCLK frequency in Slave mode must provide at least one clock cycle for each data bit that is input at SDATA. The maximum SCLK frequency is 128 •  $f_S$ , or 24.576MHz for  $f_S = 192$ kHz. The SCLK frequency in Master mode is set by the DIT4192 itself. For Software mode operation, the SCLK rate may be programmed to either 64 •  $f_S$  or 128 •  $f_S$ , using the SCLKR bit in Control Register 03<sub>HEX</sub>. In Hardware mode, the SCLK frequency is fixed at 64 •  $f_S$  for Master mode.

# AUDIO DATA FORMATS

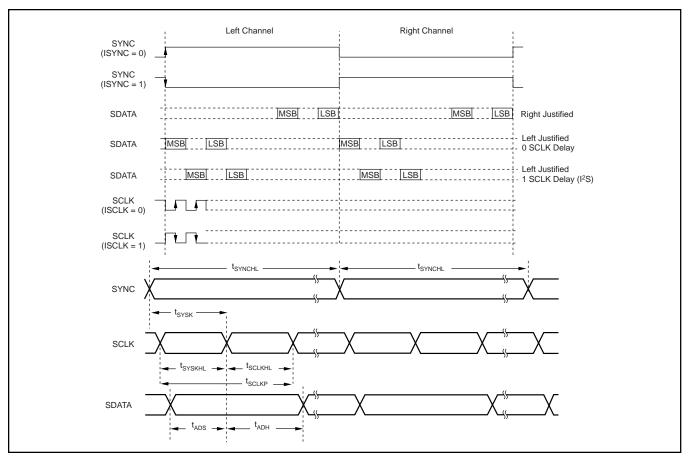

The DIT4192 supports standard audio data formats, including Philips I<sup>2</sup>S, Left-Justified, and Right-Justified data.

Software mode provides the most flexible format selection, while Hardware mode supports a limited subset of the Software mode formats. Linear PCM audio data at the SDATA input is typically presented in Binary Two's Complement, MSB first format. Encoded or non-audio data may be provided as required by the encoding scheme in use. Figure 4 shows the common data formats used by the audio serial port.

FIGURE 4. Audio Data Formats and Timing.

For Software mode, Control Register  $03_H$  is used to set the audio data format selection. Data word length may be set to 16, 18, 20, or 24 bits using the WLEN0 and WLEN1 bits. Several format parameters, including SCLK sampling edge, data delay from the start of frame, and SYNC polarity may be programmed using this register. Table IV shows examples of register bit settings for three standard audio formats. SCLK sampling edges and SYNC polarity may differ from one system implementation to the next. Consult the audio source device data sheet or technical reference for details regarding the output data formatting.

For Hardware mode, the FMT0 (pin 9) and FMT1 (pin 10) inputs are utilized to select one of four audio data formats. Refer to Table V for the available format selections.

| INPUT | PINS |                         |

|-------|------|-------------------------|

| FMT1  | FMT0 | FORMAT SELECTIONS       |

| 0     | 0    | 24-Bit Left-Justified   |

| 0     | 1    | 24-Bit I <sup>2</sup> S |

| 1 0   |      | 24-Bit Right-Justified  |

| 1     | 1    | 16-Bit Right-Justified  |

TABLE V. Audio Data Format Selection for Hardware Mode.

# **AES-3 ENCODER OPERATION**

The AES-3 encoder performs the multiplexing of audio, channel status, user, and validity data. It also performs Bi-Phase Mark encoding of the multiplexed data stream. This section describes how channel status, user, and validity data are input to the encoder function.

# **BLOCK START INPUT/OUTPUT**

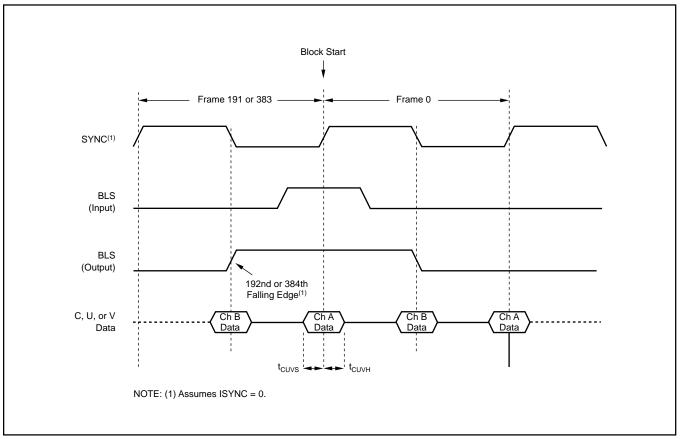

The block start is used to indicate the start of a channel status data block, which starts with Frame 0 for the AES-3 data stream. For the DIT4192, the block start signal BLS (pin 25), may be either an input or output. In Software mode, the direction of BLS is set using the BLSM bit in control register  $01_H$  (defaults to input). In Hardware mode, the direction of BLS is set by the BLSM input (pin 24). If BLSM = 0, the BLS pin is an input. If BLSM = 1, the BLS pin is an output.

For Software mode operation, the block start signal is synchronized to the audio serial port frame sync clock, SYNC (pin 12). When BLS is configured as an input pin, it is sampled on the rising edge of SYNC when the ISYNC bit in control register  $03_{\rm H}$  is set to 0. Otherwise, it is sampled on the falling edge of SYNC when the ISYNC bit is set to 1. If BLS is high when it is sampled, then a block start condition is indicated. When BLS is configured as an output and the ISYNC bit is set to 0, BLS will go high at every 192nd falling edge of SYNC for Stereo mode, or every 384th falling edge of SYNC for Mono mode. BLS will then go low on the following falling edge. If the ISYNC bit is set to 1, then BLS transitions on the rising edge of SYNC.

Hardware mode operation is similar to Software mode operation, with the exception that there are only a limited number of data formats available for the audio serial port. For Leftand Right-Justified formats, BLS behaves as it would in Software mode with ISYNC = 0. For the I<sup>2</sup>S data format, BLS behaves as it would in Software mode with ISYNC = 1.

## CHANNEL STATUS DATA INPUT

Channel status data input is determined by the control mode in use. In Software mode, the channel status data buffer is accessed through the serial control port. Buffer operations are described in detail in the section of this data sheet entitled Channel Status Buffer Operation (Software Mode Only). In Hardware mode, channel status data input is accomplished by one of two user-selectable methods.

# THE CSS INPUT

In Hardware mode, the state of the CSS input (pin 1) determines the function of dedicated channel status inputs. When CSS = 0, the COPY (pin 2), L (pin 3),  $\overline{\text{AUDIO}}$  (pin 22), and  $\overline{\text{EMPH}}$  (pin 23) inputs are used to set associated channel status data bits. The COPY and L inputs are used to set up copy protection for consumer operation, or indicate that the transmitter is operating in professional mode, without copy protection. The  $\overline{\text{AUDIO}}$  input is utilized to indicate whether the data being transmitted is PCM audio data, or non-audio data. The  $\overline{\text{EMPH}}$  input is used to indicate whether the PCM audio data has been pre-emphasized using the 50/15µs standard. See Table VI for the available options for these dedicated channel status inputs.

When CSS = 1, the channel status data is input in a serial fashion at the C input (pin 2). Data is clocked on the rising and falling edges of the SYNC input (pin 12). All channel status data bits can be written in this mode, allowing greater flexibility than the previous Hardware mode case with CSS = 0. See Figure 5 for the C input timing diagram.

|                          |          | CONTROL REGISTER 03 <sub>H</sub> BIT SETTINGS |          |              |          |               |          |             |  |  |

|--------------------------|----------|-----------------------------------------------|----------|--------------|----------|---------------|----------|-------------|--|--|

| AUDIO DATA               | Bit Name | Function                                      | Bit Name | Function     | Bit Name | Function      | Bit Name | Function    |  |  |

| FORMATS                  | JUS      | Justification                                 | DELAY    | SCLK Delay   | ISCLK    | Sampling Edge | ISYNC    | Phase       |  |  |

| Philips I <sup>2</sup> S | 0        | Left-Justified                                | 1        | 1 SCLK Delay | 0        | Rising Edge   | 1        | Inverted    |  |  |

| Left-Justified           | 0        | Left-Justified                                | 0        | 0 SCLK Delay | 0        | Rising Edge   | 0        | Noninverted |  |  |

| Right-Justified          | 1        | Right-Justified                               | 0        | 0 SCLK Delay | 0        | Rising Edge   | 0        | Noninverted |  |  |

TABLE IV. Audio Data Format Selection in Software Mode.

| INPUT | FUNCTION      | FUNCTION                                                                       |                                                            |  |  |  |  |  |

|-------|---------------|--------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| COPY  | Copy Status   | Copy Status                                                                    |                                                            |  |  |  |  |  |

| L     | Generation St | Generation Status                                                              |                                                            |  |  |  |  |  |

|       | COPY          | L                                                                              | Status                                                     |  |  |  |  |  |

|       | 0             | 0                                                                              | Consumer Mode, $PRO = 0$ , $COPY = 0$ , $L = 0$            |  |  |  |  |  |

|       | 0             | 1                                                                              | Consumer Mode, $PRO = 0$ , $COPY = 0$ , $L = 1$            |  |  |  |  |  |

|       | 1             | 0                                                                              | Consumer Mode, $PRO = 0$ , $COPY = 1$ , $L = 0$            |  |  |  |  |  |

|       | 1             | 1                                                                              | Professional Mode, PRO = 1, No Copy Protection             |  |  |  |  |  |

| AUDIO | Audio Data S  | tatus                                                                          |                                                            |  |  |  |  |  |

|       | AUDIO         | Status                                                                         |                                                            |  |  |  |  |  |

|       | 0             | Digital (or Linear I                                                           | PCM) Audio Data                                            |  |  |  |  |  |

|       | 1             | Non-Audio or Enc                                                               | oded Audio Data                                            |  |  |  |  |  |

| EMPH  | Pre-Emphasis  | Pre-Emphasis Status                                                            |                                                            |  |  |  |  |  |

|       | EMPH          | Status                                                                         | Status                                                     |  |  |  |  |  |

|       | 0             | Pre-emphasis bits                                                              | are set to indicate 50/15µs Pre-emphasis has been applied. |  |  |  |  |  |

|       | 1             | 1 Pre-emphasis bits are set to indicate that no Pre-emphasis has been applied. |                                                            |  |  |  |  |  |

TABLE VI. Channel Status Data Input for Hardware Mode with CSS = 0.

FIGURE 5. C, U, and V Data Timing.

#### USER AND VALIDITY DATA INPUT

The user data bits in the AES-3 data stream allow for a convenient way to transfer user-defined or application specific data to another device containing an AES-3 receiver. The U input (pin 27) is used in both Software and Hardware mode to input the user data in a serial fashion. Figure 5 shows the U input timing diagram.

Validity data is used to indicate that a sample is error-free audio data, or that the sample is defective and is not suitable

for further processing. In Software mode, the VAL bit in control register  $01_H$  is utilized to write the validity data. In Hardware mode, the V input (pin 26) is used to input the validity data in serial fashion. Refer to Figure 5 for V input timing for Hardware Mode.

When VAL or V = 0, this indicates that the audio data is valid and suitable for further processing. When VAL or V = 1, then the audio sample is defective and should not be used.

# LINE DRIVER OUTPUTS

The DIT4192 includes a balanced line driver. The line driver outputs are TX– (pin 17) and TX+ (pin 18). In Software mode, the line driver input is taken from either the output of the on-chip AES-3 encoder, or from an external AES-3 encoded source input at RXP (pin 9). The input source is selected using the BYPASS bit in control register  $01_H$  (defaults to the on-chip AES-3 encoder). In Hardware mode, the line driver source is always the on-chip AES-3 encoder.

The outputs of the line driver will follow the AES-3 encoded data source in normal operation. During a hardware or software reset, or when the device is in power-down mode, the line driver outputs will be forced to ground. The outputs can also be forced to ground at any time in Software mode by setting the TXOFF bit to 1 in control register  $01_{\rm H}$ .

# CONTROL PORT OPERATION (SOFTWARE MODE ONLY)

For Software mode operation, the DIT4192 includes a serial control port, which is used to write and read control registers and the channel status data buffer. Port signals include  $\overline{CS}$  (pin 5), CDIN (pin 4), CDOUT (pin 2), and CCLK (pin 3).

$\overline{\text{CS}}$  is the active low chip select. This signal must be driven low in order to write or read control registers and the channel status data buffer.

CDIN is the serial data input, while CDOUT serves as the serial data output. The CDOUT pin is a tri-state output, which is set to a high-impedance state when not performing a Read operation, or when  $\overline{CS} = 1$ .

CCLK is the data clock for the serial control interface. Data is clocked in at CDIN on the rising edge of CCLK, while data is clocked out at CDOUT on the falling edge of CCLK. Data is clocked MSB first for both CDIN and CDOUT.

# WRITE OPERATION

Figure 6 illustrates the write operation for the control port. You may write one register or buffer address at a time, or use the auto-increment capability built into the control port to perform block writes. The register or buffer data is preceded by a 16-bit header, with the first byte being used to configure control port operation and set the starting register or buffer address. The second byte of the header is comprised of "don't care" bits, which can be set to either 0 or 1 without affecting port operation.

The first byte of the header contains two control bits,  $R/\overline{W}$  and STEP, followed by a 6-bit address. For write operations,  $R/\overline{W} = 0$ . The STEP bit determines the address step size for the auto-increment operation. When STEP = 0, the address is incremented by 1. When STEP = 1, the address is incremented by 2. Incrementing by 1 is useful when writing multiple control registers in sequence, or when writing both left and right channel status data in sequence. Incrementing by 2 is useful when writing just one channel of status data in sequence.

The third byte contains the 8-bit data for the register or buffer address pointed to by the first byte of the header. To write a single address location,  $\overline{CS}$  is brought high after the least significant bit of the third byte is clocked into the port. For auto increment mode,  $\overline{CS}$  is kept low to write successive register or buffer addresses.

FIGURE 6. Write Operation Format.

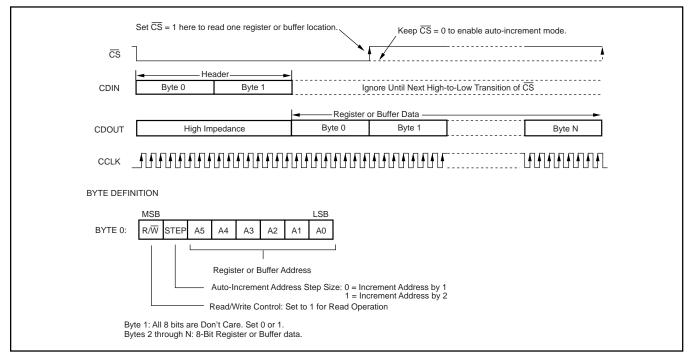

## **READ OPERATION**

Figure 7 shows an illustration of the read operation for the control port. You may read one register or buffer address at a time, or use the auto-increment capability built into the control port to perform block reads. A 16-bit header is first written to the port, with the first byte being used to configure control port operation and set the starting register or buffer address. The second byte of the header is comprised of "don't care" bits, which can be set to either 0 or 1 without affecting port operation.

The first byte of the header contains two control bits,  $R/\overline{W}$  and STEP, followed by a 6-bit address. For read operations,  $R/\overline{W} = 1$ . The STEP bit determines the address step size for

the auto-increment operation. When STEP = 0, the address is incremented by 1. When STEP = 1, the address is incremented by 2. Incrementing by 1 is useful when reading multiple control registers in sequence, or when reading both left and right channel status data in sequence. Incrementing by 2 is useful for reading just one channel of status data in sequence.

The first output data byte occurs immediately after the 16-bit header has been written. This byte contains the 8-bit data for the register or buffer address pointed to by the first byte of the header. To read a single address location,  $\overline{CS}$  is brought high after the least significant bit of the first data byte is clocked out of the port. For auto-increment mode,  $\overline{CS}$  is kept low to read successive register or buffer addresses.

FIGURE 7. Read Operation Format.

FIGURE 8. Serial Port Timing.

# CONTROL REGISTER DEFINITIONS (SOFTWARE MODE ONLY)

This section defines the control registers used to configure the DIT4192, as well as the status register used to indicate an interrupt source.

#### Register 00<sub>H</sub>: Reserved for Factory Use

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) |

|-------------|-------|-------|-------|-------|-------|-------|-------------|

| 0           | 0     | 0     | 0     | 0     | 0     | 0     | 0           |

## BLSM Block Start Mode (Defaults to 0)

When set to 0, BLS (pin 25) is configured as an input pin.

When set to 1, BLS (pin 25) is configured as an output pin.

#### VAL Audio Data Valid (Defaults to 0)

When set to 0, valid Linear PCM audio data is indicated.

When set to 1, invalid audio data or non-PCM data is indicated.

#### Register 01<sub>H</sub>: Transmitter Control Register

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) |

|-------------|-------|-------|-------|-------|-------|-------|-------------|

| TXOFF       | MCSD  | MDAT  | MONO  | BYPAS | MUTE  | VAL   | BLSM        |

## MUTE Transmitter Mute (Defaults to 0)

When set to 0, the mute function is disabled. When set to 1, the mute function is enabled, with Channel A and B audio data set to all 0's.

BYPASS Transmitter Bypass—AES-3 Data Source for the Output Driver (Defaults to 0)

When set to 0, AES-3 encoded data is taken from the output of the on-chip encoder. When set to 1, RXP (pin 9) is used as the source for AES-3 encoded data.

MONO Mono Mode Control (Defaults to 0) When set to 0, the transmitter is set to Stereo mode.

When set to 1, the transmitter is set to Mono mode.

## MDAT Data Selection Bit (Defaults to 0)

(0 = Left Channel, 1 = Right Channel)When MONO = 0 and MCSD = 0, the MDAT bit is ignored.

When MONO = 0 and MCSD = 1, the MDAT bit is used to select the source for Channel Status data.

When MONO = 1 and MCSD = 0, the MDAT bit is used to select the source for Audio data. When MONO = 1 and MCSD = 1, the MDAT bit is used to select the source for both Audio and Channel Status data.

Channel Status Data Selection (Defaults to 0) When set to 0, Channel A data is used for the A sub-frame, while Channel B data is used for the B sub-frame.

When set to 1, use the same channel status data for both A and B sub-frames. Channel status data source is selected using the MDAT bit.

TXOFF Transmitter Output Disable (Defaults to 0) When set to 0, the line driver outputs, TX– (pin 17) and TX+ (pin 18) are enabled. When set to 1, the line driver outputs are forced to ground.

#### Register 02<sub>H</sub>: Power-Down and Clock Control Register

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) |

|-------------|-------|-------|-------|-------|-------|-------|-------------|

| 0           | 0     | 0     | 0     | RST   | CLK1  | CLK0  | PDN         |

| 0 | 0 | 0 | 0 | RST | CLK1 | CLK0 | PDN |

|---|---|---|---|-----|------|------|-----|

|   |   |   |   |     |      |      |     |

|   |   |   |   |     |      |      |     |

# **Power-Down (Defaults to 1)** When set to 0, the DIT4192 operates normally. When set to 1, the DIT4192 is powered down, with the line driver outputs forced to ground.

## CLK[1:0] MCLK Rate Selection

These bits are used to select the master clock frequency applied to the MCLK input (pin 6).

| CLK1 | CLK0 | MCLK Rate                      |

|------|------|--------------------------------|

| 0    | 0    | 128 • f <sub>S</sub>           |

| 0    | 1    | 256 • f <sub>S</sub> (default) |

| 1    | 0    | 384 • f <sub>S</sub>           |

| 1    | 1    | 512 • f <sub>S</sub>           |

#### RST

PDN

MCSD

Software Reset (Defaults to 0)

When set to 0, the DIT4192 operates normally. When set to 1, the DIT4192 is reset.

# Register 03<sub>H</sub>: Audio Serial Port Control Register

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) |

|-------------|-------|-------|-------|-------|-------|-------|-------------|

| ISYNC       | ISCLK | DELAY | JUS   | WLEN1 | WLEN0 | SCLKR | M/S         |

M/S

# Master/Slave Mode (Defaults to 0)

When set to 0, the audio serial port is set for Slave operation.

When set to 1, the audio serial port is set for Master operation.

# WLEN[1:0] Audio Data Word Length

These bits are used to set the audio data word length for both Left and Right channels.

| WLEN1 | WLEN0 | Length            |

|-------|-------|-------------------|

| 0     | 0     | 24 Bits (default) |

| 0     | 1     | 20 Bits           |

| 1     | 0     | 18 Bits           |

| 1     | 1     | 16 Bits           |

# JUS Audio Data Justification (Defaults to 0)

When set to 0, the audio data is Left-Justified with respect to the SYNC edges.

When set to 1, the audio data is Right-Justified with respect to the SYNC edges.

DELAY Audio Data Delay from the Start of Frame (Defaults to 0)

This applies primarily to I<sup>2</sup>S and DSP frame formats, which use Left-Justified audio data. When set to 0, audio data starts with the SCLK period immediately following the SYNC edge which starts the frame. This is referred to as a zero SCLK delay.

When set to 1, the audio data starts with the second SCLK period following the SYNC edge which starts the frame. This is referred to as a one SCLK delay. This is used primarily for the I<sup>2</sup>S data format.

## ISCLK SCLK Sampling Edge (Defaults to 0)

When set to 0, audio serial data at SDATA (pin 13) is sampled on rising edge of SCLK. When set to 1, audio serial data at SDATA (pin 13) is sampled on falling edge of SCLK.

# ISYNC SYNC Polarity (Defaults to 0)

When set to 0, Left channel data occurs when the SYNC clock is HIGH.

When set to 1, Left channel data occurs when the SYNC clock is LOW.

For both cases, Left channel data always precedes the Right channel data in the audio frame.

#### Register 04<sub>H</sub>: Interrupt Status Register

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) |

|-------------|-------|-------|-------|-------|-------|-------|-------------|

| 0           | 0     | 0     | 0     | 0     | 0     | TSLIP | BTI         |

BTI

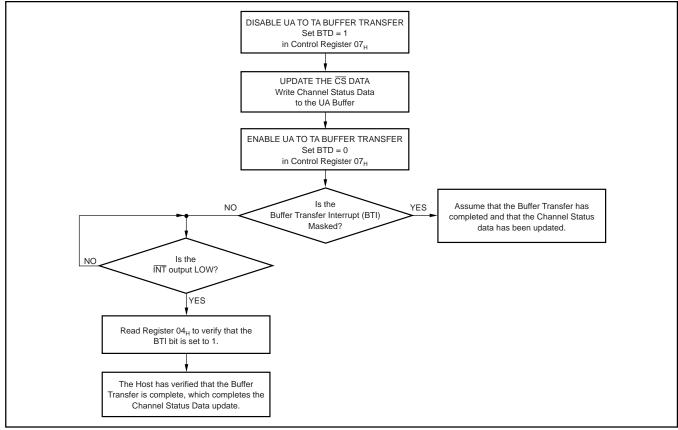

# Buffer Transfer Interrupt Status—Active High

When User Access (UA) to Transmitter Access (TA) buffer transfers are enabled, and the BTI interrupt is unmasked, this bit will go HIGH when a UA to TA buffer transfer has completed. This will also cause the  $\overline{INT}$  output (pin 22) to be driven Low, indicating that an interrupt has occurred.

TSLIP

#### Transmitter Source Data Slip Interrupt Status—Active High

This bit will go HIGH when either a Data Slip or Block Start condition is detected, and the TSLIP interrupt is unmasked. This will also cause the  $\overline{INT}$  output (pin 22) to be driven LOW, indicating that an interrupt has occurred. The function of this bit is selected using the BSSL bit in control register 05<sub>H</sub> (defaults Data Slip).