February 2004

# DS92UT16TUF UTOPIA-LVDS Bridge for 1.6 Gbps Bi-directional Data Transfers

## 1.0 General Description

The DS92UT16 is a flexible UTOPIA to LVDS Bridge device. The LVDS Bridge transparently transports the UTOPIA bus over a high speed LVDS serial link. The device includes many reliability features such as an optional 1:1 protection and built in bit error rate checking.

The parallel interface is user programmable for maximum flexibility. The user can choose between UTOPIA Level Level 2 ATM layer (master) of PHY layer (slave). The UTOPIA-LVDS Bridge supports a special MPHY (multi-PHY layer) operation mode. The MPHY operation supports up to 248 standard UTOPIA Level 2 PHY ports without adding external circuitry.

The serial interface uses LVDS Serializer and Deserializer technology. The 16:1 bit serialization allows conveying the full-duplex parallel bus over two differential transmission pairs. This enables low cost backplanes and cables. Cable transmission length can be as long 16 meters.

The serial link carries Flow control information (back pressure) in both directions. The Bridge device applies back pressure on a per queue basis over the 31 internal FIFO queues. In addition, the serial link includes an OAM (Operations and Maintenance) channel that does not detract from link performance.

There are many applications where the UTOPIA-LVDS Bridge simplifies designs. Box-to-box connections can use DS29UT16 devices across cables. Access multiplexor applications can use the devices across a PCB backplane for point-to-point and lightly loaded multidrop configurations.

### 2.0 Features

- 832 Mbps LVDS 16-bit serializer and deserializer interface

- Suitable for cable, printed circuit board, and backplane transmission paths

- 10m cable at max LVDS data rate and greater than 16m at min LVDS data rate

- Embedded clock with random data lock capability for clock recovery

- PRBS ( $x^{31} + x^{28} + 1$ ) based LVDS link BER test facility

- Two independent LVDS receiver serial ports for optional 1:1 protection

- Main and redundant LVDS transmit ports

- Loop timing capability enables LVDS recovered clock to internally drive LVDS transmit clock

- Internal buffers allow maximum LVDS serial bit rate independent of UTOPIA clock rate

- Programmable UTOPIA interface

- UTOPIA Level 2 up to 52 MHz

- ATM layer or PHY layer interface

- ATM layer interface can support up to 248 standard Level 2 PHY ports with no additional external circuitry. Configured as 31 MPHY's, each with up to 8 sub-ports

- Supports extended cell size up to 64 bytes

- Supports 16- or 8-bit data buses with parity

- Embedded bidirectional, non-blocking flow control over serial link for per MPHY back pressure

- No external memories required

- Embedded OAM channel over serial link

- Remote Alarm/Status Indications

- Link Trace Label

- Embedded Control Channel with flow control for software communication

- BIP16 based error performance monitoring

- In protected systems, the standby link OAM channel is available for embedded communications and performance/alarm monitoring

- Multiple loop-back options

- Standard microprocessor interface (Intel and Motorola compatible)

- IEEE 1149.1 JTAG port

- Temperature range: -40°C to +85°C

- CMOS technology for low power

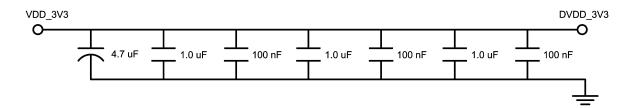

- LVDS transceiver section uses 3.3V power supply.

Digital UTOPIA section uses 2.5V power supply. All I/O are 3.3V tolerant.

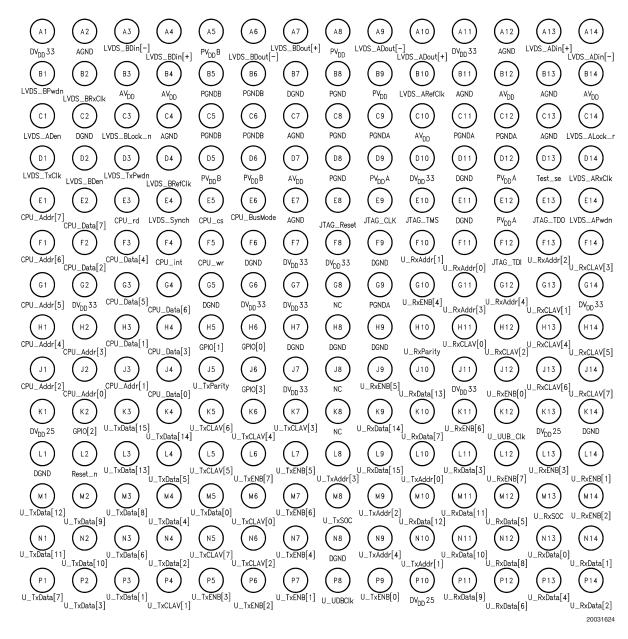

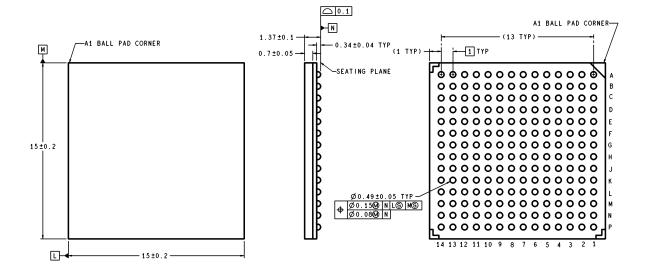

- 196 LBGA package, 15x15x1.37 mm, 1.0 mm ball pitch

## 3.0 Ordering Information

| Order Number | Package Information                                | Package Number |

|--------------|----------------------------------------------------|----------------|

| DS92UT16TUF  | 196 LBGA package, 15x15x1.37 mm, 1.0 mm ball pitch | NUJB0196       |

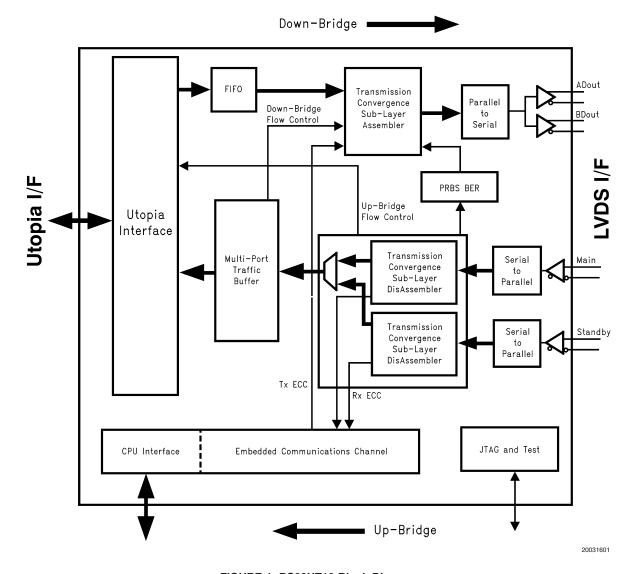

## 4.0 Block Diagram

FIGURE 1. DS92UT16 Block Diagram

## 5.0 Application Overview

## 5.0 Application Overview (Continued)

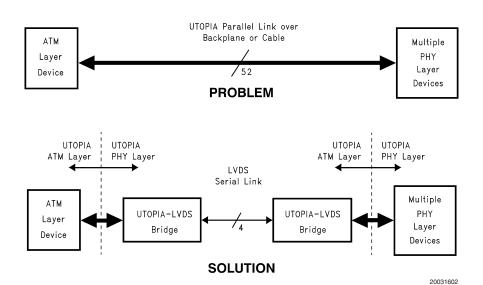

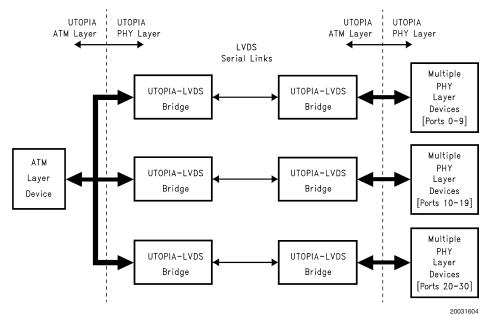

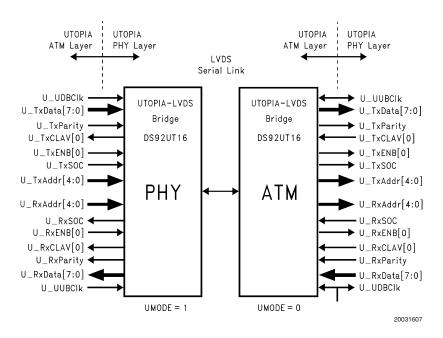

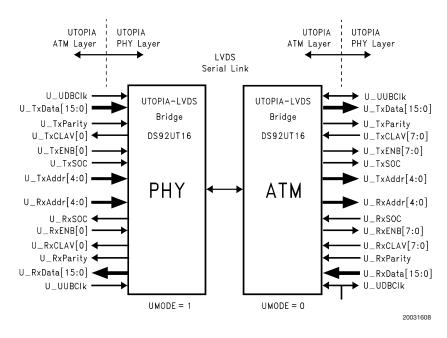

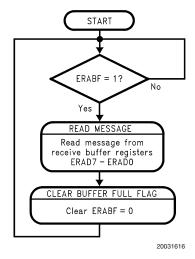

FIGURE 2. Application Example

The UTOPIA interface [1. See Section 21.0 References] is an established standard for connecting Physical Layer devices to ATM Layer devices. However, when the ATM Layer device and the Physical Layer device(s) are on separate cards within a piece of equipment, or even on separate equipment, then the parallel nature of this standard becomes a limiting factor. See Figure 2.

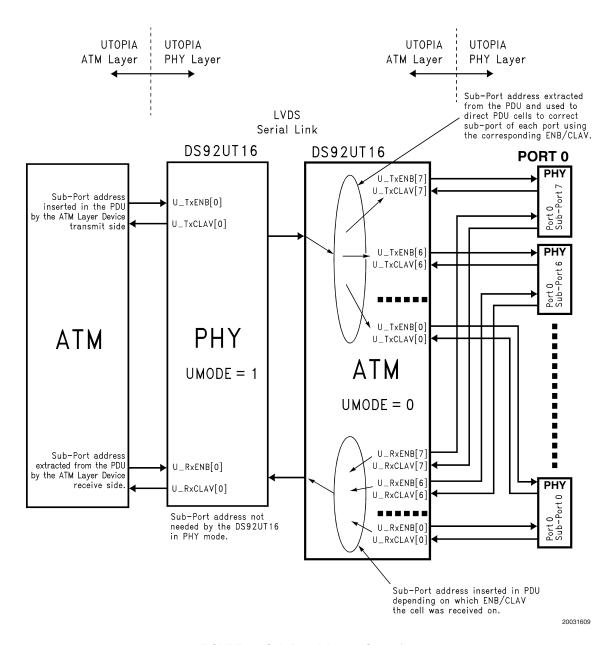

The solution is to use the DS92UT16, which is a transparent bridge that extends the UTOPIA bus over a serial LVDS interface, and is suitable for backplanes and cables. Full bidirectional flow control is incorporated, allowing backpressure to be applied to the source of the ATM cells. The 31 PHY ports available with standard UTOPIA Level 2 may be extended to 248 ports without additional external circuitry. The DS92UT16 achieves this by providing as many as 8 ENB and CLAV signals in both receive and transmit directions when acting as the ATM Layer device. This allows addressing 248 PHYs that are configured as up to 31 ports that each have as many as 8 sub-ports.

To aid equipment management and maintenance, the DS92UT16 passes an embedded 'Operations, Administration and Maintenance' (OAM) channel over the serial link. In addition, the device provides a number of loopback options that are both traffic affecting (line loopbacks) and non-traffic affecting (cell loopbacks), which simplify testing and diagnostic activities.

The DS92UT16 has a modified Bus LVDS serial output for driving cables in point-to-point applications. The cable length depends on the quality of the cable and the data rate. Increasing the cable quality, or lowering the LVDS data rate, increases the maximum possible cable length the device will drive.

When examining the trade-offs that determine the DS92UT16 maximum cable drive capability, it is important to

understand that the LVDS data rate on the cable is 18 times (16 bits plus 2 embedded clock bits) the LVDS\_TxClk rate. For example, a 35 MHz LVDS\_TxClk will produce a 630 Mbps data rate, and a 52 MHz clock will produce a 936 Mbps data rate. When using twinaxial grade differential cable, the cable length can be as long as 16m for the 35 MHz clock and approximately 10m for the 52 MHz clock.

## 6.0 Functional Description

#### **6.1 UTOPIA INTERFACE**

The DS92UT16 has an industry standard UTOPIA interface [1.] supporting Level 2 and Extended Level 2 operation. Depending on its position in the bridge link, it may operate as either the ATM layer or the physical layer in the UTOPIA protocol.

In Level 2 mode, this interface can be either a 16-bit or an 8-bit wide data path, with both octet and cell level handshaking and operating at a frequency as high as 52 MHz, facilitating 622 Mbps (STM4/OC12) line rates.

In UTOPIA Level 2 mode, the device supports Multi-PHY (MPHY) operation, whereby up to 31 PHY ports may be connected to an ATM device. The presence of cells and availability of buffer space is indicated using the CLAV signals.

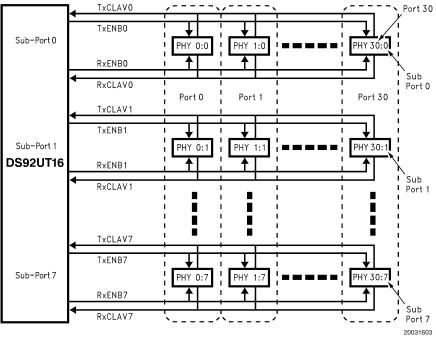

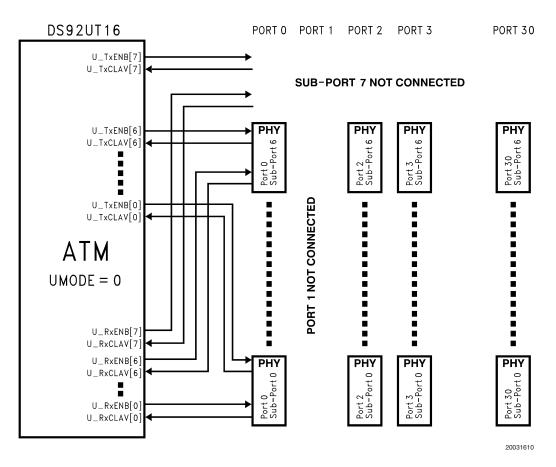

UTOPIA Level 2 defines 1 ENB and 1 CLAV signal in each direction. The DS92UT16 has extended this to 8 ENB and 8 CLAV signals, which enables up to 248 PHY ports to be connected to an ATM device without additional external circuitry as shown in *Figure 3*.

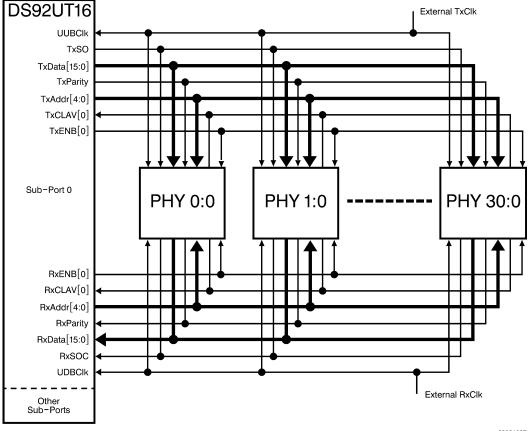

Note: The full connections for a single sub-port are shown in Figure 4.

FIGURE 3. Extended UTOPIA Level 2 for 248 PHY Ports

20031627

FIGURE 4. Detailed Connection of One Sub-Port for Extended UTOPIA Level 2

For the purposes of queueing, the 248 PHY ports are configured as sub-ports of the standard 31 ports so each port/queue has 8 sub-ports as discussed in *Section 6.2.2 Up-Bridge Multi-Port Traffic Buffer*. Each MPHY address corresponds to a port.

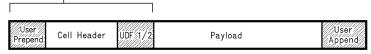

The 5 bit MPHY can address up to 31 PHY ports. At least 3 additional bits are required to give the total of 8 bits necessary for addressing 248 PHY ports. These additional address bits can be provided by the user in any of the User Prepend, Cell Header or UDF1/2 bytes of the cell as shown in *Figure 6*. The DS92UT16 is configured to extract/insert the extra address bits from/to any of these bytes.

PHY polling may be carried out as follows:

- Standard UTOPIA Level 2 with 1 CLAV signal.

- One CLAV polling 31 PHY ports.

- DS92UT16 Extended UTOPIA Level 2 with up to 8 CLAV signals.

- Each CLAV can poll 31 PHY ports giving a total of 248 PHY ports.

Multiple UTOPIA-LVDS bridge devices can be used in parallel to share up to 31 PHY ports among PHYs that are on separate line cards *Figure 5*. Each of these ports may have up to 8 sub-ports. There are constraints on the number of port addresses used per bridge in such a configuration. See *Section 9.2 MULTIPLE BRIDGE MTB CONFIGURATION*

Note: Default MTB queue thresholds must be changed to use this configuration. See Section 9.2 MULTIPLE BRIDGE MTB CONFIGURATION

FIGURE 5. Multi-Bridge System Example

Parity generation and checking is available in all modes.

To support systems where routing tags and/or padding are added to the ATM cells at a previous device, the UTOPIA interface on DS92UT16 may be programmed to handle non-standard ATM cells of length 52 bytes up to 64 bytes. See *Figure 6*. In all cases, the Start Of Cell (SOC) signal must correspond to the first byte or word of the extended cell.

Back-to-back cell transfer is supported in all modes.

When configured as an ATM layer device, receive polling and transmit polling of those Ports with queued cells is Round-Robin. The DS92UT16 will only poll those PHY ports configured as active.

### **6.2 TRAFFIC BUFFERS**

#### 6.2.1 Down-Bridge FIFO

In the down-bridge direction, a simple 3 cell FIFO (with 30 cell overhead) is used to rate adapt the data from the UTO-PIA clock domain to the LVDS clock domain for transmission. Per port queuing and back pressure/flow control is handled by the corresponding up-bridge Multi-port Traffic Buffer in the far end DS92UT16 device as described in Section 6.2.2 Up-Bridge Multi-Port Traffic Buffer and Section 6.3.5 Flow Control.

### 6.2.2 Up-Bridge Multi-Port Traffic Buffer

In the up-bridge direction, a 160 cell linked list buffer is shared across up to 31 port queues. This is called the Multi-port Traffic Buffer. Although each MPHY may be connected to 8 sub-ports/PHY's, the MTB has a single queue per MPHY port, as it only uses the 5-bit MPHY address and does not access the sub-port address bits.

Each port has a programmable upper fill threshold. In the up-bridge direction, queue overflow is avoided through the means of a per queue flow control protocol embedded in the LVDS link as described in *Section 6.3.5 Flow Control*. Should any queue reach this upper threshold, back-pressure is applied via the flow control mechanism over the serial link to the down-bridge (transmitting) device which uses the normal UTOPIA flow control handshaking to prevent any more cells being transferred and thus prevent overflow.

The individual queue per port architecture ensures that the flow control is non-blocking across the 31 ports. However, the 8 sub-ports within each port can be blocking.

Furthermore, as is the nature of link-list buffers, each queue may be over-assigned memory space, working on the assumption that not every queue will back up simultaneously. To accommodate the rare occasions where the buffer as a whole approaches full but individual queues are below their full threshold, the device also compares the overall buffer fill against a threshold. The flow control mechanism provides a global 'halt' command to ensure that no cells will be lost if the overall buffer should approach the overflow condition.

## 6.3 TRANSMISSION CONVERGENCE SUB-LAYER (TCS)

In the down-bridge direction, the Transmission Convergence Sub-layer (TCS) Assembler performs cell rate de-coupling. The TCS Assembler then prepares the cells for transport over the LVDS link by packaging them within link Transport Containers (TC).

In the up-bridge direction, the TCS Disassemblers unpack the link transport containers and route the cells to the Multiport Traffic Buffer.

MPHY address, flow control, and OAM information is embedded within the link transport containers.

#### 6.3.1 Cell Rate Decoupling

In the down-bridge direction, the TCS Assembler inserts idle cells when no valid traffic cells are available from the FIFO for onward transmission. In the up-bridge direction, the TCS Disassembler rejects all received idle cells.

#### 6.3.2 Link Transport Container (TC)

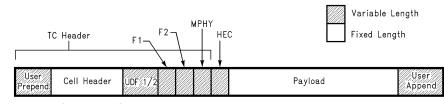

The ATM cells received on the UTOPIA interface can be standard or user-specified cells. Cell length is programmable from 52 to 64 bytes. These cells are treated as Protocol Data Units (PDU), which are packaged into Transport Containers (TC) for transmission over the serial link. In the reverse direction, the cell PDUs are unpacked from the link TCs before being passed out on the UTOPIA interface.

### This is illustrated in Figure 6.

The PDU fields are configured as shown in *Table 1*. The total PDU cell length must be in the range of 52 to 64 bytes. In addition, variable length fields must be programmed to an even number of bytes because the DS92UT16 operates with an internal 16 bit data path. The total number of bytes defined for User Prepend plus UDF1/2 and User Append must not exceed 12 bytes to maintain the maximum PDU cell length of 64 bytes.

**TABLE 1. PDU Cell Format Options**

| Field        | Fixed/<br>Variable | Bytes                 |

|--------------|--------------------|-----------------------|

| User Prepend | Variable           | 0, 2, 4, 6, 8, 10, 12 |

| Cell Header  | Fixed              | 4                     |

| UDF1/2       | Variable           | 2, 0 in 16 bit mode   |

|              | (On/Off)           | 1, 0 in 8 bit mode    |

| Payload      | Fixed              | 48                    |

| User Append  | Variable           | 0, 2, 4, 6, 8, 10, 12 |

Although the UDF1/2 bytes will always be present, the DS92UT16 can be programmed to either transport these bytes or ignore them. If they are to be ignored, then the TCS strips them out in the down-bridge direction and the UTOPIA up-bridge section inserts a HEC byte in UDF 1. Otherwise, they can be transported transparently the same as any other PDU byte.

These bytes contain the byte with sub-port address bits for attaching as many as 248 PHY devices.

**PDU Cell from UTOPIA Interface**

Link Transport Container (TC)

20031605

FIGURE 6. PDU and Link Transport Container Format

Each link TC has an MPHY address byte, two Flow Control (F) Channel bytes, and a HEC byte in addition to the PDU cell. The two F1 and F2 bytes per TC constitute the F Channel, which is used for flow control and OAM purposes over the link. The TCS uses the HEC byte for container delineation, frame delineation, and cell header error detection.

#### 6.3.3 MPHY Tagging and Routing

In the down-bridge direction, the DS92UT16 adds an additional byte (MPHY byte) to each PDU. It contains the MPHY port address associated with that PDU, as shown in *Table 2*.

TABLE 2. MPHY Byte

| Bit      | 7   | 6     | 5      | 4     | 3   | 2    | 1    | 0 |

|----------|-----|-------|--------|-------|-----|------|------|---|

| Function | MPH | Y Por | t Addr | ess 0 | -31 | Rese | rved |   |

At the other end of the link, this byte is used to route the incoming PDU from the LVDS interface to the appropriate MPHY port queue.

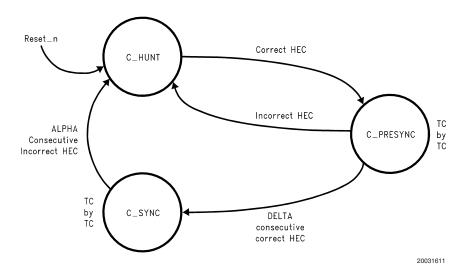

### 6.3.4 Transport Container Delineation and Error Monitoring

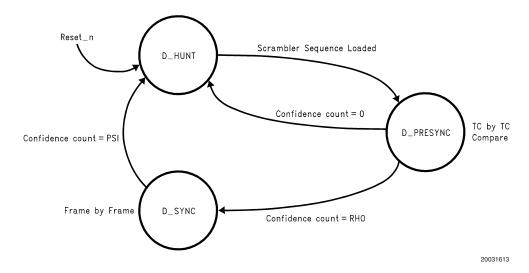

In the down-bridge direction, the device calculates and inserts the HEC byte using the CRC-8 polynomial  $x^8+x^2+x+1$  and optional coset  $x^6+x^4+x^2+1$  defined in I.432.1 [2.]. The HEC byte is calculated over the preceding 7–19 bytes, which make up the link TC header. To aid delineation at the far end, the entire contents of the TC, excluding the HEC, are scrambled and the HEC is calculated on the scrambled TC header. A scrambler using the pseudo-random sequence polynomial  $x^{31}+x^{28}+1$  defined in I.432.1 [2.] is used.

In the up-bridge direction, the device determines the cell delineation within the received data by locking onto the HEC byte within the transport container, using the algorithm specified in I.432.1 [2.].

During normal operation in the up-bridge direction, the device monitors the HEC bytes for errors, with an option to reject cells containing errored HEC's. A performance metric on the number of errored cells detected is maintained.

Although the HEC byte normally over-writes the UDF1 byte before cells are passed out over a physical medium, the DS92UT16 has the option to retain the UDF1 and UDF2 information fields in order to provide a truly transparent UTOPIA bridge. If it is not necessary to pass the UDF1/2 bytes between the ATM and PHY devices at either end of the link, then the user has the option to suppress them to improve link efficiency.

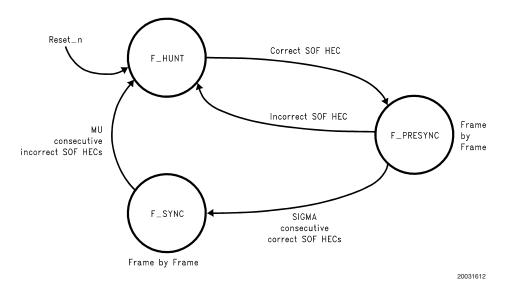

Furthermore, in order to easily share-out the F Channel bandwidth between flow control and various OAM functions, the DS92UT16 uses a frame structure as shown in *Section 6.3.6 F Channel Byte Usage Within the Frame.* A frame contains 56 transport containers with ATM cells. The start of frame is indicated by the HEC byte of TC0, which has had the coset  $x^6 + x^4 + x^2 + 1$  added to it. This differentiates the start of frame HEC from the normal cell HEC's.

#### 6.3.5 Flow Control

The flow control mechanism within the DS92UT16 enables applying back-pressure to the source of the ATM cells in both directions. The flow control works independently per queue for all 31 queues. It uses a simple 'halt/send' command per PHY Port. At the destination buffer, the fill level of each Port queue is examined against a programmed threshold. Should the threshold be reached, a halt command is returned to the source, which prevents any more cells being sent to that Port until a 'send' command is subsequently received. Only the Port in question is affected, so this is a non-blocking protocol over the normal 31 Ports. However, the 8 sub-ports within a Port do not have individual flow control. This means a sub-port can block other sub-ports within that Port.

Since a regular flow control opportunity is provided via the F1/F2 bytes of the F Channel, only a small amount of headroom need be reserved to allow for latency in this protocol. Furthermore, should a number of PHY ports approach their limit simultaneously and/or the overall buffer approach a defined global threshold, a global halt may be issued, temporarily blocking all traffic.

The global halt/send command also allows the user to safely maximize the use of the shared buffer by over-assigning the memory among the Ports.

The flow control command is illustrated in *Table 3*. Each port is assigned a control bit in specified F-bytes within the frame structure, as shown in *Section 6.3.6 F Channel Byte Usage Within the Frame*. Within the F byte logic, 1 represents a 'halt' command to that port and logic 0 represents a 'send' command. A global halt is indicated by all ports containing a halt command. The msb of Flow Control 3 byte is reserved.

TABLE 3. Flow Control Coding Within the F Bytes

| Flow      |             | Flow        | Flow       | Flow      |  |

|-----------|-------------|-------------|------------|-----------|--|

| Control 3 |             | Control 2   | Control 1  | Control 0 |  |

| Res       | Ports 30-24 | Ports 23-16 | Ports 15-8 | Ports 7-0 |  |

#### 6.3.6 F Channel Byte Usage Within the Frame

For the majority of time, the F Channel F1/F2 bytes are used as a flow control opportunity, providing a rapid throttle-back mechanism as described in *Section 6.3.5 Flow Control*. In addition, a small number of F bytes are stolen in a regular fashion to provide a low bandwidth OAM channel. This is controlled by the TC number within the frame, as illustrated in *Table 4*. Hence, an OAM channel is formed by the F1/F2 bytes in TCs 6, 13, 20, 27, 34, 41, 48 and 55, with the F1/F2 bytes in the remaining containers forming a flow control signalling channel.

TABLE 4. F Channel Byte Usage Within the Frame

| TC0                                                                                        | TC1                                                                                        | TC2                                                                                        | тсз                                                                                  | TC4                                                                                        | TC5                                                                                  | TC6                                          |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|

| Flow Control 3                                                                             | Flow Control 1                                                                             | Flow Control 3                                                                             | Flow Control 1                                                                       | Flow Control 3                                                                             | Flow Control 1                                                                       | Alarm/Sig.                                   |

| Flow Control 2                                                                             | Flow Control 0                                                                             | Flow Control 2                                                                             | Flow Control 0                                                                       | Flow Control 2                                                                             | Flow Control 0                                                                       | Link Labels                                  |

| TC7                                                                                        | TC8                                                                                        | TC9                                                                                        | TC10                                                                                 | TC11                                                                                       | TC12                                                                                 | TC13                                         |

| Flow Control 3                                                                             | Flow Control 1                                                                             | Flow Control 3                                                                             | Flow Control 1                                                                       | Flow Control 3                                                                             | Flow Control 1                                                                       | ECC1                                         |

| Flow Control 2                                                                             | Flow Control 0                                                                             | Flow Control 2                                                                             | Flow Control 0                                                                       | Flow Control 2                                                                             | Flow Control 0                                                                       | ECC2                                         |

| TC14                                                                                       | TC15                                                                                       | TC16                                                                                       | TC17                                                                                 | TC18                                                                                       | TC19                                                                                 | TC20                                         |

| Flow Control 3                                                                             | Flow Control 1                                                                             | Flow Control 3                                                                             | Flow Control 1                                                                       | Flow Control 3                                                                             | Flow Control 1                                                                       | ECC3                                         |

| Flow Control 2                                                                             | Flow Control 0                                                                             | Flow Control 2                                                                             | Flow Control 0                                                                       | Flow Control 2                                                                             | Flow Control 0                                                                       | ECC4                                         |

| TC21                                                                                       | TC22                                                                                       | TC23                                                                                       | TC24                                                                                 | TC25                                                                                       | TC26                                                                                 | TC27                                         |

| Flow Control 3                                                                             | Flow Control 1                                                                             | Flow Control 3                                                                             | Flow Control 1                                                                       | Flow Control 3                                                                             | Flow Control 1                                                                       | BIP16                                        |

| Flow Control 2                                                                             | Flow Control 0                                                                             | Flow Control 2                                                                             | Flow Control 0                                                                       | Flow Control 2                                                                             | Flow Control 0                                                                       |                                              |

| TC28                                                                                       | TC29                                                                                       | TC30                                                                                       | TC31                                                                                 | TC32                                                                                       | TC33                                                                                 | TC34                                         |

|                                                                                            |                                                                                            |                                                                                            |                                                                                      |                                                                                            |                                                                                      |                                              |

| Flow Control 3                                                                             | Flow Control 1                                                                             | Flow Control 3                                                                             | Flow Control 1                                                                       | Flow Control 3                                                                             | Flow Control 1                                                                       | Reserved                                     |

| Flow Control 3<br>Flow Control 2                                                           | Flow Control 1<br>Flow Control 0                                                           | Flow Control 3<br>Flow Control 2                                                           | Flow Control 1<br>Flow Control 0                                                     | Flow Control 3<br>Flow Control 2                                                           | Flow Control 1<br>Flow Control 0                                                     | Reserved                                     |

|                                                                                            |                                                                                            |                                                                                            |                                                                                      |                                                                                            |                                                                                      | Reserved TC41                                |

| Flow Control 2                                                                             | Flow Control 0                                                                             | Flow Control 2                                                                             | Flow Control 0                                                                       | Flow Control 2                                                                             | Flow Control 0                                                                       |                                              |

| Flow Control 2<br>TC35                                                                     | Flow Control 0 TC36                                                                        | Flow Control 2 TC37                                                                        | Flow Control 0 TC38                                                                  | Flow Control 2 TC39                                                                        | Flow Control 0 TC40                                                                  | TC41                                         |

| Flow Control 2 TC35 Flow Control 3                                                         | Flow Control 0 TC36 Flow Control 1                                                         | Flow Control 2 TC37 Flow Control 3                                                         | Flow Control 0  TC38  Flow Control 1                                                 | Flow Control 2 TC39 Flow Control 3                                                         | Flow Control 0 TC40 Flow Control 1                                                   | TC41<br>ECC5                                 |

| Flow Control 2  TC35  Flow Control 3  Flow Control 2                                       | Flow Control 0  TC36  Flow Control 1  Flow Control 0                                       | Flow Control 2  TC37  Flow Control 3  Flow Control 2                                       | Flow Control 0 TC38 Flow Control 1 Flow Control 0                                    | Flow Control 2  TC39  Flow Control 3  Flow Control 2                                       | Flow Control 0  TC40 Flow Control 1 Flow Control 0                                   | TC41<br>ECC5<br>ECC6                         |

| Flow Control 2  TC35 Flow Control 3 Flow Control 2  TC42                                   | Flow Control 0  TC36 Flow Control 1 Flow Control 0  TC43                                   | Flow Control 2  TC37 Flow Control 3 Flow Control 2  TC44                                   | Flow Control 0 TC38 Flow Control 1 Flow Control 0 TC45                               | Flow Control 2 TC39 Flow Control 3 Flow Control 2 TC46                                     | Flow Control 0 TC40 Flow Control 1 Flow Control 0 TC47                               | TC41<br>ECC5<br>ECC6<br>TC48                 |

| Flow Control 2 TC35 Flow Control 3 Flow Control 2 TC42 Flow Control 3                      | Flow Control 0  TC36 Flow Control 1 Flow Control 0  TC43 Flow Control 1                    | Flow Control 2  TC37 Flow Control 3 Flow Control 2  TC44 Flow Control 3                    | Flow Control 0 TC38 Flow Control 1 Flow Control 0 TC45 Flow Control 1                | Flow Control 2 TC39 Flow Control 3 Flow Control 2 TC46 Flow Control 3                      | Flow Control 0 TC40 Flow Control 1 Flow Control 0 TC47 Flow Control 1                | TC41<br>ECC5<br>ECC6<br>TC48<br>ECC7         |

| Flow Control 2  TC35  Flow Control 3  Flow Control 2  TC42  Flow Control 3  Flow Control 2 | Flow Control 0  TC36  Flow Control 1  Flow Control 0  TC43  Flow Control 1  Flow Control 0 | Flow Control 2  TC37  Flow Control 3  Flow Control 2  TC44  Flow Control 3  Flow Control 2 | Flow Control 0 TC38 Flow Control 1 Flow Control 0 TC45 Flow Control 1 Flow Control 0 | Flow Control 2  TC39  Flow Control 3  Flow Control 2  TC46  Flow Control 3  Flow Control 2 | Flow Control 0 TC40 Flow Control 1 Flow Control 0 TC47 Flow Control 1 Flow Control 0 | TC41<br>ECC5<br>ECC6<br>TC48<br>ECC7<br>ECC8 |

## 6.3.7 OAM Channel

#### 6.3.7.1 Remote Alarm and Signaling Byte

A byte-wide remote alarm and signaling channel is carried in the F1 byte in TC6 as shown in *Section 6.3.6 F Channel Byte Usage Within the Frame*. This provides a means for the device at the far end of the LVDS link to signal an alarm condition to the near end and vise-versa. This byte also contains the ECC flow control signals. The format of this byte is as shown below. Bit [0] is reserved.

TABLE 5. Remote Alarm and Signalling Byte

| Bit      | 7     | 6     | 5   | 4     | 3   | 2    | 1    | 0   |

|----------|-------|-------|-----|-------|-----|------|------|-----|

| Function | RLOSA | RLOSB | RBA | RDSLL | EVN | ESSA | ESSB | Res |

- RLOSA Remote Loss Of Signal lock at far end device receive port A.

- RLOSB Remote Loss Of Signal lock at far end device receive port B.

- RBA Remote far end device active receive port. Set = remote receive port B active and Clear = remote receive port A active.

- RDSLL Remote far end device active port Descrambler

Loss of Lock. Set = Out of lock and Clear = In

lock.

- EVN ECC Tx Data Valid/Null indication.

- ESSA ECC RxA Stop/Start indication.

- ESSB ECC RxB Stop/Send indication.

The status of the received RLOSA, RLOSB, RBA and RDSSL bits is reflected in the RARA register for receive port

A and in RBRA for receive port B. See Section 18.33 RE-CEIVE PORT A REMOTE STATUS AND ALARMS—0x3C RARA and Section 18.52 RECEIVE PORT B REMOTE STATUS AND ALARMS—0x7C RBRA for descriptions of these registers.

The function of the ECC signaling bits EVN, ESSA, and ESSB is described in *Section 16.0 Embedded Communication Channel Operation*.

#### 6.3.7.2 Link Trace Label Byte

Also, in TC6 a byte-wide link trace label is carried in the F2 byte as shown in *Section 6.3.6 F Channel Byte Usage Within the Frame*. This allows the user to verify link connectivity, which is especially useful when a number of cable links are being used. The DS92UT16 may be programmed with both a link label value to transmit and an expected link label. Should the received link label not match the expected value, an alarm interrupt may be raised.

The received Link Label byte is software accessible and an interrupt may be raised on a change of received Link Label byte. So the Link Label byte may also be used as a user defined channel to pass one byte per frame across the link.

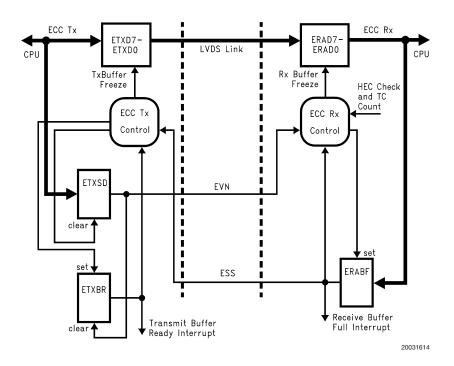

#### 6.3.7.3 Embedded Communications Channel (ECC)

An Embedded Communications Channel is provided over the link for software messaging, download, etc. in the F1/F2 bytes of TCs 13, 20, 41 and 48 as shown in *Table 4*. The ECC byte contents are not processed by the DS92UT16. Hence the DS92UT16 is transparent to and does not restrict the system messaging protocol.

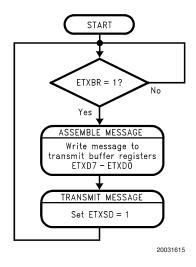

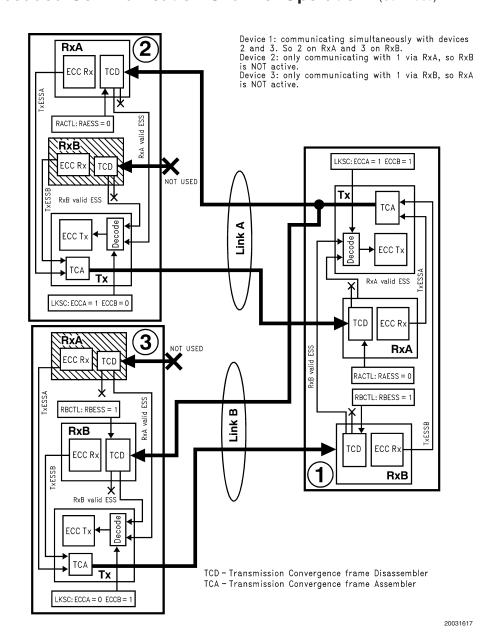

The ECC consists of an 8 byte Tx Buffer with corresponding Tx Buffer Ready and Tx Buffer Send flags, and an 8 byte Rx

Buffer with a corresponding Rx Buffer Full Flag. All bytes of the buffers are software read/write accessible. Tx Buffer Ready is read only.

At the ECC transmit side, the reset state sets the Tx Buffer Ready flag and clears the Tx Buffer Send flag. Then the software assembles a message for transmission in the Tx Buffer. To send a message, the software simply sets Tx Buffer Send, which automatically clears Tx Buffer Ready. The contents of the Tx Buffer are transmitted to the far-end. The Tx Buffer will automatically be retransmitted until the far-end indicates that it has been successfully received. When notified by the far end of successful reception, Tx Buffer Ready is set and an interrupt raised to the software to indicate successful transmission. A new message may now be assembled in the Tx Buffer and transmitted by setting Tx Buffer Send. As all the Tx Buffer bytes are read/ write, the message to be transmitted can be assembled in any order and read back by the software before transmission. The same message can be retransmitted simply by setting Tx Buffer Send again.

At the ECC receive side, the reset state clears the Rx Buffer Full flag. When all 8 bytes of a message have been successfully received and stored in the Rx Buffer, the Rx Buffer Full flag is set and an interrupt raised. As all the Rx Buffer bytes are read/write, the message can be read in any order by the software. A new message will not overwrite the current received message until the Rx Buffer Full flag is cleared by the software indicating that the current Rx Buffer has been read and a new message can be received.

The ECC data flow is controlled across the link using the EVN, ESSA, and ESSB bits of the Remote Alarm and Signaling byte (Section 6.3.7.1 Remote Alarm and Signaling Byte).

As there are two independent LVDS receive ports, the DS92UT16 has two independent ECC receive sections. These are assigned to the LVDS receive ports Port A and Port B. The ECC of the standby link may therefore be used for software communication.

Section 16.0 Embedded Communication Channel Operation describes the operation and control of the ECC in detail.

#### 6.3.7.4 BIP16

A Bit-Interleaved-Parity mechanism provides a live error performance metric on the LVDS link. A BIP16 value is calculated over a previous block of 28 containers and inserted in the F1/F2 bytes of containers 27 and 55, as shown in *Section 6.3.6 F Channel Byte Usage Within the Frame*. At the far end, the re-calculated BIP16 values are compared against the received values. Any bit errors in this comparison are counted. Should the number of errors exceed a programmed threshold, then an interrupt may be raised.

## 6.3.7.5 F Channel (Flow Control and OAM) Bandwidth Analysis

This section analyses the bandwidth used by the various components of the F Channel. The figures are dependent upon the link bandwidth and the size of the PDU/ATM cells being carried in the Transport Containers. This illustration is restricted to 800 Mbps and PDU sizes of 52 and 64 bytes. By adding the 4 bytes for the F Channel, the TCs are then 56 and 68 bytes respectively.

Table 6 illustrates the number of bytes used for each function in the F Channel. The top row gives the total number of

Transport Containers per Frame as 56. It then shows the number of bytes in each Frame for OAM and Flow Control. There is a total of 112 bytes in each Frame for the F Channel.

Table 7 shows the bit rate used by each portion of the F Channel. The larger 68 byte container uses a lower proportion of the channel bandwidth for F Channel functions.

Table 8 shows the percentage of the channel bandwidth used for each of the functions. The total F Channel bandwidth is only 3.57% of total bandwidth even with the smaller container size.

TABLE 6. F Channel Bandwidth - Bytes

| Number of Transport Containers in Frame (8 rows x 7 columns) | 56  |

|--------------------------------------------------------------|-----|

| Bytes per Frame for Remote Alarms and Signalling             | 1   |

| Bytes per Frame for Link Label                               | 1   |

| Bytes per Frame for ECC                                      | 8   |

| Bytes per Frame Reserved                                     | 2   |

| Bytes per Frame for BIP16                                    | 4   |

| Bytes per Frame for OAM                                      | 16  |

| Bytes per Frame for Flow Control                             | 96  |

| Bytes per Frame for F Channel                                | 112 |

TABLE 7. F Channel Bandwidth — Mbps

| Link BW - Mbps         | 800   | 800   |

|------------------------|-------|-------|

| Container Size - Bytes | 56    | 68    |

| Remote Alarm BW - Mbps | 0.26  | 0.21  |

| Link Label BW - Mbps   | 0.26  | 0.21  |

| ECC BW - Mbps          | 2.04  | 1.68  |

| Reserved BW - Mbps     | 0.51  | 0.42  |

| BIP16 BW - Mbps        | 1.02  | 0.84  |

| OAM BW - Mbps          | 4.08  | 3.36  |

| Flow Control BW - Mbps | 24.49 | 20.17 |

| F Channel BW - Mbps    | 28.57 | 23.53 |

|                        |       |       |

TABLE 8. F Channel Bandwidth — Percentage

|                        |      | J    |

|------------------------|------|------|

| Link BW - Mbps         | 800  | 800  |

| Container Size - Bytes | 56   | 68   |

| Remote Alarm BW%       | 0.03 | 0.03 |

| Link Label BW%         | 0.03 | 0.03 |

| ECC BW%                | 0.26 | 0.21 |

| Reserved BW%           | 0.06 | 0.05 |

| BIP16 BW%              | 0.13 | 0.10 |

| OAM BW%                | 0.51 | 0.42 |

| Flow Control BW%       | 3.06 | 2.52 |

| F Channel BW%          | 3.57 | 2.94 |

|                        |      |      |

#### **6.4 LVDS PHYSICAL INTERFACE**

The DS92UT16 provides one dual transmit and two independent receive high speed LVDS serial interfaces with 800 Mbps bandwidth. The LVDS Interface transmits and receives data over lightly loaded backplanes or up to 10m of cable. The single transmit block drives two pairs of differen-

tial outputs with independent TRI-STATE® controls for each. The same data is transmitted over both pairs of transmit pins. The two serial receive interfaces are completely separate and independent and are denoted Port A and Port B. Only one receive port is selected for traffic at any one time. This is designated the Active Port. The Standby receive port may be powered down. Alternatively, the Standby receive port's OAM channel can be made available for software communications using the ECC, and for link performance monitoring. This allows the condition of the Standby link to be determined. The LOCK status of both Active and Standby ports is monitored automatically.

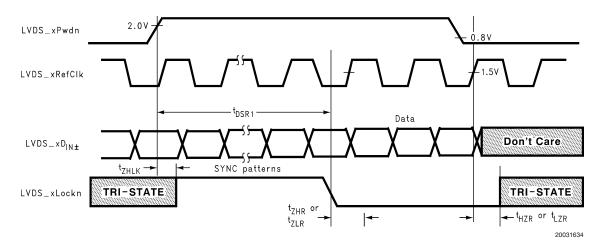

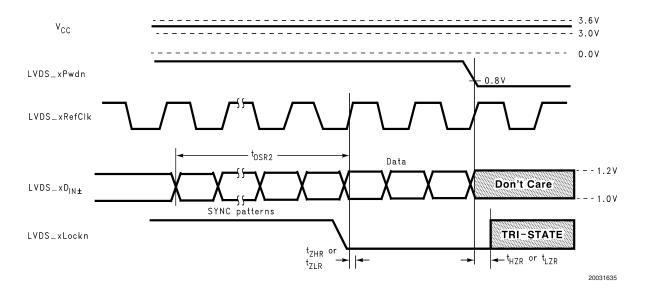

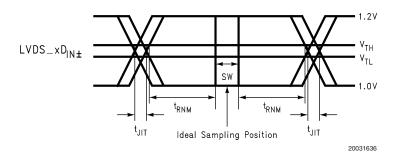

The transmitted data stream contains embedded clock information. The receiver's clock recovery circuit locks onto the embedded clock in either a random data pattern, or by instructing the transmitter to send SYNCH patterns. The DS92LV16 can send SYNCH patterns on power-up or when synchronization is lost. The latter option requires a feedback loop in either hardware or software between the transmitter and the receiver, but has the benefit of a faster lock time. The LOCK status of both receive ports is reflected on external pins and alarm/status bits that are readable via the microprocessor port. The LOCK status, along with the currently active port, is transmitted to the far-end receiver via the Remote Alarm and Signalling byte of the OAM channel as described in Section 6.3.7.1 Remote Alarm and Signaling Byte. The recovered clocks of both receive ports are available on external pins.

A Loop Timing option is available whereby the LVDS transmit clock can be sourced directly from the recovered clock of the active receiver, rather than from the external transmit clock input pin.

The transmit port and two receive ports may be independently powered down via microprocessor control. Similarly, the device may be forced to send SYNCH patterns on the transmit port via microprocessor control.

To assist in designer testing and system commissioning of the LVDS interface, the DS92UT16 has a built in BER test facility. The device may be configured to send a PRBS pattern in place of ATM cells. At the receiver, the device locks onto this PRBS pattern and provides an error metric.

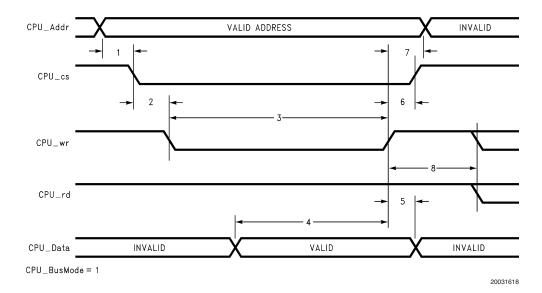

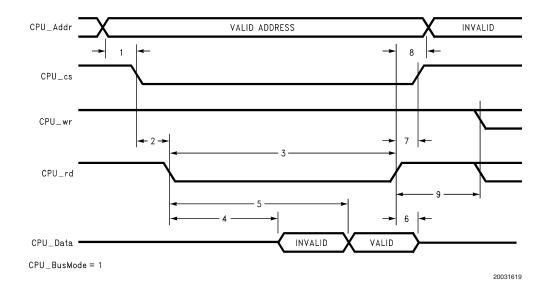

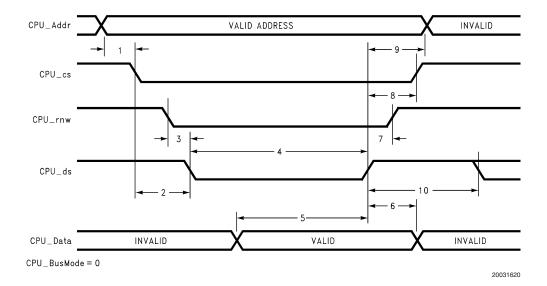

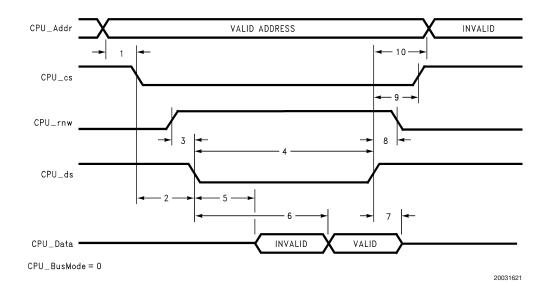

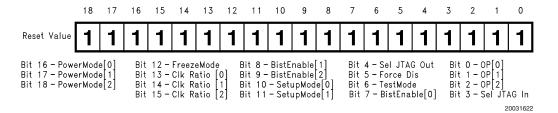

#### **6.5 CPU INTERFACE**

The DS92UT16 contains a flexible microprocessor port capable of interfacing to any common system processor. Via this port, the system software can customize the behavior of the device from the various options provided, monitor the system performance, and activate diagnostic facilities such as loop-backs and LVDS BER testing.

In addition to an 8-bit address and 8-bit data bus plus the associated bus protocol control signals, the port includes an open-drain interrupt signal. The device may assert this signal on the detection of various alarms within the device, such as excessive HEC errors, ECC buffer full/empty, loss of lock etc. Any of the potential internal sources of this interrupt may be inhibited individually via an interrupt mask.

A software lock mechanism is implemented to prevent spurious modification of some of the DS92UT16 software accessible registers. A predefined UNLOCK write sequence is necessary to allow unrestricted software write access to the DS92UT16. A corresponding LOCK write sequence will prevent any software write access to the these registers. Read access is unrestricted except as noted in the next paragraph. See *Table 9* for the LOCK and UNLOCK sequences. Only

device configuration registers such as PDU cell length, UTO-PIA interface mode, etc. are protected in this way. All other registers associated with the ECC, performance monitoring and interrupts are always write accessible by the software except as noted in next paragraph. See Section 18.1 SOFT-WARE LOCK—0x00 to 0x01 SLK0 to SLK1.

**TABLE 9. Software Lock Sequences**

| Meaning         | Sequence  | Address | Data |

|-----------------|-----------|---------|------|

| Unlock Sequence | 1st write | 0x00    | 0x00 |

|                 | 2nd write | 0x01    | 0xFF |

| LOCK Sequence   | 1st write | 0x00    | 0xDE |

|                 | 2nd write | 0x01    | 0xAD |

Powering down a Receive Port inhibits access to the associated registers. This feature saves power when a Receive Port is not in use. It allows re-reading the last value read from a register associated with that Receive Port and disallows writing to registers. Receive Port A (RxA) in Power-down mode inhibits access to registers described in Section 18.21 RECEIVE PORT A LINK LABEL—0x20 RALL to Section 18.39 RECEIVE PORT A BIT ERROR COUNT—0x43 to 0x45 RABEC2 to RABEC0. Receive Port B (RxB) in Power-down mode inhibits access to registers described in Section 18.40 RECEIVE PORT B LINK LABEL—0x60 RBLL to Section 18.58 RECEIVE PORT B BIT ERROR COUNT—0x83 to 0x85 RBBEC2 to RBBEC0. The contents of these registers are not lost or altered in Power-down mode.

#### 6.6 PERFORMANCE MONITORING AND ALARMS

The DS92UT16 provides a number of performance metrics and alarms to assist in equipment/network management. The programmer can independently enable or disable these alarms to raise an interrupt. See Section 14.0 Performance Monitoring for a detailed description of the Performance Monitoring and General Alarms.

#### **6.7 TEST INTERFACE**

The IEEE 1149.1 JTAG [4.] port on the device provides access to the built-in test features such as boundary SCAN, Internal SCAN and RAM BIST. It may be used to test the device individually or as part of a more comprehensive circuit board or system test. (NOTE: The internal SCAN and RAM BIST functions are not intended for user access. Therefore, the device user should never assert the Test\_se pin.)

#### **6.8 LOOPBACKS**

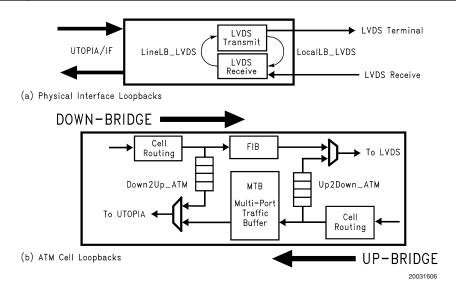

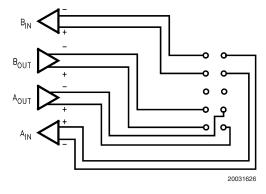

To assist in diagnostic testing, the device provides both LVDS interface loopbacks and ATM cell loopbacks. The former is suitable for designer or commission testing when the device is not passing live traffic. The latter allows cell trace testing on live traffic. The ATM cell loopback operates by recognizing the user-defined cell header of the special loopback cells. The available loopback options are shown in *Table 10*.

In addition to providing a live round trip test via the cell loopbacks, the DS92UT16 helps pinpoint failures between transmit and receive paths by counting the number of loopback cells received.

All loopbacks are programmable via the microprocessor interface.

## **TABLE 10. Loopback Options**

| LineLB_LVDS  | Physical loopback at the LVDS interface. Loop entering LVDS traffic back out of the device. |

|--------------|---------------------------------------------------------------------------------------------|

| LocalLB_LVDS | Physical loopback at the LVDS interface. Loop exiting LVDS traffic back into the device.    |

| Up2Down_ATM  | ATM loopback. Route defined cell entering the device at the LVDS interface back out.        |

| Down2Up_ATM  | ATM loopback. Route defined cell entering the device at the UTOPIA interface back out.      |

FIGURE 7. LVDS Interface and ATM Cell Loopback Options

## 7.0 Signal Description

Package ball assignment in Section 20.0 Package

**TABLE 11. Pin Description**

| Signal Name      | Description                                | Width | Signal Type     | Polarity    | Internal<br>Bias |

|------------------|--------------------------------------------|-------|-----------------|-------------|------------------|

| UTOPIA INTERFACE |                                            |       |                 |             | 1                |

| U_TxData [15:0]  | Transmit toward the PHY Layer data bus.    | 16    | BiDir (Note 2)  |             |                  |

| U_TxParity       | Transmit data bus parity bit. (odd parity) | 1     | BiDir (Note 2)  |             |                  |

| U_TxCLAV [7:1]   | Transmit cell available - Extended.        | 7     | Input (Note 3)  | Active High | Pull Down        |

| U_TxCLAV [0]     | Transmit cell available - Normal/Extended. | 1     | BiDir (Note 1)  | Active High | Pull Down        |

| U_TxENB [7:1]    | Enable Data transfers - Extended.          | 7     | Output (Note 3) | Active Low  |                  |

| U_TxENB [0]      | Enable Data transfers - Normal/Extended.   | 1     | BiDir (Note 2)  | Active Low  |                  |

| U_TxSOC          | Transmit Start Of Cell.                    | 1     | BiDir (Note 2)  | Active High |                  |

| U_TxAddr [4:0]   | Address of MPHY device being selected.     | 5     | BiDir (Note 2)  |             |                  |

| U_RxData [15:0]  | Receive from the PHY Layer data bus.       | 16    | BiDir (Note 1)  |             |                  |

| U_RxParity       | Receive data bus parity bit. (odd parity)  | 1     | BiDir (Note 1)  |             |                  |

| U_RxCLAV [7:1]   | Receive cell available - Extended.         | 7     | Input (Note 3)  | Active High | Pull Down        |

| U_RxCLAV [0]     | Receive cell available - Normal/Extended.  | 1     | BiDir (Note 1)  | Active High | Pull Down        |

| U_RxENB [7:1]    | Enable Data transfers - Extended.          | 7     | Output (Note 3) | Active Low  |                  |

| U_RxENB [0]      | Enable Data transfers - Normal/Extended.   | 1     | BiDir (Note 2)  | Active Low  |                  |

| U_RxSOC          | Receive Start Of Cell.                     | 1     | BiDir (Note 1)  | Active High |                  |

| U_RxAddr [4:0]   | Address of MPHY device being selected.     | 5     | BiDir (Note 2)  |             |                  |

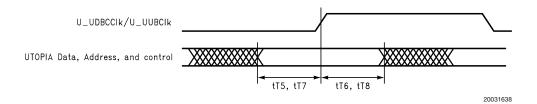

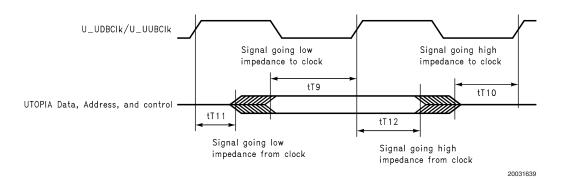

| U_UDBClk         | UTOPIA Down Bridge - Input transfer clock. | 1     | Input (Note 4)  |             |                  |

| U_UUBCIk         | UTOPIA Up Bridge - Output transfer clock.  | 1     | Input (Note 5)  |             |                  |

## 7.0 Signal Description (Continued)

TABLE 11. Pin Description (Continued)

| Signal Name                           | Description                                    | Width | Signal Type | Polarity              | Internal<br>Bias |

|---------------------------------------|------------------------------------------------|-------|-------------|-----------------------|------------------|

| LVDS INTERFACE                        | 1                                              |       |             | 1                     |                  |

| LVDS_ADout[+,-]                       | A Serial data differential outputs.            | 2     | Output      |                       |                  |

| LVDS_BDout[+,-]                       | B Serial data differential outputs.            | 2     | Output      |                       |                  |

| LVDS_ADenb                            | Serial transmit data A output enable.          | 1     | Input       | Active High           | Pull Up          |

| LVDS_BDenb                            | Serial transmit data B output enable.          | 1     | Input       | Active High           | Pull Up          |

| LVDS_Synch                            | External control to transmit SYNCH patterns on | 1     | Input       | Active High           | Pull Down        |

|                                       | serial interface.                              |       |             |                       |                  |

| LVDS_TxClk                            | Transmit clock.                                | 1     | Input       |                       |                  |

| LVDS_TxPwdn                           | Transmit section power down                    | 1     | Input       | Active Low            | Pull Up          |

| LVDS_ADin[+,-]                        | PortA Serial data differential inputs.         | 2     | Input       |                       |                  |

| LVDS_ALock_n                          | PortA Clock recovery lock status               | 1     | Output      |                       |                  |

| LVDS_ARxClk                           | PortA Recovered clock.                         | 1     | Output      |                       |                  |

| LVDS_ARefClk                          | PortA Reference clock for receive PLLs.        | 1     | Input       |                       |                  |

| LVDS_APwdn                            | PortA Power Down.                              | 1     | Input       | Active Low            | Pull Up          |

| LVDS_BDin[+,-]                        | PortB Serial data differential inputs.         | 2     | Input       |                       |                  |

| LVDS_Block_n                          | PortB Clock recovery lock status.              | 1     | Output      |                       |                  |

| LVDS_BRxClk                           | PortB Recovered clock.                         | 1     | Output      |                       |                  |

| LVDS_BRefClk                          | PortB Reference clock for receive PLLs.        | 1     | Input       |                       |                  |

| LVDS_BPwdn                            | PortB Power Down.                              | 1     | Input       | Active Low            | Pull Up          |

| CPU & GENERAL CO                      | ONTROL                                         |       |             |                       |                  |

| CPU_cs                                | Select signal used to validate the address bus | 1     | Input       | Active Low            |                  |

|                                       | for read and write data transfers.             |       |             |                       |                  |

| CPU_rd (CPU_ds)                       | Read or Data Strobe, depending on CPU_BusMode. | 1     | Input       | Active Low            |                  |

| CPU_wr (CPU_rnw)                      | Write or Read/Write, depending on CPU_BusMode. | 1     | Input       | Active Low<br>(Write) |                  |

| CPU_int                               | Interrupt request line.                        | 1     | Output      | Active Low            | Open Drain       |

| CPU_Data[7:0]                         | Data bus.                                      | 8     | BiDir       |                       |                  |

| CPU_Addr[7:0]                         | Address bus.                                   | 8     | Input       |                       |                  |

| CPU_BusMode                           | Mode select for bus protocol.                  | 1     | Input       |                       | Pull Down        |

| GPIO [3:0]                            | General Purpose Input/Output.                  | 4     | BiDir       |                       |                  |

| Reset_n                               | Reset min pulse is 2X slowest clock period.    | 1     | Input       | Active Low            | Pull Up          |

| JTAG TEST INTERFA                     | ACE                                            |       |             |                       |                  |

| JTAG_CLK                              | Test clock.                                    | 1     | Input       |                       |                  |

| JTAG_Reset                            | Test circuit reset.                            | 1     | Input       | Active Low            | Pull Up          |

| JTAG_TMS                              | Test Mode Select.                              | 1     | Input       |                       | Pull Up          |

| JTAG_TDI                              | Test Data In.                                  | 1     | Input       |                       | <u> </u>         |

| JTAG_TDO                              | Test Data Out.                                 | 1     | Output      |                       |                  |

| Test_se                               | SCAN enable (for manufacturing test only)      | 1     | Input       | Active High           | Pull Down        |

| TOTAL PIN COUNT                       | 3 77                                           |       |             |                       |                  |

| Total Functional I/O                  |                                                |       |             | 133                   |                  |

| LVDS V <sub>DD</sub> /V <sub>SS</sub> | 3.3V LVDS power for analog and digital         | 46    |             |                       |                  |

| CV <sub>DD</sub> /CV <sub>SS</sub>    | 2.5V Core Power for digital functions          | 6     |             |                       |                  |

| IOV <sub>DD</sub> /IOV <sub>SS</sub>  | 3.3V I/O power ring                            |       |             | 8                     |                  |

| Total Power                           |                                                |       |             | 60                    |                  |

| No Connect                            | No signal connected to this pin                |       |             | 3                     |                  |

|                                       | ,                                              | 196   |             |                       |                  |

13

## 7.0 Signal Description (Continued)

#### TABLE 11. Pin Description (Continued)

Note 2: These pins are Outputs in ATM Layer mode and Inputs PHY Layer mode.

Note 3: These pins are only used in PHY layer mode, Extended 248 PHY mode. In Normal 31 PHY mode or ATM layer mode, they must be unconnected.

Note 4: In PHY layer mode this is the Utopia TxClk and in ATM layer mode this is the Utopia RxClk.

Note 5: In PHY layer mode this is the Utopia RxClk and in ATM layer mode this is the Utopia TxClk.

## 8.0 UTOPIA Interface Operation

This section describes the operation of the UTOPIA Interface of the DS92UT16. The UTOPIA interface mode of operation is defined in the UTOPIA Configuration (UCFG) register described in *Section 18.59 UTOPIA CONFIGURATION—0xA0 UCFG*. The format of the PDU cells carried over this interface is defined in the PDU Configuration (PDUCFG) register described in *Section 18.5 PDU CONFIGURATION—0x05 PDUCFG*.

The interface can operate in ATM layer mode or PHY layer mode. When operating as a Level 2 ATM layer interface, the protocol can be extended to cope with up to 248 PHY ports rather than the maximum 31 allowed by the standard Level 2 definition. This Extended Level 2 mode is achieved with eight CLAV and eight ENB signals.

On power up the device defaults to ATM layer mode. To prevent potential contention on the Utopia interface signals, all the Utopia pins which are bidirectional are configured as outputs in tri-state mode and the Utopia interface block is disabled. The user must select the device operating mode, ATM layer or PHY layer, by writing the appropriate value to the UMODE bit of the UCFG register before enabling the Utopia interface block and releasing the Utopia interface pins. Enabling the Utopia interface and releasing the Utopia pins is achieved by setting the UBDEN bit of the UCFG register.

## 8.1 UTOPIA BASIC LEVEL 2 MODE - 31 PORTS (Default Mode)

In UTOPIA Level 2 mode:

8-bit or 16-bit data buses are controlled by the BWIDTH bit of the UCFG register. In 8-bit mode only U\_TxData[7:0] and U\_RxData[7:0] are valid; parity is calculated and checked only over these bits of the data buses and the upper bits of the data buses are not used.

In 16-bit mode of the full U\_TxData[15:0] and U\_RxData[15:0] are valid and parity is calculated over all bits of the data buses.

- One ATM Layer can communicate with up to 31 PHY ports using the MPhy address busses U\_TxAddr[4:0] and U\_RxAddr[4:0] and the control signals U\_TxCLAV[0], U\_RxCLAV[0], U\_TxENB[0] and U\_RxENB[0].

- U\_TxCLAV[7:1], U\_RxCLAV[7:1], U\_TxENB[7:1] and U\_RxENB[7:1] are not used.

- All Queues from 30 to 0 of the MTB may be used. There

is one queue for each MPhy address so the use of the

queues will depend on the connected ports list defined by

the UCPL3-UCPL0 registers.

- Uses the connected ports list defined by the UCPL3-UCPL0 registers. In ATM mode, these registers are used to determine the ports that should be polled. In PHY mode, these registers are used to determine which MPhy addresses the device should respond to during polling.

- The connected sub-port list defined in the UCSPL register is not used.

- The sub-port address location defined by USPAL and USPAM registers is not used.

- The CLAV mode bits CLVM[1:0] of the UCFG register should be defined as CLVM[1:0] = 00.

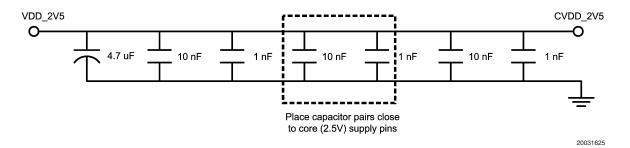

The configuration of the inputs/outputs of the UTOPIA Level 2 interface for ATM Layer mode and PHY Layer mode is shown in *Figure 8*. The main difference is that in ATM mode the CLAV pins are inputs and the MPhy Address and ENB pins are outputs; whereas in PHY mode, the CLAV pins are outputs and the MPhy Address and ENB pins are inputs.

Note that in ATM Layer mode the DS92UT16 does not generate the UTOPIA clocks and must be supplied with these clocks just as in PHY mode.

## 8.0 UTOPIA Interface Operation (Continued)

FIGURE 8. Basic UTOPIA Level 2 UMODE Configuration

## 8.1.1 ATM Polling

When configured as an ATM Layer device, the DS92UT16 polls the connected PHY ports using the MPhy address busses U\_TxAddr and U\_RxAddr. Only those ports which are connected will be polled. The connected ports list defined in the UCPL3-UCPL0 registers is used to determine which ports are connected. The PHY ports respond only on U\_TxCLAV[0] and U\_RxCLAV[0]. On reset the UCPL3-UCPL0 registers are all set to 0xFF so the DS92UT16 will poll all ports.

#### 8.1.2 PHY Polling

When configured as a PHY Layer device the DS92UT16 is polled by the connected ATM device. During polling the DS92UT16 will only respond to MPhy addresses, on U\_TxAddr and U\_RxAddr, which are defined as connected. The connected ports list defined in the UCPL3-UCPL0 registers is used to determine which ports are connected. On reset the UCPL3-UCPL0 registers are all set to 0xFF so the DS92UT16 will respond to all MPhy addresses during polling. The DS92UT16 responds only on U\_TxCLAV[0] and U\_RxCLAV[0].

**NOTE:** There must always be at least one connected port defined in the UCPL3–UCPL0 registers. If no ports are to be connected then use Configuration Traffic Inhibit mode described in *Section 10.0 Configuration and Traffic Inhibit Operation*.

#### 8.2 UTOPIA EXTENDED LEVEL 2 MODE - 248 PORTS

In UTOPIA Extended Level 2 mode:

8-bit or 16-bit data buses are controlled by the BWIDTH bit of the UCFG register. In 8-bit mode, only U\_TxData[7:0] and U\_RxData[7:0] are valid; parity is calculated and checked only over these bits of the data buses. In 16-bit mode, the full U\_TxData[15:0] and U\_RxData[15:0] are valid; parity is calculated and checked over all bits of the data buses.

- In ATM mode, the DS92UT16 can communicate with up to 248 PHY ports using the MPhy address busses U\_TxAddr[4:0] and U\_RxAddr[4:0], and the control signals U\_TxCLAV[7:0], U\_RxCLAV[7:0], U\_TxENB[7:0] and U\_RxENB[7:0]. In PHY mode, the DS92UT16 behaves as a standard Level 2 device and only 31 ports are needed using the MPhy address busses U\_TxAddr[4:0] and U\_RxAddr[4:0], and the control signals U\_TxCLAV[0], U\_RxCLAV[0], U\_TxENB[0] and U\_RxENB[0].

- All Queues from 30 to 0 of the MTB may be used. There

is one queue for each MPhy address so the use of the

queues will depend on the connected ports list defined by

the UCPL3-UCPL0 registers.

- The connected ports list defined by the UCPL3-UCPL0 registers and the connected sub-port list defined in the UCSPL register are used. In ATM mode, these registers are used to determine which ports should be polled. In PHY mode, these registers are used to determine which MPhy addresses the device should respond to during polling.

- The sub-port address location defined by USPAL and USPAM registers is used in ATM mode to determine the location of the 3-bit sub-port address in the PDU cell. In PHY mode these registers are not used.

- The CLAV mode bits CLVM[1:0] of the UCFG register should be defined as CLVM[1:0] = 11.

The configuration of the inputs/outputs of the UTOPIA Level 2 interface for ATM Layer mode and PHY Layer mode is shown in *Figure 9*.

## 8.0 UTOPIA Interface Operation (Continued)

FIGURE 9. Extended UTOPIA Level 2 UMODE Configuration

The main difference is that in ATM mode the CLAV pins are inputs and the MPhy Address and ENB pins are outputs, whereas in PHY mode the CLAV pins are outputs and the MPhy Address and ENB pins are inputs. Also, in ATM mode all eight CLAV and ENB pins are used, but in PHY mode only one of the CLAV and ENB pins are used.

Note that in ATM Layer mode the DS92UT16 does not generate the UTOPIA clocks but must be supplied with these clocks just as in PHY mode.

#### 8.2.1 ATM Polling

When configured as an ATM Layer device, the DS92UT16 polls the connected PHY ports using the MPhy address busses U\_TxAddr and U\_RxAddr. Only those ports which are connected will be polled. The connected ports list defined in the UCPL3-UCPL0 registers is used to determine which ports are connected. The PHY ports respond on U\_TxCLAV[7:0] and U\_RxCLAV[7:0]. The MPhy address determines the Port and the CLAV pin number determines the sub-port. Therefore up to 8 sub-ports may be connected to a port. Polling of a single MPhy address will get eight responses on the eight CLAV lines. The DS92UT16 uses the connected sub-port list defined in the UCSPL register to determine which of these eight sub-port responses are valid. On reset, the UCPL3-UCPL0 registers are all set to 0xFF and the UCSPL register is set to 0x01, so the DS92UT16 will poll all ports and assume only sub-port zero is connected.

## 8.2.2 PHY Polling

When configured as a PHY Layer device, the DS92UT16 is polled by the connected ATM device. During polling, the DS92UT16 will only respond to MPhy addresses on U\_TxAddr and U\_RxAddr, which are defined as connected. The connected ports list defined in the UCPL3-UCPL0 registers is used to determine which ports are connected. On

reset the UCPL3-UCPL0 registers are all set to 0xFF so the DS92UT16 will respond to all MPhy addresses during polling.

**NOTE:** There must always be at least one connected port defined in the UCPL3–UCPL0 registers. If no ports are to be connected then use Configuration Traffic Inhibit mode described in *Section 10.0 Configuration and Traffic Inhibit Operation*.

#### 8.2.3 Sub-Port Address

The operation of the sub-port address is illustrated in *Figure 10*. To use the Extended Level 2 mode that allows addressing up to 248 Ports, the ATM Layer (that which drives the DS92UT16 in PHY mode) must be capable of inserting a three bit sub-port address in the PDU cell for use by the DS92UT16. This 3-bit sub-port address must reside in either the User Prepend, Cell Header, or UDF bytes. It's location is defined in the UTOPIA Sub-Port Address Location (USPAL) and UTOPIA Sub-Port Address Mask (USPAM) registers. The USPAL register defines which byte of the User Prepend, Cell Header, or UDF, contains the address and the USPAM register defines which three bits of that byte are the sub-port address.

**Transmit Path Example:** The MPhy address is interpreted as the Port address. So, a cell destined for the PHY designated as Port 0 Sub-Port 7 has the three bit sub-port address 7 (binary "111") inserted into the defined sub-port address location of the PDU cell by the ATM layer head-end. It is then transmitted to the DS92UT16 in PHY mode using MPhy address 0. The DS92UT16 in PHY mode does not examine the sub-port address because all cells are transmitted downbridge anyway.

At the far end, the DS92UT16 in ATM mode extracts the sub-port address. This is used to determine which sub-port CLAV/ENB signals the destination PHY is connected to. A

## 8.0 UTOPIA Interface Operation

(Continued)

port address of 0 and a sub-port address of 7 means that the destination PHY is MPhy address 0 attached to U\_TxENB[7] and U\_TxCLAV[7]. The cell is then transmitted to that PHY.

FIGURE 10. Sub-Port Address Operation

Receive Path Example: The DS92UT16 in ATM mode receives a cell from the PHY with MPhy address 0 attached to U\_RxENB[6] and U\_RxCLAV[6] and designates it as from Port 0 Sub-Port 6. The DS92UT16 inserts the sub-port address 6 (binary "110") into the sub-port address location of the received PDU. Then this PDU is transmitted to the head-end. The head-end ATM layer device must extract this sub-port address from the PDU to determine the full address of the originating PHY.

#### 8.2.4 Connected Port and Sub-Port Lists

Figure 11 illustrates the usage of the connected port list registers (UCPL3–UCPL0) and the connected sub-port list register (UCSPL). In this case, the DS92UT16 in ATM mode defines Port 1 and Sub-port 7 as not connected.

The UCPL3-UCPL0 registers contain 31 bits corresponding to the 31 possible Ports addressed by the MPhy address busses. If a bit location in the UCPL3-UCPL0 registers is set, then that Port is connected. The sub-ports of the con-

## 8.0 UTOPIA Interface Operation

(Continued)

nected Port are defined by the UCSPL register. If a bit location in the UCSPL register is set, then that sub-port is connected.

In Figure 11, the registers are set as follows: UCPL3 = UCPL2 = UCPL1 = 0xF, UCPL0 = 0xFD, and UCSPL = 0xEF.

With bit 1 of UCPL0 cleared, then Port 1 is not connected. This means that none of the eight sub-ports of Port 1 are connected. So Port 1 Sub-port 7, Port 1 Sub-port 6, Port 1 Sub-port 5, Port 1 Sub-port 4, Port 1 Sub-port 3, Port 1

Sub-port 2, Port 1 Sub-port 1, and Port 1 Sub-port 0 are not connected. Port 1 will therefore, not be polled.

With bit 7 of UCSPL cleared, then sub-port 7 is not connected. This means that sub-port 7 for all possible 31 ports is not connected. So Port 31 Sub-port 7, Port 30 Sub-port 7, Port 29 Sub-port 7,.....and Port 0 Sub-port 7 are not connected.

Therefore, clearing a bit in the UCPL3–UCPL0 registers will disconnect 8 possible PHY port locations and clearing a bit in the UCSPL register will disconnect 31 possible PHY port locations.

FIGURE 11. Connected Port and Connected Sub-Port Usage

## 9.0 MTB Queue Configuration

### 9.1 SINGLE BRIDGE MTB CONFIGURATION

The Multi-port Traffic Buffer is a 160 cell linked-list buffer that is shared across as many as 31 Port queues. There is a single queue per MPHY address.

In the up-bridge direction, a per queue flow control protocol (described in *Section 6.3.5 Flow Control*) prevents queue overflow. Each Port has a programmable upper fill threshold. Should any queue reach this upper threshold, back-pressure is applied over the serial link, via the flow control mechanism, to the far end (transmitting) device. The transmitting device uses the normal UTOPIA flow control handshaking to prevent any more cells being transferred to that MPHY and thus prevents overflow.

With link-list buffers, each queue may be over-assigned memory space, working on the assumption that not every queue will back up simultaneously. To accommodate the rare occasions where the buffer as a whole approaches full but individual queues are below their full threshold, the device also compares the overall buffer fill against a threshold. Should the overall buffer approach overflow, the flow control mechanism provides a global 'halt' command to ensure that no cells will be lost.

The MTB Queue Threshold, MTBQT30-MTBQT0 registers define the maximum size in PDU cells of each of the 31 queues. If all 31 queues are being used it is recommended that the threshold be left at the default of 4 cells. If less than 31 queues are in use then the queue thresholds may be raised if required. The recommended maximum queue thresholds are given in *Table 12*. These are recommended maximum thresholds only.

## 9.0 MTB Queue Configuration

(Continued)

It is further recommended that any queue that is not being used is set with a threshold of zero. When a queue has reached its programmed threshold the device flow control mechanism will prevent the far end device from accepting cells for that MPHY address. Therefore, by setting the threshold of an unused queue to zero, it prevents the UTO-

PIA interface of the far end device from accepting cells for that MPHY address by either, not asserting the CLAV for that MPHY address when in PHY Mode, or not selecting that MPHY address when in ATM mode.

Also, note that setting a threshold of zero will cause the corresponding Queue Full bit in the MTBQFL3-MTBQFL0 registers to be continuously set for that queue.

TABLE 12. Recommended Maximum MTB Queue Thresholds

| Number of     | Recommended | Number of     | Recommended |

|---------------|-------------|---------------|-------------|

| Queues in Use | Threshold   | Queues in Use | Threshold   |

| 31            | 4           | 15            | 15          |

| 30            | 4           | 14            | 16          |

| 29            | 5           | 13            | 18          |

| 28            | 5           | 12            | 20          |

| 27            | 5           | 11            | 23          |

| 26            | 6           | 10            | 26          |

| 25            | 6           | 9             | 29          |

| 24            | 7           | 8             | 34          |

| 23            | 7           | 7             | 39          |

| 22            | 8           | 6             | 47          |

| 21            | 9           | 5             | 58          |

| 20            | 10          | 4             | 74          |

| 19            | 10          | 3             | 100         |

| 18            | 11          | 2             | 100         |

| 17            | 12          | 1             | 154         |

| 16            | 4           |               |             |

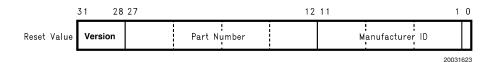

#### 9.2 MULTIPLE BRIDGE MTB CONFIGURATION