#### 查询MAX2310EEI供应商

捷多邦,专业PCB打样工厂,24小时加急出货

### 19-1507; Rev 1; 3/03 EVALUATION KIT AVAILABLE CDMA IF VGAs and I/Q Demodulators with VCO and Synthesizer

#### **General Description**

The MAX2310/MAX2312/MAX2314/MAX2316 are IF receivers designed for dual-band, dual-mode, and single-mode N-CDMA and W-CDMA cellular phone systems. The signal path consists of a variable gain amplifier (VGA) and I/Q demodulator. The devices feature guaranteed +2.7V operation, a dynamic range of over 110dB, and high input IP3 (-33dBm at 35dB gain, 1.7dBm at -35dB).

Unlike similar devices, the MAX2310 family of receivers includes dual oscillators and synthesizers to form a self-contained IF subsystem. The synthesizer's reference and RF dividers are fully programmable through a 3-wire serial bus, enabling dual-band system architectures using any common reference and IF frequency. The differential baseband outputs have enough bandwidth to suit both N-CDMA and W-CDMA systems, and offer saturated output levels of 2.7Vp-p at a low +2.75V supply voltage. Including the low-noise voltage-controlled oscillator (VCO) and synthesizer, the MAX2310 draws only 26mA from a +2.75V supply in CDMA (differential IF) mode.

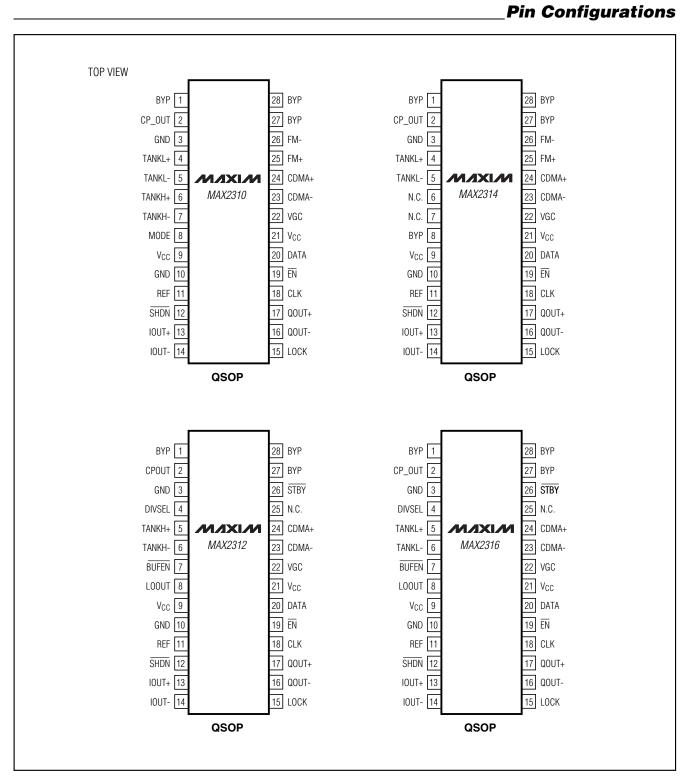

The MAX2310/MAX2312/MAX2314/MAX2316 are available in 28-pin QSOP packages.

#### **Applications**

Single/Dual/Triple-Mode CDMA Handsets

Globalstar Dual-Mode Handsets

Wireless Data Links

Tetra Direct-Conversion Receivers

Wireless Local Loop (WLL)

#### **Features**

- Complete IF Subsystem Includes VCO and Synthesizer

- Supports Dual-Band, Triple-Mode Operation

- VGA with >110dB Gain Control

- Quadrature Demodulator

- High Output Level (2.7V)

- Programmable Charge-Pump Current

- Supports Any IF Frequency Between 40MHz and 300MHz

- 3-Wire Programmable Interface

- Low Supply Voltage (+2.7V)

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX2310EEI | -40°C to +85°C | 28 QSOP     |

| MAX2312EEI | -40°C to +85°C | 28 QSOP     |

| MAX2314EEI | -40°C to +85°C | 28 QSOP     |

| MAX2316EEI | -40°C to +85°C | 28 QSOP     |

|            |                |             |

Pin Configurations appear at end of data sheet. Block Diagram appears at end of data sheet.

#### \_Selector Guide

| PART    | MODE                                | DESCRIPTION                                                                          | INPUT RANGE     |

|---------|-------------------------------------|--------------------------------------------------------------------------------------|-----------------|

| MAX2310 | AMPS,<br>Cellular CDMA,<br>PCS CDMA | Dual Band, Triple Mode                                                               | 40MHz to 300MHz |

| MAX2312 | PCS CDMA                            | Single Band, Single Mode                                                             | 67MHz to 300MHz |

| MAX2314 | AMPS,<br>Cellular CDMA              | Single Band, Dual Mode                                                               | 40MHz to 150MHz |

| MAX2316 | Cellular CDMA                       | Single Band, Single Mode or<br>Single Band, Dual Mode with<br>External Discriminator | 40MHz to 150MHz |

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND        | 0.3V, +6.0V                      |

|-------------------------------|----------------------------------|

| SHDN to GND                   | 0.3V to (V <sub>CC</sub> + 0.3V) |

| STBY, BUFEN, MODE, EN, DATA,  |                                  |

| CLK, DIVSEL                   | 0.3V to (V <sub>CC</sub> + 0.3V) |

| VGC to GND0.3V, the lesser of | of +4.2V or $(V_{CC} + 0.3V)$    |

| AC Signals TankH ±, TankL ±,  |                                  |

| REF, FM ±, CDMA ±             | 1.0V peak                        |

|                               |                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +2.7V \text{ to } +5.5V, \text{ MODE} = \text{DIVSEL} = \overline{\text{SHDN}} = \overline{\text{STBY}} = \overline{\text{BUFEN}} = \text{high}, \text{ differential output load} = 10 \text{k}\Omega, \text{ } \text{T}_{\text{A}} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ registers set to default power-up settings}. Typical values are at V_{CC} = +2.75V and T_{\text{A}} = +25^{\circ}\text{C}, \text{ unless otherwise noted}.)$

| PARAMETER                                    | SYMBOL           | COND                                           | ITIONS                                        | MIN | ТҮР                   | MAX  | UNITS |

|----------------------------------------------|------------------|------------------------------------------------|-----------------------------------------------|-----|-----------------------|------|-------|

|                                              |                  | CDMA mode                                      | $T_A = +25^{\circ}C$                          |     | 25.9                  | 37.5 |       |

|                                              |                  | CDIMA Mode                                     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |                       | 41.5 |       |

|                                              |                  | FM IQ mode                                     | $T_A = +25^{\circ}C$                          |     | 25.4                  | 36.7 |       |

|                                              |                  | FIVE IQ HIOUE                                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |                       | 40.6 |       |

|                                              |                  | FM I mode                                      | $T_A = +25^{\circ}C$                          |     | 24.7                  | 35.7 |       |

| Supply Current (Note 1)                      | Icc              | TWITHOUG                                       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |                       | 39.5 | mA    |

|                                              |                  | STANDBY (VCO_H)                                | $T_A = +25^{\circ}C$                          |     | 12.3                  | 18.8 |       |

|                                              |                  |                                                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |                       | 20.7 |       |

|                                              |                  | STANDBY (VCO_L)                                | $T_A = +25^{\circ}C$                          |     | 11.5                  | 18.4 |       |

|                                              |                  | STANDET (VCO_L)                                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |                       | 20.3 |       |

|                                              |                  | Addition for LO out $(\overline{B})$           | JFEN = low)                                   |     | 3.5                   |      |       |

| Shutdown Current                             | Icc              | $\overline{\text{SHDN}} = \text{low}$          |                                               |     | 1.5                   | 10   | μA    |

| Register Shutdown Current                    | ICC              |                                                |                                               |     | 3                     | 5.8  | mA    |

| Logic High                                   |                  |                                                |                                               | 2.0 |                       |      | V     |

| Logic Low                                    |                  |                                                |                                               |     |                       | 0.5  | V     |

| Logic High Input Current                     | Ιн               |                                                |                                               | 2   |                       |      | μA    |

| Logic Low Input Current                      | ١ <sub>١</sub> ٢ |                                                |                                               |     |                       | 2    | μA    |

| VGC Control Input Current                    |                  | $0.5V < V_{VGC} < 2.3V$                        |                                               | -5  |                       | 5    | μΑ    |

| VGC Control Input Current<br>During Shutdown |                  | SHDN = low                                     |                                               |     |                       | 1    | μA    |

| Lock Indicator High (locked)                 |                  | 50k $\Omega$ load                              |                                               | 2.0 |                       |      | V     |

| Lock Indicator Low (unlocked)                |                  | 50k $\Omega$ load                              |                                               |     |                       | 0.5  | V     |

| DC Offset Voltage                            |                  | I+ to I- and Q+ to Q-, PLL locked -20 ±1.5 +20 |                                               | +20 | mV                    |      |       |

| Common-Mode Output Voltage                   |                  | V <sub>CC</sub> = 2.75V                        |                                               |     | V <sub>CC</sub> - 1.4 |      | V     |

### **AC ELECTRICAL CHARACTERISTICS**

(MAX2310/MAX2314 or MAX2312/MAX2316 EV kit,  $V_{CC} = +2.75V$ , registers set to default power-up states,  $f_{IN} = 210.88MHz$  for CDMA,  $f_{IN} = 85.88MHz$  for FM,  $f_{REF} = 19.68MHz$ , synthesizer locked with passive 2nd-order lead-lag loop filter, SHDN = high, VGC set for +35dB voltage gain, differential output load =  $10k\Omega$ , all power levels referred to  $50\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                  | SYMBOL           | COND                                               | MIN          | TYP   | MAX   | UNITS |        |

|--------------------------------------------|------------------|----------------------------------------------------|--------------|-------|-------|-------|--------|

| Input Frequency                            | fin              | (Note 2)                                           |              | 40    |       | 300   | MHz    |

| Reference Frequency                        | fref             | (Note 2)                                           |              |       |       | 39    | MHz    |

| Frequency Reference Signal<br>Level        | VREF             |                                                    |              | 0.2   |       |       | Vp-р   |

| SIGNAL PATH, CDMA MODE                     |                  |                                                    |              |       |       |       |        |

| Inc. It Third Order Intereent              |                  | Gain = -35dB (Note 3)                              |              |       | 1.7   |       | alDuna |

| Input Third-Order Intercept                | IIP3             | Gain = +35dB (Note 4                               | )            |       | -33.2 |       | dBm    |

| Innut 1dD Compression                      | Dur              | Gain = -35dB                                       |              | -9    | -6.4  |       | alDura |

| Input 1dB Compression                      | P1dB             | Gain = +35dB                                       |              | -44   | -38.3 |       | dBm    |

| Input 0.0EdB Deconsitization               |                  | (Note 5)                                           | Gain = -35dB |       | -14.8 |       | dBm    |

| Input 0.25dB Desensitization               |                  | (NOLE 5)                                           | Gain = +35dB |       | -49   |       | иып    |

| Minimum Voltage Gain                       | Av               | V <sub>GC</sub> = 0.5V (Note 6)                    |              |       | -54.8 | -49   | dB     |

| Maximum Voltage Gain                       | Av               | V <sub>GC</sub> = 2.3V (Note 6)                    |              | 56    | 61.3  |       | dB     |

|                                            |                  | Gain = -35dB                                       |              |       | 62.9  |       | -10    |

| DSB Noise Figure                           | NF               | Gain = +35dB                                       |              |       | 6.36  |       | dB     |

| SIGNAL PATH, FM_IQ MODE                    |                  |                                                    |              | 1     |       |       | 1      |

| Input Third-Order Intercept                | IIP3             | (Nioto 7)                                          | Gain = -35dB |       | -6.0  |       | dDm    |

| input mird-Order intercept                 | IIFS             | (Note 7)                                           | Gain = +35dB |       | -31   |       | dBm    |

| Input 1dB Comprossion                      | Dur              | (Nistee 6, 8)                                      | Gain = -35dB | -20   | -16.2 |       | dBm    |

| Input 1dB Compression                      | P <sub>1dB</sub> | (Notes 6, 8)                                       | Gain = +35dB | -44   | -38.4 |       |        |

| Minimum Voltage Gain                       | Av               | VGC = 0.5V (Note 6)                                |              |       | -50.2 | -47.4 | dB     |

| Maximum Voltage Gain                       | Av               | V <sub>GC</sub> = 2.3V (Note 6)                    |              | 58.5  | 63.4  |       | dB     |

| SIGNAL PATH, CDMA and FM                   | IQ MODE          |                                                    |              |       |       |       |        |

| Maximum Gain Variation<br>Over Temperature |                  | Normalized to +25°C                                |              |       | ±2.5  |       | dB     |

| Baseband 0.5dB Bandwidth                   |                  |                                                    |              |       | 4.2   |       | MHz    |

| Quadrature Suppression                     |                  | TA = T <sub>MIN</sub> to T <sub>MAX</sub> (Note 6) |              | +28   | +35   |       | dB     |

| LO to Baseband Leakage                     |                  |                                                    |              |       | 1     |       | mVp-p  |

| Saturated Output Level                     | VSAT             | Differential                                       |              |       | 2.7   |       | Vp-р   |

| PHASE-LOCKED LOOP                          | - I              |                                                    |              |       |       |       |        |

|                                            | fvco_L           | (Noto 2)                                           |              | 80    |       | 300   |        |

| VCO Tune Range                             | fvco_н           | (Note 2)                                           |              | 135   |       | 600   | MHz    |

| LOOUT Output Power                         | PLO              | $R_L = 50\Omega$ , $\overline{BUFEN} = 1c$         |              | -13.7 |       | dBm   |        |

### AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2310/MAX2314 or MAX2312/MAX2316 EV kit,  $V_{CC} = +2.75V$ , registers set to default power-up states,  $f_{IN} = 210.88MHz$  for CDMA,  $f_{IN} = 85.88MHz$  for FM,  $f_{REF} = 19.68MHz$ , synthesizer locked with passive 2nd-order lead-lag loop filter, SHDN = high, VGC set for +35dB voltage gain, differential output load = 10k $\Omega$ , all power levels referred to 50 $\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                      | SYMBOL | CONDITIONS                                                                    | MIN   | ΤΥΡ  | MAX  | UNITS  |

|------------------------------------------------|--------|-------------------------------------------------------------------------------|-------|------|------|--------|

| VCO Minimum Divide Ratio                       | M1, M2 |                                                                               |       |      | 256  |        |

| VCO Maximum Divide Ratio                       | M1, M2 |                                                                               | 16383 |      |      |        |

| REF Minimum Divide Ratio                       | R1, R2 |                                                                               |       |      | 2    |        |

| REF Maximum Divide Ratio                       | R1, R2 |                                                                               | 2047  |      |      |        |

| Minimum Phase Detector<br>Comparison Frequency |        | (Note 6)                                                                      |       |      | 20   | kHz    |

| Maximum Phase Detector<br>Comparison Frequency |        | (Note 6)                                                                      | 1500  |      |      | kHz    |

| Base Band Spurious due to PLL                  |        |                                                                               |       |      | -50  | dBc    |

|                                                |        | 1kHz offset                                                                   |       | -72  |      |        |

|                                                |        | 12.5kHz offset                                                                |       | -100 |      |        |

| LOOUT at 85MHz,<br>VCO_L Enabled (Note 9)      |        | 30kHz offset                                                                  |       | -110 |      | dBc/Hz |

|                                                |        | 120kHz offset                                                                 |       | -119 |      |        |

|                                                |        | 900kHz offset                                                                 |       | -125 |      |        |

|                                                |        | 1kHz offset                                                                   |       | -64  |      |        |

|                                                |        | 12.5kHz offset                                                                |       | -91  |      |        |

| LOOUT at 210MHz,<br>VCO_H Enabled (Note 9)     |        | 30kHz offset                                                                  |       | -105 |      | dBc/Hz |

|                                                |        | 120kHz offset                                                                 |       | -115 |      |        |

|                                                |        | 900kHz offset                                                                 |       | -125 |      |        |

| TURBO LOCK                                     |        |                                                                               |       |      |      |        |

|                                                |        | Acquisition, $CPX = XX$ , $TC = 1$                                            | 1480  | 2100 | 2650 |        |

| Charge Durge Course (Ciple                     |        | Locked, CPX = 00                                                              | 105   | 150  | 190  |        |

| Charge-Pump Source/Sink<br>Current             |        | Locked, CPX = 01                                                              | 150   | 210  | 265  | μA     |

|                                                |        | Locked, CPX = 10                                                              | 210   | 300  | 380  | ]      |

|                                                |        | Locked, CPX = 11                                                              | 300   | 425  | 530  |        |

| Charge-Pump Source/Sink<br>Matching            |        | Locked, all values of CPX,<br>0.5V < V <sub>CP</sub> < V <sub>CC</sub> - 0.5V |       | 0.2  | 10   | %      |

**Note 1:** FM\_IQ and FM\_I modes are not available on MAX2312 and MAX2316.

Note 2: Recommended operating frequency range.

**Note 3:** f<sub>1</sub> = 210.88MHz, f<sub>2</sub> = 210.89MHz, P<sub>f1</sub> = P<sub>f2</sub> = -15dBm.

**Note 4:** f<sub>1</sub> = 210.88MHz, f<sub>2</sub> = 210.89MHz, P<sub>f1</sub> = P<sub>f2</sub> = -50dBm.

**Note 5:** Small-signal gain at 200kHz below the LO frequency will be reduced by less than 0.25dB when an interfering signal at 1.25MHz below the LO frequency is applied at the specified level.

**Note 6:** Guaranteed by design and characterization.

**Note 7:**  $f_1 = 85.88MHz$ ,  $f_2 = 85.98MHz$ ,  $P_{f1} = P_{f2} = -15dBm$ .

**Note 8:**  $f_1 = 85.88MHz$ ,  $f_2 = 85.98MHz$ ,  $P_{f1} = P_{f2} = -50dBm$ .

**Note 9:** Measured at LOOUT with BD = 0 (÷2 selected).

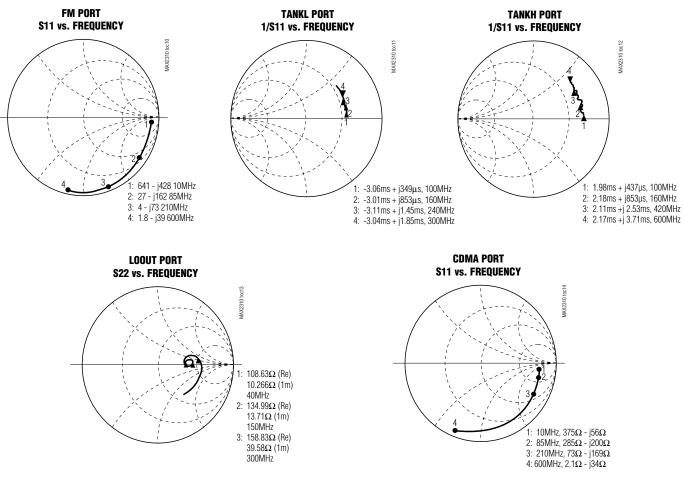

### **Typical Operating Characteristics**

(MAX2310/MAX2314 or MAX2312/MAX2316 EV kit, V<sub>CC</sub> = +2.75V, registers set to default power-up states, f<sub>IN</sub> = 210.88MHz for CDMA, fIN = 85.88MHz for FM, fREF = 19.68MHz, synthesizer locked with passive 2nd-order lead-lag loop filter, SHDN = high, VGC set for +35dB voltage gain, differential output load =  $10k\Omega$ , all power levels referred to  $50\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

5

### **Typical Operating Characteristics (continued)**

(MAX2310/MAX2314 or MAX2312/MAX2316 EV kit,  $V_{CC} = +2.75V$ , registers set to default power-up states,  $f_{IN} = 210.88MHz$  for CDMA,  $f_{IN} = 85.88MHz$  for FM,  $f_{REF} = 19.68MHz$ , synthesizer locked with passive 2nd-order lead-lag loop filter,  $\overline{SHDN} = high$ , VGC set for +35dB voltage gain, differential output load =  $10k\Omega$ , all power levels referred to  $50\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

#### **Pin Description**

|         | PI      | IN      |         | NAME              | FUNCTION                                                                 |

|---------|---------|---------|---------|-------------------|--------------------------------------------------------------------------|

| MAX2310 | MAX2312 | MAX2314 | MAX2316 |                   | FONCTION                                                                 |

| 1       | 1       | 1, 8    | 1       | BYP               | Bypass Node. Must be capacitively decoupled (bypassed) to analog ground. |

| 2       | 2       | 2       | 2       | CP_OUT            | Charge-Pump Output                                                       |

| 3       | 3       | 3       | 3       | GND               | Analog Ground Reference                                                  |

| 4, 5    | _       | 4, 5    | 5, 6    | TANKL+,<br>TANKL- | Differential Tank Input for Low-Frequency Oscillator                     |

|         | 4       | —       | 4       | DIVSEL            | High selects M1/R1; low selects M2/R2.                                   |

### Pin Description (continued)

|         | Р       | IN      |         |                   |                                                                                                                                                                            |

|---------|---------|---------|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX2310 | MAX2312 | MAX2314 | MAX2316 | NAME              | FUNCTION                                                                                                                                                                   |

| 6, 7    | 5, 6    | _       | _       | TANKH+,<br>TANKH- | Differential Tank Input for High-Frequency Oscillator                                                                                                                      |

| _       | 7       | _       | 7       | BUFEN             | LO Buffer Amplifier—active low                                                                                                                                             |

| _       | —       | 6, 7    | _       | N.C.              | No Connection. Must be left open-circuit.                                                                                                                                  |

| 8       |         |         | _       | MODE              | Mode Select. High selects CDMA mode; low selects FM mode.                                                                                                                  |

|         | 8       |         | 8       | LOOUT             | Internal VCO Output. Depending on setting of BD bit, LOOUT is either the VCO frequency (twice the IF frequency) or one-half the VCO frequency (equal to the IF frequency). |

| 9       | 9       | 9       | 9       | V <sub>CC</sub>   | +2.7V to +5.5V Supply for Digital Circuits                                                                                                                                 |

| 10      | 10      | 10      | 10      | GND               | Digital Ground                                                                                                                                                             |

| 11      | 11      | 11      | 11      | REF               | Reference Frequency Input                                                                                                                                                  |

| 12      | 12      | 12      | 12      | SHDN              | Shutdown Input—active low. Low powers down entire device, including registers and serial interface.                                                                        |

| 13, 14  | 13, 14  | 13, 14  | 13, 14  | IOUT+,<br>IOUT-   | Differential In-Phase Baseband Output, or FM signal output FM_I mode is selected.                                                                                          |

| 15      | 15      | 15      | 15      | LOCK              | Lock Output—open-collector pin. Logic high indicates phase-<br>locked condition.                                                                                           |

| 16, 17  | 16, 17  | 16, 17  | 16, 17  | QOUT-,<br>QOUT+   | Differential Quadrature-Phase Baseband Output. Disabled if FM_I mode is selected.                                                                                          |

| 18      | 18      | 18      | 18      | CLK               | Clock input of the 3-wire serial bus                                                                                                                                       |

| 19      | 19      | 19      | 19      | ĒN                | Enable Input. When low, input shift register is enabled.                                                                                                                   |

| 20      | 20      | 20      | 20      | DATA              | Data input of the 3-wire serial bus.                                                                                                                                       |

| 21      | 21      | 21      | 21      | V <sub>CC</sub>   | 2.7V to 5.5V Supply for Analog Circuits                                                                                                                                    |

| 22      | 22      | 22      | 22      | VGC               | VGA Gain Control Input. Control voltage range is 0.5V to 2.3V.                                                                                                             |

| 23, 24  | 23, 24  | 23, 24  | 23, 24  | CDMA-,<br>CDMA+   | Differential CDMA Input. Active in CDMA mode.                                                                                                                              |

| 25      | _       | 25      |         | FM+               | Differential Positive Input. Active in FM mode.                                                                                                                            |

|         | 25      | _       | 25      | N.C.              | No Connection.                                                                                                                                                             |

| 26      |         | 26      |         | FM-               | Differential Negative Input for FM signal. Bypass to GND for single-ended operation.                                                                                       |

|         | 26      | _       | 26      | STBY              | Standby Input—active low. Low powers down VGA and demod-<br>ulator while keeping VCO, PLL, and serial bus on.                                                              |

| 27, 28  | 27, 28  | 27, 28  | 27, 28  | BYP               | Bypass Node. Must be capacitively decoupled (bypassed) to analog $V_{\mbox{CC}}.$                                                                                          |

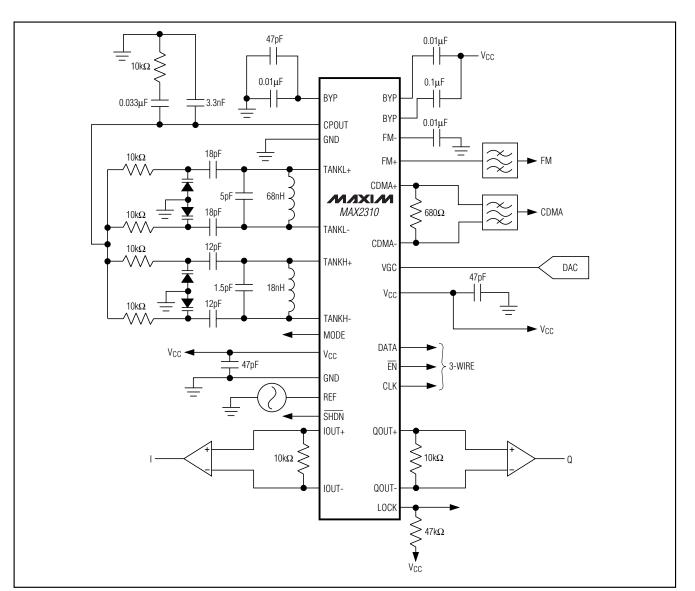

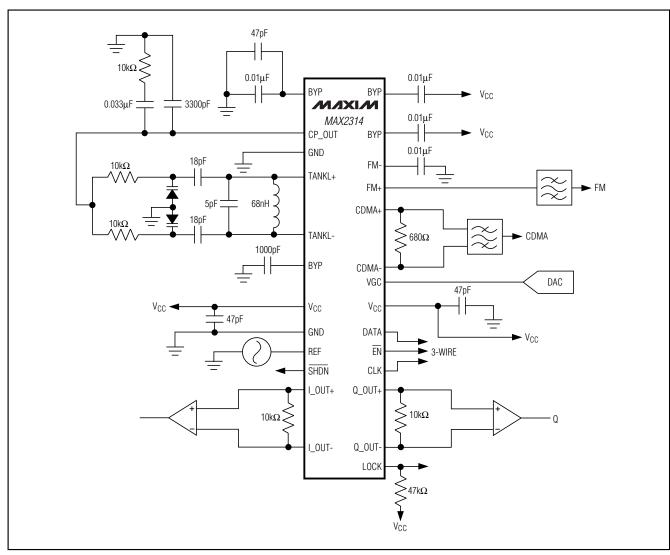

Figure 1. MAX2310 Typical Operating Circuit

### **Detailed Description**

#### MAX2310

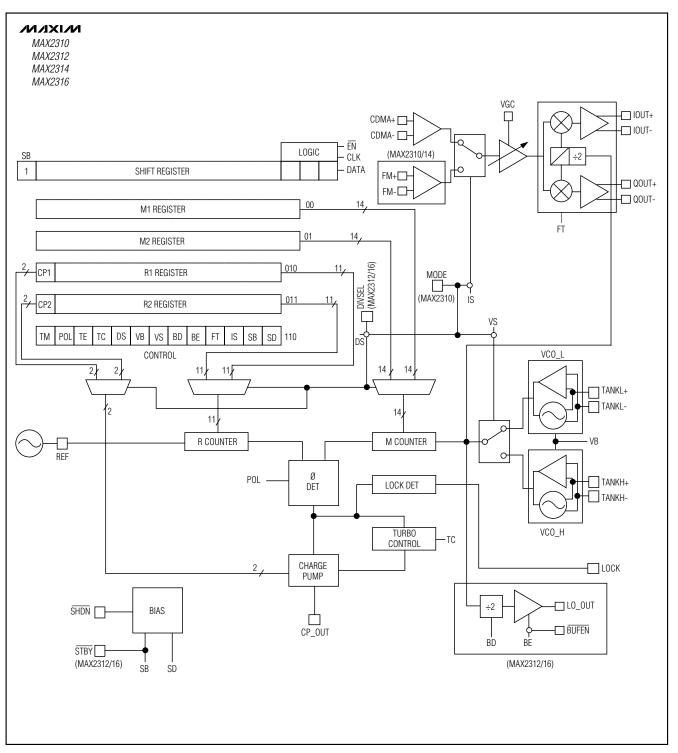

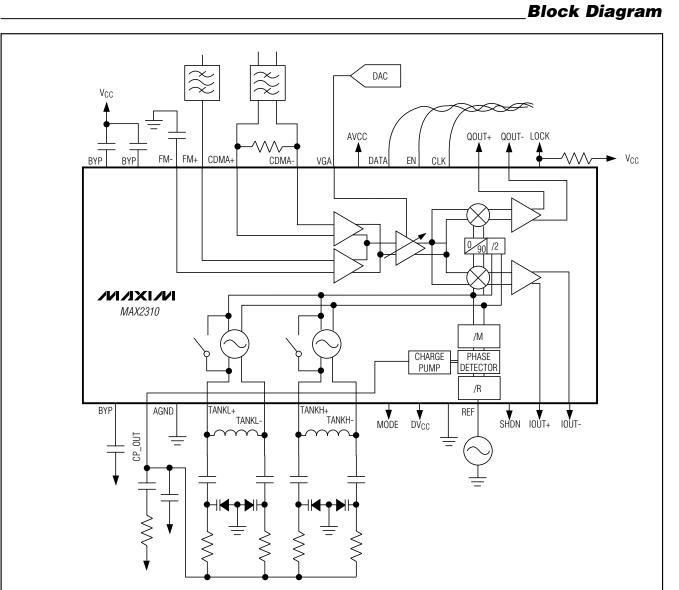

The MAX2310 is intended for dual-band (PCS and cellular) and dual-mode code division multiple access (CDMA) and FM applications (Figure 1). The device includes an IF variable-gain amplifier, quadrature demodulator, dual VCOs, and dual-frequency synthesizers (Figure 7). Dual VCOs are provided for applications using different IF frequencies for each mode or band of operation. The analog FM output signal can be configured for conversion to the I channel, or it may be converted in quadrature to both the I and Q channels. The MAX2310's operation modes are described in Table 1. These modes are set by programming the control register and setting logic levels on control pins. If MODE is left floating, the internal register controls the operation. If driven high or low, mode will override certain register bits, as shown in Table 1.

#### Table 1. MAX2310 Control Register States

|                     |                                                            | PI     | NS   | M<br>S<br>B | 1      |         |             | CON    | TROL    | REC     | GISTI   | ER    |         |        |             | L<br>S<br>B |

|---------------------|------------------------------------------------------------|--------|------|-------------|--------|---------|-------------|--------|---------|---------|---------|-------|---------|--------|-------------|-------------|

| OPERATIONAL<br>MODE | ACTION<br>RESULT                                           | SHDN   | MODE | TEST_MODE   | CP POL | TEST_EN | TURBOCHARGE | DIVSEL | VCO_BYP | VCO_SEL | BUF_DIV | BUFEN | FM_TYPE | IN_SEL | <u>STBY</u> | SHDN        |

| SHUTDOWN            | Shutdown pin completely powers down the chip               | L      | Х    | x           | Х      | Х       | x           | x      | X       | Х       | Х       | x     | Х       | Х      | Х           | x           |

| SHUTDOWN            | 0 in shutdown register bit leaves serial port active       | Н      | x    | x           | x      | x       | x           | X      | Х       | x       | x       | х     | х       | х      | x           | 0           |

| STANDBY             | 0 in standby register bit turns off VGA and modulator only | Н      | х    | х           | х      | 0       |             |        |         |         | х       | х     |         |        | 0           | 1           |

| CDMA                | Mode pin overrides VCO_SEL,<br>DIVSEL, and IN_SEL to high  | Н      | н    |             |        | 0       |             | X      |         | х       | х       | х     | Х       | х      | 1           | 1           |

| CDMA                | Floating mode pin returns control to register              | Н      | F    |             |        | 0       |             | 1      |         | 1       | х       | х     | Х       | 1      | 1           | 1           |

| FM_IQ               | Mode pin overrides VCO_SEL,<br>DIVSEL, and IN_SEL to low   | Н      | L    |             |        | 0       |             | X      |         | х       | х       | х     | 0       | х      | 1           | 1           |

| FM_IQ               | Floating mode pin returns control to register              | Н      | F    |             |        | 0       |             |        |         |         | х       | х     | 0       | 0      | 1           | 1           |

| FM_I                | Mode pin overrides VCO_SEL,<br>DIVSEL, and IN_SEL to low   | Н      | L    |             |        | 0       |             | X      |         | х       | х       | х     | 1       | х      | 1           | 1           |

| FM_I                | Floating pins return control to register                   | H<br>L | F    |             |        | 0       |             |        |         |         | Х       | х     | 1       | 0      | 1           | 1           |

**Note:** H = high, L = low, F = floating pin, X = don't care, Blank = independent parameter, 1 = logic high, 0 = logic low.

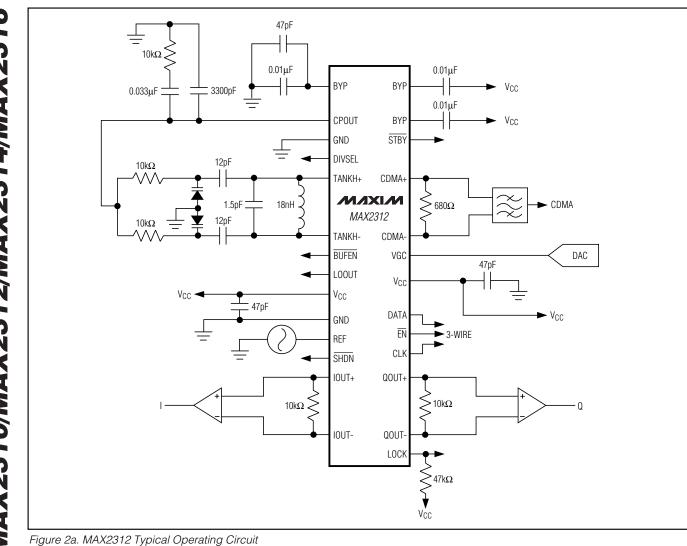

#### MAX2312/MAX2316

The MAX2312/MAX2316 quadrature demodulators are simplified versions of the MAX2310 that can be used in single-mode CDMA or dual mode using an external FM discriminator (Figures 2a and 2b). The MAX2312 VCO is optimized for the 67MHz to 300MHz IF frequency range, while the MAX2316 VCO is optimized for the 40MHz to 150MHz IF frequency range.

Both devices include a buffered output for the VCO. The buffered VCO output can be used to support systems implementing traditional limiting IF stages for FM demodulation in dual-mode phones as well as for the transmit LO in TDD systems. This buffered output can be configured for the VCO frequency (twice the IF frequency) or one-half the VCO frequency (IF frequency). The BUFEN pin enables this feature. A standby mode, in which only the VCO and synthesizer are operational, can be selected through the serial interface or the STBY pin. The MAX2312/MAX2316s' operational modes are described in Table 2. These modes are set by programming the control register and/or setting logic levels on control pins. If the control pins (STBY, BUFEN, DIVSEL) are left floating, the internal register controls the operational mode. If driven high or low, the control pins will override certain register bits, as shown in Table 2.

Figure 2b. MAX2316 Typical Operating Circuit

### Table 2. MAX2312/MAX2316 Control Register States

|                     |                                                                      |         | PI      | NS    |             | M<br>S<br>B |        |         | (           | CON     | FROL    | REC     | GISTI   | ER      |         |        |             | L<br>S<br>B |

|---------------------|----------------------------------------------------------------------|---------|---------|-------|-------------|-------------|--------|---------|-------------|---------|---------|---------|---------|---------|---------|--------|-------------|-------------|

| OPERATIONAL<br>MODE | ACTION<br>RESULT                                                     | SHDN    | DIVSEL  | BUFEN | <u>STBY</u> | TEST_MODE   | CP_POL | TES_TEN | TURBOCHARGE | DIVSEL  | VCO_BYP | VCO_SEL | BUF_DIV | BUFEN   | FM_TYPE | IN_SEL | <u>STBY</u> | SHDN        |

| SHUTDOWN            | Shutdown pin com-<br>pletely powers down<br>the chip                 | L       | x       | x     | x           | x           | x      | x       | x           | x       | x       | x       | x       | x       | x       | x      | х           | x           |

| SHUTDOWN            | 0 in shutdown register<br>bit leaves serial bus<br>active            | н       | x       | x     | x           | x           | x      | х       | x           | x       | x       | x       | x       | x       | x       | x      | х           | 0           |

| STANDBY             | 0 in standby pin turns<br>off VGA and modulator<br>only              | н       |         |       | L           |             |        | 0       |             |         |         | x       |         |         |         |        | х           | 1           |

| STANDBY             | 0 in standby register bit<br>turns off VGA and mod-<br>ulator only   | н       | H/<br>L | н     |             |             |        | 0       |             |         |         | x       |         |         |         |        | 0           | 1           |

| DIVIDER<br>SELECT   | DIV_SEL pin overrides<br>DIV_SEL register bit                        | Н       | H/<br>L |       | н           |             |        | 0       |             | х       |         | х       |         |         |         |        |             | 1           |

| DIVIDER<br>SELECT   | If DIV_SEL pin is float-<br>ed, then register bit<br>selects divider | н       | F       |       | н           |             |        | 0       |             | 1/<br>0 |         | x       |         |         |         |        |             | 1           |

| LO BUFFER<br>ENABLE | BUFEN pin controls the<br>LO buffer and overrides<br>the bit         | H/<br>L |         | н     |             |             |        | 0       |             |         |         | x       |         | х       |         |        |             | 1           |

| LO BUFFER<br>ENABLE | If pin is floated, then<br>BUFEN register bit<br>controls buffer     | н       |         | F     |             |             |        | 0       |             |         |         | x       |         | 1/<br>0 |         |        |             | 1           |

**Note:** H = high, L = low, 1 = logic high, 0 = logic low, X = don't care, blank = independent parameter.

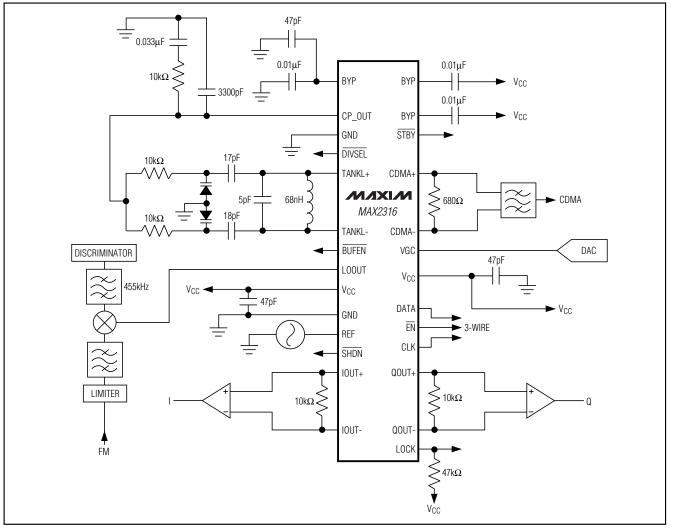

Figure 3. MAX2314 Typical Operating Circuit

#### MAX2314

The MAX2314 supports CDMA cellular-band, dualmode operation. As with the MAX2310, the FM mode can be configured for conversion to the I port or quadrature conversion to both the I and Q ports (Figure 3). The MAX2314's operational modes are described in Table 3. These modes are set by programming the control register and setting logic levels on control pins.

#### **Applications Information**

#### Variable-Gain Amplifier and Demodulator

The MAX2310 family provides a Variable-Gain Amplifier (VGA) with exceptional gain range. The MAX2310/ MAX2314 support multimode applications with dual differential inputs, selectable with the IN\_SEL (IS) control bit. On the MAX2310 this function can be controlled with the MODE pin, which overrides the IS control bit. The VGA's gain is controlled over a 110dB range with

Table 3. MAX2314 Control Register States

|                     |                                                           | P<br>I<br>N | M<br>S<br>B |        |         | (           | CON    | FROL    | REC     | GISTI   | ER    |         |        | 1    | L<br>S<br>B |

|---------------------|-----------------------------------------------------------|-------------|-------------|--------|---------|-------------|--------|---------|---------|---------|-------|---------|--------|------|-------------|

| OPERATIONAL<br>MODE | ACTION<br>RESULT                                          | SHDN        | TEST_MODE   | CP_POL | TEST_EN | TURBOCHARGE | DIVSEL | VCO_BYP | VCO_SEL | BUF_DIV | BUFEN | FM_TYPE | IN_SEL | STBY | SHDN        |

| SHUTDOWN            | Shutdown pin completely shuts down chip                   | L           | Х           | Х      | x       | x           | х      | Х       | x       | х       | Х     | х       | Х      | x    | х           |

| SHUTDOWN            | 0 in shutdown register bit leaves seri-<br>al port active | н           | х           | х      | х       | х           | х      | х       | х       | х       | Х     | Х       | х      | х    | L           |

| STANDBY             | 0 in standby pin turns off VGA and modulator only         | Н           |             |        | 0       |             |        |         | 0       | х       | х     |         |        | 0    | 1           |

| CDMA                | CDMA operation                                            | н           |             |        | 0       |             |        |         | 0       | Х       | Х     | Х       | 1      | 1    | 1           |

| FM_IQ               | FM IQ quadrature operation                                | н           |             |        | 0       |             |        |         | 0       | Х       | Х     | 0       | 0      | 1    | 1           |

| FM_I                | FM I operation                                            | Н           |             |        | 0       |             |        |         | 0       | Х       | Х     | 1       | 0      | 1    | 1           |

Note: H = high, L = low, 1 = logic high, 0 = logic low, X = don't care, blank = independent parameter

the VGC pin. The output of the VGA drives the RF ports of a quadrature demodulator. The MAX2310/MAX2314 provide two types of FM demodulation, controlled by the FM\_TYPE (FT) control bit. When FM\_TYPE is "1," the signal is passed through both the I and Q signal paths for subsequent lowpass filtering and A/D conversion at baseband. If FM\_TYPE is "0," the FM signal is passed through the I mixer only.

#### Voltage-Controlled Oscillator, Buffers, and Quadrature Generation

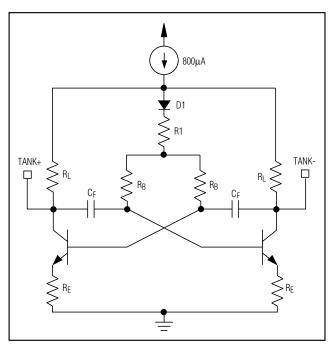

The LO signal for downconversion is provided by a voltage-controlled oscillator (VCO) consisting of an onchip differential oscillator, and an off-chip high-Q resonant network. Figure 4 shows a simplified schematic of the VCO oscillator. Multiband operation is supported by the MAX2310 with dual VCOs. VCO\_H and VCO\_L are selectable with the MODE pin or the VCO\_SEL (VS) control bit. They oscillate at twice the desired LO frequency. For applications requiring an external LO, the VCOs can be bypassed with the VCO\_BYP (VB) control bit.

The MAX2312/MAX2316 buffer the output of the VCO and provide this signal at the LOOUT pin. This signal is enabled by the BUFEN (BE) control bit or by the BUFEN control pin. The frequency of this signal is selected by the BUF\_DIV (BD) control bit, and can be either the VCO frequency or half the VCO frequency.

Quadrature downconversion is realized by providing inphase (I) and quadrature-phase (Q) components of the LO signal to the LO ports of the demodulator described above. The quadrature LO signals are generated by dividing the VCO output frequency using two latches. The appropriate latch outputs provide I and Q signals at the desired LO frequency.

#### Synthesizer

The VCO's output frequency is controlled by an internal phase-locked-loop (PLL) dual-modulus synthesizer. The loop filter is off-chip to simplify loop design for emerging applications. The tunable resonant network is also off-chip for maximum Q and for system design flexibility. The VCO output frequency is divided down to the desired comparison frequency with the M counter. The M counter consists of a 4-bit A swallow counter and a 10-bit P counter. A reference signal is provided from an external source and is divided down to the comparison frequency with the R counter. The two divided signals are compared with a three-state digital phase-frequency detector. The phase-detector output drives a charge pump as well as lock-detect logic and turbocharge control logic. The charge pump output (CP\_OUT) pin is processed by the loop filter and drives the tunable resonant network, altering the VCO frequency and closing the loop.

Multimode applications are supported by two independent programmable registers each for the M counter (M1, M2), the R counter (R1, R2), and the charge-pump output current magnitude (CP1, CP2). The DIVSEL (DS) bit selects which set of registers is used. It can be overridden by the MAX2310's MODE pin or the MAX2312/ MAX2316's DIVSEL pin. Programming these registers is discussed in the *3-Wire Interface and Registers* section.

Figure 4. Voltage-Controlled Oscillators

When the part initially powers up or changes state, the synthesizer acquisition time can be reduced by using the Turbo feature, enabled by the TURBOCHARGE (TC) control bit. Turbo functionality provides a larger charge-pump current during acquisition mode. Once the VCO frequency is acquired, the charge-pump output current magnitude automatically returns to the pre-programmed state to maintain loop stability and minimize spurs in the VCO output signal.

The lock detect output indicates when the PLL is locked with a logic high.

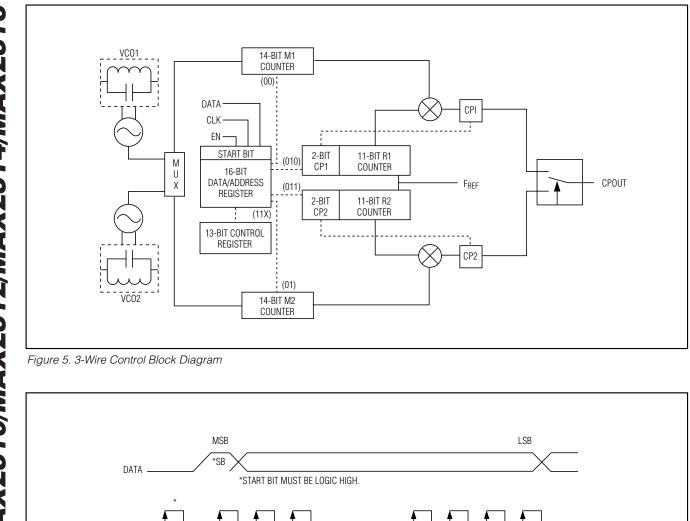

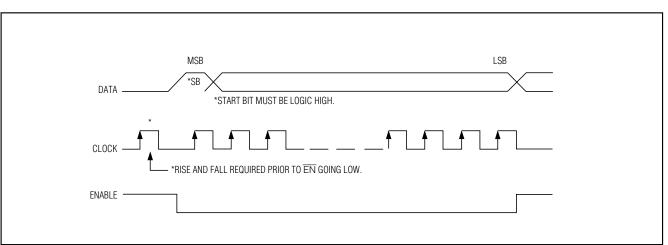

#### **3-Wire Interface and Registers**

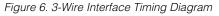

The MAX2310 family incorporates a 3-wire interface for synthesizer programming and device configuration (Figure 5). The 3-wire interface consists of a clock, data, and ENABLE. It controls the VCO dividers (M1 and M2), reference frequency dividers (R1 and R2), and a 13-bit control register. The control register is used to set up the operational modes (Table 4). The input shift is 17 data bits long and requires a total of 18 clock bits (Figure 6). A single clock pulse is required before enable drops low to initialize the data bus.

Whenever the M or R divide register value is programmed and downloaded, the control register must also be subsequently updated. This prevents turbolock from going active when not desired.

The <u>SHDN</u> control bit is notable because it differs from the <u>SHDN</u> pin. When the <u>SHDN</u> control bit is low, the registers and serial interface are left active, retaining the values stored in the latches, while the rest of the device is shut off. In contrast, the <u>SHDN</u> pin, when low, shuts down everything, including the registers and serial interface. See the functional diagram in Figure 7.

#### Registers

Figure 8 shows the programming logic. The 17-bit shift register is programmed by clocking in data at the rising edge of CLK. Before the shift register is able to accept data, it must be initialized by driving it with at least one full clock cycle at the CLK input with  $\overline{EN}$  high (see Figure 6). Pulling enable low will allow data to be clocked into the shift register; pulling enable high loads the register addressed by A0, A1, and A2, respectively (Figure 8). Table 5 lists the power-on default values of all registers. Table 6 lists the charge-pump current, depending on CP0 and CP1.

Figure 7. Functional Diagram

MAX2310/MAX2312/MAX2314/MAX2316

#### POWER-BIT BIT ID **BIT NAME** UP LOCATION FUNCTION STATE 0 = LSBTΜ TEST\_MODE 0 12 Must be 0 for normal operation. Logic "1" causes the charge-pump output CP\_OUT to source current when $f_{RFF}/R > f_{VCO}/M$ . This state is used when the VCO tune polarity is such that increasing voltage produces increasing fre-POL CP\_POL 1 11 quency. Logic "0" causes CP\_OUT to source current when fvco/M > f<sub>REF</sub>/R. This state is used when increasing tune voltage causes the VCO frequency to decrease. ΤE TEST\_ENABLE 10 Must be 0 for normal operation. 0 Logic "1" activates turbocharge mode, which provides rapid fre-TC TURBO\_CHARGE 1 9 quency acquisition in the PLL. DS DIV\_SEL 8 Logic "1" selects M1/R1 divide ratios. Logic "0" selects M2/R2. 1 VB 0 7 Logic "1" bypasses the VCO inputs for external VCO operation. VCO BYP VS VCO SEL 1 6 Logic "1" selects VCO\_H. Logic "0" selects VCO\_L. Logic "1" selects divide-by-2 on LOOUT port. Logic "0" bypasses ΒD **BUF\_DIV** 0 5 divider. ΒE BUFEN Logic "1" disables LOOUT. Logic "0" enables LOOUT. 1 4 Active in FM mode. Logic "0" selects quadrature demodulator for FT FM TYPE 0 3 FM mode. Logic "1" selects downconversion to I port. IS IN\_SEL 1 2 Logic "0" selects FM input port. Logic "1" selects CDMA input. Logic "0" enables standby mode, which shuts down the VGA and SB STBY 1 1 demodulator stages, leaving the VCO locked and the registers active. Logic "0" enables register-based shutdown. This mode shuts down SHDN SD 1 0 everything except the M and R latches and the serial bus.

#### Table 4. Control Register, Default State: 0B57h, Address: 110b

#### Table 5. Register Defaults

| REGISTER | DEFAULT              |

|----------|----------------------|

| M1       | 10519 <sub>DEC</sub> |

| M2       | 4269 <sub>DEC</sub>  |

| R1       | 492 <sub>DEC</sub>   |

| R2       | 492DEC               |

| CTRL     | OB57 <sub>HEX</sub>  |

| CP0      | 11 BIN               |

| CP1      | 11 BIN               |

### Table 6. Charge-Pump Control Bits

| CP1 | CP0 | CHARGE-PUMP CURRENT<br>AFTER ACQUISITION<br>(µA) |

|-----|-----|--------------------------------------------------|

| 0   | 0   | 150                                              |

| 0   | 1   | 210                                              |

| 1   | 0   | 300                                              |

| 1   | 1   | 425                                              |

|                      |       |                   |                   |                   |    |    |    |    |    |    |    |    |    |                  |                                     | ADDRESS<br>DECODED |                |        |

|----------------------|-------|-------------------|-------------------|-------------------|----|----|----|----|----|----|----|----|----|------------------|-------------------------------------|--------------------|----------------|--------|

|                      | START | BIT               |                   |                   |    |    |    |    |    |    |    |    |    |                  | ▲<br>A <sub>2</sub> /M <sub>0</sub> | <b>↑</b><br>A1     | A₀             |        |

| SHIFT REGISTER       | 1     |                   |                   |                   |    |    |    |    |    |    |    |    |    |                  | A <sub>2</sub> /M <sub>0</sub>      | A <sub>1</sub>     | A <sub>0</sub> | 🗕 DATA |

|                      |       | . ↓               | ¥                 | ¥                 | ¥  | ¥  | ♦  | ¥  | ¥  | ¥  | ¥  | ♦  | ¥  | ♦                | ♦                                   |                    | -              |        |

| M1 REGISTER          |       | M <sub>1</sub> 13 |                   |                   |    |    |    |    |    |    |    |    |    |                  | M <sub>1/0</sub>                    | 0                  | 0              |        |

| M2 REGISTER          |       | M <sub>2</sub> 13 |                   |                   |    |    |    |    |    |    |    |    |    |                  | M <sub>2/0</sub>                    | 0                  | 1              |        |

| CP1 AND R1 REGISTERS |       | CP <sub>1/1</sub> | CP <sub>1/0</sub> | R <sub>1/10</sub> |    |    |    |    |    |    |    |    |    | R <sub>1/0</sub> | 0                                   | 1                  | 0              |        |

| CP2 AND R2 REGISTERS |       | CP <sub>2/1</sub> | CP <sub>2/0</sub> | R <sub>2/10</sub> |    |    |    |    |    |    |    |    |    | R <sub>2/0</sub> | 0                                   | 1                  | 1              |        |

| CTRL REGISTER        |       | TM                | POL               | TE                | TC | DS | VB | VS | BD | BE | FT | IS | SB | SD               | 1                                   |                    | 0              |        |

Figure 8. Programming Logic

### Chip Information

TRANSISTOR COUNT: 6422

MAX2310/MAX2312/MAX2314/MAX2316

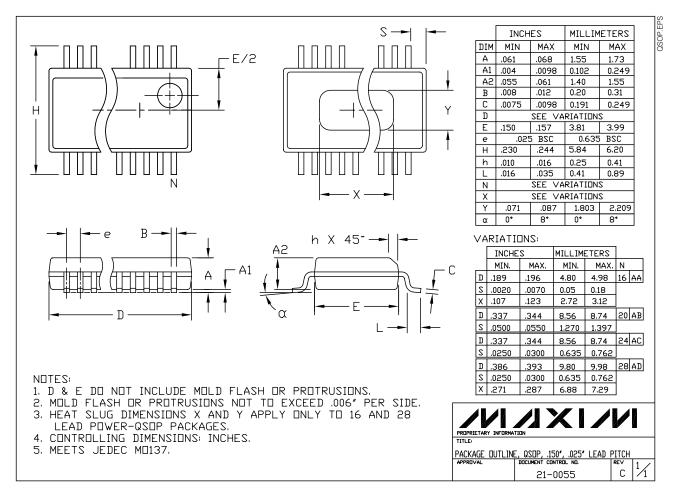

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600