##

## **Quad Differential LVECL/LVPECL Buffer/Receivers**

#### **General Description**

The MAX9400/MAX9402/MAX9403/MAX9405 are extremely fast, low-skew guad LVECL/ECL or LVPECL/ PECL buffer/receivers designed for high-speed data and clock driver applications. These devices feature an ultra-low propagation delay of 335ps and channel-tochannel skew of 16ps in asynchronous mode with 86mA supply current.

The four channels can be operated synchronously with an external clock, or in asynchronous mode determined by the state of the SEL input. An enable input provides the ability to force all the outputs to a differential low

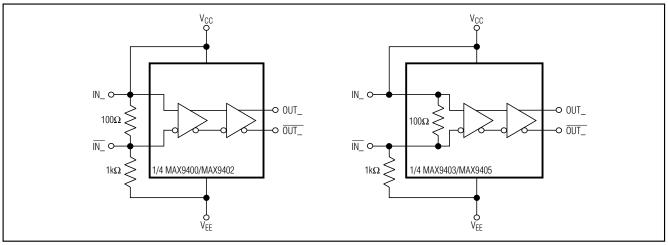

A variety of input and output terminations are offered for maximum design flexibility. The MAX9400 has open inputs and open emitter outputs. The MAX9402 has open inputs and  $50\Omega$  series outputs. The MAX9403 has  $100\Omega$  differential input impedance and open emitter outputs. The MAX9405 has  $100\Omega$  differential input impedance and  $50\Omega$  series outputs.

These devices operate with a supply voltage of (Vcc - $V_{EE}$ ) = 2.375V to 5.5V, and are specified for operation from -40°C to +85°C. These devices are offered in space-saving 32-pin 5mm × 5mm TQFP and 32-lead 5mm × 5mm QFN packages.

### **Applications**

Data and Clock Driver and Buffer Central Office Backplane Clock Distribution DSLAM Backplane Base Station ATE

WWW.DZSC.COM Functional Diagram appears at end of data sheet.

#### **Features**

- ◆ 400mV Differential Output at 3.0GHz Data Rate

- ♦ 335ps Propagation Delay in Asynchronous Mode

- ♦ 8ps Channel-to-Channel Skew in Synchronous Mode

- ♦ Integrated 50Ω Outputs (MAX9402/MAX9405)

- ♦ Integrated 100Ω Inputs (MAX9403/MAX9405)

- ♦ Synchronous/Asynchronous Operation

### **Ordering Information**

| PART        | TEMP<br>RANGE  | PIN-<br>PACKAGE | DATA<br>INPUT | ОИТРИТ     |

|-------------|----------------|-----------------|---------------|------------|

| MAX9400EHJ  | -40°C to +85°C | 32 TQFP         | Open          | Open       |

| MAX9400EGJ* | -40°C to +85°C | 32 QFN          | Open          | Open       |

| MAX9402EHJ  | -40°C to +85°C | 32 TQFP         | Open          | 50Ω        |

| MAX9402EGJ* | -40°C to +85°C | 32 QFN          | Open          | $50\Omega$ |

| MAX9403EHJ  | -40°C to +85°C | 32 TQFP         | 100Ω          | Open       |

| MAX9403EGJ* | -40°C to +85°C | 32 QFN          | 100Ω          | Open       |

| MAX9405EHJ  | -40°C to +85°C | 32 TQFP         | 100Ω          | 50Ω        |

| MAX9405EGJ* | -40°C to +85°C | 32 QFN          | 100Ω          | $50\Omega$ |

|             |                |                 |               |            |

<sup>\*</sup>Future product—contact factory for availability.

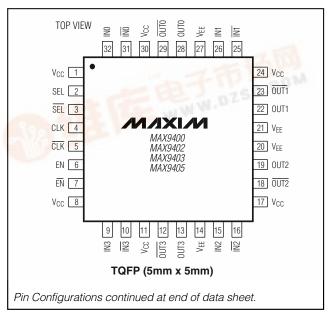

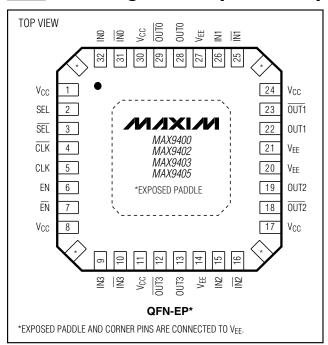

### Pin Configurations

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to V <sub>EE</sub> 0.3V to (          |          |

|-------------------------------------------------------|----------|

| Differential Input Voltage                            | ±3V      |

| Continuous Output Current                             | 50mA     |

| Surge Output Current                                  | 100mA    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |          |

| 32-Pin 5mm x 5mm TQFP                                 |          |

| (derate 9.5mW/°C above +70°C)                         | 761mW    |

| 32-Lead 5mm x 5mm QFN                                 |          |

| (derate 21.3mW/°C above +70°C)                        | 1.7W     |

| Junction-to-Ambient Thermal Resistance in Still Air   |          |

| 32-Pin 5mm x 5mm TQFP                                 | +105°C/W |

| 32-Lead 5mm x 5mm QFN                                 | +47°C/W  |

| Junction-to-Ambient Thermal Resistance with 500LFPM Airflow 32-Pin 5mm x 5mm TQFP | +73°C/W                               |

|-----------------------------------------------------------------------------------|---------------------------------------|

| 32-Pin 5mm x 5mm TQFP                                                             | · · · · · · · · · · · · · · · · · · · |

| 32-Lead 5mm x 5mm QFN  Operating Temperature Range                                | 40°C to +85°C                         |

| Junction Temperature                                                              |                                       |

| ESD Protection Human Body Model (Inputs and Outputs) Soldering Temperature (10s)  |                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} - V_{EE} = 2.375V \text{ to } 5.5V, \text{MAX9400/MAX9403} \text{ outputs terminated with } 50\Omega \pm 1\% \text{ to } V_{CC} - 2.0V. \text{ Typical values are at } V_{CC} - V_{EE} = 3.3V, V_{IHD} = V_{CC} - 0.9V, V_{ILD} = V_{CC} - 1.7V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Notes 1, 2, and 3)

| PARAMETER                       | SYMBOL            |                     | CONDITIONS                                                                                                                                                       | MIN                   | TYP                    | MAX                   | UNITS |  |

|---------------------------------|-------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|-------|--|

| INPUTS (IN_, IN_, CLK, CLK, EN  | , EN, SEL, S      | EL)                 |                                                                                                                                                                  |                       |                        |                       |       |  |

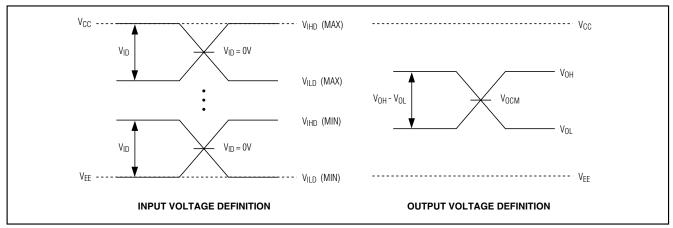

| Differential Input High Voltage | V <sub>IHD</sub>  | Figure 1            |                                                                                                                                                                  | V <sub>EE</sub> + 1.4 |                        | Vcc                   | V     |  |

| Differential Input Low Voltage  | V <sub>ILD</sub>  | Figure 1            |                                                                                                                                                                  | VEE                   |                        | V <sub>CC</sub> - 0.2 | V     |  |

| Differential Input Voltage      | V <sub>ID</sub>   | Figure 1            | V <sub>CC</sub> - V <sub>EE</sub> < +3.0V                                                                                                                        | 0.2                   |                        | V <sub>CC</sub> -     | V     |  |

|                                 |                   |                     | V <sub>CC</sub> - V <sub>EE</sub> ≥ +3.0V                                                                                                                        | 0.2                   |                        | 3.0                   |       |  |

| Input Current                   | 1 1               | MAX9400/<br>MAX9402 | EN, $\overline{\text{EN}}$ , SEL, $\overline{\text{SEL}}$ , IN_, $\overline{\text{IN}}$ , CLK, or $\overline{\text{CLK}}$ = V <sub>IHD</sub> or V <sub>ILD</sub> | -10                   |                        | 25                    |       |  |

| Input Current                   | lih, lil          | MAX9403/<br>MAX9405 | EN, EN, SEL, SEL, CLK, or CLK = V <sub>IHD</sub> or V <sub>ILD</sub>                                                                                             | -10                   |                        | 25                    | μΑ    |  |

| Differential Input Resistance   | RIN               | MAX9403/MA          | X9405                                                                                                                                                            | 86                    |                        | 114                   | Ω     |  |

| OUTPUTS (OUT_, OUT_)            |                   |                     |                                                                                                                                                                  |                       |                        |                       |       |  |

| Differential Output Voltage     | V <sub>OH</sub> - | Figure 1            |                                                                                                                                                                  | 600                   | 660                    |                       | mV    |  |

| Output Common-Mode Voltage      | Vocm              | Figure 1            | Figure 1                                                                                                                                                         |                       | V <sub>CC</sub> - 1.25 | V <sub>CC</sub> -     | V     |  |

| Internal Current Source         | ISINK             | MAX9402/MA          | MAX9402/MAX9405, Figure 2                                                                                                                                        |                       | 8.3                    | 10                    | mA    |  |

| Output Impedance                | Rout              | MAX9402/MA          | 40                                                                                                                                                               | 50                    | 60                     | Ω                     |       |  |

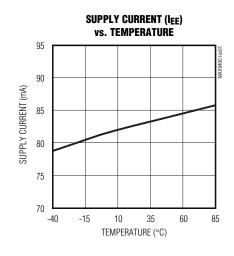

| POWER SUPPLY                    |                   |                     |                                                                                                                                                                  |                       |                        |                       |       |  |

| Supply Current                  | IEE               | MAX9402/MA          |                                                                                                                                                                  | 150                   | 180                    | mA                    |       |  |

| Supply Guiletti                 | 'EE               | MAX9400/MA          |                                                                                                                                                                  | 86                    | 118                    | IIIA                  |       |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} - V_{EE} = 2.375 V \ to \ 5.5 V, \ outputs \ terminated \ with \ 50 \Omega \ \pm 1\% \ to \ V_{CC} - 2.0 V, \ enabled, \ CLK = 3.2 GHz, \ f_{IN} = 1.6 GHz, \ input \ transition time = 125ps (20% \ to 80%), \ V_{IHD} = V_{EE} + 1.2 V \ to \ V_{CC}, \ V_{ILD} = V_{EE} \ to \ V_{CC} - 0.2 V, \ V_{IHD} - V_{ILD} = 0.2 V \ to \ smaller \ of \ IV_{CC} - V_{EE} \ or \ 3V, \ unless \ otherwise noted. Typical \ values \ are \ at \ V_{CC} - V_{EE} = 3.3 V, \ V_{IHD} = V_{CC} - 0.9 V, \ V_{ILD} = V_{CC} \ 1.7 V, \ T_{A} = +25 ^{\circ}C, \ unless \ otherwise noted.) (Notes 1, 4)$

| PARAMETER                                       | SYMBOL                   | COND                                                    | CONDITIONS                    |      |      |        | UNITS   |  |

|-------------------------------------------------|--------------------------|---------------------------------------------------------|-------------------------------|------|------|--------|---------|--|

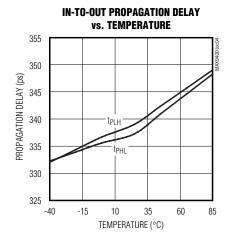

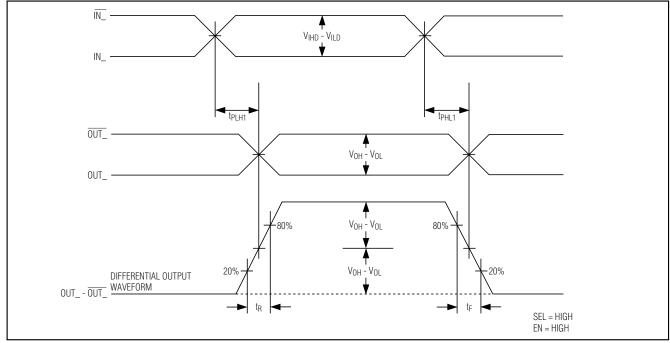

| IN-to-OUT Differential                          | tPLH1                    | MAX9400/MAX9403                                         | SEL - bigh Figure 2           | 237  | 335  | 437    | no      |  |

| Propagation Delay                               | tPHL1                    | MAX9402/MAX9405                                         | SEL = high, Figure 3          | 237  | 335  | 437    | ps      |  |

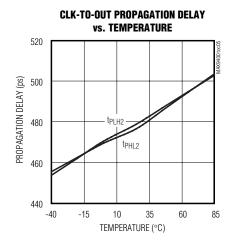

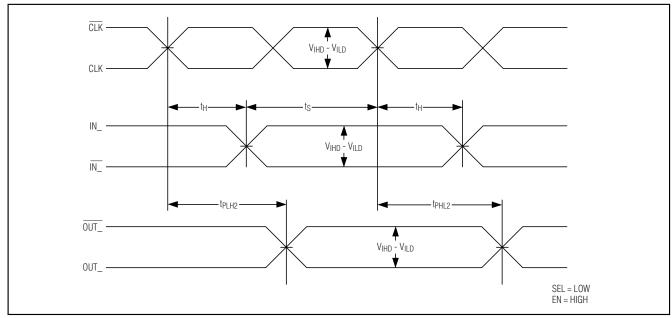

| CLK-to-OUT Differential                         | tPLH2                    | MAX9400/MAX9403                                         | MAX9400/MAX9403               |      |      |        | 20      |  |

| Propagation Delay                               | tPHL2                    | MAX9402/MAX9405                                         | SEL = low, Figure 4           | 397  | 475  | 597    | ps      |  |

| IN-to-OUT Channel-to-Channel<br>Skew (Note 5)   | tskD1                    | SEL = high                                              |                               | 16   | 80   | ps     |         |  |

| CLK-to-OUT Channel-to-<br>Channel Skew (Note 5) | tskD2                    | SEL = low                                               |                               | 8    | 55   | ps     |         |  |

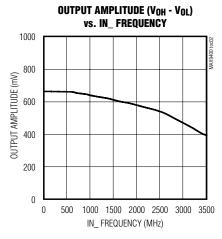

| Maximum Clock Frequency                         | fCLK(MAX)                | V <sub>OH</sub> - V <sub>OL</sub> ≥ 500mV, S            | 3.0                           |      |      | GHz    |         |  |

| Maximum Data Frequency                          | fIN(MAX)                 | V <sub>OH</sub> - V <sub>OL</sub> ≥ 400mV, S            | 2                             |      |      | GHZ    |         |  |

| Added Random Jitter (Note 6)                    | t <sub>RJ</sub>          | SEL = low, $f_{CLK} = 3.0$                              |                               | 0.64 | 1.3  |        |         |  |

| Added Handom Sitter (Note 6)                    | rHJ                      | SEL = high, f <sub>IN</sub> = 2GH                       | lz                            |      | 0.74 | 1.5 ps | ps(RMS) |  |

| Added Deterministic Jitter                      | to                       | SEL = low, $f_{CLK} = 3.0$<br>$2^{23} - 1$ PRBS pattern | GHz, IN_ = 3.0Gbps            |      | 17   | 30     | D0(D D) |  |

| (Note 6)                                        | tDJ                      | SEL = high, IN = 2.0G pattern                           | ibps 2 <sup>23</sup> - 1 PRBS |      | 40   | 55     | ps(P-P) |  |

| IN-to-CLK Setup Time                            | ts                       | Figure 4                                                |                               | 80   |      |        | ps      |  |

| CLK-to-IN Hold Time                             | tH                       | Figure 4                                                | Figure 4                      |      |      |        | ps      |  |

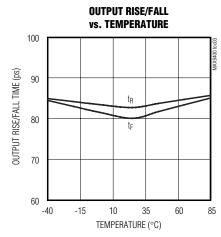

| Output Rise Time                                | t <sub>R</sub>           | Figure 3                                                |                               |      | 80   | 120    | ps      |  |

| Output Fall Time                                | t <sub>F</sub>           | Figure 3                                                |                               | 80   | 120  | ps     |         |  |

| Propagation Delay Temperature<br>Coefficient    | Δt <sub>PD</sub> /<br>ΔT |                                                         |                               |      | 0.2  | 1      | ps/°C   |  |

- Note 1: Measurements are made with the device in thermal equilibrium.

- Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative.

- Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full operating temperature range.

- Note 4: Guaranteed by design and characterization. Limits are set to ±6 sigma.

- Note 5: Measured between outputs of the same part at the signal crossing points for a same-edge transition.

- Note 6: Device jitter added to the input signal.

#### **Typical Operating Characteristics**

$(V_{CC} - V_{EE} = 3.3V, MAX9400, outputs terminated with 50\Omega \pm 1\% to V_{CC} - 2.0V, enabled, SEL = high, CLK = 2.0GHz, flN = 1.0GHz, input transition time = 125ps (20% to 80%), V<sub>IHD</sub> = V<sub>CC</sub> - 1.0V, V<sub>ILD</sub> = V<sub>CC</sub> - 1.5V, T<sub>A</sub> = +25°C, unless otherwise noted.)$

### Pin Description

| PIN                    | NAME             | FUNCTION                                                                                                                                                                                                                                                        |

|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 8,11,<br>17, 24, 30 | V <sub>C</sub> C | Positive Supply Voltage. Bypass $V_{CC}$ to $V_{EE}$ with 0.1 $\mu$ F and 0.01 $\mu$ F ceramic capacitors. Place the capacitors as close to the device as possible with the smaller value capacitor closest to the device.                                      |

| 2                      | SEL              | Noninverting Differential Select Input. Setting SEL = high and SEL = low (differential high) enables all four channels to operate asynchronously. Setting SEL = low and SEL = high (differential low) enables all four channels to operate in synchronous mode. |

| 3                      | SEL              | Inverting Differential Select Input                                                                                                                                                                                                                             |

| 4                      | CLK              | Noninverting Differential Clock Input                                                                                                                                                                                                                           |

| 5                      | CLK              | Inverting Differential Clock Input. A rising edge on CLK (and falling on CLK) transfers data from the inputs to the outputs when SEL = low.                                                                                                                     |

| 6                      | EN               | Noninverting Differential Output Enable Input. Setting EN = high and $\overline{\text{EN}}$ = low (differential high) enables the outputs. Setting EN = low and $\overline{\text{EN}}$ = high (differential low) drives outputs low.                            |

| 7                      | ĒN               | Inverting Differential Output Enable Input                                                                                                                                                                                                                      |

| 9                      | IN3              | Noninverting Differential Input 3                                                                                                                                                                                                                               |

| 10                     | ĪN3              | Inverting Differential Input 3                                                                                                                                                                                                                                  |

| 12                     | OUT3             | Inverting Differential Output 3                                                                                                                                                                                                                                 |

| 13                     | OUT3             | Noninverting Differential Output 3                                                                                                                                                                                                                              |

| 14, 20,<br>21, 27      | VEE              | Negative Supply Voltage                                                                                                                                                                                                                                         |

| 15                     | IN2              | Noninverting Differential Input 2                                                                                                                                                                                                                               |

| 16                     | ĪN2              | Inverting Differential Input 2                                                                                                                                                                                                                                  |

| 18                     | OUT2             | Inverting Differential Output 2                                                                                                                                                                                                                                 |

| 19                     | OUT2             | Noninverting Differential Output 2                                                                                                                                                                                                                              |

| 22                     | OUT1             | Noninverting Differential Output 1                                                                                                                                                                                                                              |

| 23                     | OUT1             | Inverting Differential Output 1                                                                                                                                                                                                                                 |

| 25                     | ĪN1              | Inverting Differential Input 1                                                                                                                                                                                                                                  |

| 26                     | IN1              | Noninverting Differential Input 1                                                                                                                                                                                                                               |

| 28                     | OUT0             | Noninverting Differential Output 0                                                                                                                                                                                                                              |

| 29                     | OUT0             | Inverting Differential Output 0                                                                                                                                                                                                                                 |

| 31                     | ĪNO              | Inverting Differential Input 0                                                                                                                                                                                                                                  |

| 32                     | IN0              | Noninverting Differential Input 0                                                                                                                                                                                                                               |

| _                      | EP               | Exposed Paddle (MAX940_EGJ only). Connected to VEE internally. See package dimensions.                                                                                                                                                                          |

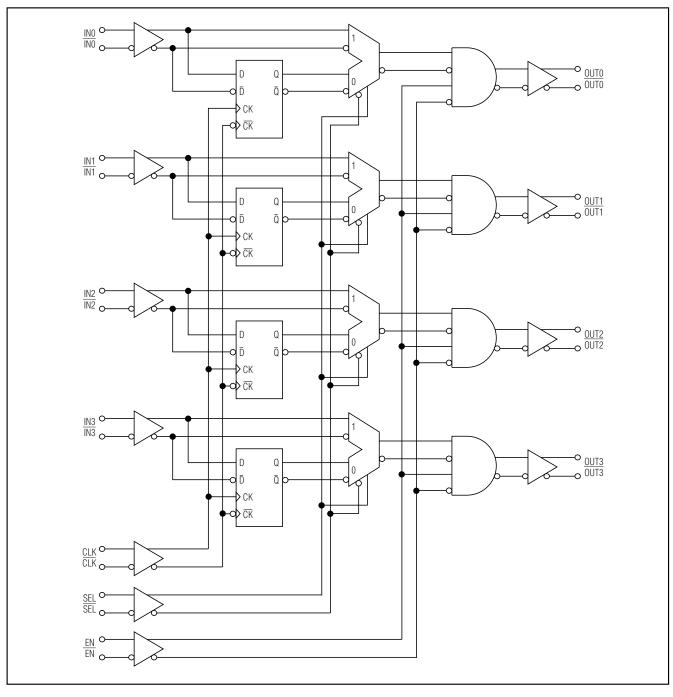

#### **Detailed Description**

The MAX9400/MAX9402/MAX9403/MAX9405 are extremely fast, low-skew quad LVECL/ECL or LVPECL/PECL buffer/receivers designed for high-speed data and clock driver applications. The devices feature an ultra-low propagation delay of 335ps and channel-to-channel skew of 16ps in asynchronous mode with an 86mA supply current.

The four channels can be operated synchronously with an external clock, or in asynchronous mode, determined by the state of the SEL input. An enable input provides the ability to force all the outputs to a differential low state.

A variety of input and output terminations are offered for maximum design flexibility. The MAX9400 has open inputs and open-emitter outputs. The MAX9402 has open inputs and  $50\Omega$  series outputs. The MAX9403 has  $100\Omega$  differential input impedance and open-emitter outputs. The MAX9405 has  $100\Omega$  differential input impedance and  $50\Omega$  series outputs.

#### **Supply Voltage**

The MAX9400/MAX9402/MAX9403/MAX9405 are designed for operation with a single supply. Using a single negative supply of VEE = -2.375V to -5.5V (VCC = ground) yields LVECL/ECL-compatible input and output levels. Using a single positive supply of VCC = 2.375V to 5.5V (VEE = ground) yields LVPECL/PECL input and output levels.

#### Data Inputs

The MAX9400/MAX9402 have open inputs and require external termination. The MAX9403/MAX9405 have integrated 100 $\Omega$  differential input termination resistors from IN\_ to  $\overline{\text{IN}}$ , reducing external component count.

#### **Outputs**

The MAX9402/MAX9405 have internal  $50\Omega$  series output termination resistors and 8mA internal pulldown current sources. Using integrated resistors reduces external component count.

The MAX9400/MAX9403 have open-emitter outputs. An external termination is required. See the *Output Termination* section.

#### **Enable**

Setting EN = high and  $\overline{\text{EN}}$  = low enables the device. Setting EN = low and  $\overline{\text{EN}}$  = high forces the outputs to a differential low, and all changes on CLK, SEL, and IN\_ are ignored.

#### **Asynchronous Operation**

Setting SEL = high and SEL = low enables the four channels to operate independently as buffer/receivers.

The CLK signal is ignored in this mode. In asynchronous mode, the CLK signal should be set to either a logic low or high state to minimize noise coupling.

#### **Synchronous Operation**

Setting SEL = low and SEL = high enables all four channels to operate in synchronous mode. In this mode, buffered inputs are clocked into flip-flops simultaneously on the rising edge of the differential clock input (CLK and CLK).

#### **Differential Signal Input Limit**

The maximum signal magnitude of the differential inputs is VCC - VEE or 3V, whichever is less.

#### **Applications Information**

#### **Input Bias**

Unused inputs should be biased or driven as shown in Figure 5. This avoids noise coupling that might cause toggling at the unused outputs.

#### **Output Termination**

Terminate open-emitter outputs (MAX9400/MAX9403) through  $50\Omega$  to  $V_{CC}$  - 2V or use an equivalent Thevenin termination. Terminate both outputs and use identical termination on each for the lowest output-to-output skew. When a single-ended signal is taken from a differential output, terminate both outputs. For example, if OUT\_ is used as a single-ended output, terminate both OUT\_ and  $\overline{OUT}$ \_.

Ensure that the output currents do not exceed the current limits as specified in the *Absolute Maximum Ratings* table. Under all operating conditions, the device's total thermal limits should be observed.

#### **Power-Supply Bypassing**

Adequate power-supply bypassing is necessary to maximize the performance and noise immunity. Bypass VCC to VEE with high-frequency surface-mount ceramic 0.1µF and 0.01µF capacitors as close to the device as possible with the 0.01µF capacitor closest to the device pins. Use multiple bypass vias for connection to minimize inductance.

#### **Circuit Board Traces**

Input and output trace characteristics affect the performance of the MAX9400/MAX9402/MAX9403/MAX9405. Connect each of the inputs and outputs to a  $50\Omega$  characteristic impedance trace. Avoid discontinuities in differential impedance and maximize common-mode noise immunity by maintaining the distance between differential traces and avoid sharp corners. Minimize the number of vias to prevent impedance discontinuities. Reduce reflections by maintaining the  $50\Omega$  characteristics.

acteristic impedance through connectors and across cables. Minimize skew by matching the electrical length of the traces.

**Chip Information**

TRANSISTOR COUNT: 713

PROCESS: Bipolar

Figure 1. Input and Output Voltage Definitions

Figure 2. Input and Output Configurations

Figure 3. IN-to-OUT Propagation Delay and Transition Timing Diagram

Figure 4. CLK-to-OUT Propagation Delay Timing Diagram

Figure 5. Input Bias Circuits for Unused Inputs

### Pin Configurations (continued)

### Functional Diagram

10 \_\_\_\_\_\_/II/XI/VI

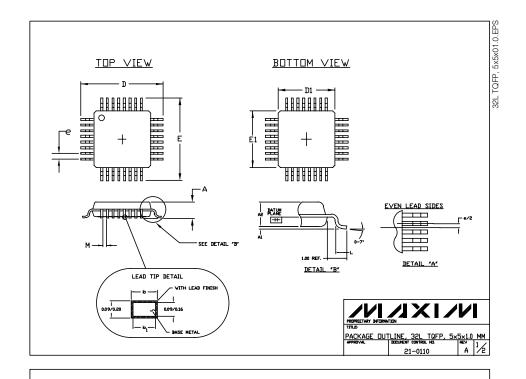

#### **Package Information**

- NOTES:

1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

2. DATUM PLANE HED IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

3. DIMENSIONS DI AND EL DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.254 MM ON DI AND EL DIMENSIONS.

4. THE TUP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15 MILLIMETERS.

5. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE BOTHOM AT MAXIMUM MATERIAL CONDITION.

7. THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION MO-136.

- MD-136.

B. LEADS SHALL BE COPLANAR WITHIN .004 INCH.

|                | JEDEC VARIATIONS          |            |  |  |  |  |  |  |  |  |  |

|----------------|---------------------------|------------|--|--|--|--|--|--|--|--|--|

|                | DIMENSIONS IN MILLIMETERS |            |  |  |  |  |  |  |  |  |  |

|                | A.                        | AA         |  |  |  |  |  |  |  |  |  |

|                | 5x5x1                     | 5×5×1.0 MM |  |  |  |  |  |  |  |  |  |

|                | MIN. MAX.                 |            |  |  |  |  |  |  |  |  |  |

| Α              | ~~                        | 1.20       |  |  |  |  |  |  |  |  |  |

| A <sub>1</sub> | 0.05                      | 0.15       |  |  |  |  |  |  |  |  |  |

| Az             | 0.95                      | 1.05       |  |  |  |  |  |  |  |  |  |

| D              | 7.00 BSC.                 |            |  |  |  |  |  |  |  |  |  |

| D <sub>1</sub> | 5.00                      | BSC.       |  |  |  |  |  |  |  |  |  |

| Ε              | 7.00 BSC.                 |            |  |  |  |  |  |  |  |  |  |

| E1             | 5.00                      | BSC.       |  |  |  |  |  |  |  |  |  |

| L              | 0.45                      | 0.75       |  |  |  |  |  |  |  |  |  |

| м              | 0.15                      | The same   |  |  |  |  |  |  |  |  |  |

| N              | 3                         | 2          |  |  |  |  |  |  |  |  |  |

| e              | 0.50                      | BSC.       |  |  |  |  |  |  |  |  |  |

| ь              | 0.17                      | 0.27       |  |  |  |  |  |  |  |  |  |

| b1             | 0.17                      | 0.23       |  |  |  |  |  |  |  |  |  |

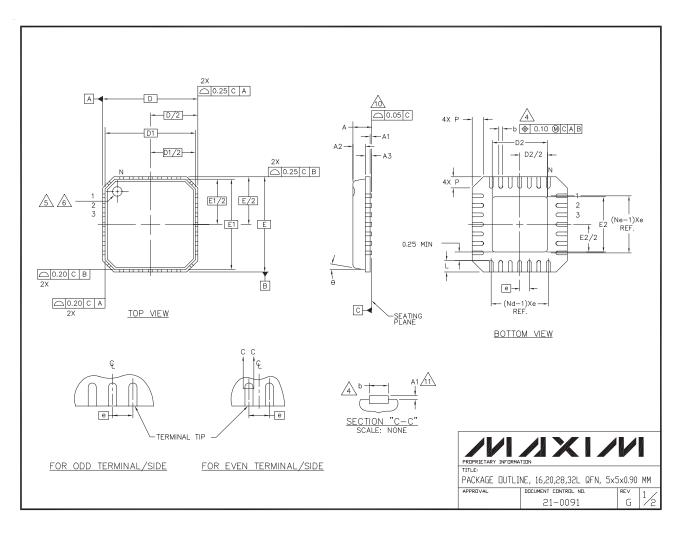

### Package Information (continued)

12 \_\_\_\_\_\_\_/VI/XI/VI

#### Package Information (continued)

#### NOTES:

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM)

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/ LASER MARKED.

- 6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.05mm.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDED PART OF EXPOSED PAD FROM MEASURING.

- 10. MEETS JEDEC MO220.

- 11. THIS PACKAGE OUTLINE APPLIES TO ANVIL SINGULATION (STEPPED SIDES) AND TO SAW SINGULATION (STRAIGHT SIDES) QFN STYLES.

| S                |      |           |                |     |

|------------------|------|-----------|----------------|-----|

| M<br>B           | DII  | IS        | N <sub>O</sub> |     |

| S<br>M<br>B<br>O | MIN. | NOM.      | MAX.           | NO. |

| A                | 0.80 | 0.90      | 1.00           |     |

| A1               | 0.00 | 0.01      | 0.05           |     |

| A2               | 0.00 | 0.65      | 1.00           |     |

| A3               |      | 0.20 REF. |                |     |

| D                |      | 5.00 BSC  |                |     |

| D1               |      | 4.75 BSC  |                |     |

| E                |      | 5.00 BSC  |                |     |

| E1               |      | 4.75 BSC  |                |     |

| θ                | 0.   | -         | 12°            |     |

| Р                | 0    |           | 0.60           |     |

| D2               | 1.25 | _         | 3.25           |     |

| E2               | 1.25 | ı         | 3.25           |     |

| S<br>Y<br>M | PITCH | VARIATI | ON B | N <sub>C</sub> | S<br>Y<br>M<br>R | PITCH | VARIAT   | ION B | N <sub>O</sub> | S<br>M<br>R | PITCH | VARIAT   | ION C | N <sub>O</sub> | S<br>Y<br>M<br>R | PITCH | VARIAT   | ION D | N <sub>O</sub> |

|-------------|-------|---------|------|----------------|------------------|-------|----------|-------|----------------|-------------|-------|----------|-------|----------------|------------------|-------|----------|-------|----------------|

| ٠<br>ا      | MIN.  | NOM.    | MAX. | Ϋ́E            | <u>_</u>         | MIN.  | NOM.     | MAX.  | Ϋ́E            | <u>ا</u> و  | MIN.  | NOM.     | MAX.  | Ĭ <sub>Ε</sub> | <u>ે</u>         | MIN.  | NOM.     | MAX.  | E              |

| e           | 0     | .80 BSC |      |                | e                |       | 0.65 BSC |       |                | e           |       | 0.50 BSC |       |                | e                |       | 0.50 BSC |       |                |

| N           |       | 16      |      | 3              | N                |       | 20       |       | 3              | N           |       | 28       |       | 3              | N                |       | 32       |       | 3              |

| Nd          |       | 4       |      | 3              | Nd               |       | 5        |       | 3              | Nd          |       | 7        |       | 3              | Nd               |       | 8        |       | 3              |

| Ne          |       | 4       |      | 3              | Ne               |       | 5        |       | 3              | Ne          |       | 7        |       | 3              | Ne               |       | 8        |       | 3              |

|             | 0.35  | 0.55    | 0.75 |                | L                | 0.35  | 0.55     | 0.75  |                | L           | 0.35  | 0.55     | 0.75  |                | L                | 0.30  | 0.40     | 0.50  |                |

| ь           | 0.28  | 0.33    | 0.40 | 4              | Ъ                | 0.23  | 0.28     | 0.35  | 4              | ь           | 0.18  | 0.23     | 0.30  | 4              | Ъ                | 0.18  | 0.23     | 0.30  | 4              |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.