19-0982; Rev 1; 7/96

## Fault-Protected Analog Multiplexer with Latch

#### **General Description**

Maxim's MAX368/369 are 8 channel single-ended (1 of 8) and 4 channel differential (2 of 8) fault-protected multiplexers with on-chip data latches. Using a series N-channel, P-channel, N-channel structure, these multiplexers provide significantly improved fault protection over previous devices. If power to the multiplexers is removed while input voltages are still applied, all channels turn off, allowing only a few nanoamperes of leakage current to flow in the inputs. This not only protects the multiplexer and the circuitry connected to the output, but also protects the sensors or signal sources which drive the multiplexer inputs.

When an overvoltage signal of up to ±35V is applied to an analog input of a Maxim fault-protected multiplexer, that input channel turns off. If the overvoltage is applied to an on channel, the multiplexer output is clamped to less than its power supply voltage, thereby protecting sensitive circuitry that may be connected to the multiplexer output.

All channel selection and control inputs are fully compatible with both TTL and CMOS logic levels. In addition, break-before-make switch operation is guaranteed and typical power dissipation is less than 7 milliwatts, which makes the MAX 368/369 ideally suited for portable equipment usage.

#### **Applications**

Data Acquisition Systems

Industrial Process Control Systems

Avionics Test Equipment

Signal Routing Between Systems

Computer Controlled Analog Data Logging

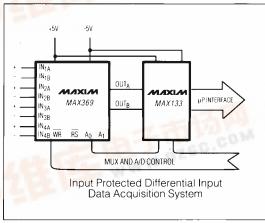

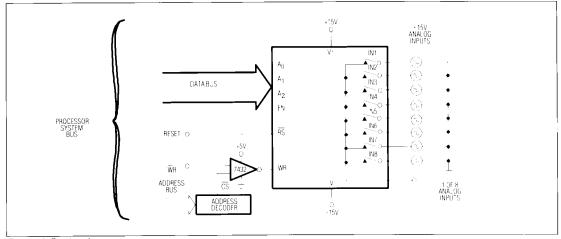

### Typical Operating Circuit

#### Features

- All Switches Off with Power Supplies Off

- ♦ Overvoltage Protection up to ±35V

- Only Nanoamperes of Input Current under All Fault Conditions

- **♦ Latch-Up Proof Construction**

- ♦ Operates from ±4.5 to ±18V Supplies

- ♦ All Digital Inputs are TTL and CMOS Compatible

- ♦ Internal Data Latches for Channel Selection

#### **Ordering Information**

| PART      | TEMP. RANGE     | PACKAGE             |

|-----------|-----------------|---------------------|

| MAX368C/D | 0°C to +70°C    | Dice                |

| MAX368CPN | 0°C to +70°C    | 18 Lead Plastic DIP |

| MAX368CJN | 0°C to +70°C    | 18 Lead CERDIP      |

| MAX368CWN | 0°C to +70°C    | 18 Lead Wide SO     |

| MAX368EPN | -40°C to +85°C  | 18 Lead Plastic DIP |

| MAX368EJN | -40°C to +85°C  | 18 Lead CERDIP      |

| MAX368EWN | -40°C to +85°C  | 18 Lead Wide SO     |

| MAX368MJN | -55°C to +125°C | 18 Lead CERDIP      |

| MAX369C/D | 0°C to +70°C    | Dice                |

| MAX369CPN | 0°C to +70°C    | 18 Lead Plastic DIP |

| MAX369CJN | 0°C to +70°C    | 18 Lead CERDIP      |

| MAX369CWN | 0°C to +70°C    | 18 Lead Wide SO     |

| MAX369EPN | -40°C to +85°C  | 18 Lead Plastic DIP |

| MAX369EJN | -40°C to +85°C  | 18 Lead CERDIP      |

| MAX369EWN | -40°C to +85°C  | 18 Lead Wide SO     |

| MAX369MJN | -55°C to +125°C | 18 Lead CERDIP      |

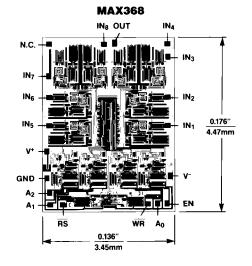

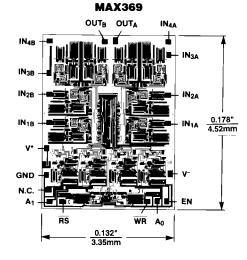

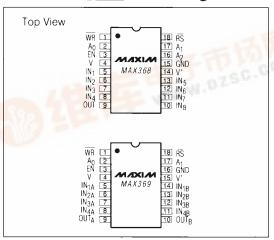

#### **Pin Configurations**

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

| ABSOLUTE MAXIMUM RATINGS                                                                                             |                                                                                 |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Voltage between Supply Pins                                                                                          | Continuous Current, S or D                                                      |

| V. +22V<br>V -22V                                                                                                    | Peak Current, S or D                                                            |

| B : 11 10 #                                                                                                          | (Pulsed at 1ms, 10% duty cycle max) 40mA<br>Power Dissipation (Note 1) (CERDIP) |

| Digital Input Overvoltage: $V_{EN}$ , $V_{A}$ $\begin{cases} V_{Supply}(+) & +4V \\ V_{Supply}(-) & -4V \end{cases}$ | Operating Temperature Range MAX368/369C 0 C to +70 C                            |

| Analog Input Overvoltage with Multiplexer Power On:                                                                  | MAX368/369E40 C to +85 C                                                        |

| $V_{\rm S} = \begin{cases} V_{\rm S,poly}(+) & +20V \\ V_{\rm S,poly}(-) & -20V \end{cases}$                         | MAX368/369M55 C to +125 C                                                       |

| VSapply( )                                                                                                           | Storage Temperature Range                                                       |

| Analog Input Overvoltage with Multiplexer Power Off:                                                                 | Note 1: Derate 12.8mW/ Clabove Ia - +70 C                                       |

| $V_{S} \begin{cases} V_{S,mov}(+) & +35V \\ V_{S,mov}(-) & -35V \end{cases}$                                         | Note 1. 170 de 12.01 Tr o dosto in                                              |

| ***   Verman( )                                                                                                      |                                                                                 |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V'  $\pm$  +15V, V - -15V; GND = 0, WR = 0, RS = 2 4V unless otherwise noted.)

| PARAMET                                 | ER     | SYMBOL                                                         | CONDI                                                 | ITIONS                                                   | TEMP *  | TYP          |              | UFFIX        |            | UFFIX        | UNITS |

|-----------------------------------------|--------|----------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|---------|--------------|--------------|--------------|------------|--------------|-------|

| ANALOG SWITC                            |        |                                                                |                                                       |                                                          | -       |              | MIN          | MAX          | MIN        | MAX          |       |

| Analog Signal Ra                        |        | VANALOG                                                        | (Note 2)                                              |                                                          | 1       |              | - 15         | 15           | 15         | 15           | V     |

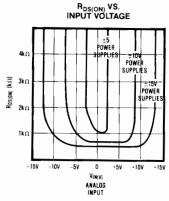

| Drain-Source<br>ON Resistance           |        | fos ioni                                                       | V <sub>D</sub> = ±10V. V<br>I <sub>S</sub> = 100μA. ' |                                                          | 1.3     | •            |              | 1500<br>1800 |            | 1800<br>2000 | Ω     |

| Greatest Change<br>Between Channo       |        | $\Delta$                                                       | -10V < V <sub>S</sub> <                               | 10V                                                      | 1 j     | 10           |              |              |            |              | . 00  |

| Source OFF<br>Leakage Current           |        | ls (Ott)                                                       | · ·                                                   | $V_{\rm S} = \pm 10V V_{\rm D} = \mp 10V$                | 1 2     | -0 005       | - 1<br>-50   | 1<br>50      | -5<br>-50  | -5<br>50     |       |

| D : 055                                 | MAX368 |                                                                | V <sub>I \(\sigma\)</sub> = 0.8V                      | $V_{\text{C}1} = \pm 10V$<br>$V_{\text{C}2} = \pm 10V$   | 1<br>2  | -0.015       | -2<br>-200   | 2<br>200     | -5<br>-200 | 5<br>200     |       |

| Drain OFF<br>Leakage Current            | MAX369 | lp :eff)                                                       |                                                       | $V_{13} = \pm \frac{10V}{10V}$<br>$V_{5} = \pm 10V$      | 1 2     | -0 008       | -1<br>-100   | 1<br>100     | 5<br>100   | 5<br>100     | nΑ    |

| MAX368 Drain ON                         |        | V <sub>S</sub> - V <sub>D</sub> = ±1<br>V <sub>SN</sub> = 2.4V | VOV                                                   | 1 2                                                      | -0.03   | -2<br>200    | ?<br>200     | 5<br>-200    | 5<br>200   |              |       |

| Leakage Current MAX369                  |        | li: (ON)                                                       | $V_{A,-} = 0.8V$<br>$V_{A+1} = 2.4V$                  |                                                          | 1<br>2  | -0.015       | - 1<br>- 100 | 1<br>100     | -5<br>-100 | 5<br>100     |       |

| LOGIC INPUT                             | 1      | L                                                              |                                                       |                                                          |         | •            |              |              |            |              |       |

| Logic Input Curre                       | ent    |                                                                | V <sub>A</sub> = 2.4V                                 |                                                          | 1, 2, 3 | -0.002       | -1           | 1            | - 1        | 1            |       |

| (Input Voltage Hi                       |        | I <sub>AH</sub>                                                | V <sub>A</sub> = 14V                                  |                                                          | 1. 2. 3 | 0 006        | -1           | 1            | - 1        | 1            | μΑ    |

| Logic Input Current (Input Voltage Low) |        | · I <sub>AL</sub>                                              | $V_{iN} = 0 \text{ or } 2.$<br>RS = 0V. WF            |                                                          | 1, 2, 3 | -0.002       | -1           | 1            | ,<br>1     | 1            |       |

| FAULT                                   |        |                                                                |                                                       |                                                          |         |              |              |              |            |              |       |

|                                         |        | V <sub>D</sub> = 0V (No<br>Analog Over                         | te 3)<br>rvoltage = ±33\                              | 1 2                                                      |         | -10<br>-2000 | 10<br>2000   | 20<br>-2000  | 20<br>2000 | . ^A         |       |

| Input Leakage C<br>(with Overvoltage    |        | Istoria                                                        | V <sub>IN</sub> = ±25V.<br>(Note 3)                   | V;) = +10V                                               | 1       |              | -5           | 5            | - 1()      | 10           | μΑ    |

| Input Leakage C<br>(with Power Supp     |        | l <sub>D (OLE)</sub>                                           | $V_{IN} = \pm 25V$ ,<br>$A_{G} = A_{1} - A_{3}$       | $V_1 \sim V_2 = 0V$<br>$\Rightarrow = 0V \text{ or } 5V$ | 1       |              | -2           | 2            | .5         | 5            | μА    |

<sup>\*1 – 25</sup> C, 2 – 125 C, 85 C, 70 C, 3 = -55 C, -40 C, 0 C

#### **ELECTRICAL CHARACTERISTICS (continued)**

(V' -+15V, V --15V; GND -0, WR =0,  $\overline{RS}=2.4V$  unless otherwise noted.)

| PARAME                             | TER     | SYMBOL                | CONDITIONS                                                                                                                         | TEMP *  | ТҮР | M SUFFIX     | E,C SUFFIX   | UNITS  |

|------------------------------------|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------------|--------------|--------|

| DYNAMIC                            |         |                       |                                                                                                                                    |         |     |              |              |        |

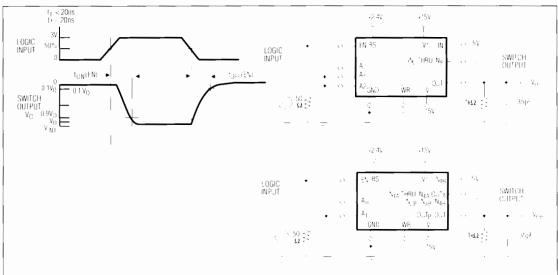

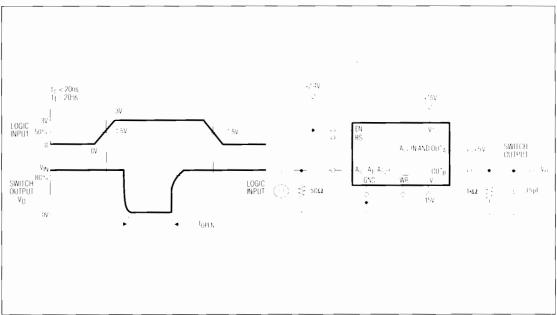

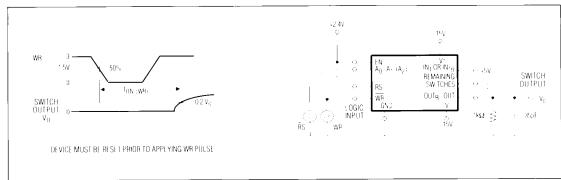

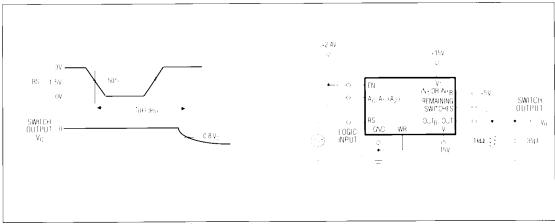

| Switching Time<br>Multiplexer      | of      | t <sub>IRANS</sub>    | See Figure 2                                                                                                                       | 1       | 0.6 | 1            | 1            |        |

| Break-Before-N<br>Interval         | Make    | toers                 | See Figure 4                                                                                                                       | 1       | 0.2 | 1            |              |        |

| Enable and Wri<br>Turn ON Time     | te      | Чомны мвг             | Sec Figures 3 and 5                                                                                                                | 1 1     | 1   | 15_          | 1.5          | μs     |

| Enable and Res<br>Turn OFF Time    |         | torrien as:           | See Figures 3 and 6                                                                                                                | 1       | 0.4 | 1            | 1            |        |

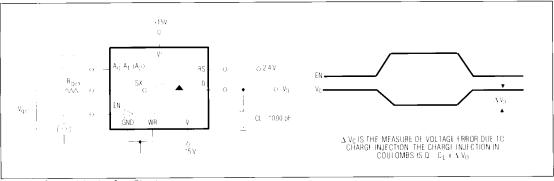

| Charge Injectio                    | n       | . a                   | See Figure 7 and<br>Tables 1A and 1B                                                                                               | 1       | 55  |              |              | рС     |

| OFF Isolation                      |         | OIRR                  | V <sub>1</sub> ·r. = 0. R <sub>1</sub> = 1k <b>Ω</b><br>C <sub>1</sub> = 15pF. V <sub>11</sub> =7V <sub>HM</sub> ·s,<br>f = 100kHz | 1       | 68  | 1            |              | dΒ     |

| Logic Input Cap<br>with Switch OFF |         | C <sup>41</sup>       | f – 1MHz                                                                                                                           | 1       | 5   |              |              | pF     |

| Input Capacitar<br>with Switch OFI |         | Caron:                | V <sub>Ir.</sub> - 0                                                                                                               | 1       | 5   |              |              |        |

| Output<br>Capacitance              | MAX368  |                       | f = 140kHz                                                                                                                         | 1 1     | 25  |              |              | Fla    |

| with Switch<br>OFF                 | MAX369  | . C <sub>D(1)+1</sub> | V <sub>OD</sub> 0                                                                                                                  | 1 _     | 12  |              |              |        |

| WR Pulse Width                     | 1       | t <sub>ww</sub>       | See Figure 1                                                                                                                       | 1, 2, 3 |     | 300          | 300          |        |

| Ax. EN Data Va<br>to WR            | lid     | tow                   | Set-up Time<br>See Figure 1                                                                                                        | 1, 2, 3 |     | 180          | 180          | ns     |

| Az, EN Data Va<br>after WR         | lid     | t <sub>wo</sub>       | Hold Time<br>See Figure 1                                                                                                          | 1, 2, 3 | 0   | 10           | 30           | ns     |

| RS Pulse Width                     |         | t <sub>RS</sub>       | V <sub>I1</sub> = 5V<br>See Figure 1                                                                                               | 1, 2. 3 |     | 300          | 500          |        |

| SUPPLY                             |         |                       | •                                                                                                                                  |         |     |              |              |        |

| Positive Supply                    | Current | i.<br>I               | · V: <sub>1s</sub> - 2.4V, V <sub>A</sub> = 0V/5V                                                                                  | 1, 2, 3 |     | 1 25<br>1.5  | 1.5<br>2.0   | , mA   |

| Negative Suppl<br>Current          | y       | 1                     | 1                                                                                                                                  | 1. 2. 3 |     | -0.1<br>-0.2 | -0.1<br>-0.2 | · IIIA |

<sup>11 25</sup> C, 2 - 125 C. 85 C. 70 C, 3 = -55 C, -40 C, 0 C

Note 2: When the analog signal exceeds +13.5V or -12V, the blocking action of Maxim's gate structure goes into

Note 2: Which the ariang signal exceeds + 13.5 V or -12V, the blocking action of maxim signes structure goes into operation. Only leakage currents flow and the channel on resistance rises to infinity.

Note 3: The value shown is the steady state value. The transient leakage is typically 10μA. See detailed description.

Note 4: Electrical Characteristics, such as ON Resistance will change when power supplies other than ±15V are used.

Note 5: Digital input leakage is primarily due to the clamp diodes. Typical leakage is less than 1nA at +25 C.

#### **TRUTH TABLE — MAX368**

| A <sub>2</sub> | A 1    | A <sub>0</sub> | EN    | WR     | RS  | ON<br>SWITCH                              |

|----------------|--------|----------------|-------|--------|-----|-------------------------------------------|

| Latc           | hing   |                |       |        |     |                                           |

| ×              | ×      | ×              | ×     | †<br>† | 1   | Maintains<br>previous<br>switch condition |

| Rese           | et     |                |       |        |     |                                           |

| ×              | X      | X              | Х     | X      | ()  | NONE<br>( atches cleared)                 |

| Tran           | spareı | nt Oper        | ation |        |     |                                           |

| X I            | Х      | X              | . ()  | ()     | 1   | NONE                                      |

| 0              | ()     | 0              | 1     | ()     | 1   | 1                                         |

| О              | ()     | 1              | 1     | C      | 1   | 2                                         |

| ()             | 1      | 0              | 1     | ()     | 1   | 3                                         |

| ()             | 1      | 1              | 1     | ()     | 1   | 4                                         |

| 1              | ()     | ()             | 1     | ()     | 1   | 5                                         |

| 1              | ()     | 1              | . 1   | ()     | 1 1 | 6                                         |

| 1 1            | 1      | ()             | . 1   | ()     | 1   | 7                                         |

| 1              | 1      | 1              | 1     | ()     | 1   | 8                                         |

#### **TRUTH TABLE — MAX369**

| <b>A</b> 1 | $A_0$  | EN      | WR    | RS |   | ON<br>SWITCH                              |

|------------|--------|---------|-------|----|---|-------------------------------------------|

| Late       | hing   |         |       |    | ٠ |                                           |

| X          | ×      | ×       | •     | 1  |   | Maintains<br>previous<br>switch condition |

| Res        | et     |         |       |    |   |                                           |

| ×          | ×      | ×       | ×     | 0  |   | NONE<br>(latchesicleared)                 |

| Tran       | spare  | nt Oper | ation |    |   |                                           |

| Χ          | ,<br>X | 0       | 0     |    | 1 | NON                                       |

| 0          | C      | 1       | C     | 4  |   | •                                         |

| ()         | 1      | 1       | 0     | 4  | 1 | 2                                         |

| 1          | C      | 1       | C     | 1  |   | 3                                         |

| 1          | 1      | 1       | C     | 1  |   | -4                                        |

**NOTE:** Logic "1"  $V_{A+1} \ge 2.4V$ . Logic "0"  $V_{A_1} \le 0.8V$

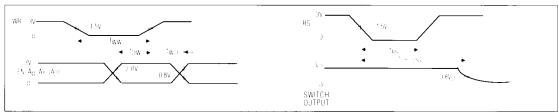

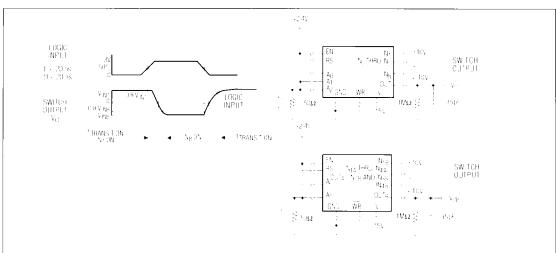

Figure 1 Typical Timing Diagrams for  $\overline{\text{MAX368/369}}$

Figure 2: Transition Time Test Circuits

Figure 3. Enable ton/toff Time Test Circuit

Figure 4 Open Time (B.B.M.) Interval Test Circuit

Figure 5 Write Turn-On Time toN(WR) Test Circuit

Figure 6 Reset Turn-Off Time toFF(RS) Test Circuit

Figure 7. Charge Injection Test Circuit

#### **Detailed Description**

#### **Fault Protection Circuitry**

Maxim's MAX368/369 are fully fault-protected for continuous input voltages up to  $\pm 35$ V, whether or not the  $\pm V_{SUP}$  and  $\pm V_{SUP}$  power supplies are present. These devices use a "series FET" protection scheme which not only protects the multiplexer output from overvoltage, but also limits the input current to sub-microamp levels.

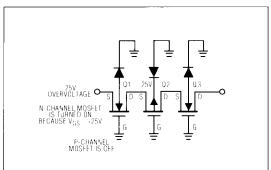

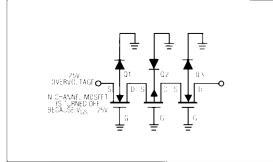

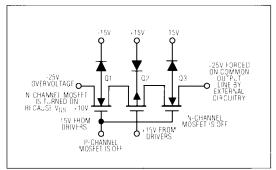

Figures 8 and 9 show how the series FET circuit protects against overvoltage conditions. When power is off, the gates of all the FETs are at ground. With a -25V input, N-channel FET Q1 is turned on by the +25V gate-to-source voltage. The P-channel device (Q2), however, has +25V VGs and is turned off, thereby preventing the input signal from reaching the output. If the input voltage is +25V, Q1 has a negative VGs, which turns it off. Similarly, only sub-microamp leakage currents can flow from the output back to the input, since any over voltage will turn off either Q1 or Q2.

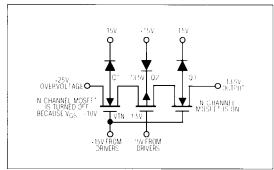

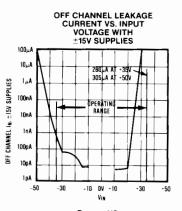

Figure 10 shows the condition of an OFF channel with +V<sub>SUP</sub> and V<sub>SUP</sub> present. As with Figures 8 and 9, either

an N-channel or a P-channel device will be off for any input voltage from -35V to +35V. The leakage current with negative overvoltages will immediately drop to a few nanoamps at 25°C. For positive overvoltages the fault current will initially be 10 or 20 $\mu A$ , decaying over a few seconds to the nanoamp level. The time constant of this decay is caused by the discharge of stored charge from internal nodes and does not compromise the fault protection scheme.

Figure 11 shows the condition of the ON channel with  $+V_{SUP}$  and  $-V_{SUP}$  present. With input voltages less than  $\pm 10V$ , all three FETs are on and the input signal appears at the output. If the input voltage exceeds  $+V_{SUP}$  minus the N-channel threshold voltage ( $V_{TN}$ ), then the N-channel FET will turn off. For voltages more negative than  $-V_{SUP}$  minus the P-channel threshold ( $V_{TP}$ ), the P-channel device will turn off. Since  $V_{TN}$  is typically 1.5V and  $V_{TP}$  is typically 3V, the multiplexer's output swing is limited to about -12V to +13.5V with  $\pm 15V$  supplies

Figure 8. -25V Overvoltage with Multiplexer Power OFF

Figure 9. +25V Overvoltage with Multiplexer Power OFF

Figure 10. -25V Overvoltage on an OFF Channel with Multiplexer Power Supply ON

Figure 11. +25V Overvoltage Input to the ON Channel

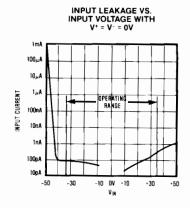

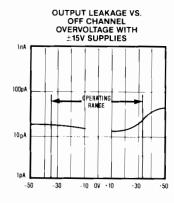

The Typical Operating Characteristics graphs show typical leakage vs. input voltage curves. Although the maximum rated overvoltage of these devices is ±35V, the MAX368/369 typically has excellent performance up to ±40V, providing additional margin for the unknown transients that exist in the real world. In summary, the MAX368/369 provides superior protection from all fault conditions, while using a standard, readily produced junction isolated CMOS process.

#### **Digital Control Circuitry**

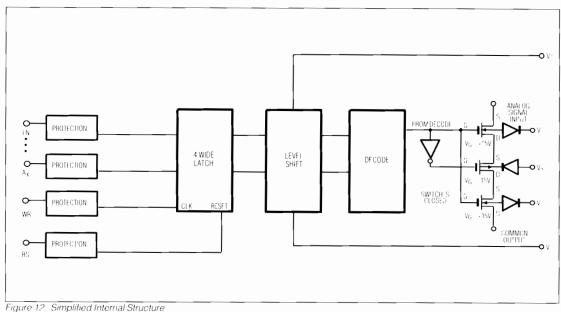

The internal structure of the MAX368/369 includes translators for the A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, EN, RS, and WR digital inputs. latches, a decode section for channel selection (see Truth Tables on the fourth page of this data sheet). The gate structure consists of series N-channel/ P-channel/ N-channel MOSFETs (see Figure 12). This combination produces a very rugged, fault tolerant multiplexer with address latch capability, and does so with extremely low power dissipation.

Write (WR), and Reset (RS) strobes are provided for interfacing with microprocessor bus lines (Figure 13). alleviating the need for the microprocessor to provide constant address inputs to the MUX in order to hold on to a particular channel.

When the write strobe is in the low state (less than 0.8V), and the reset strobe is in the high state (greater than 2.4V), the MUXs are in the transparent mode; this means that the MUXs act similar to non-latching MUXs such as the MAX358/359 or the HI-508A/509A

When the write input goes to the high state (>2.4V), the previous BCD address input will be latched and held in that state indefinitely. To pull the MUX out of this state, either the write input (WR) must be taken low (0.8V), back to the transparent state, or the Reset (RS) input taken low, turning off all channels.

The function of the Reset input is to allow for turning off all channels when the RS input is low (<0.8V); this has the dual function of resetting channel selection back to the channel 1 mode.

The MAX368/369 is designed to work with single as well as dual supplies, and good performance can be expected in the 9V to 22V single supply range. For example, with a single +15V power supply, analog signals in the range of +3.3V to +12V can be switched normally, and overvoltages up to ±35V can still be tolerated. If negative signals, around 0V are expected, a negative supply is needed. However, only -5V is needed to normally switch signals in the -2V to +12V range (-5V, +15V supplies). No current is drawn from the negative supply, so Maxim's MAX635 D/C to D/C converter does the job very nicely.

The EN latch allows all switches to be turned OFF under program control. This becomes useful when two or more MAX368s are cascaded to build 16-line and larger analog signal input multiplexers.

### **Typical Operating Characteristics**

#### **Applications**

#### Operation with Supply Voltages Other than ±15V

The main effect of supply voltages other than  $\pm 15 \text{V}$  is the reduction in output signal range. The MAX368/369 limits the output voltage to about 1.5V below  $\pm \text{V}_{SUP}$  and about 3V above V<sub>SUP</sub>. In other words, the output swing is limited to  $\pm 3.5 \text{V}$  to  $\pm 2 \text{V}$  when operating from  $\pm 5 \text{V}$ . The Typical Operating Characteristics graphs show typical R<sub>DS(ON)</sub> for  $\pm 15 \text{V}$ ,  $\pm 10 \text{V}$ , and  $\pm 5 \text{V}$  power supplies. Maxim guarantees the MAX368/369 for operation from  $\pm 4.5 \text{V}$  to  $\pm 18 \text{V}$  supplies. The switching delays increase by about a factor of 2 at  $\pm 5 \text{V}$ , but break-before-make action is preserved.

The MAX368/369 can be operated with a single +9V to +22V supply, as well as asymmetrical power supplies such as +15V and -5V. The digital threshold will remain approximately 1 6V above the GROUND pin, and the analog characteristics such as  $R_{DS(ON)}$  are determined

by the total voltage difference between +VsuP and  $\,$  VsuP Connect  $\,$  VsuP to 0V when operating with a +9V to +22V single supply.

The MAX368/369 digital threshold is relatively independent of the power supply voltages, going from a typical 1.6V when  $\pm V_{SUP}$  is 15V to 1.5V typical with a 5V  $\pm V_{SUP}$ . This means that Maxim's MAX368/369 will operate with standard TTL logic levels, even with  $\pm 5V$  power supplies. In all cases, the threshold of the Enable pin is the same as the other logic inputs.

#### Operation as a Demultiplexer

The MAX368/369 will function as a demultiplexer, where the input is applied to the Output pin, and the Input pins are used as outputs. The MAX368/369 provide both break-before-make action and full fault protection when operated as a demultiplexer, unlike earlier generations of fault protected multiplexers.

Figure 13. Bus Interface

#### Switching Characteristics and Charge Injection

Table 1 shows typical charge injection levels vs. power supply voltages and analog input voltage for the MAX368 and MAX369. Note that since the channels are well matched, the differential charge injection for the MAX368/369 is typically less than 5 picocoulombs. The charge injection that occurs during switching creates a voltage transient whose magnitude is inversely proportional to the capacitance on the multiplexer output.

The channel-to-channel switching time is typically 600ns, with about 200ns of break-before-make delay. This 200ns break-before-make delay prevents the input-to-input short that would occur if two input channels were simultaneously connected to the output. In a typical data acquisition system such as that shown in Figure 13, the dominant delay is not the switching time of the MAX368/MAX369 multiplexer but is the settling time of the following amplifier and sample/hold. Another limiting factor is the RC time constant of the multiplexer RDS(ON) plus the signal source impedance multiplied by the load capacitance on the output of the multiplexer. Even with low signal source impedances, 100pF of capacitance on the multiplexer output approximately doubles the settling time for 0.01% accuracy settling.

#### Digital Interface Levels

The typical digital threshold of both the address lines and the enable pin is 1.6V, with a temperature coefficient of approximately -3mV/°C. This ensures compatibility with 0.8V to 2.4V TTL logic swings over the entire temperature range. The digital threshold is relatively independent of the supply voltages, moving from 1.6V typical to 1.5V typical as the power supplies are reduced from ±15V to ±5V. In all cases, the digital threshold is referenced to the GROUND pin.

Table 1A. MAX368 CHARGE INJECTION

| Supply Voltage | Analog Input Level   | Injected Charge           |

|----------------|----------------------|---------------------------|

| ±5V            | +1.7V<br>0V<br>-1.7V | +100pC<br>+70pC<br>+45pC  |

| ±10V           | +5V<br>0V<br>-5V     | +200pC<br>+130pC<br>+60pC |

| ±15V           | +10V<br>0V<br>-10V   | +300pC<br>+180pC<br>+50pC |

Test Conditions:  $C_L=1000 pF$  on multiplexer output; the tabulated analog input level is applied to channel 1; channels 2 through 8 inputs are open circuited.  $EN=+5V, A_1=A_2=0V, A_0$  is toggled at 2kHz rate between 0V and 3V. +100 picocoulombs of charge creates a +100mV step when injected into a 1000pF load capacitance.

Table 1B. MAX369 CHARGE INJECTION

| Supply  | Analog      | Injected Charge |        |                       |  |  |  |

|---------|-------------|-----------------|--------|-----------------------|--|--|--|

| Voltage | Input Level | Out A           | Out B  | Differential<br>A - B |  |  |  |

| ±5V     | +1.7V       | +105pC          | +107pC | -2pC                  |  |  |  |

|         | 0V          | +73pC           | +48pC  | -1pC                  |  |  |  |

|         | -1.7V       | +48pC           | +50pC  | -2pC                  |  |  |  |

| ±10V    | +5V         | +215pC          | +220pC | -5pC                  |  |  |  |

|         | 0V          | +135pC          | +139pC | -4pC                  |  |  |  |

|         | -5V         | +62pC           | +63pC  | -1pC                  |  |  |  |

| ±15V    | +10V        | +325pC          | +330pC | -5pC                  |  |  |  |

|         | 0V          | +180pC          | +185pC | -5pC                  |  |  |  |

|         | -10V        | +55pC           | +55pC  | 0pC                   |  |  |  |

Test Conditions:  $C_L=1000pF$  on Out A and Out B; the tabulated analog input level is applied to inputs 1A and 1B; channels 2 through 4 are open circuited. EN = +5V,  $A_1=0V$ ,  $A_0$  is toggled from 0V to 3V at a 2kHz rate.

The digital inputs can also be driven with CMOS logic levels swinging from either +Vsup to -Vsup or from +Vsup to Ground. The digital input current is just a few nanoamps of leakage at all input voltage levels, with a guaranteed maximum of 1 $\mu A$ . The digital inputs are protected from ESD by a 30V zener diode between the input and +Vsup, and can be driven  $\pm 6V$  beyond the supplies without drawing excessive current.

#### Channel-to-Channel Crosstalk, Off Isolation and Digital Feedthrough

At DC and low frequencies, the channel-to-channel crosstalk is caused by variations in output leakage currents as the off channel input voltages are varied. The MAX368/369 output leakage varies only a few picoamps as all 7 off inputs are toggled from -10V to +10V. The output voltage change depends on the impedance level at the MAX368/369 output, which is  $R_{\rm DS(ON)}$  plus the input signal source resistance in most cases, since the load driven by the MAX368/369 is usually a high impedance. For a signal source impedance of  $10 k\Omega$  or lower, the DC crosstalk exceeds 120 dB.

Table 2 shows typical AC crosstalk and off isolation performance. Digital feedthrough is masked by the analog charge injection when the output is enabled.

When the output is disabled, the digital feedthrough is virtually unmeasurable, since the digital pins are physically isolated from the analog section by the GROUND and -V<sub>SUP</sub> pins. The groundplane formed by these lines is continued onto the MAX368/369 die to provide over 100dB isolation between the digital and analog sections.

## Table 2A. TYPICAL OFF ISOLATION REJECTION RATIO

| Frequency           | 100kHz | 500kHz | 1 <b>MH</b> z |

|---------------------|--------|--------|---------------|

| One Channel Driven  | 74dB   | 72dB   | 66dB          |

| All Channels Driven | 64dB   | 48dB   | 44dB          |

Test Conditions:  $V_{IN}$  = 20 $V_{PK-PK}$  at the tabulated frequency,  $R_L$  = 1.5k between OUT and ground, EN = 0V.

OIRR = 20 Log  $\frac{20 \text{ V}_{PK-PK}}{\text{V}_{OUT} \text{ (PK-PK)}}$

## Table 2B. TYPICAL CROSSTALK REJECTION RATIO

| Frequency             | 100kHz | 500kHz | 1MHz |

|-----------------------|--------|--------|------|

| R <sub>L</sub> = 1.5k | 70dB   | 68dB   | 64dB |

| R <sub>L</sub> = 10k  | 62dB   | 46dB   | 42dB |

Test Conditions: Specified  $R_L$  connected from OUT to ground, EN = +5V,  $A_0 = A_1 = A_2 = 0V$  (Channel 1 selected).  $20V_{PK-PK}$  at the tabulated frequency is applied to Channel 2. All other channels are open circuited. Similar crosstalk rejection can be observed between any two channels.

#### \_ Chip Topographies