OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

Some of the contact our Technical Support Center at contact our Technical Support Center at contact our Technical Support Center at 1-888-INTERSIL or WWW.intersil.com/tsc

December 1995, Rev. G

FN7026

## 50MHz Current Feedback Amplifier

# élantec.

The EL2020 is a fast settling, wide bandwidth amplifier optimized for gains between -10 and +10. Built using

the Elantec monolithic Complementary Bipolar process, this amplifier uses current mode feedback to achieve more bandwidth at a given gain then a conventional voltage feedback operational amplifier.

The EL2020 will drive two double terminated  $75\Omega$  coax cables to video levels with low distortion. Since it is a closed loop device, the EL2020 provides better gain accuracy and lower distortion than an open loop buffer. The device includes output short circuit protection, and input offset adjust capability.

The bandwidth and slew rate of the EL2020 are relatively independent of the closed loop gain taken. The 50MHz bandwidth at unity gain only reduces to 30MHz at a gain of 10. The EL2020 may be used in most applications where a conventional op amp is used, with a big improvement in speed power product.

## Ordering Information

| PART NUMBER | TEMP. RANGE    | PACKAGE    | PKG. NO. |

|-------------|----------------|------------|----------|

| EL2020CN    | -40°C to +85°C | 8-Pin PDIP | MDP0031  |

| EL2020CM    | -40°C to +85°C | 20-Pin SOL | MDP0027  |

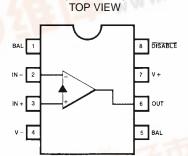

**EL2020**

(8-PIN PDIP)

### **Pinouts**

### **Features**

- Slew rate 500V/µs

- ±33mA output current

- Drives ±2.4V into 75Ω

- Differential phase < 0.1°</li>

- Differential gain < 0.1%</li>

- V supply ±5V to ±18V

- · Output short circuit protected

- Uses current mode feedback

- 1% settling time of 50ns for 10V step

- Low cost

- 9mA supply current

- 8-pin mini-dip

## **Applications**

- Video gain block

- Residue amplifier

- Radar systems

- Current to voltage converter

- Coax cable driver with gain of 2

Manufactured under U.S. Patent No. 4,893,091.

## **EL2020**

# **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| $V_S$     | Supply Voltage                              | $I_{OP}$ | Peak Output Current Short Circuit Protected |

|-----------|---------------------------------------------|----------|---------------------------------------------|

| $V_{IN}$  | Input Voltage                               |          | Output Short Circuit Duration Continuous    |

| $V_{IN}$  | Differential Input Voltage                  | $T_A$    | Operating Temperature Range                 |

|           | Input Current (Pins 2 or 3)                 | $T_J$    | Operating Junction Temperature              |

| $I_{INS}$ | Input Current (Pins 1, 5, or 8) ±5mA        |          | Plastic Package, SOL150°C                   |

| $P_{D}$   | Maximum Power Dissipation (See Curves)1.25W | $T_{ST}$ | Storage Temperature65°C to +150°C           |

A heat sink is required to keep the junction temperature below the absolute maximum when the output is short circuited

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# Open Loop Electrical Specifications $V_S = \pm 15V$

|                            |                                                                                                                   |                                     | LIMITS |       |     |       |

|----------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|-------|-----|-------|

| PARAMETER                  | DESCRIPTION                                                                                                       | TEMP                                | MIN    | TYP   | MAX | UNITS |

| V <sub>OS</sub> (Note 1)   | Input Offset Voltage                                                                                              | 25°C                                | -10    | 3     | +10 | mV    |

|                            |                                                                                                                   | T <sub>MIN</sub> , T <sub>MAX</sub> | -15    |       | +15 | mV    |

| ΔV <sub>OS</sub> /ΔT       | Offset Voltage Drift                                                                                              |                                     |        | -30   |     | μV/°C |

| CMRR (Note 2)              | Common Mode Rejection Ratio                                                                                       | ALL                                 | 50     | 60    |     | dB    |

| PSRR (Note 3)              | Power Supply Rejection Ratio                                                                                      | 25°C                                | 65     | 75    |     | dB    |

|                            |                                                                                                                   | T <sub>MIN</sub> , T <sub>MAX</sub> | 60     |       |     | dB    |

| +I <sub>IN</sub>           | Non-inverting Input Current                                                                                       | 25°C, T <sub>MAX</sub>              | -15    | 5     | +15 | μΑ    |

|                            |                                                                                                                   | T <sub>MIN</sub>                    | -25    |       | +25 | μΑ    |

| +R <sub>IN</sub>           | Non-Inverting Input Resistance                                                                                    | ALL                                 | 1      | 5     |     | ΜΩ    |

| +IPSR (Note 3)             | Non-Inverting Input Current<br>Power Supply Rejection                                                             | 25°C, T <sub>MAX</sub>              |        | 0.05  | 0.5 | μA/V  |

|                            |                                                                                                                   | T <sub>MIN</sub>                    |        |       | 1.0 | μA/V  |

| -I <sub>IN</sub> ( Note 1) | -Input Current                                                                                                    | 25°C, T <sub>MAX</sub>              | -40    | 10    | +40 | μΑ    |

|                            |                                                                                                                   | T <sub>MIN</sub>                    | -50    |       | +50 | μA    |

| -ICMR (Note 2)             | -Input Current<br>Common Mode Rejection                                                                           | 25°C, T <sub>MAX</sub>              |        | 0.5   | 2.0 | μA/V  |

|                            |                                                                                                                   | T <sub>MIN</sub>                    |        |       | 4.0 | μA/V  |

| -IPSR (Note 3)             | -Input Current<br>Power Supply Rejection                                                                          | 25°C, T <sub>MAX</sub>              |        | 0.05  | 0.5 | μA/V  |

|                            |                                                                                                                   | T <sub>MIN</sub>                    |        |       | 1.0 | μA/V  |

| R <sub>ol</sub>            | Transimpedence ( $\Delta V_{OUT} / \Delta (-I_{IN})$ )<br>R <sub>L</sub> = 400 $\Omega$ , V <sub>OUT</sub> = ±10V | 25°C, T <sub>MAX</sub>              | 300    | 1000  |     | V/mA  |

|                            |                                                                                                                   | T <sub>MIN</sub>                    | 50     |       |     | V/mA  |

| A <sub>VOL1</sub>          | Open Loop DC Voltage Gain $R_L = 400\Omega$ , $V_{OUT} = \pm 10V$                                                 | 25°C, T <sub>MAX</sub>              | 70     | 80    |     | dB    |

|                            |                                                                                                                   | T <sub>MIN</sub>                    | 60     |       |     | dB    |

| A <sub>VOL2</sub>          | Open Loop DC Voltage Gain $R_L = 100\Omega$ , $V_{OUT} = \pm 2.5V$                                                | 25°C, T <sub>MAX</sub>              | 60     | 70    |     | dB    |

|                            |                                                                                                                   | T <sub>MIN</sub>                    | 55     |       |     | dB    |

| Vo                         | Output Voltage Swing                                                                                              | 25°C, T <sub>MAX</sub>              | ±12    | ±13   |     | V     |

|                            | $R_L = 400\Omega$                                                                                                 | T <sub>MIN</sub>                    | ±11    |       |     | V     |

| Гоит                       | Output Current                                                                                                    | 25°C, T <sub>MAX</sub>              | ±30    | ±32.5 |     | mA    |

|                            | $R_L = 400\Omega$                                                                                                 | T <sub>MIN</sub>                    | ±27.5  |       |     | mA    |

---

## EL2020

# Open Loop Electrical Specifications $V_S = \pm 15V$ (Continued)

|                    |                                               |                                     | LIMITS |     |     |       |

|--------------------|-----------------------------------------------|-------------------------------------|--------|-----|-----|-------|

| PARAMETER          | DESCRIPTION                                   | TEMP                                | MIN    | TYP | MAX | UNITS |

| IS                 | Quiescent Supply Current                      | 25°C                                |        | 9   | 12  | mA    |

|                    |                                               | T <sub>MIN</sub> , T <sub>MAX</sub> |        |     | 15  | mA    |

| I <sub>S OFF</sub> | Supply Current, Disabled, V <sub>8</sub> = 0V | ALL                                 |        | 5.5 | 7.5 | mA    |

| I <sub>LOGIC</sub> | Pin 8 Current, Pin 8 = 0V                     | ALL                                 |        | 1.1 | 1.5 | mA    |

| I <sub>D</sub>     | Min Pin 8 Current to Disable                  | ALL                                 |        | 120 | 250 | μΑ    |

| I <sub>E</sub>     | Max Pin 8 Current to Enable                   | ALL                                 |        |     | 30  | μΑ    |

### NOTES:

- 1. The offset voltage and inverting input current can be adjusted with an external 10kΩ pot between pins 1 and 5 with the wiper connected to V<sub>CC</sub> (Pin 7) to make the output offset voltage zero.

- 2.  $V_{CM} = \pm 10V$ .

- 3.  $\pm 4.5 \text{V} \le \text{V}_{\text{S}} \le \pm 18 \text{V}$ .

## AC Closed Loop Electrical Specifications $V_S = \pm 15V$ , $T_A = 25$ °C

| PARAMETER                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MIN         | TYP                           | MAX | UNITS                   |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------|-----|-------------------------|

| SR1<br>FPBW1<br>t <sub>R</sub> 1<br>t <sub>F</sub> 1<br>t <sub>P</sub> 1      | Closed Loop Gain of 1V/V (0dB), $R_F = 1k\Omega$ Slew Rate, $R_I = 400\Omega$ , $V_O = \pm 10V$ , test at $V_O = \pm 5V$ Full Power Bandwidth (Note 1) Rise Time, $R_I = 100\Omega$ , $V_{OUT} = 1V$ , 10% to 90% Fall Time, $R_I = 100\Omega$ , $V_{OUT} = 1V$ , 10% to 90% Propagation Delay, $R_I = 100\Omega$ , $V_{OUT} = 1V$ , 50% Points                                                                                                                    | 300<br>4.77 | 500<br>7.95<br>6<br>6<br>8    |     | V/µs<br>MHz<br>ns<br>ns |

| BW<br>ts<br>ts                                                                | Closed Loop Gain of 1V/V (0dB), R <sub>F</sub> = $820\Omega$<br>-3dB Small Signal Bandwidth, R <sub>I</sub> = $100\Omega$ , V <sub>O</sub> = $100MV$<br>1% Settling Time, R <sub>I</sub> = $400\Omega$ , V <sub>O</sub> = $10V$<br>0.1% Settling Time, R <sub>I</sub> = $400\Omega$ , V <sub>O</sub> = $10V$                                                                                                                                                       |             | 50<br>50<br>90                |     | MHz<br>ns<br>ns         |

| SR10<br>FPBW10<br>t <sub>R</sub> 10<br>t <sub>F</sub> 10<br>t <sub>P</sub> 10 | Closed Loop Gain of 10V/V (20dB), R <sub>F</sub> = 1 k $\Omega$ , R <sub>G</sub> = 111 $\Omega$ Slew Rate, R <sub>I</sub> = 400 $\Omega$ , V <sub>O</sub> = ±10V, Test at V <sub>O</sub> = ±5V Full Power Bandwidth Rise Time, R <sub>I</sub> = 100 $\Omega$ , V <sub>OUT</sub> = 1V, 10% to 90% Fall Time, R <sub>I</sub> = 100 $\Omega$ , V <sub>OUT</sub> = 1V, 10% to 90% Propagation Delay, R <sub>I</sub> = 100 $\Omega$ , V <sub>OUT</sub> = 1V, 50% points | 300<br>4.77 | 500<br>7.95<br>25<br>25<br>12 |     | V/µs<br>MHz<br>ns<br>ns |

| BW<br>ts<br>ts                                                                | Closed Loop Gain of 10V/V (20dB), R <sub>F</sub> = $680\Omega$ , R <sub>G</sub> = $76\Omega$ -3dB Small Signal Bandwidth, R <sub>I</sub> = $100\Omega$ , V <sub>O</sub> = $100$ mV 1% Settling Time, R <sub>I</sub> = $400\Omega$ , V <sub>O</sub> = $10$ V 0.1% Settling Time, R <sub>I</sub> = $400\Omega$ , V <sub>O</sub> = $10$ V                                                                                                                             |             | 30<br>55<br>280               |     | MHz<br>ns<br>ns         |

### NOTE:

---

<sup>1.</sup> Full Power Bandwidth is guaranteed based on Slew Rate measurement. FPBW =  $SR/2\pi V_{peak}$ .

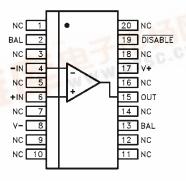

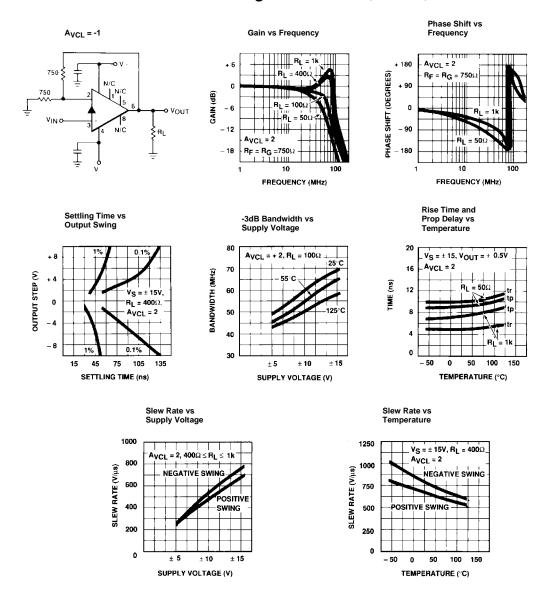

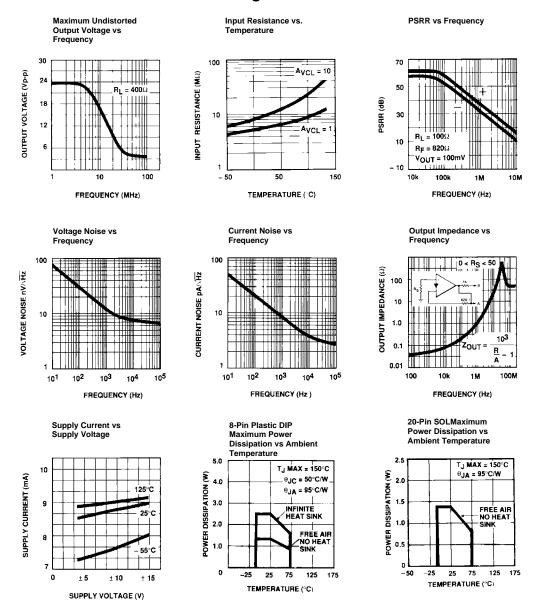

# Typical Performance Curves Non-Inverting Gain of One

# Typical Performance Curves Non-Inverting Gain of One (Continued)

# Typical Performance Curves Non-Inverting Gain of One (Continued)

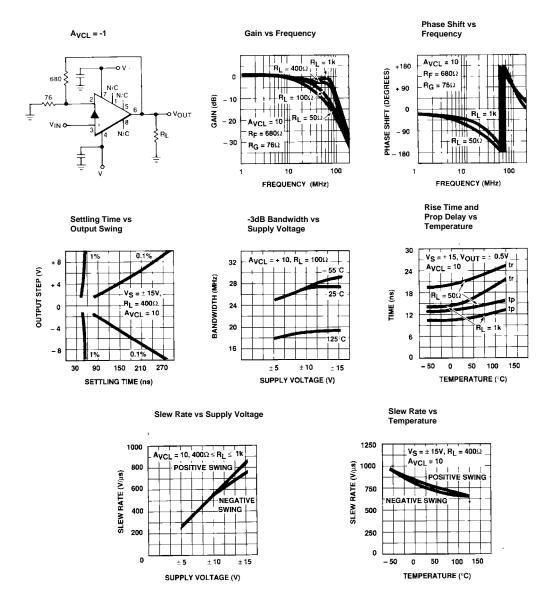

# Typical Performance Curves Non-Inverting Gain of One (Continued)

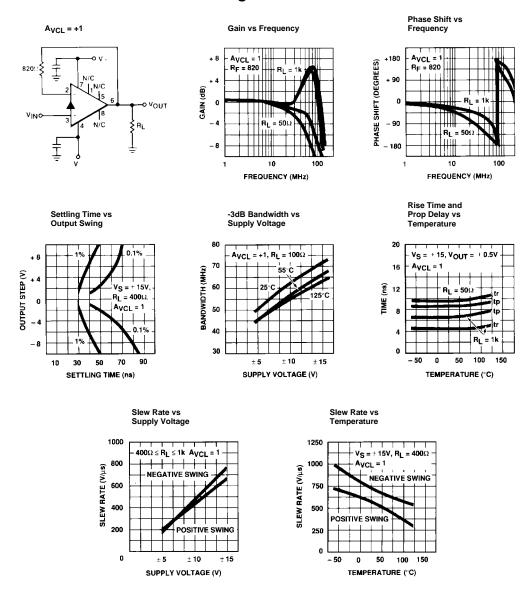

## Typical Performance Curves Non-Inverting Gain of One

# Application Information

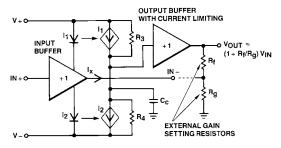

### Theory of Operation

The EL2020 has a unity gain buffer similar to the EL2003 from the non-inverting input to the inverting input. The error signal of the EL2020 is a current flowing into (or out of) the inverting input. A very small change in current flowing through the inverting input will cause a large change in the output voltage. This current amplification is the transresistance (R<sub>OL</sub>) of the EL2020 [V<sub>OUT</sub> = R<sub>OL</sub> \* I<sub>INV</sub>]. Since R<sub>OL</sub> is very large ( $\approx$  106), the current flowing into the inverting input in the steady state (non-slewing) condition is very small.

Therefore we can still use op-amp assumptions as a first order approximation for circuit analysis, namely that...

- 1. The voltage across the inputs  $\approx 0$  and

- 2. The current into the inputs is  $\approx 0$

SIMPLIFIED BLOCK DIAGRAM OF EL2020

. . . . . .

### Resistor Value Selection and Optimization

The value of the feedback resistor (and an internal capacitor) sets the AC dynamics of the EL2020. A nominal value for the feedback resistor is  $1k\Omega$ , which is the value used for production testing. This value guarantees stability. For a given gain, the bandwidth may be increased by decreasing the feedback resistor and, conversely, the bandwidth will be decreased by increasing the feedback resistor.

Reducing the feedback resistor too much will result in overshoot and ringing, and eventually oscillations. Increasing the feedback resistor results in a lower -3dB frequency. Attenuation at high frequency is limited by a zero in the closed loop transfer function which results from stray capacitance between the inverting input and ground.

### **Power Supplies**

The EL2020 may be operated with single or split power supplies as low as ±3V (6V total) to as high as ±18V (36V total). The slew rate degrades significantly for supply voltages less than ±5V (10V total), but the bandwidth only changes 25% for supplies from ±3V to ±18V. It is not necessary to use equal value split power supplies, i.e., -5V and +12V would be excellent for 0V to 1V video signals. Bypass capacitors from each supply pin to a ground plane are recommended. The EL2020 will not oscillate even with minimal bypassing, however, the supply will ring excessively with inadequate capacitance. To eliminate supply ringing and the errors it might cause, a 4.7µF tantalum capacitor with short leads is recommended for both supplies. Inadequate supply bypassing can also result in lower slew rate and longer settling times.

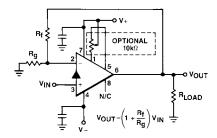

**NON-INVERTING AMPLIFIER**

# EL2020 TYPICAL NON-INVERTING AMPLIFIER CHARACTERISTICS

|                |         |         |           | 10V SETTLING<br>TIME |       |

|----------------|---------|---------|-----------|----------------------|-------|

| Α <sub>V</sub> | $R_{F}$ | $R_{G}$ | BANDWIDTH | 1%                   | 0.1%  |

| +1             | 820Ω    | None    | 50MHz     | 50ns                 | 90ns  |

| +2             | 750Ω    | 750Ω    | 50MHz     | 50ns                 | 100ns |

| +5             | 680Ω    | 170Ω    | 50MHz     | 50ns                 | 200ns |

| +10            | 680Ω    | 76Ω     | 30MHz     | 55ns                 | 280ns |

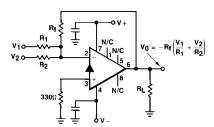

**SUMMING AMPLIFIER**

### **EL2020 TYPICAL INVERTING AMPLIFIER CHARACTERISTICS**

|                |         |                                 |           | 10V SETTLING<br>TIME |       |

|----------------|---------|---------------------------------|-----------|----------------------|-------|

| A <sub>V</sub> | $R_{F}$ | R <sub>1</sub> , R <sub>2</sub> | BANDWIDTH | 1%                   | 0.1%  |

| -1             | 750Ω    | 750Ω                            | 40MHz     | 50ns                 | 130ns |

| -2             | 750Ω    | 375Ω                            | 40MHz     | 55ns                 | 160ns |

| -5             | 680Ω    | 130Ω                            | 40MHz     | 55ns                 | 160ns |

| -10            | 680Ω    | 68Ω                             | 3MHz      | 70ns                 | 170ns |

### Input Range

The non-inverting input to the EL2020 looks like a high resistance in parallel with a few picofarads in addition to a DC bias current. The input characteristics change very little with output loading, even when the amplifier is in current limit.

The input characteristics also change when the input voltage exceeds either supply by 0.5V. This happens because the input transistor's base-collector junctions forward bias. If the input exceeds the supply by LESS than 0.5V and then returns to the normal input range, the output will recover in less than 10ns. However if the input exceeds the supply by MORE than 0.5V, the recovery time can be 100s of nanoseconds. For this reason it is recommended that Schottky diode clamps from input to supply be used if a fast recovery from large input overloads is required.

### Source Impedance

The EL2020 is fairly tolerant of variations in source impedances. Capacitive sources cause no problems at all, resistive sources up to  $100 k\Omega$  present no problems as long as care is used in board layout to minimize output to input coupling. Inductive sources may cause oscillations; a  $1 k\Omega$  resistor in series with the input lead will usually eliminate problems without sacrificing too much speed.

-----

#### **Current Limit**

The EL2020 has internal current limits that protect the output transistors. The current limit goes down with junction temperature rise. At a junction temperature of  $+175^{\circ}$ C the current limits are at about 50mA. If the EL2020 output is shorted to ground when operating on  $\pm15$ V supplies, the power dissipation could be as great as 1.1W. A heat sink is required in order for the EL2020 to survive an indefinite short. Recovery time to come out of current limit is about 50ns.

### Using the EL2020 with Output Buffers

When more output current is required, a wideband buffer amplifier can be included in the feedback loop of the EL2020. With the EL2003 the subsystem overshoots about 10% due to the phase lag of the EL2003. With the EL2004 in the loop, the overshoot is less than 2%. For even more output current, several buffers can be paralleled.

**EL2020 BUFFERED WITH AN EL2004**

### Capacitive Loads

The EL2020 is like most high speed feedback amplifiers in that it does not like capacitive loads between 50pF and 1000pF. The output resistance works with the capacitive load to form a second non-dominate pole in the loop. This results in excessive peaking and overshoot and can lead to oscillations. Standard resistive isolation techniques used with other op amps work well to isolate capacitive loads from the EL2020.

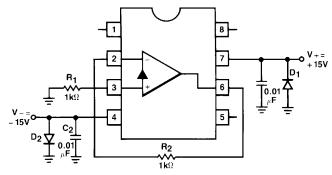

### Offset Adjust

To calculate the amplifier system offset voltage from input to output we use the equation:

Output Offset Voltage =  $V_{OS} (R_F/R_G+1) \pm I_{BIAS} (R_F)$

The EL2020 output offset can be nulled by using a  $10k\Omega$  potentiometer from pins 1 to 5 with the slider tied to pin 7 (+V<sub>CC</sub>). This adjusts both the offset voltage and the inverting input bias current. The typical adjustment range is  $\pm 80$ mV at the output.

### Compensation

The EL2020 is internally compensated to work with external feedback resistors for optimum bandwidth over a wide range of closed loop gain. The part is designed for a nominal  $1k\Omega$  of feedback resistance, although it is possible to get more bandwidth by decreasing the feedback resistance.

The EL2020 becomes less stable by adding capacitance in parallel with the feedback resistor, so feedback capacitance is not recommended.

The EL2020 is also sensitive to stray capacitance from the inverting input to ground, so the board should be laid out to keep the physical size of this node small, with ground plane kept away from this node.

#### **Active Filters**

The EL2020's low phase lag at high frequencies makes it an excellent choice for high performance active filters. The filter response more closely approaches the theoretical response than with conventional op amps due to the EL2020's smaller propagation delay. Because the internal compensation of the EL2020 depends on resistive feedback, the EL2020 should be set up as a gain block.

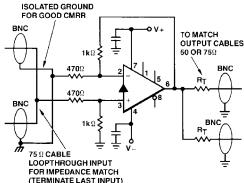

### **Driving Cables**

The EL2020 was designed with driving coaxial cables in mind. With 30mA of output drive and low output impedance, driving one to three  $75\Omega$  double terminated coax cables with one EL2020 is practical. Since it is easy to set up a gain of +2, the double matched method is the best way to drive coax cables, because the impedance match on both ends of the cable will suppress reflections. For a discussion on some of the other ways to drive cables, see the section on driving cables in the EL2003 data sheet.

### Video Performance Characteristics

The EL2020 makes an excellent gain block for video systems, both RS-170 (NTSC) and faster. It is capable of driving 3 double terminated  $75\Omega$  cables with distortion levels acceptable to broadcasters. A common video application is to drive a  $75\Omega$  double terminated coax with a gain of 2.

To measure the video performance of the EL2020 in the non-inverting gain of 2 configuration, 5 identical gain-of-two circuits were cascaded (with a divide by two  $75\Omega$  attenuator between each stage) to increase the errors.

The results, shown in the photos, indicate the entire system of 5 gain-of-two stages has a differential gain of 0.5% and a differential phase of 0.5°. This implies each device has a

---

differential gain/phase of 0.1% and 0.1°, but these are too small to measure on single devices.

DIFFERENTIAL PHASE OF 5 CASCADED GAIN-OF-TWO STAGES

DIFFERENTIAL PHASE OF 5 CASCADED GAIN-OF-TWO STAGES

### Video Distribution Amplifier

The distribution amplifier shown below features a difference input to reject common mode signals on the  $75\Omega$  coax cable input. Common mode rejection is often necessary to help to eliminate 60Hz noise found in production environments.

VIDEO DISTRIBUTION AMPLIFIER WITH DIFFERENCE INPUT

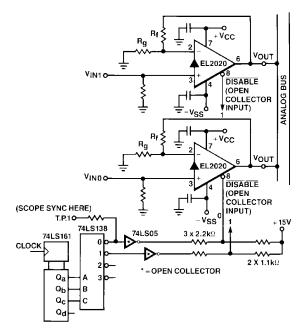

## EL2020 Disable/Enable Operation

The EL2020 has an enable/disable control input at pin 8. The device is enabled and operates normally when pin 8 is left open or returned to pin 7,  $V_{CC}.$  When more than  $250\mu A$  is pulled from pin 8, the EL2020 is disabled. The output becomes a high impedance, the inverting input is no longer driven to the positive input voltage, and the supply current is halved. To make it easy to use this feature, there is an internal resistor to limit the current to a safe level (~1.1mA) if pin 8 is grounded.

To draw current out of pin 8 an "open collector output" logic gate or a discrete NPN transistor can be used. This logic interface method has the advantage of level shifting the logic signal from 5V supplies to whatever supply the EL2020 is operating on without any additional components.

### Using the EL2020 as a Multiplexer

An interesting use of the enable feature is to combine several amplifiers in parallel with their outputs common. This combination then acts similar to a MUX in front of an amplifier. A typical circuit is shown.

When the EL2020 is disabled, the DC output impedance is very high, over  $10k\Omega$ . However there is also an output capacitance that is non-linear. For signals of less than 5V peak to peak, the output capacitance looks like a simple 15pF capacitor. However, for larger signals the output capacitance becomes much larger and non-linear.

The example multiplexer will switch between amplifiers in 5µs for signals of less than  $\pm 2V$  on the outputs. For full output signals of 20V peak to peak, the selection time becomes 25µs. The disabled outputs also present a capacitive load and therefore only three amplifiers can have their outputs shorted together. However an unlimited number can sum together if a small resistor (25Ω) is inserted in series with each output to isolate it from the "bus". There will be a small gain loss due to the resistors of course.

**USING THE EL2020 AS A MULTIPLEXER**

-----

# **Burn-In Circuit**

PIN NUMBERS ARE FOR DIP PACKAGES.

ALL PACKAGES USE THE SAME SCHEMATIC.

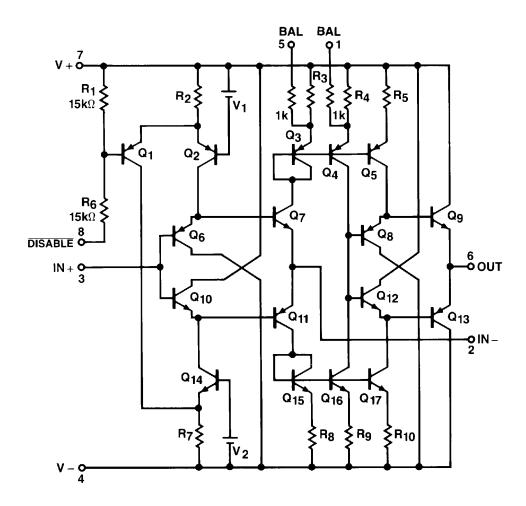

# **Equivalent Circuit**

## EL2020

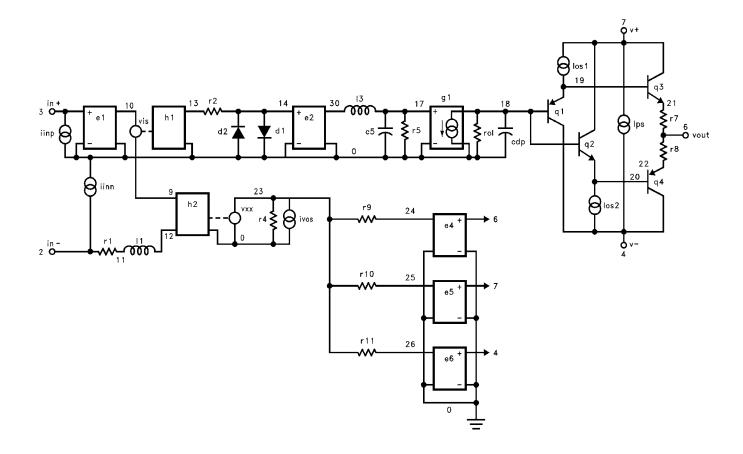

### EL2020 Macromodel

```

Revision A. March 1992

* Enhancements include PSRR, CMRR, and Slew Rate Limiting

* Connections: +input

-input

+Vsupply

-Vsupply

| output

.subckt M2020

2 7

3

6

* Input Stage

e1 10 0 3 0 1.0

vis 10 9 0V

h2 9 12 vxx 1.0

r1 2 11 50

I1 11 12 29nH

iinp 3 0 10µA

iinm 2 0 5µA

* Slew Rate Limiting

h1 13 0 vis 600

r2 13 14 1K

d1 14 0 dclamp

d2 0 14 dclamp

* High Frequency Pole

*e2 30 0 14 0 0.00166666666

15 30 17 1.5µH

c5 17 0 1pF

r5 17 0 500

* Transimpedance Stage

g1 0 18 17 0 1.0

rol 18 0 1Meg

cdp 18 0 5pF

* Output Stage

q1 4 18 19 qp

q2 7 18 20 qn

q3 7 19 21 qn

q4 4 20 22 qp

r7 21 6 4

r8 22 6 4

ios1 7 19 2.5mA

ios2 20 4 2.5mA

* Supply

ips 7 4 3mA

* Error Terms

ivos 0 23 5mA

vxx 23 0 0V

```

## EL2020 Macromodel (Continued)

```

e4 24 0 6 0 1.0

e5 25 0 7 0 1.0

e6 26 0 4 0 1.0

r9 24 23 1K

r10 25 23 1K

r11 26 23 1K

*

* Models

*

.model qn npn (is=5e-15 bf=100 tf=0.2nS)

.model qp pnp (is=5e-15 bf=100 tf=0.2nS)

.model dclamp d(is=1e-30 ibv=0.266 bv=1.67 n=4)

.ends

```

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

11 :----