OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

NO RECOMMENDED REPLACEMENT

contact our Technical Support Center at

contact our Technical Support

1-888-INTERSIL or www.intersil.com/tsc

November 1993, Rev. F

FN7027

### Monolithic Pin Driver

# élantec.

The EL2021 is designed to drive programmed voltages into difficult loads. It has the required circuitry to be

used as the pin driver electronics in board test systems. Capable of overpowering logic outputs, the part can accurately drive independently set high and low levels with programmed Slew Rates into reactive loads. It can also be placed into high impedance to monitor the load without having to disconnect. Previous board testers had multiplexing schemes to reduce the number of pin drivers required. With the small size and power consumption of the monolithic EL2021, a driver per node with little or no multiplexing becomes practical. Since only a few pins of "bed-of-nails" board testers need be active at any given time, the power-down feature saves substantial power in large systems.

### Ordering Information

| PART NUMBER | TEMP. RANGE  | PACKAGE | PKG. NO. |

|-------------|--------------|---------|----------|

| EL2021CJ    | 0°C to +75°C | CerDIP  | MDP0031  |

### **Pinout**

EL2021 (18-PIN DIP) TOP VIEW

#### **Features**

- · Wide range of programmable analog output levels

- 0.5 Ampere output drive with external transistors

- Programmable Slew Rate

- Low overshoot with large capacitive loads-stable with 500pF

- 3-state output

- · Power-down capability

- Wide supply range

- Overcurrent sense

### **Applications**

- Loaded circuit board testers

- Digital testers

- Programmable 4-quadrant power supplies

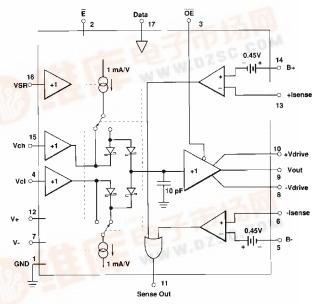

### **Block Diagram**

### Truth Table

| Ē | ŌĒ | DATA | V <sub>OUT</sub> | COMMENTS    |

|---|----|------|------------------|-------------|

| 0 | 0  | 0    | V <sub>CL</sub>  | Active      |

| 0 | 0  | 1    | V <sub>CH</sub>  | Active      |

| 0 | 1  | Х    | High-Z           | Third State |

| 1 | Х  | Х    | Undefined        | Power-down  |

### EL2021

### **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| V+                  | Supply Voltage0.3V to +16V               | V <sub>OUT</sub> , [ | Orive+,                                   |

|---------------------|------------------------------------------|----------------------|-------------------------------------------|

| V-                  | Supply Voltage 0.03V to -16V             | Drive-               | Output Currents45mA to +45mA              |

| B+, B-              | Supply Voltages V- to V+                 | $T_J$                | Junction Temperature                      |

| Sense+              | Input Voltages (-2V + B+) to (0.3V +B+)  | TA                   | Operating Ambient                         |

| Sense-              | Input Voltages (-0.3V + B-) to (2V + B-) |                      | Temperature Range0°C to +75°C             |

| E, VSR,             |                                          | $T_{ST}$             | Storage Temperature65°C to +150°C         |

| OE, Data            | Input Voltages0.3 to +6V                 | $P_{D}$              | Power Dissipation (T <sub>A</sub> = 25°C) |

| $V_{CH}$ , $V_{CL}$ | Input Voltages B- to B+ and V- to V+     |                      | (See Curves)                              |

| Sense Out           | Output Current10mA to +10mA              |                      |                                           |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

**DC Electrical Specifications**  $T_A = 25$ °C,  $V_T = 15$ ,  $V_T = -10$ V,  $B_T = V_{CH} + 3.6$ V,  $B_T = V_{CL} - 3.6$ V, No Load. Data and  $\overline{OE}$  levels are: L = 2.0V and H = 3.0V (CMOS thresholds).  $\overline{E}$  levels are: L = 1.5V and H = 3.5V. All tests done using 2N2222 and 2N2907 output transistors with Beta>40 @  $I_C$  = 400mA and Beta>27 @  $I_C$  = 500mA and  $V_{CE}$  = 3.1V.  $\overline{OE}$  and  $\overline{E}$  low.

| PARAMETER                          | DESCRIPTION                         | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                     | MIN                                                       | TYP            | MAX                                                    | UNITS                    |

|------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|--------------------------------------------------------|--------------------------|

| I <sub>S</sub>                     | V+, -Supply Currents                | V <sub>CH</sub> = 5V, V <sub>CL</sub> = 0, VSR = 2.5V, Data = H or L<br>V <sub>CH</sub> = 11V, V <sub>CL</sub> = -6V, VSR = 5V, Data = H or L<br>V <sub>CH</sub> = -6V, V <sub>CL</sub> = 11V, VSR+2.5V, Data = H or L                                                                                                                                                                         | 15<br>21<br>15                                            | 25<br>33<br>25 | 30<br>45<br>30                                         | mA<br>mA<br>mA           |

| I <sub>S</sub> , disabled          | V+, -Supply Currents                | $V_{CH} = 5V$ , $V_{CL} = 0V$ , $VSR = 2.5V$ , $Data = H \text{ or } L$ , $\overline{E} = H$                                                                                                                                                                                                                                                                                                   | 0                                                         | 0.5            | 2.5                                                    | mA                       |

| IVCH                               | V <sub>CH</sub> Input Current       | $V_{CH}$ = -1V to +7.5V, $V_{CL}$ = 0V, VSR = 5V, Data = H or L                                                                                                                                                                                                                                                                                                                                | -20                                                       | 5              | 20                                                     | μA                       |

| I <sub>VCL</sub>                   | V <sub>CL</sub> Input Current       | $V_{CL}$ = -3.5V to +3.5V, $V_{CH}$ = 0V, VSR = 5V, Data = H or L                                                                                                                                                                                                                                                                                                                              | -20                                                       | -5             | 20                                                     | μA                       |

| I <sub>DATA</sub>                  | Data Input Current                  | V <sub>CH</sub> = 5V, V <sub>CL</sub> = 0V, VSR = 5V, Data = 0 or 5V                                                                                                                                                                                                                                                                                                                           | -50                                                       | 5              | 50                                                     | μΑ                       |

| I <sub>OE</sub>                    | OE Input Current                    | $V_{CH} = 5V$ , $V_{CL} = 0V$ , $VSR = 5V$ , Data = L, $\overline{OE} = 0V$ or $5V$                                                                                                                                                                                                                                                                                                            | -20                                                       | 5              | 20                                                     | μΑ                       |

| IE                                 | E Input Current                     | $V_{CH} = 5V$ , $V_{CL} = 0V$ , $VSR = 5V$ , $Data = L$ , $\overline{E} = 0V$ or $5V$                                                                                                                                                                                                                                                                                                          | -20                                                       | 2              | 20                                                     | μΑ                       |

| I <sub>VSR</sub>                   | VSR Input Current                   | V <sub>CH</sub> = 5V, V <sub>CL</sub> = 0V, Data = L, VSR = 0V or 5V                                                                                                                                                                                                                                                                                                                           | -20                                                       | 2              | 20                                                     | μΑ                       |

| ±I <sub>SENSE</sub>                | Sense Input Currents                | V <sub>CH</sub> = 5V, V <sub>CL</sub> = 0V, VSR = 5V, Data = 0V or 5V                                                                                                                                                                                                                                                                                                                          | -20                                                       | 5              | 20                                                     | μΑ                       |

| I <sub>B</sub> +, I <sub>B</sub> - | B+, B- Input Currents               | V <sub>CH</sub> = 5V, V <sub>CL</sub> = 0V, Data = L, VSR = 5V                                                                                                                                                                                                                                                                                                                                 | -20                                                       | 5              | 20                                                     | μΑ                       |

| Vo                                 | Output Voltage                      | $V+=14.5V,V-=-9.5V$ $V_{CH}=5V,V_{CL}=0,VSR=1V,Data=L,\\ OutputCurrent=-100mA,0mA,or+100mA\\ OutputCurrent=-400mAor+400mA\\ OutputCurrent=-500mAor+500mA\\ V_{CH}=5V,V_{CL}=0,VSR=1V,Data=H\\ OutputCurrent=-100mA,0mA,or+100mA\\ OutputCurrent=-400mAor+400mA\\ OutputCurrent=-500mAor+500mA\\ V_{CH}=11V,V_{CL}=-6V,VSR=1V,I_{OUT}=0,Data=L\\ V_{CH}=11V,V_{CL}=-6V,VSR=1V,I_{OUT}=0,Data=H$ | -50<br>-300<br>-600<br>4.95<br>4.7<br>4.4<br>-6.1<br>10.9 |                | 50<br>300<br>600<br>5.05<br>5.3<br>5.6<br>-5.9<br>11.1 | mV<br>mV<br>mV<br>V<br>V |

| ISENSE+<br>ISENSE-                 | +ISENSE Threshold -ISENSE Threshold | $V_{CH}$ = 5V, $V_{CL}$ = 0, VSR = 2.5V, $R_{SENSE}$ = 1 $\Omega$ , Data = H $V_{CH}$ = 5V, $V_{CL}$ = 0, VSR = 2.5V, $R_{SENSE}$ = 1 $\Omega$ , Data = L                                                                                                                                                                                                                                      | 400<br>-400                                               | 450<br>-450    | 600<br>-600                                            | mA<br>mA                 |

| Vo, sense                          | Sense Out Levels                    | V <sub>CH</sub> = 5V, V <sub>CL</sub> = 0, VSR = 2.5V, Data L or H,<br>Output Current = -350mA or +350mA<br>Output Current = -550mA or +550mA                                                                                                                                                                                                                                                  | 0<br>3.5                                                  |                | 0.6<br>5.0                                             | V<br>V                   |

| lout,tri                           | High-Impedance<br>Output Leakage    | $V_{CH}$ = 5V, $V_{CL}$ = 0, VSR = 2.5V, Data = L, $\overline{OE}$ = H, Output Voltage = -2.5V or +7.5V                                                                                                                                                                                                                                                                                        | -100                                                      | 5              | 100                                                    | μΑ                       |

### EL2021

### **AC Electrical Specifications**

DC test conditions apply except where noted. For AC tests, R<sub>L</sub> = 1k, C<sub>L</sub> = 200pF. Delay times are measured from  $\overline{\text{OE}}$  or Data crossing 2.5V, V<sub>CH</sub> = 5V, V<sub>CL</sub> = 0.

| PARAMETER        | DESCRIPTION                            | CONDITIONS                                                                                                                                                              | MIN                  | TYP          | MAX               | UNITS          |

|------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------|-------------------|----------------|

| SR+              | +Slew Rate                             | Data L to H, Output from 0.5V to 4.5V, VSR = 1V VSR = 3V                                                                                                                | 80<br>150            | 100<br>240   | 120<br>360        | V/µs<br>V/µs   |

| SR-              | -Slew Rate                             | Data H to L, Output from 4.5V to 0.5V, VSR = 1V VSR = 3V                                                                                                                | -80<br>-150          | -100<br>-240 | -120<br>-360      | V/µs<br>V/µs   |

| SRSYM            | Slew Rate<br>Symmetry                  | $ \left[ \frac{(SR+)-(SR-)}{(SR+)+(SR-)} \right] VSR = 1V $ $VSR = 2V $                                                                                                 | -10<br>-20           |              | 10<br>20          | %<br>%         |

| T <sub>PD</sub>  | Propagation Delay                      | Data L to H, Output to 0.2V, VSR = 2.5V<br>Data H to L, Output to 4.8V, VSR = 2.5V                                                                                      | 6.5<br>6.5           | 9<br>9       | 11.5<br>11.5      | ns<br>ns       |

| T <sub>S</sub>   | Settling Time                          | VSR = 5V, Data L to H, Output 4.5V to 5V±0.2V<br>VSR = 5V, Data H to L, Output 0.5V to ±0.2V                                                                            |                      |              | 30<br>30          | ns<br>ns       |

| os               | Overshoot                              | VSR = 1V, Data L to H or H to L<br>VSR = 1V, $\overline{OE}$ H to L, Data = L, R <sub>L</sub> to 5V<br>VSR = 1V, $\overline{OE}$ H to L, Data = H, R <sub>L</sub> to 0V | -300<br>-300<br>-300 |              | 300<br>300<br>300 | mV<br>mV<br>mV |

| T <sub>PDA</sub> | Propagation Delay,<br>High-Z to Active | VSR = 2.5V, $\overline{OE}$ H to L, $C_L$ = 50pF<br>$R_L$ to 5V, Data = L, Output to 3.5V<br>$R_L$ to 0V, Data = H, Output to 1.5V                                      |                      |              | 50<br>50          | ns<br>ns       |

| T <sub>PDH</sub> | Propagation Delay,<br>Active to High-Z | VSR = 2.5V, $\overline{OE}$ L to H, C <sub>L</sub> = 50pF,<br>Data = L, R <sub>L</sub> to 5V, Output to 0.5V<br>Data = H, R <sub>L</sub> to 0V, Output to 4.5V          |                      |              | 50<br>50          | ns<br>ns       |

## Pin Description Table

| PIN# | NAME                 | DESCRIPTION                                                                                                                                                                                             |  |

|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | GND                  | System ground.                                                                                                                                                                                          |  |

| 2    | Е                    | Enable control input. A logic low allows normal operation; a logic high puts the device into power down mode. No output levels are defined in powerdown nor does the output behave as a high impedance. |  |

| 3    | OE                   | Output Enable input. A logic low sets the output to low-impedance driver mode; a logic high places the output into a high-impedance state.                                                              |  |

| 4    | V <sub>CL</sub>      | Lower analog control input. When Data = $\overline{OE}$ = $\overline{E}$ = L, the V <sub>CL</sub> level is output as V <sub>OUT</sub> (assuming V <sub>CL</sub> < V <sub>CH</sub> ).                    |  |

| 5    | B-                   | System power supply. The EL2021 uses this pin as a negative output current monitor connection Little current is drawn from this pin, transient or static.                                               |  |

| 6    | I <sub>SENSE</sub> - | Negative output current monitor input.                                                                                                                                                                  |  |

| 7    | V-                   | Negative power supply. Because all negative output drive currents come from this pin (as much as 60mA transiently), good bypassing is essential.                                                        |  |

| 8    | Drive-               | Output to external pnp transistor base.                                                                                                                                                                 |  |

| 9    | V <sub>OUT</sub>     | High-current input and output, depending on OE.                                                                                                                                                         |  |

| 10   | Drive+               | Output to external npn transistor base.                                                                                                                                                                 |  |

| 11   | Sense Out            | Logic output which signals that a high + or - output current is flowing.                                                                                                                                |  |

| 12   | V+                   | Positive power supply. Like V-, it should be well bypassed.                                                                                                                                             |  |

| 13   | I <sub>SENSE</sub> + | Positive output current monitor input.                                                                                                                                                                  |  |

| 14   | B+                   | System power supply, similar to B                                                                                                                                                                       |  |

| 15   | V <sub>CH</sub>      | Higher analog control input. When Data = H and $\overline{OE}$ = $\overline{E}$ = L, the V <sub>CH</sub> level is output as V <sub>OUT</sub> (assuming V <sub>CH</sub> > V <sub>CL</sub> ).             |  |

| 16   | VSR                  | Slew rate control input. A 1V level on this pin causes the output to slew at 100V/µs, 0.5V causes a slew rate of 50V/µs, etc.                                                                           |  |

| 17   | Data                 | Output level control input. This pin digitally selects $V_{CL}$ or $V_{CH}$ as the output voltage when $\overline{OE} = \overline{E} = L$ .                                                             |  |

| 18   | N/C                  | Not Connected.                                                                                                                                                                                          |  |

2 ----

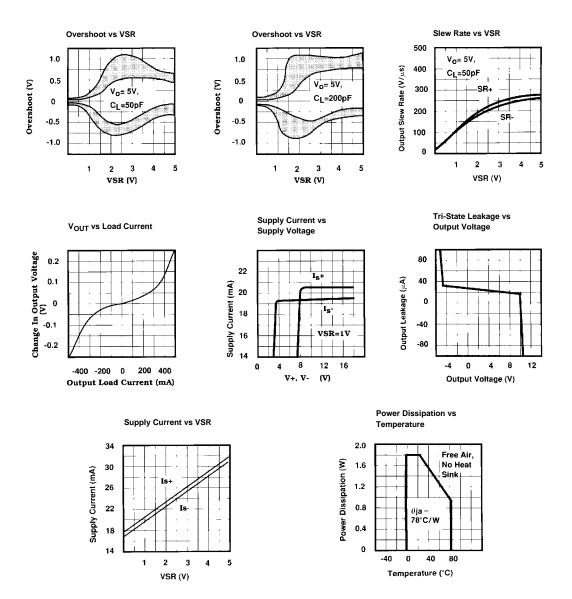

### **Typical Performance Curves**

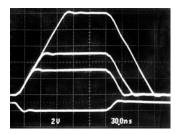

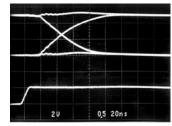

Family of output waveshapes. ECL, TTL, CMOS, HCMOS with C1 = 50pF, VSR = 1V.

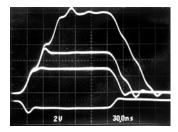

Family of output waveshapes. ECL, TTL, CMOS, HCMOS with C1 = 200pF, VSR = 1V.erting Gains

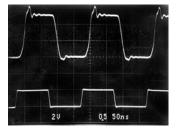

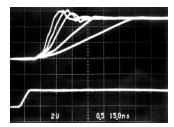

Output waveshapes with 5 MHz data rate. C1 = 50pF, VSR = 4V.

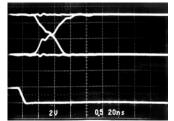

Family of output waveshapes. ECL, TTL, CMOS, HCMOS with C1 = 200pF, VSR = 1V, and overcompensated with 22pF from each drive pin to ground.

Family of output waveshapes from active H, L to high-impedance H, L.

Family of output waveshapes from high-impedance H, L to active H, L.

Family of + output edges, 0V to 5V for VSR = 0.5V, 1V, 2V, 3V, 5V.

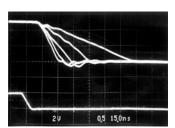

Family of—output edges, 5V to 0V or VSR = 0.5V, 1V, 2V, 3V, 5V.

### Typical Performance Curves (Continued)

### Applications Information

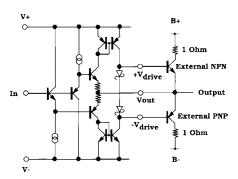

#### **Output Stage**

To meet the requirements of low output impedance, wide bandwidth, and large capacitive load driving capability, the EL2021 has a fairly exotic output stage. Figure 1 shows a simplified schematic of the circuit, only applicable in normal, low impedance mode. External transistors are used to handle the large load currents and peak power dissipations. Since there is no need for good AC crossover distortion performance in a pin driver, the output transistors are operated class C. That is, for small output currents, neither output transistor will conduct bias current, and when load currents do flow, one of the devices is off. This is accomplished by biasing the output transistors from Schottky

diodes D1 and D2. In operation, the diode forward voltage is about 0.4V, whereas the "on" output transistor will have a  $V_{\mbox{\footnotesize{BE}}}$  of 0.6V. This leaves only 0.2V across the "off" transistor's base-emitter junction, not nearly enough to cause bias currents to flow in it. Schottky diodes have a temperature drift similar to silicon transistors, so the class C bias maintains over temperature. One caution is that the diodes are in the IC package and are thermally separate from the transistors, so there can exist temperature differences between packages that can cause thermal runaway. Runaway is avoided as long as the external transistors are not hotter than the EL2021 package by more than 80°C. The only way runaway has been induced as of this writing is to use "freeze spray" on the IC package while the output transistors are very hot.

-----

FIGURE 1. SIMPLIFIED OUTPUT STAGE (NORMAL MODE)

This circuit allows the external transistors to run from B+ and B- supplies that are of less voltage than V+ and V- to conserve power. Reducing B± supplies also reduces dissipations in the output devices themselves. B+ is typically made K volts more than V<sub>CH</sub> and B- made K volts more negative than V<sub>Cl</sub> . Ideally K is made as small as possible to minimize output transistor dissipation, but two factors limit how small K can be. These factors are both related to the fact that transistors have two collector resistance numbers: "hard" and "soft" saturation resistance. As a transistor begins to saturate at high collector currents and small collectoremitter voltages, minority carriers begin to be generated from the base-collector junction. These carriers act as more collector dopant and actually reduce effective series collector resistance. At conditions of heavy saturation, the collector is flooded with minority carriers and exhibits minimum collector resistance. In this way, small geometry transistors like the 2N2222 and 2N2907 devices have excellent collector-emitter voltage drops at high currents, but are actually still in heavy saturation for 1V-2V drops. This "soft" saturation shows up as reduced beta at high currents and moderate V<sub>CF</sub>'s as well as very poor AC performance. A transistor may exhibit an ft of only 2MHz in soft saturation when, like the 2N2222, it gives 300MHz in non-saturated mode. The EL2021 requires the output transistors to have an ft of at least 200MHz to prevent degradation in overshoot, slew rate into heavy loads, and tolerance of heavy output capacitance. With a K of 3.2V and  $1\Omega$  collector resistors, almost all 2N2222 and 2N2907 devices perform well, but we have obtained devices from some vendors where the beta does indeed fall prematurely at reduced  $V_{\mbox{\scriptsize CE}}$  and high currents. It is important to characterize the external devices for the service that the EL2021 will be expected to provide.

The output stage of the EL2021 does not ring appreciably into a capacitive load in quiescent conditions, but it does ring while it slews. This is an unusual characteristic, but the output slews monotonically and the slew "ripple" does not cause problems in use. The slew ripple does cause a similar "ripple" in the overshoot-vs-VSR characteristic: the overshoot may decrease for slightly increasing VSR, then increase again for larger VSR's again. The overshoot-vs-VSR graphs presented in this data sheet thus reflect the

range of overshoot rather than one particular device's wavy curve.

The typical 2N2222 and 2N2907 will deliver 750mA into a short-circuit. This puts four watts of dissipation into the 2N2222 for  $V_{CH}$  = 5V. The npn can dissipate this power for a few tenths of a second as long as a metal-base TO-39 package is used. The small or non-metal-based packages have short thermal time constants and high thermal resistances, so they should withstand shorts for only a few milliseconds. The Sense Out signal should be used to control  $\overline{\text{OE}}$  or reduce  $V_{CH}$  and  $V_{CL}$  to relieve the output devices from overcurrent conditions.

Transistors such as the MJE200 and MJE210 have very much improved collector resistances and high-current beta compared to the 2N2222 and 2N2907. Their  $f_{\mbox{\scriptsize T}}$ 's are almost as good and sustain at higher currents, and high-current output accuracy will improve. They allow a K of 2V to reduce dissipations further, but short-circuit currents will be as much as two amperes! The geometries of these transistors are larger, and the added transistor capacitances will slow the maximum Slew Rates that the EL2021 can provide.

If transistors with ft's less than 200MHz are used, the EL2021 will need to be overcompensated. This is accomplished by connecting equal capacitors from the Drive pins to ground. These capacitors will range from 10pF to 50pF. The overcompensation will slow the maximum slew rate, but it will improve the overshoot and reactive load driving capability, and can be considered a useful technique.

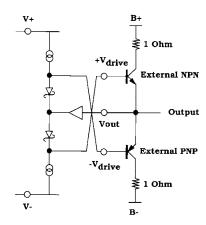

Figure 2 shows the equivalent output stage schematic when the circuit is in high-impedance mode ( $\overline{OE}$  = H). The external transistors have their base-emitter junctions each reverse-biased by a Schottky diode drop. A buffer amplifier copies the output voltage to give a bootstrapped bias for the Schottky stack. This scheme guarantees that the external transistors will be off for any output level, and the output leakage current is simply the bias current of the buffer.

The circuit works properly for AC signals up to 500V/µs. Above this slew rate, the buffer cannot keep up and the external transistors may turn on transiently. Because of the bootstrap action, the output capacitance is less than 10pF up to 10MHz of small-signal bandwidth and 300V/µs slew rate, increasing beyond these values. Adding overcompensation capacitors will degrade the slew rate that the output can withstand before current is drawn.

It is sometime necessary to provide a "snubber" network-a series R and C- to provide a local R.F. impedance for the buffer to look into.  $330\Omega$  and 56pF should serve. Also, it is well to provide some DC path to ground (47k for instance) to bias the output stage when no actual circuit is connected to the EL2021 in high-impedance mode.

FIGURE 2. SIMPLIFIED OUTPUT STAGE (HIGH-IMPEDANCE MODE)

#### **Power Supplies**

In typical operation, V+ and V- can be as much as  $\pm 15V$  and as little as  $V_{CH}$  +3V and  $V_{CL}$  -3V, respectively. When driving heavy output currents, however, it is wise to have 5V of headroom above  $V_{CH}$  and below  $V_{CL}$  to ensure no saturation of devices within the EL2021 and attendant waveshape distortions. Thus, for  $V_{CH}$  = 5V and  $V_{CL}$  = -2V, minimum operating voltages are +10, -7V. It is very important to bypass the supply terminals with low-inductance capacitors to ground, since the full base drive currents of the output transistors are derived from these supplies. Because the pulse currents can reach 60mA, the capacitors should be at least a microfarad; 4.7µF tantalum are ideal and require no small bypasses in parallel.

B+ and B- can be any voltage within V+ and V- and some amount previously discussed above V<sub>CH</sub> and below V<sub>CL</sub>. If V<sub>CH</sub> or V<sub>CL</sub> exceeds B+ or B-, very large internal fault currents can flow when the EL2021 attempts to bring an output transistor's base beyond the collector voltage. The bypassing care of the V± lines apply to the B± lines, as well as the fact that ampere currents can occur. Large (100µF–  $500\mu F$ ) capacitors should be used to bypass perhaps every tenth EL2021.

The  $V_{CH}$ ,  $V_{CL}$ , Data and  $\overline{OE}$  lines should be driven locally so as to not pick up magnetic interference from the output. The inductance of interconnects to these lines can allow coupling to cause waveshape anomalies or even oscillations. If long lines are unavoidable, local 1k resistors or 50pF–100pF capacitors to ground can also serve the purpose.

#### Data Pin

The slew rate of the input to the Data pin should be kept less than 1000V/µs. Some feedthrough can occur for large Slew Rates which will distort the output waveshape. A 1k–2k resistor in series with the data pin will reduce feedthrough.

#### **Current Sense**

The output current is sensed by comparing the voltage dropped across the external shunt resistors to an internal 0.45V reference. The center of the trip level is adjusted for the particular output transistor betas listed in the data specifications. Transistors with less beta at high currents will cause the sense comparators to trip at slightly higher output currents. The  $1\Omega$  shunt resistors should be non-inductive. The family of wirewound resistors called "non-inductive" are too inductive for these shunts.

The response of the Sense Out can be thought of as slow attack and fast decay. A continuous overcurrent condition must last for at least 2 $\mu$ s before Sense Out will go high, but will clear to low only about 200ns after the overcurrent is withdrawn. This allows transient currents due to slewing capacitive load to not generate a flag. On the other hand, the output transistors will not be damaged with only a 2 $\mu$ s system reaction time to a short-circuit.

#### **Construction Practices**

The major cautions in connecting to the EL2021 involve magnetic rather than capacitive parasitic concerns. The circuits can output as much as 100A/µs. Even with normal Slew Rates and moderately large capacitive loads, the dl/dT can cause magnetic fields in harmless looking wires to fill adjacent lines with noise, and sometimes ringing or even sustained feedback. Thus, rules for wiring the EL2021 are:

- Keep leads short and large. Short wires are less inductive, as are wires with large surface area. The large surface area also reduces skin resistance at high frequencies, important at high currents (at 100MHz, current penetrates only a few microns in metals).

- Use a ground plane. Due to inductance and skin effect, "ground" voltages will be different only inches apart on a copper ground plane. Individual wires do not create ground at high frequencies. The common "star" ground is a very bad idea for high-current and high-frequency circuits.

- Dress all wires against the ground plane. The magnetic fields that the wires would have generated will be intercepted by the ground plane and absorbed, thus reducing the wire's effective inductance. The capacitance added by this method is not important to EL2021 operation.

- 4. The external transistors should have short interconnects to the EL2021, the collector shunt resistors, and the bypass capacitors. As previously stated, the shunt resistors must not be wire wound because of their inductance.

- 5. The bypass capacitors should have low series resistance and inductance, but should not have a high Q. This may seem contradictory, but a 4.7μF tantalum capacitor seems to work the best. An electrolytic capacitor should be added to help bolster the supply levels in the 0.1μs–1μs after a transition. No small capacitors are needed in parallel with the tantalums. The bypasses' ground returns

-----

are best connected to the area of ground inside the package outline to reduce the circulating current path length, if possible.

#### Using the EL2021 without External Transistors

By connecting both drive pins to the output pin, the EL2021 can be used as a stand-alone driver, not requiring the external transistors. The EL2021 is good for more than

50mA in this mode. The output impedance rises to  $12\Omega$ , however, and the current sense and high-impedance mode are not available. The ripple seen in slew edges using the external transistors is largely absent from the stand-alone waveshapes; and overshoot is markedly improved at VSR > 1V, especially with large capacitive loads.

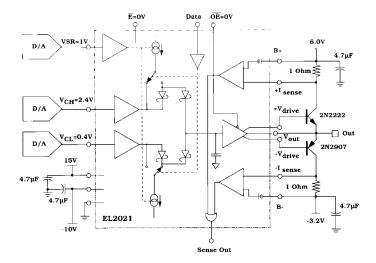

### **Typical Applications**

100V/µS HIGH-CURRENT PIN DRIVER OUTPUTTING TTL LEVELS

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

2 ---