#### Features

- Complete video level restoration system

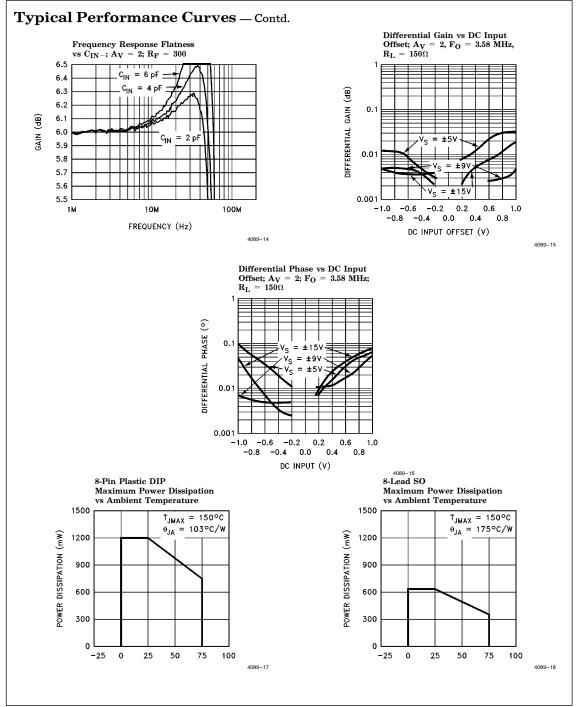

- 0.02% differential gain and 0.05° differential phase accuracy at NTSC

- 60 MHz bandwidth

- 0.1 dB flatness to 10 MHz

- $V_S = \pm 5V \text{ to } \pm 15V$

- TTL/CMOS hold signal

#### **Applications**

- Input amplifier in video equipment

- Restoration amplifier in video mixers

#### **Ordering Information**

| Part No. | Temp. Range  |             |         |  |  |  |

|----------|--------------|-------------|---------|--|--|--|

| EL4089CN | 0°C to +75°C | 8-Pin P-DIP | MDP0031 |  |  |  |

| EL4089CS | 0°C to +75°C | 8-Lead SO   | MDP0027 |  |  |  |

#### General Description

The EL4089C is an 8-pin complete DC-restored monolithic video amplifier sub-system. It contains a high quality video amplifier and a nulling, sample-and-hold amplifier specifically designed to stabilize video performance.

When the HOLD logic input is set to a TTL/CMOS logic 0, the sample- and-hold amplifier can be used to null the DC offset of the video amplifer.

When the HOLD input goes to a TTL/CMOS logic l, the correcting voltage is stored on the video amplifier's input coupling capacitor. The correction voltage can be further corrected as need be, on each video line.

The video amplifier is optimized for video performance and low power. Its current feedback design allows the user to maintain essentially the same bandwidth over a gain range of nearly 10:1. The amplifier drives back-terminated 75 $\Omega$  lines.

The EL4089C is fabricated in Elantec's proprietary Complementary Bipolar process which produces NPN and PNP transistors with equivalent AC and DC performance. The EL4089C is specified for operation over  $0^{\circ}$ C to  $+75^{\circ}$ C temperature range.

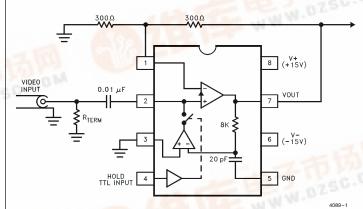

#### **Connection Diagram**

DC restoring amplifier with a gain of 2, restoring to ground.

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a "controlled document". Current revisions, if any, to these specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 1993 Elantec, Inc.

January 1996 Rev

# TD is 3.5in

## EL4089C

### DC Restored Video Amplifier

#### Absolute Maximum Ratings $(T_A = 25^{\circ}C)$

$\begin{array}{lll} \text{Operating Ambient} & & & & \\ \text{Temperature Range} & & 0^{\circ}\text{C to} + 75^{\circ}\text{C} \\ \text{Operating Junction Temperature} & & & \\ \text{Plastic DIP or SOL} & & 150^{\circ}\text{C} \\ \text{Storage Temperature Range} & & -65^{\circ}\text{C to} + 150^{\circ}\text{C} \\ \end{array}$

#### Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore  $T_J = T_C = T_A$ .

| Test Level | Test Procedure                                                                                                 |

|------------|----------------------------------------------------------------------------------------------------------------|

| I          | 100% production tested and QA sample tested per QA test plan QCX0002.                                          |

| II         | $100\%$ production tested at $T_{ m A}=25^{\circ}{ m C}$ and QA sample tested at $T_{ m A}=25^{\circ}{ m C}$ , |

|            | $T_{ m MAX}$ and $T_{ m MIN}$ per QA test plan QCX0002.                                                        |

| III        | QA sample tested per QA test plan QCX0002.                                                                     |

| IV         | Parameter is guaranteed (but not tested) by Design and Characterization Data.                                  |

| v          | Parameter is typical value at $T_A = 25^{\circ}C$ for information purposes only.                               |

|            |                                                                                                                |

#### Open Loop DC Electrical Characteristics

Provisional Supplies at  $\pm 15$ V, Load = 1 k $\Omega$ ;  $T_A = +25$ °C

| Parameter              | Description                                      | Temp   | Min | Тур | Max | Test<br>Level | Units              |

|------------------------|--------------------------------------------------|--------|-----|-----|-----|---------------|--------------------|

| Amplifier Sec          | Amplifier Section (HOLD = $5V$ )                 |        |     |     |     |               |                    |

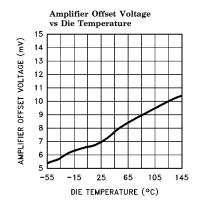

| v <sub>os</sub>        | Input Offset Voltage                             | + 25°C |     | 12  | 25  | II            | mV                 |

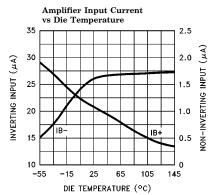

| IP+                    | IN+ Input Bias Current                           | + 25°C |     | 1   | 5   | II            | μΑ                 |

| Ib-                    | IN — Input Bias Current                          | + 25°C |     | 18  | 150 | II            | μΑ                 |

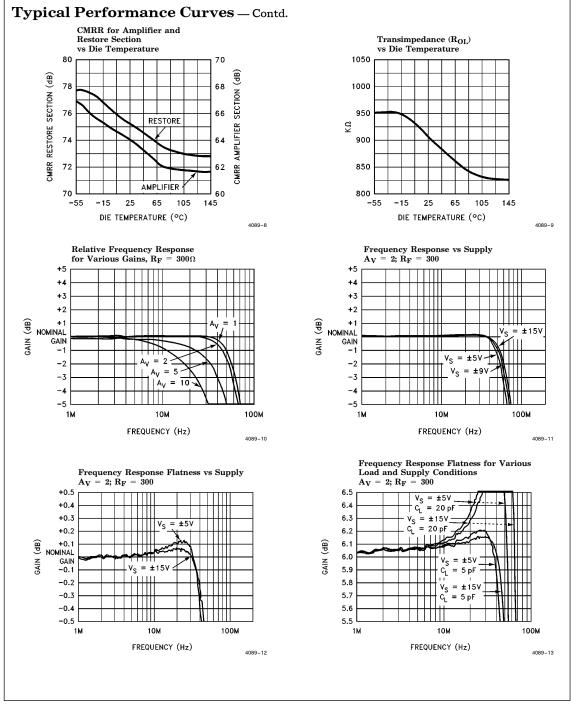

| $R_{ m OL}$            | Transimpedance (Note 1)                          | + 25°C | 180 | 800 |     | II            | $\mathbf{k}\Omega$ |

| $R_{IN-}$              | IN – Resistance                                  | + 25°C |     | 20  |     | v             | Ω                  |

| CMRR                   | Common Mode Rejection Ratio<br>(Note 2)          | + 25°C | 44  | 60  |     | II            | dB                 |

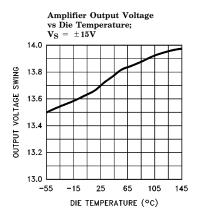

| v <sub>o</sub>         | Output Voltage Swing                             | + 25°C | ±12 | ±13 |     | II            | V                  |

| I <sub>SC</sub>        | Short Circuit Current (IN + Only Driven to 0.5V) | + 25°C | 45  | 100 |     | II            | mA                 |

| Restore Section        | on                                               |        |     |     |     |               |                    |

| V <sub>OS</sub> , Comp | Composite Input Offset Voltage<br>(Note 3)       | + 25°C |     | 3   | 7   | II            | mV                 |

| Ib+,r                  | Restore In+ Input Bias Current                   | + 25°C |     | 3   | 12  | II            | μΑ                 |

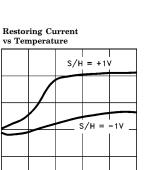

| I <sub>OUT</sub>       | Restoring Current Available                      | + 25°C | 180 | 300 |     | II            | μΑ                 |

| CMRR                   | Common Mode Rejection Ratio<br>(Note 2)          | + 25°C | 60  | 70  |     | II            | dB                 |

#### Open Loop DC Electrical Characteristics - Contd.

Provisional Supplies at  $\pm 15$ V, Load =  $1 \text{ k}\Omega$ ;  $T_A = +25$ °C

| Parameter                   | Description                           | Temp   | Min | Тур | Max  | Test<br>Level | Units |

|-----------------------------|---------------------------------------|--------|-----|-----|------|---------------|-------|

| Restore Section             | —Contd.                               |        |     |     |      |               | 1     |

| PSRR                        | Power Supply Rejection Ratio (Note 4) | + 25°C | 60  | 90  |      | II            | dB    |

| V <sub>THRESHOLD</sub>      | HOLD Logic Threshold                  | + 25°C | 0.8 |     | 2.0  | II            | v     |

| I <sub>IH</sub> , Hold      | HOLD Input Current @ Logic High       | + 25°C |     | 1   | 5    | II            | μΑ    |

| ${ m I_{IL}}$ , ${ m Hold}$ | HOLD Input Current @ Logic Low        | + 25°C |     | 5   | 15   | II            | μΑ    |

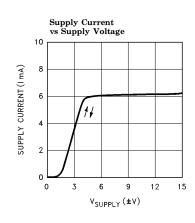

| Supply Current              | t                                     |        |     |     |      |               |       |

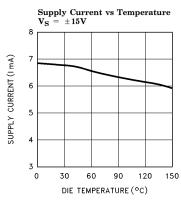

| Isy, Hold                   | Supply Current (HOLD = 5V)            | + 25°C | 4.8 | 6.0 | 9.0  | II            | mA    |

| Isy, Sampling               | Supply Current (HOLD = 0V)            | + 25°C | 5.0 | 6.5 | 11.0 | II            | mA    |

#### **Closed Loop AC Electrical Characteristics**

Provisional Supplies at  $\pm 15V$ , Load  $= 150\Omega$  and 15 pF.  $R_f$  and  $R_g = 300\Omega$ ;  $A_V = 2$ ,  $T_A = 25^{\circ}C$ . (See Note 7 about Test Fixture)

| Parameter       | Description                                           | g                                            | Min | Typ          | Max | Test<br>Level | Units      |

|-----------------|-------------------------------------------------------|----------------------------------------------|-----|--------------|-----|---------------|------------|

| Amplifier Sec   | tion                                                  |                                              |     |              |     |               |            |

| SR              | Slew Rate (Note 5)                                    |                                              |     | 500          |     | V             | V/μs       |

| SR              | Slew Rate with $\pm 5V$ Supplies (Note 5)             |                                              |     | 275          |     | v             | V/μs       |

| BW              | Bandwidth $\pm5	ext{V}$ Supplies                      | −3 dB<br>−3 dB                               |     | 60<br>55     |     | v<br>v        | MHz<br>MHz |

| BW              | Bandwidth<br>±5V Supplies                             | $\pm 0.1 \text{ dB}$<br>$\pm 0.1 \text{ dB}$ |     | 25<br>23     |     | v<br>v        | MHz<br>MHz |

| dG              | Differential Gain<br>at 3.58 MHz (Note 6)             | $V_{S} = \pm 15V$ $V_{S} = \pm 5V$           |     | 0.02<br>0.03 |     | v<br>v        | %<br>%     |

| dPh             | Differential Phase<br>at 3.58 MHz (Note 6)            | $V_{S} = \pm 15V$ $V_{S} = \pm 5V$           |     | 0.05<br>0.06 |     | v<br>v        | 0          |

| Restore Section |                                                       |                                              |     |              |     |               |            |

| SR              | Restore Amplifier Slew Rate<br>(Test Circuit) 20%–80% |                                              |     | 25           |     | v             | V/μs       |

| $T_{ m HE}$     | Time to Enable Hold                                   |                                              |     | 25           |     | v             | ns         |

| $	au_{ m HD}$   | Time to Disable Hold                                  |                                              |     | 40           |     | V             | ns         |

Note 1: For current feedback amplifiers,  $A_{\mbox{\scriptsize VOL}} = \, R_{\mbox{\scriptsize OL}}/R_{\mbox{\scriptsize IN}\,-}.$

Note 2:  $V_{CM} = \pm 10V$  for  $V_S = \pm 15V$ .

Note 3: Measured from S/H Input to amplifier output, while restoring.

Note 4:  $V_{OS}$  is measured at  $V_S=\pm 4.5V$  and  $V_S=\pm 16V$ , both supplies are changed simultaneously. Note 5: SR measured at 20% to 80% of a 4V pk-pk square wave.

Note 6: DC offset from -0.714V through +0.714V, ac amplitude is 286 mVp-p, equivalent to 40 ire.

Note 7: Test fixture was designed to minimize capacitance at the IN - input. A "good" fixture should have less than 2 pF of stray capacitance to ground at this very sensitive pin. See application notes for further details.

## EL4089C

500

300

200

100

0

RESTORE (MA) 400

## DC Restored Video Amplifier

120

90

DIE TEMPERATURE (°C)

150

4089-4

4089-7

## EL4089C

### DC Restored Video Amplifier

#### **Typical Application**

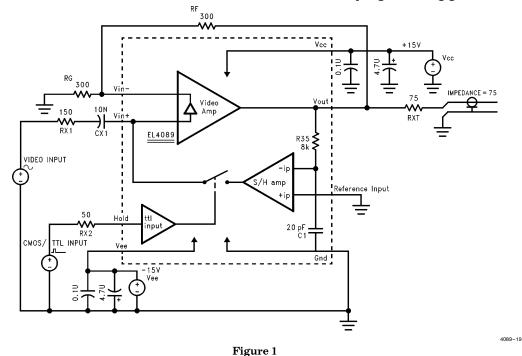

The EL4089 can be used to DC-restore a video waveform (see Fig. 1). The above circuit forces the cable driving video amplifier's output to ground when the HOLD pin is at a logic low.

The "correction voltage" is stored on capacitor CX1, an external ceramic capacitor. The capacitor value is chosen from the system requirements. The typical input bias current to the video amplifier is 1  $\mu$ A, so for a 62  $\mu$ s hold time, and a 0.01  $\mu$ F capacitor, the output voltage drift is 6.2 mV in one line.

The S/H amplifier can provide a typical current of 300  $\mu$ A to charge capacitor CX1, so with a 1.2  $\mu$ s sampling time, the output can be corrected by 36 mV in each line.

Using a smaller value of CX1 increases both the voltage that can be corrected, and the drift while being held, likewise, using a larger value of CX1, reduces the voltages.

The RX1 resistor is in the circuit purely to simulate some external source impedance, and is not needed as a real component. Likewise for RX2. The  $75\Omega$  back terminating resistor RXT is recommended when driving  $75\Omega$  cables.

The board layout should have a ground plane underneath the EL4089, with the ground plane cut away from the vicinity of the  $V_{\rm IN}-$  pin, (pin 1). This helps to minimize the stray capacitance on pin 1.

Power supply bypassing is important, and a 0.1  $\mu F$  ceramic capacitor, from each power pin to ground, placed very close to the power pins, together with a 4.7  $\mu F$  tantalum bead capacitor, is recommended.

When both digital and Analog grounds are on the same board, the EL4089 should be on the Analog ground. The digital ground can be connected to the Analog ground through a  $100\Omega-300\Omega$  resistor, near the EL4089. This allows the digital signal a return path, while preventing the digital noise from corrupting the analog ground.

, 41

#### **Table of Charge Storage Capacitor vs Droop Charging Rates**

| Cap Value<br>nF | Droop in 60 μs<br>mV | Charge in 1.2 μs<br>mV | Charge in 4 μs<br>mV |  |  |

|-----------------|----------------------|------------------------|----------------------|--|--|

| 10              | 6                    | 36                     | 120                  |  |  |

| 33              | 1.8                  | 11                     | 36                   |  |  |

| 100             | 0.6                  | 3.6                    | 12                   |  |  |

Basic formulae are: V (droop) = Ib + \* (Line time - Sample time) / Capacitor and V (charge) =  $I_{OUT}$  \* Sample time / Capacitor

For best results the source impedance should be kept low, using a buffer for example.

Because the S/H effectively shorts the input signal during Sample, the input should not be sampled during active video. Typically the sample is made during the back porch period of horizontal blanking. For this reason color composite signals, which have color burst on the back porch, can not be passed. See EL2090 or EL4093 for this application.

#### General Disclaimer

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

Elantec, Inc. 1996 Tarob Court Milpitas, CA 95035

Telephone: (408) 945-1323 (800) 333-6314

Fax: (408) 945-9305 European Office: 44-71-482-4596

#### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. products in Life Support Systems are requested to contact Elantec, Inc. factory head quarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.