Data Sheet July 28, 2005 FN6167.0

# High Voltage TFT-LCD Logic Driver

The EL5000A is high voltage TFT-LCD logic driver with +40V and -30V output swing capability. Manufactured using the Intersil proprietary monolithic high voltage bipolar process, it is capable of delivering 100mA output peak current into 5nF of capacitive load. To simplify external circuitry, the EL5000A integrates additional logic circuits.

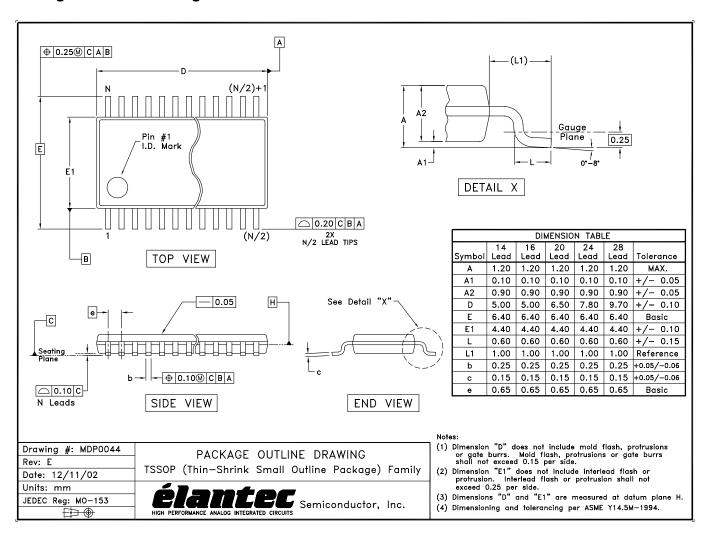

The EL5000A can operate on 3.3V logic supply and high voltage -30V to +40V output supplies. The EL5000A is available in TSSOP-16 package. It is specified for operation over the -20°C to +85°C extended temperature range.

# **Ordering Information**

| PART<br>NUMBER                | PACKAGE                   | TAPE &<br>REEL | PKG. DWG. # |

|-------------------------------|---------------------------|----------------|-------------|

| EL5000AER                     | 16-Pin TSSOP              | -              | MDP0044     |

| EL5000AER-T7                  | 16-Pin TSSOP              | 7"             | MDP0044     |

| EL5000AER-T13                 | 16-Pin TSSOP              | 13"            | MDP0044     |

| EL5000AERZ<br>(See Note)      | 16-Pin TSSOP<br>(Pb-Free) | -              | MDP0044     |

| EL5000AERZ-T7<br>(See Note)   | 16-Pin TSSOP<br>(Pb-Free) | 7"             | MDP0044     |

| EL5000AERZ-<br>T13 (See Note) | 16-Pin TSSOP<br>(Pb-Free) | 13"            | MDP0044     |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- · 3.3V logic supply

- 40V V<sub>ON</sub> output high level

- -30V V<sub>OFF</sub> output low level

- 166kHz input logic frequency

- 100mA output peak current

- · 10mA output continuous current

- · TTL-compatible logic input

- Pb-free plus anneal available (RoHS compliant)

# **Applications**

TFT-LCD panels

### **Pinout**

EL5000A (16-PIN TSSOP) TOP VIEW

### EL5000A

# **Absolute Maximum Ratings** $(T_A = 25^{\circ}C)$

| V <sub>DD</sub>                                                                                                    | I <sub>OUT</sub> (peak)                               |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| V <sub>ON</sub>                                                                                                    | I <sub>OUT</sub> (continuos), CKV, CKVB, or STVP 30mA |

| V <sub>OFF</sub>                                                                                                   | I <sub>OUT</sub> (continuous, total)                  |

| V <sub>CL</sub>                                                                                                    | T <sub>AMBIENT</sub> 20°C to +85°C                    |

| V <sub>CKV</sub> , V <sub>CKVB</sub> , V <sub>STVP</sub> ,                                                         | T <sub>JUNCTION</sub> 20°C to +150°C                  |

| V <sub>CKVCS</sub> , V <sub>CKVBCS</sub> , V <sub>STVP</sub> V <sub>ON</sub> + 1 diode/V <sub>OFF</sub> - 1 diode  | T <sub>STORAGE</sub> 65°C to +150°C                   |

| V <sub>CPV</sub> , V <sub>OE</sub> , V <sub>STV</sub> , V <sub>OECON</sub> V <sub>DD</sub> + 1 diode/GND - 1 diode | P <sub>DISSIPATION</sub> See Curves                   |

| V <sub>DISH</sub> · · · · · · · · GND + 1 diode/V <sub>OFF</sub> - 1 diode                                         | Maximum Power Dissipation See Curves                  |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# $\textbf{Electrical Specifications} \qquad \text{$V_{ON}$ = 20V, $V_{OFF}$ = -14V, $V_{DD}$ = 3.3V, 4.7nF Load on STV, CKV, CKVB, unless otherwise specified.}$

| PARAMETER            | DESCRIPTION                     | CONDITION                                   | MIN   | TYP   | MAX   | UNIT |

|----------------------|---------------------------------|---------------------------------------------|-------|-------|-------|------|

| $I_{VDD}$            | V <sub>DD</sub> Supply Current  | All inputs low                              |       | 1.1   |       | mA   |

|                      |                                 | CPV = 3.1V, other inputs low                | 0.7   | 1.5   | 2.5   | mA   |

| I <sub>VON</sub>     | V <sub>ON</sub> Supply Current  | All inputs low                              |       | 0.25  |       | mA   |

|                      |                                 | CPV = 3.1V, other inputs low                | 0.2   | 0.45  | 0.9   | mA   |

| I <sub>VOFF</sub>    | V <sub>OFF</sub> Supply Current | All inputs low                              |       | 0.25  |       | mA   |

|                      |                                 | CPV = 3.1V, other inputs low                | -1.25 | -0.7  | -0.30 | mA   |

| I <sub>STV</sub>     | STV Input Current               | STV = 3.1V                                  | 25    | 130   | 180   | μA   |

|                      |                                 | STV = 0.2V                                  | -1    | 0     | 1     | μΑ   |

| I <sub>CPV</sub>     | CPV Input Current               | CPV = 3.1V                                  | 20    | 60    | 90    | μA   |

|                      |                                 | CPV = 0.2V                                  | -1    | 0     | 1     | μA   |

| l <sub>OE</sub>      | OE Input Current                | OE = 0.2V                                   | -1    | 0     | 1     | μΑ   |

|                      |                                 | OE = 3.1V, OECON = 0.2V                     | 200   | 450   | 700   | μA   |

|                      |                                 | OE = 3.1V, OECON = 3.1V                     | -1    | 0     | 1     | μΑ   |

| loecon               | OECON Input Current             | OECON - 0.2V, OE = 3.1V                     | -40   | -25   | -5    | μΑ   |

|                      |                                 | OECON - 0.2V, OE = 0.2V                     | -1    | 0     | 1     | μA   |

| V <sub>CKV</sub> +   | CKV Positive Output Swing       | V <sub>ON</sub> = +20V, 1mA output current  | 19.1  | 19.3  | 19.5  | V    |

| V <sub>CKV</sub>     | CKV Negative Output Swing       | V <sub>OFF</sub> = -14V, 1mA output current | -13.1 | -13.3 | -13.5 | V    |

| V <sub>CKVB</sub> +  | CKVB Positive Output Swing      | V <sub>ON</sub> = +20V, 1mA output current  | 19.1  | 19.3  | 19.5  | V    |

| V <sub>CKVB</sub>    | CKVB Negative Output Swing      | V <sub>OFF</sub> = -14V, 1mA output current | -13.1 | -13.3 | -13.5 | V    |

| V <sub>STVP</sub> +  | STVP Positive Output Swing      | V <sub>ON</sub> = +20V, 1mA output current  | 19.0  | 19.2  | 19.4  | V    |

| V <sub>STVP</sub>    | STVP Negative Output Swing      | V <sub>OFF</sub> = -14V, 1mA output current | -13.1 | -13.3 | -13.5 | V    |

| R <sub>IN</sub>      | CPV, OE, STV Input Resistance   |                                             |       | 3     |       | kΩ   |

| C <sub>IN</sub>      | CPV, OE, STV Input Capacitance  |                                             |       | 1.5   |       | pF   |

| T <sub>R</sub> -CKV  | CKV Rise Time                   |                                             | 0.3   | 0.5   | 0.7   | μs   |

| T <sub>F</sub> -CKV  | CKV Fall Time                   |                                             | 0.5   | 0.75  | 1     | μs   |

| T <sub>R</sub> -CKVB | CKVB Rise Time                  |                                             | 0.3   | 0.5   | 0.7   | μs   |

| T <sub>F</sub> -CKVB | CKVB Fall Time                  |                                             | 0.5   | 0.75  | 1     | μs   |

| T <sub>R</sub> -STVP | STVP Rise Time                  |                                             | 1.2   | 1.6   | 2.4   | μs   |

| T <sub>F</sub> -STVP | STVP Fall Time                  |                                             | 1.2   | 1.6   | 2.4   | μs   |

$\textbf{Electrical Specifications} \qquad \textit{V}_{ON} = 20 \textit{V}, \ \textit{V}_{OFF} = -14 \textit{V}, \ \textit{V}_{DD} = 3.3 \textit{V}, \ 4.7 \textit{nF} \ \textit{Load on STV}, \ \textit{CKV}, \ \textit{CKVB}, \ \textit{unless otherwise specified}. \ \textbf{(Continued)}$

| PARAMETER                | DESCRIPTION                     | CONDITION | MIN | TYP  | MAX | UNIT |

|--------------------------|---------------------------------|-----------|-----|------|-----|------|

| T <sub>D</sub> -CKV+     | CKV Rising Edge Delay Time      |           | 0.5 | 0.9  | 1.3 | μs   |

| T <sub>D</sub> -CKV-     | CKV Falling Edge Delay Time     |           | 0.7 | 1.1  | 1.5 | μs   |

| T <sub>D</sub> -CKVB+    | CKVB Rising Edge Delay Time     |           | 0.5 | 0.9  | 1.3 | μs   |

| T <sub>D</sub> -CKVB-    | CKVB Falling Edge Delay Time    |           | 0.7 | 1.1  | 1.5 | μs   |

| T <sub>D</sub> -STVP+    | STVP Rising Edge Delay Time     |           | 1.3 | 1.75 | 2.2 | μs   |

| T <sub>D</sub> -STVP-    | STVP Falling Edge Delay Time    |           | 1.2 | 1.7  | 2   | μs   |

| T <sub>D</sub> -CKV_CS+  | CKV_CS Rising Edge Delay Time   |           | 1.6 | 2.3  | 2.9 | μs   |

| T <sub>D</sub> -CKV_CS-  | CKV_CS Falling Edge Delay Time  |           | 3.4 | 4.1  | 4.8 | μs   |

| T <sub>D</sub> -CKVB_CS+ | CKVB_CS Rising Edge Delay Time  |           | 1.6 | 2.3  | 2.9 | μs   |

| T <sub>D</sub> -CKVB_CS- | CKVB_CS Falling Edge Delay Time |           | 3.4 | 4.1  | 4.8 | μs   |

# **Typical Performance Curves**

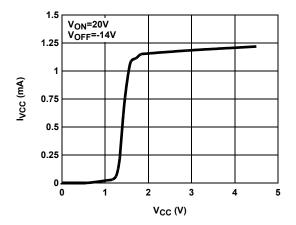

FIGURE 1.  $V_{SS}$  SUPPLY CURRENT vs  $V_{CC}$

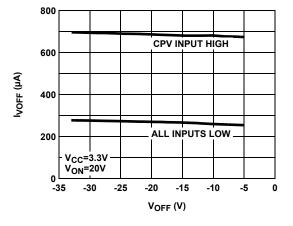

FIGURE 3.  $V_{\mbox{OFF}}$  DC SUPPLY CURRENT vs  $V_{\mbox{OFF}}$

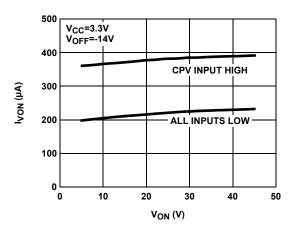

FIGURE 2. VON DC SUPPLY CURRENT vs VON

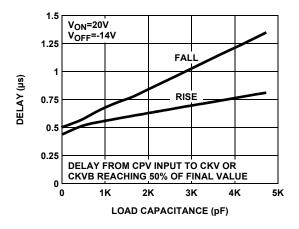

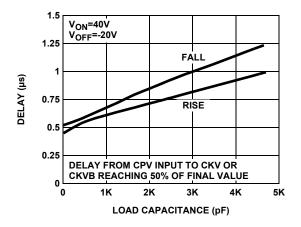

FIGURE 4. CLOCK DELAY vs LOAD CAPACITOR

## Typical Performance Curves (Continued)

FIGURE 5. CLOCK DELAY vs LOAD CAPACITOR

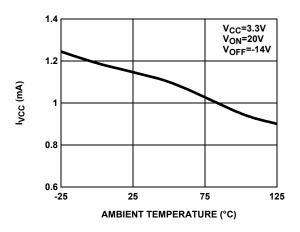

FIGURE 7. V<sub>CC</sub> SUPPLY CURRENT vs TEMPERATURE

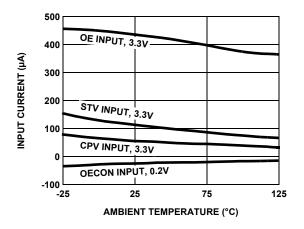

FIGURE 9. INPUT BIAS CURRENTS vs TEMPERATURE

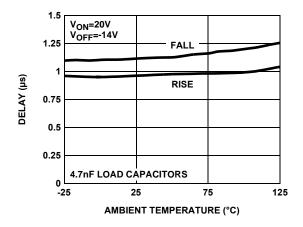

FIGURE 6. CLOCK DELAY vs TEMPERATURE

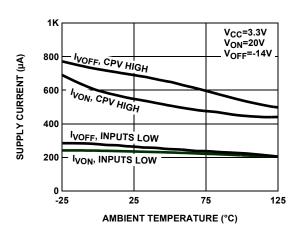

FIGURE 8. DC SUPPLY CURRENTS vs TEMPERATURE

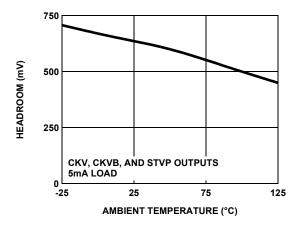

FIGURE 10. OUTPUT SWING HEADROOM vs TEMPERATURE

### Typical Performance Curves (Continued)

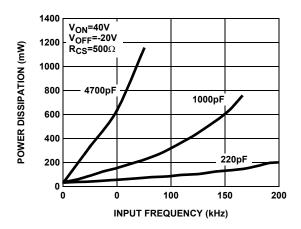

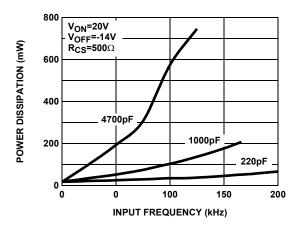

FIGURE 11. POWER CONSUMPTION VS FREQUENCY AND LOAD

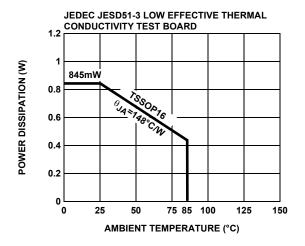

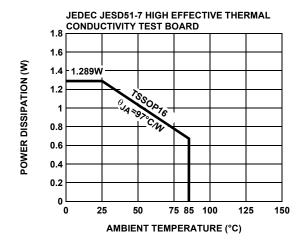

FIGURE 13. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

FIGURE 12. POWER CONSUMPTION VS FREQUENCY AND LOAD

FIGURE 14. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

Engle?

# EL5000A

# Pin Descriptions

| PIN NUMBER | PIN NAME | PIN FUNCTION                                         |  |

|------------|----------|------------------------------------------------------|--|

| 1          | VON      | Positive supply                                      |  |

| 2          | CKV      | High voltage output, scan clock out                  |  |

| 3          | CKVCS    | Discharge switch input, CKV charge share             |  |

| 4          | NC       | No connect                                           |  |

| 5          | CKVBCS   | Discharge switch input, CKVB charge share            |  |

| 6          | CKVB     | High voltage output, scan clock even                 |  |

| 7          | STVP     | High voltage output, scan start pulse                |  |

| 8          | VOFF     | Negative supply                                      |  |

| 9          | GND      | Ground                                               |  |

| 10         | CPV      | H sync timing, H sync clock 1                        |  |

| 11         | OE       | Writing timing, H sync clock 2                       |  |

| 12         | VTS      | V sync timing, V sync                                |  |

| 13         | GND      | Ground, logic return                                 |  |

| 14         | OECON    | OE disable input, OE blank                           |  |

| 15         | DISH     | Discharge function input, V <sub>OFF</sub> discharge |  |

| 16         | VDD      | Logic power supply                                   |  |

.

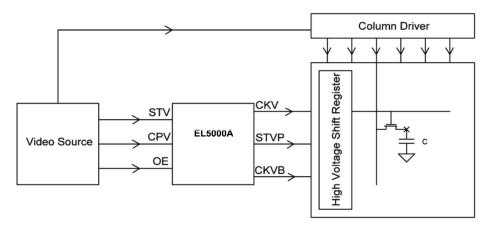

FIGURE 15. EL5000A SYSTEM BLOCK DIAGRAM

# Application Information

### **General Description**

The EL5000A is a high performance 70V TFT-LCD row driver. It level shifts TTL level timing signals from the video source into 70V peak to peak output voltage. Its output is capable of delivering 100mA peak current into 1nF of capacitive load. It also incorporates logic to control the output timings. The logic timing control circuit is powered from 3.3V supply. Figure 15 shows the system block diagram.

### Input Signals

The device performs beside of level transformation also logic operation between the input signals:

- STV Vertical Sync Timing signal, frequency range around 60Hz

- CPV Horizontal Sync Timing signal, frequency range up to 166kHz

- OE Output Enable Write Signal, frequency range up to 166kHz

### **Output Signals**

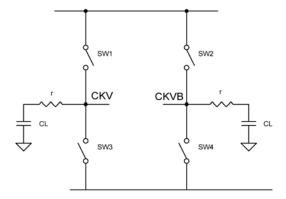

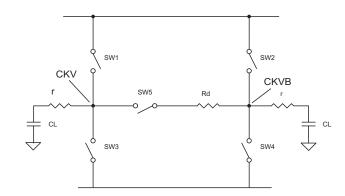

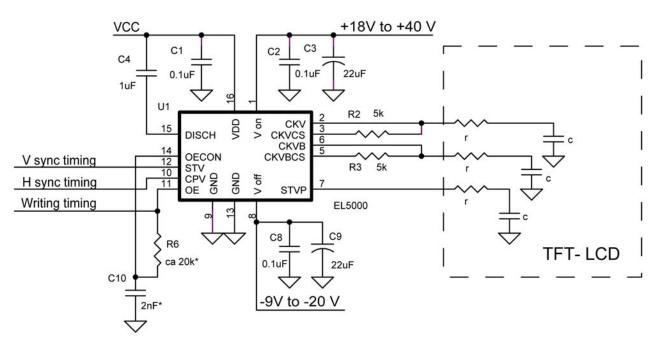

The output signals, CKV and CKVB are generated by EL5000A internal switches. Figure 16 depicts the simplified schematic of the output stage and interface.

FIGURE 16. SIMPLIFIED SCHEMATIC OF OUTPUT STAGE

$C_L$  capacitors model the capacitive loading appeared at the inputs of the TFT-LCD panel for the CKV and the CKVB signals. The  $C_L$  is typically between 1nF and 5nF.

In addition to switches SW1, SW2, SW3, and SW4, a fifth switch is added to reduce the power dissipation and shape the output waveform. Figure 17 shows the location of the additional SW5 switch.

FIGURE 17. SW5 SWITCH LOCATION

In reality, each switch consists of two such switches, one for the positive discharge and one for the negative discharge, see Figure 18.

FIGURE 18. BI-DIRECTIONAL SWITCHES

Due to the actual solid-state construction of the switches, the capacitors  $C_L$  does not get discharged entirely. The amount of left over charges depends on the value of the voltages of  $V_{ON}$  and  $V_{OFF}$  on the capacitors.

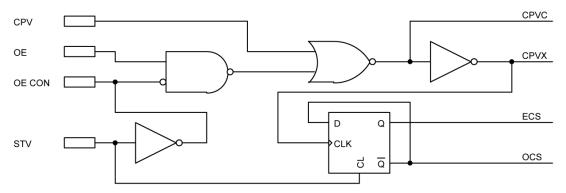

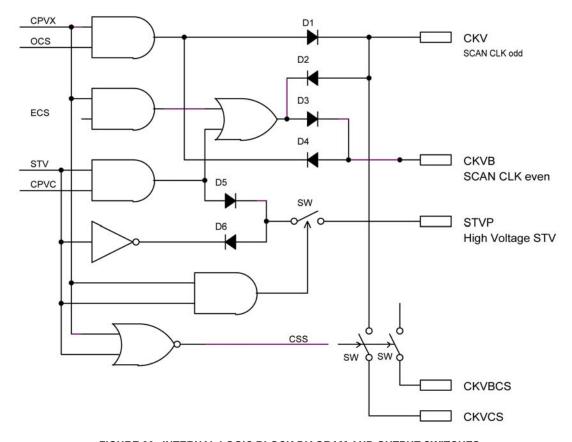

## Internal Logic Block Diagram

Figures 19 and 20 show the internal block diagram. In order to reduce power dissipation, most of the logic circuitry is

powered from 3.3 V logic supply. The output of the 3.3 V logic is level-shifted to drive the output switches.

FIGURE 19. INTERNAL LOGIC BLOCK DIAGRAM

FIGURE 20. INTERNAL LOGIC BLOCK DIAGRAM AND OUTPUT SWITCHES

### **Output Waveforms**

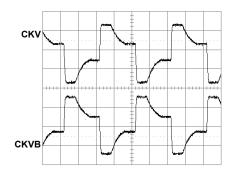

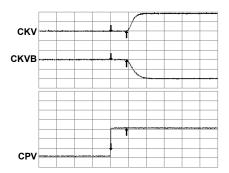

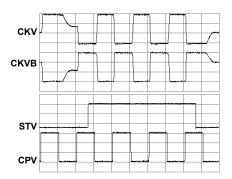

Figure 21 shows a typical CKV and CKVB output waveforms. The output droop rate depends on the external discharge resistor value and the output capacitor load.

FIGURE 21. CKV AND CKVB OUTPUT WAVEFORMS

FIGURE 22. CPV TO CKV/CKVB DELAY

Figure 22 shows the delay time between the incoming horizontal sync timing pulse CPV and the generated output pulses.  $\Delta t$  is dependent mainly on the value of  $C_L$ . Figure 23 shows the effect of STV.

FIGURE 23. EFFECT OF STV

# **Auxiliary Functions**

DISH: It discharges V<sub>OFF</sub> when the logic power voltage level drops out, when 'DISH' is < -0.6V (V<sub>CC</sub> system power turns off), V<sub>OFF</sub> is connected to ground level by 1k $\Omega$ .

OECON: It provides continuos polarity changes to the TFT-LCD panel during the vertical blanking.

FIGURE 24. TYPICAL APPLICATION CIRCUIT

### **Power Dissipation**

The dissipated power in  $R_3$  and  $R_6$  could calculated as follows:

We assume that:

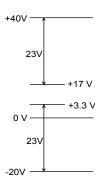

- V<sub>ON</sub> = 40V

- V<sub>OFF</sub> = -20V

- H sync timing frequency = 60kHz

- C<sub>L</sub> = 5nF

The value of  $V_L$ , the left over voltage in the capacitors in that case is 23V for the positive discharge and 3.3V for the negative discharge.

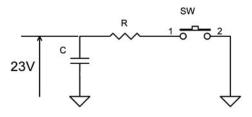

The voltage change across the capacitor is therefore 23V, see Figure 25.

The stored energy in the capacitor is:

$$1/2 \times V^2 C = 1/2 \times 23^2 \times 5 \times 10^{-9} = 132 \mu W$$

The energy which is stored in the capacitor will be dissipated on the resistor see Figure 26. The switch will close  $2 \times 60,000$  in every second.

Since the process will be repeated 2 times, for the CKV and the CKVB. In 0,000 cycles per second the power dissipation in  $R_3$  and  $R_6$  becomes:

$$2 \times 1.32 \times 10^{-6} \times 60^{3} = 160 \text{mW}$$

FIGURE 25.

FIGURE 26.

For different values of V<sub>ON</sub>, V<sub>OFF</sub>, C<sub>L</sub> and H sync timing frequency, the worst case dissipation can be calculated in a similar matter. The value of the R<sub>3</sub> and R<sub>6</sub> must be selected such that the capacitor C<sub>L</sub> is discharged via R<sub>3</sub> or R<sub>6</sub> resistor in one half period of the H sync timing.

Figures 11 and 12 show the total power dissipation over a range of possible voltages, operating frequencies and loads. Care should be taken to prevent the power from exceeding the maximum rating of the package, as shown in Figure 13.

## Package Outline Drawing

NOTE: The package drawing shown here may not be the latest version. To check the latest revision, please refer to the Intersil website at http://www.intersil.com/design/packages

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Single of the second se