# Visha 3 Video CD Processor Product Brief

### **DESCRIPTION**

The Vista®3 ES3890 single-chip Video CD (VCD) processor is the latest innovation of ESS's family of VCD chips for VCD players. The Vista3 ES3890 is based on the ESS Programmable Multimedia Processor (PMP) architecture consisting of a 32-bit video controller and a 64-bit video processor and it integrates the TV-encoder, thus eliminating the need for a VCD companion chip.

The ES3890 integrates an audio ADC for microphone inputs, two video DACs for Composite and S-video outputs, and digital echo circuitry. With Visla 3, VCD player design and board layout become simpler, the VCD system cost is much reduced, and it offers a very flexible design configuration for 512 kB or 2 MB system RAM.

The ES3890 performs all of the functions such as video filtering, NTSC/PAL conversion, audio and video error concealment, and picture zoom in/out up to 4x magnification. It supports On-Screen-Display (OSD) with 4 colors in 8 degrees of transparency, Karaoke, and VCD 2.0 Playback Control (PBC).

Features in the Vidua 3 ES3890 solution include: a 7-band audio graphic equalizer display with five pre-configured settings and environment effects, Karaoke voice recording for sing-along, and Karaoke scoring.

The ES3890 also offers the ESS SmartBright™ movie brightness feature, the ESS SmartColor™ color balancing feature, as well as the Kodak® Picture CD and Fujicolor® CD JPEG photo viewing features.

The ESS SmartBright™ feature allows the brightness level of VCD movies being played back to be adjusted in real time while the ESS SmartColor feature allows the skin color of JPEG photos being viewed to be enhanced. Other features found with the ES3890 include support for CD+G Karaoke, CD-Text, and Windows™ Media Audio (WMA) decoding and playback.

The ES3890 is available in an industry-standard 128-pin Plastic Quad Flat Pack (PQFP) device package.

#### **FEATURES**

- ESS proprietary dual CPU PMP core.

- Integrated TV-encoder.

- VCD 1.1 and 2.0 compatible.

- Composite or S-video output.

- CCIR601 non-square operation.

- NTSC/PAL formats.

- · Video error concealment.

- SmartBright feature for adjusting brightness of movies during playback.

- Video scaling and X- and Y-axis interpolation.

- Motion pan and zoom to 4X magnification.

- Video CD 2.0 Playback Control.

- · JPEG photos decoding and playback.

- Kodak Picture CD and Fujicolor CD JPEG image viewing.

- SmartColor feature for adjusting skin color of JPEG photos during viewing.

- · Trick mode functions.

- · Dual microphones inputs.

- 7-band audio graphic equalizer.

- Programmable master clock for external audio DAC.

- Digital echo up to 168 ms delay.

- Karaoke voice recording.

- Karaoke scoring.

- CD+G Karaoke.

- · Karaoke and subtitle functions.

- MP3 audio playback.

- · CD-DA with CD-Text.

- Vocal reverb simulates a theater acoustic environment.

- Windows Media Audio decoding.

- Flexible design for 512 kB or 2 MB memory.

- Direct servo control.

- Remote control interface for power standby on/off.

- 4-bit On-Screen Display controller with 3-bit blending supports 4 colors in 8 degrees of transparency.

- Power management.

- Optional lead-free leads using 98%-Sn/2%-Cu or 98%-Sn/2%-Bi with ES3890FF.

ESS Technology, Inc. SAM0487-031704

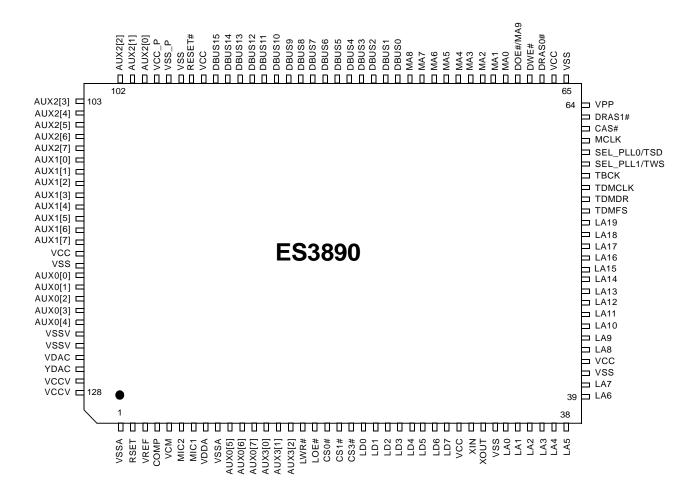

## **ES3890 PINOUT DIAGRAM**

The device pinout for the ES3890 is shown in Figure 1.

Figure 1 ES3890 Device Pinout

2 SAM0487-031704 ESS Technology, Inc.

**ES3890 PIN DESCRIPTION**

# **ES3890 PIN DESCRIPTION**

Table 1 lists the pin descriptions for the ES3890.

Table 1 ES3890 Pin Description

| Names      | Pin Numbers         | 1/0 | Definitions                                                                                                               |  |

|------------|---------------------|-----|---------------------------------------------------------------------------------------------------------------------------|--|

| VSSA       | 1, 9                | G   | Ground for analog circuits.                                                                                               |  |

| RSET       | 2                   | 0   | Reset. Internal current source generator. Connect this pin to a $510\Omega$ resistor to ground.                           |  |

| VREF       | 3                   | 0   | Output reference voltage. Connect to a 0.01– $\mu F$ high-frequency bypass capacitor to VSSA.                             |  |

| COMP       | 4                   | 0   | Compensation capacitance for low-pass filter on VDAC. Connect to a 0.01– $\mu$ F high-frequency bypass capacitor to VSSA. |  |

| VCM        | 5                   | 0   | ADC analog voltage reference. Connect to a 0.01–μF filter capacitor to VSSA.                                              |  |

| MIC1, MIC2 | 6, 7                | I   | Microphone inputs.                                                                                                        |  |

| VDDA       | 8                   | Р   | 5.0V power supply for analog circuits.                                                                                    |  |

| AUX0[7:5]  | 10-12               | I/O | General-purpose programmable I/O.                                                                                         |  |

| AUX3[2:0]  | 13-15               | I/O | General-purpose programmable I/O.                                                                                         |  |

| LWR#       | 16                  | 0   | RISC interface Write Enable (active-low).                                                                                 |  |

| LOE#       | 17                  | 0   | RISC SRAM Output Enable (active-low).                                                                                     |  |

| CS0#       | 18                  | 0   | Chip select 0 for SRAM (active-low).                                                                                      |  |

| CS1#       | 19                  | 0   | Chip select 1 for SRAM (active-low).                                                                                      |  |

| CS3#       | 20                  | 0   | Chip select 3 for SRAM (active-low).                                                                                      |  |

| LD[7:0]    | 21-28               | I/O | Data bus.                                                                                                                 |  |

| VCC        | 29, 42, 66, 95, 116 | Р   | Core power supply (2.5V).                                                                                                 |  |

| XIN        | 30                  | I   | Crystal connection or input source of 27MHz.                                                                              |  |

| XOUT       | 31                  | 0   | Crystal connection or output drive of an input clock source.                                                              |  |

| VSS        | 32, 41, 65, 97, 117 | G   | Ground for core.                                                                                                          |  |

| LA[19:0]   | 33-40, 43-54        | 0   | Address bus.                                                                                                              |  |

| TDMFS      | 55                  | I   | Frame signal from CDROM.                                                                                                  |  |

| TDMDR      | 56                  | I   | Data signal from CDROM.                                                                                                   |  |

| TDMCLK     | 57                  | I   | Clock signal from CDROM.                                                                                                  |  |

| TBCK       | 58                  | 0   | Transmit clock when sending audio IIS data to external DAC.                                                               |  |

| SEL_PLL1   | 59                  | I   | PLL mode select 1. Pulldown to ground to bypass PLL. Pullup to VCC for optimal performance.                               |  |

| TWS        |                     | 0   | Audio strobe signal of IIS signals to external DAC.                                                                       |  |

| SEL_PLL0   | 60                  | I   | PLL mode select 0. Pulldown to GND to bypass PLL. Pullup to VCC for optimal performance.                                  |  |

| TSD        |                     | 0   | Audio data of IIS signals to external DAC.                                                                                |  |

| MCLK       | 61                  | I/O | Media clock input to drive external audio devices or media clock output when driven by external source into the ES3890.   |  |

ESS Technology, Inc. SAM0487-031704 3

Table 1 ES3890 Pin Description (Continued)

| Names      | Pin Numbers | I/O | Definitions                                                                             |  |

|------------|-------------|-----|-----------------------------------------------------------------------------------------|--|

| CAS#       | 62          | 0   | Column Address Strobe to DRAM (active-low).                                             |  |

| DRAS1#     | 63          | 0   | Row Address Strobe 1 to DRAM (active-low).                                              |  |

| VPP        | 64          | Р   | 5V power supply.                                                                        |  |

| DRAS0#     | 67          | 0   | Row Address Strobe 0 to DRAM (active-low).                                              |  |

| DWE#       | 68          | 0   | Write Enable to DRAM (active-low).                                                      |  |

| DOE#       | 60          | 0   | Data Out Enable to DRAM (active-low).                                                   |  |

| MA9        | 69          | 0   | Multiplexed memory row and column address.                                              |  |

| MA[8:0]    | 70-78       | 0   | Multiplexed memory row and column address.                                              |  |

| DBUS[15:0] | 79-94       | I/O | Input when DRAM is being read. Output when DRAM is being written.                       |  |

| REST#      | 96          | I   | External system reset forces ES3890 to do a reset (active-low).                         |  |

| VSS_P      | 98          | G   | Ground for system PLL.                                                                  |  |

| VCC_P      | 99          | Р   | 2.5V power supply for system PLL.                                                       |  |

| AUX2[0]    | 100         | I/O | General-purpose programmable I/O. May be used for VFD clock.                            |  |

| AUX2[1]    | 101         | I/O | General-purpose programmable I/O. May be used for Subcode-Q data.                       |  |

| AUX2[2]    | 102         | I/O | General-purpose programmable I/O. May be used for Subcode-Q clock.                      |  |

| AUX2[3]    | 103         | I/O | General-purpose programmable I/O.                                                       |  |

| AUX2[4]    | 104         | I/O | General-purpose programmable I/O. May be used for C2PO error correction flag from CDROM |  |

| AUX2[5]    | 105         | I/O | General-purpose programmable I/O.                                                       |  |

| AUX2[6]    | 106         | I/O | General-purpose programmable I/O. May be used for Subcode sync S0 or S1 detection.      |  |

| AUX2[7]    | 107         | I/O | General-purpose programmable I/O.                                                       |  |

| AUX1[5:0]  | 108-113     | I/O | General-purpose programmable I/O.                                                       |  |

| AUX1[6]    | 114         | I/O | General-purpose programmable I/O. May be used for VFD data output.                      |  |

| AUX1[7]    | 115         | I/O | General-purpose programmable I/O. May be used for VFD data input.                       |  |

| AUX0[1:0]  | 118, 119    | I/O | General-purpose programmable I/O.                                                       |  |

| AUX0[2]    | 120         | I   | General-purpose programmable input.                                                     |  |

| AUX0[4:3]  | 121, 122    | I/O | General-purpose programmable I/O.                                                       |  |

| VSSV       | 123, 124    | G   | Ground for VDAC circuit.                                                                |  |

| VDAC       | 125         | 0   | Video DAC V output. Connect to a $37.7\Omega$ resistor to ground for proper operation.  |  |

| YDAC       | 126         | 0   | Video DAC Y output. Connect to a $37.7\Omega$ resistor to ground for proper operation.  |  |

| VCCV       | 127, 128    | Р   | 2.5V power supply for video DAC circuit.                                                |  |

4 SAM0487-031704 ESS Technology, Inc.

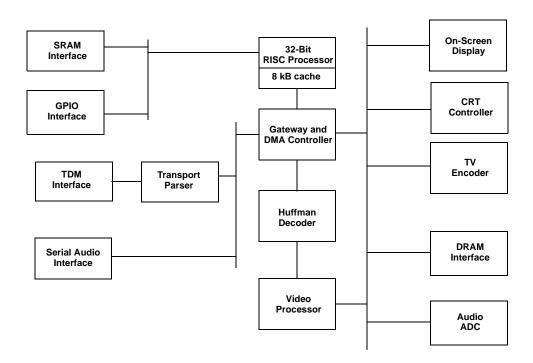

# **FUNCTIONAL DESCRIPTION**

Figure 2 below shows the internal block diagram of the ES3890.

Figure 2 ES3890 Block Diagram

ESS Technology, Inc. SAM0487-031704 5

### ORDERING INFORMATION

| Part Number | Description                                   | Package      |

|-------------|-----------------------------------------------|--------------|

| ES3890F     | Visba3 VCD Processor                          | 128-pin PQFP |

| ES3890FF    | Visba3 VideoCD Processor with lead-free leads | 128-pin PQFP |

The letter F at the end of the part number identifies the package type PQFP.

The second letter F at the end of the part number indicates lead-free leads with the device.

ESS Technology, Inc. 48401 Fremont Blvd. Fremont, CA 94538 Tel: (510) 492-1088

Fax: (510) 492-1898

No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

$\ensuremath{\mathsf{ESS}}$  Technology, Inc. makes no representations or warranties regarding the content of this document.

All specifications are subject to change without prior notice.

ESS Technology, Inc. assumes no responsibility for any errors contained herein.

U.S. patents pending.

MPEG is the Moving Picture Experts Group of the ISO/IEC. References to MPEG in this document refer to the ISO/IEC JTC1 SC29 committee draft ISO 11172 dated January 9, 1992.

Visba is a registered trademark of ESS Technology, Inc.

All other trademarks are trademarks of their respective companies and are used for identification purposes only.