# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

## HEF4753B LSI

#### DESCRIPTION

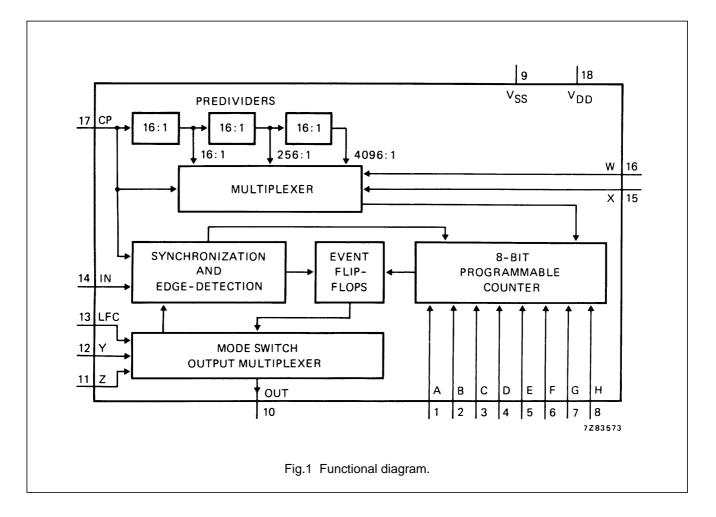

The HEF4753B is a universal timer module for counting and dividing as well as for event-recognition and manipulation of input sequences.

The following functions are included: synchronization and edge-detection of the input signal, programmable counter, clock divider with different lengths, operating mode decoder, control logic and output multiplexer.

Depending on the operating mode and the application, the circuit works as a presettable 8-bit counter with

transient-pulse suppression, pulse duration selector divider, counter, positive or negative edge delaying module or low-frequency control circuit. All manipulation possibilities depend on a time scaling, which is adjustable by the 8-bit programmable counter and the system clock. The system clock can be divided internally by 1, 16, 256 or 4096 as input clock for the counter. In all cases the manipulated input sequence appears at the only output OUT.

#### FAMILY DATA, IDD LIMITS category LSI

See Family Specifications

# HEF4753B LSI

#### FUNCTION TABLES

| INPUTS |   |   | OPERATING MODE                  |  |  |  |

|--------|---|---|---------------------------------|--|--|--|

| LFC    | Y | Z | OPERATING MODE                  |  |  |  |

| L      | L | Н | counter                         |  |  |  |

| L      | Н | L | divider                         |  |  |  |

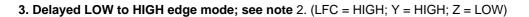

| Н      | Н | L | delayed LOW to HIGH edge        |  |  |  |

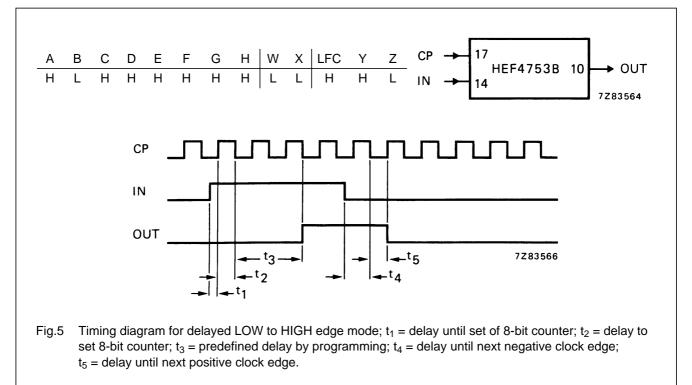

| Н      | L | Н | delayed HIGH to LOW edge        |  |  |  |

| Н      | Н | н | transient pulse suppression     |  |  |  |

| L      | Н | н | frequency recognition           |  |  |  |

| LFC    | L | L | digital pulse duration selector |  |  |  |

#### Notes

1. H = HIGH state (the more positive voltage).

2. L = LOW state (the less positive voltage).

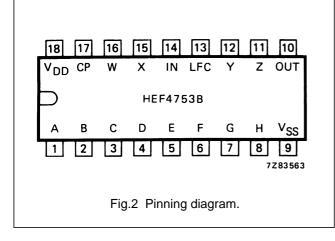

- HEF4753BP(N): 18-lead DIL; plastic (SOT102-3) HEF4753BD(N): 18-lead DIL; ceramic (cerdip) (SOT133)

- (): Package Designator North America

#### Programmable 8-bit counter (1)

| INPUTS ACTIVE LOW | VALUE |  |  |  |  |

|-------------------|-------|--|--|--|--|

| А                 | 1     |  |  |  |  |

| В                 | 2     |  |  |  |  |

| С                 | 4     |  |  |  |  |

| D                 | 8     |  |  |  |  |

| Е                 | 16    |  |  |  |  |

| F                 | 32    |  |  |  |  |

| G                 | 64    |  |  |  |  |

| Н                 | 128   |  |  |  |  |

#### Note

1. All inputs A to H HIGH is not allowed.

#### 12-bit predivider

| w | x | CLOCK FOR PROGRAMMABLE<br>COUNTER CP/X |

|---|---|----------------------------------------|

| L | L | X = 1                                  |

| L | н | X =16                                  |

| н | L | X = 256                                |

| Н | Н | X = 4096                               |

#### Product specification

## Universal timer module

# HEF4753B LSI

#### FUNCTIONAL DESCRIPTION

#### Clock divider and decoder

The clock signal at input CP is, at its original frequency, the system clock, but it also drives the programmable counter. The counter input frequency can be predivided by the factors 1/16, 1/256 and 1/4096, depending on the logic state of inputs W and X (according to the function tables above).

#### 8-bit programmable counter

The 8 inputs A to H are the set inputs of the 8 counter flip-flops. The setting is triggered by an edge of the input signal (at input IN) depending on of the chosen mode.

#### Event flip-flops, synchronization and edge-detection

The event flip-flops are used to recognize the positive and/or negative edge of the input signal at IN. Parts of the flip-flops are used together with the programmable 8-bit counter as a retriggerable mono-flop, which defines the time scaling for event recognition. The input IN is synchronized by the clock signal CP.

#### Mode switch and output multiplexer

This function switches the chosen output to the output (OUT) and gives the mode of which the edge at input IN has to be detected. The inputs Z, Y and LFC give 7 modes +1, that means in mode 'Digital Filter' the input LFC can be HIGH or LOW.

#### **OPERATING MODES**

The circuit has 6 operating modes which are activated by the logic state of inputs LFC, Y and Z. An extra mode is possible by using two circuits which are connected such so they function as a digital band-filter.

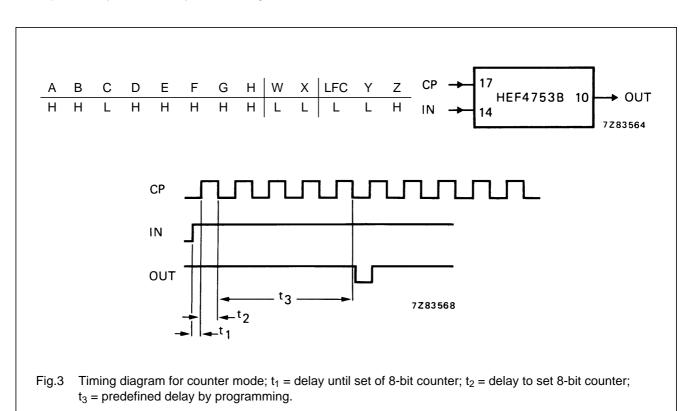

#### 1. Counter mode (LFC = LOW; Y = LOW; Z = HIGH)

In this mode the output OUT should be connected to input IN. If not, only one counter cycle starts after a transition at input IN (see Fig.3 and note 1.).

HEF4753B LSI

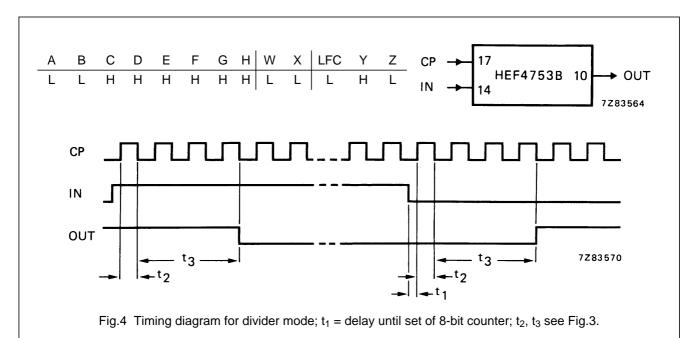

#### **2. Divider mode** (LFC = LOW; Y = HIGH; Z = LOW)

In this mode the output OUT should be connected to input IN. If not, only one counter cycle starts after a transition at input IN (see Fig.4 and note 1.).

HEF4753B LSI

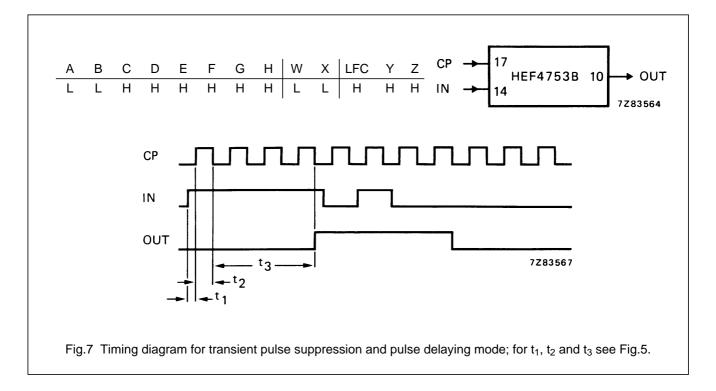

#### 5. Transient pulse suppression and pulse delaying mode; see note 2. (LFC = Y = Z = HIGH)

In this mode the circuit is working as a digital low-pass filter. An undisturbed pulse will only be delayed (see Fig.7).

HEF4753B LSI

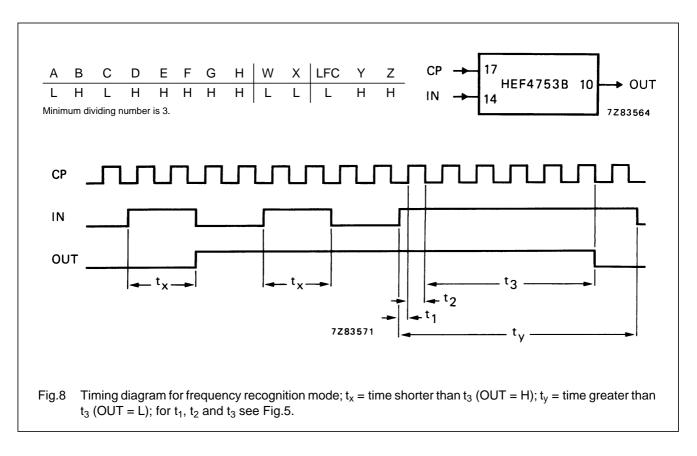

#### 6. Frequency recognition mode (LFC = LOW; Y = HIGH; Z = HIGH)

The incoming signal must be symmetrical within the limits as given by the specified delay time in note 2., to achieve lower or higher frequency detection (see Fig.8).

# Universal timer module HEF4753B

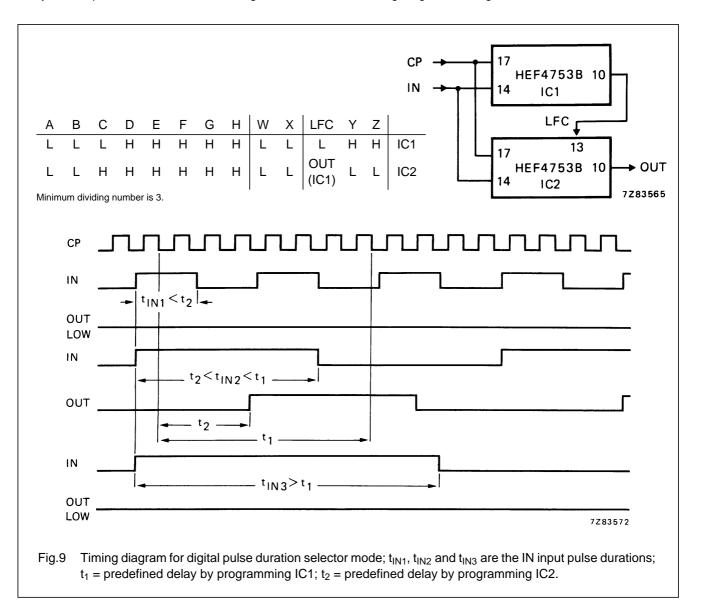

#### 7. Digital pulse duration selector mode (Y = Z = LOW)

This mode is a combination of two circuits, both used for frequency recognition. Both circuits are driven by the same clock and same input signal, but programmed for different frequencies. The LFC input of the low-frequency circuit is set to logic LOW, the output is connected to the LFC input of the high-frequency circuit, whose output (OUT) is the 'filter' output. The delay time depends on the same facts as given in note 2.. For timing diagram see Fig.9.

#### Notes to operating modes

- 1. The number of clocks for one cycle in the counter and divider mode is:

- a. Contents of programmable counter plus one if X = W = LOW.

- b. Contents of programmable counter multiplied by 16, 256 or 4096 if X and/or W = HIGH.

- 2. The delay in the modes 3, 4, 6 and 7, and the delay which is identical to the maximum duration of the transient pulse in mode 5 depend on the optional divided clock frequency, the input conditions of the 8-bit presetable counter and in addition, different times of propagation delays, jitter and maximum one half of a clock frequency period.

# HEF4753B LSI

### DC CHARACTERISTICS

$V_{SS} = 0 V$

|                 | V <sub>DD</sub> | V <sub>OH</sub><br>V | V <sub>OL</sub> |                  | T <sub>amb</sub> (°C) |      |      |      |      |      |    |

|-----------------|-----------------|----------------------|-----------------|------------------|-----------------------|------|------|------|------|------|----|

|                 |                 |                      |                 | SYMBOL           | <b>-40</b>            |      | + 25 |      | + 85 |      |    |

|                 |                 |                      | _               |                  | MIN.                  | MAX. | MIN. | MAX. | MIN. | MAX. |    |

| Output (sink)   | 4,75            |                      | 0,4             |                  | 2,7                   | _    | 2,3  | _    | 1,8  | _    | mA |

| current LOW     | 10              |                      | 0,5             | I <sub>OL</sub>  | 9,5                   | _    | 8,0  | _    | 6,3  | _    | mA |

| (pin 10)        | 15              |                      | 1,5             |                  | 24,0                  | _    | 20,0 | -    | 16,0 | _    | mA |

| Output (source) | 5               | 4,6                  |                 |                  | 0,6                   | _    | 0,5  | _    | 0,4  | _    | mA |

| current HIGH    | 10              | 9,5                  |                 | <br>             | 1,8                   | _    | 1,5  | _    | 1,2  | _    | mA |

| (pin 10)        | 15              | 13,5                 |                 | –I <sub>OH</sub> | 6,0                   | _    | 5,0  | _    | 4,0  | _    | mA |

#### AC CHARACTERISTICS

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                      | V <sub>DD</sub><br>V | SYMBOL                          | MIN. | TYP.     | MAX. |     | TYPICAL EXTRAPOLATION<br>FORMULA |

|----------------------|----------------------|---------------------------------|------|----------|------|-----|----------------------------------|

| Propagation delays   | 5                    |                                 |      | 420      | 850  | ns  |                                  |

| $CP \rightarrow OUT$ | 10                   | t <sub>PHL</sub>                |      | 180      | 360  | ns  |                                  |

| HIGH to LOW          | 15                   |                                 |      | 120      | 250  | ns  |                                  |

|                      | 5                    |                                 |      | 450      | 900  | ns  |                                  |

| LOW to HIGH          | 10                   | t <sub>PLH</sub>                |      | 200      | 400  | ns  |                                  |

|                      | 15                   |                                 |      | 140      | 280  | ns  |                                  |

| Output transition    | 5                    |                                 |      | 30       | 60   | ns  |                                  |

| times                | 10                   | t <sub>THL</sub>                |      | 15       | 30   | ns  |                                  |

| HIGH to LOW          | 15                   |                                 |      | 10       | 20   | ns  |                                  |

|                      | 5                    |                                 |      | 60       | 120  | ns  |                                  |

| LOW to HIGH          | 10                   | t <sub>TLH</sub>                |      | 30       | 60   | ns  |                                  |

|                      | 15                   |                                 |      | 20       | 40   | ns  |                                  |

| Input rise and       | 5                    |                                 |      |          |      |     |                                  |

| fall times           | 10                   | t <sub>r</sub> , t <sub>f</sub> |      | no limit |      |     |                                  |

| pins 13, 14, 17      | 15                   |                                 |      |          |      |     |                                  |

| Maximum clock        | 5                    |                                 | 3    | 6        |      | MHz |                                  |

| pulse frequency      | 10                   | f <sub>max</sub>                | 7    | 14       |      | MHz |                                  |

| pins 17; δ = 50%     | 15                   |                                 | 8    | 17       |      | MHz |                                  |

# HEF4753B LSI

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P (μW)                                                                       |                                        |

|-----------------|----------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|

| Dynamic power   | 5                    | 1 800 $f_i + \sum (f_o C_L) \times V_{DD}^2$                                                     | where                                  |

| dissipation per | 10                   | 8 000 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup>  | f <sub>i</sub> = input freq. (MHz)     |

| package (P)     | 15                   | 19 000 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup> | f <sub>o</sub> = output freq. (MHz)    |

|                 |                      |                                                                                                  | C <sub>L</sub> = load capacitance (pF) |

|                 |                      |                                                                                                  | $\sum (f_o C_L) = sum of outputs$      |

|                 |                      |                                                                                                  | V <sub>DD</sub> = supply voltage (V)   |