# **FLASH MEMORY**

## **Document Title**

32M x 8 Bit NAND Flash Memory

## **Revision History**

| evision No. | <u>History</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Draft Date       | Remark                  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------|

| 0.0         | Initial issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | April. 10th 1999 | Advanced<br>Information |

| 0.1         | Revised real-time map-out algorithm(refer to technical notes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | July. 23th 1999  | Advanced                |

| 0.2         | 1. Changed device name<br>i. KM29U256T -> K9F5608U0M-YCB0<br>ii. KM29U256IT -> K9F5608U0M-YIB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Sep. 15th 1999   | Preliminary             |

| 0.3         | <ol> <li>Changed tWP AC Timing         <ul> <li>If tCS is set less than 10ns, tWP must be minimum 35ns, otherwise tWP may be minimum 25ns.</li> </ul> </li> <li>Changed Sequential Row Read operation         <ul> <li>The Sequential Read 1 and 2 operation is allowed only within a block</li> <li>Changed invalid block(s) marking method prior to shipping</li> <li>The invalid block(s) information is written the 1st or 2nd page of the invalid block(s) with 00h data</li></ul></li></ol>                                                                                                                                                                                                           | Mar. 21th 2000   | Preliminary             |

| 0.4         | 1. Changed Endurance : 1million -> 100K Program/Erase Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Apr. 7th 2000    | Preliminary             |

| 0.5         | <ol> <li>Changed package name         <ul> <li>K9S5608U0M-MCB0 -&gt;K9F5608U0M-MCB0(Micro Flash Card)</li> </ul> </li> <li>Changed invalid block(s) marking method prior to shipping         <ul> <li>The invalid block(s) status is defined by the 6th byte in the spare area. Samsung makes sure that either the 1st or 2nd page of every invalid block has 00h data at the column address of 517.             <ul></ul></li></ul></li></ol>                                                                                                                                                                                                                                                              | Apr. 29th 2000   | Preliminary             |

| 0.6         | <ol> <li>Removed Micro Flash Card</li> <li>Changed SE pin description</li> <li>SE is recommended to coupled to GND or Vcc and should not be toggled during reading or programming.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | July 17th 2000   | Final                   |

| 0.7         | <ol> <li>Explain how pointer operation works in detail.</li> <li>Renamed GND input (pin # 6) on behalf of SE (pin # 6)         <ul> <li>The SE input controls the access of the spare area. When SE is high, the spare area is not accessible for reading or programming. SE is recommended to be coupled to GND or Vcc and should not be toggled during reading or programming.</li> <li>Connect this input pin to GND or set to static low state unless the sequential read mode excluding spare area is used.</li> </ul> </li> <li>Updated operation for tRST timing         <ul> <li>If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us.</li> </ul> </li> </ol> | Nov. 20th 2000   |                         |

any questions, please contact the SAMSUNG branch office near you.

**ELECTRONICS**

SAMSUNG

1

## 32M x 8 Bit NAND Flash Memory

### **FEATURES**

- Voltage Supply : 2.7V~3.6V

- Organization

- Memory Cell Array : (32M + 1024K)bit x 8bit

- Data Register : (512 + 16)bit x8bit

- Automatic Program and Erase

- Page Program : (512 + 16)Byte

- Block Erase : (16K + 512)Byte

- 528-Byte Page Read Operation

- Random Access : 10µs(Max.)

- Serial Page Access : 50ns(Min.)

- Fast Write Cycle Time

- Program time : 200µs(Typ.)

- Block Erase Time : 2ms(Typ.)

- Command/Address/Data Multiplexed I/O Port

- Hardware Data Protection

- Program/Erase Lockout During Power Transitions

- Reliable CMOS Floating-Gate Technology

- Endurance : 100K Program/Erase Cycles

- Data Retention : 10 Years

- Command Register Operation

- Package :

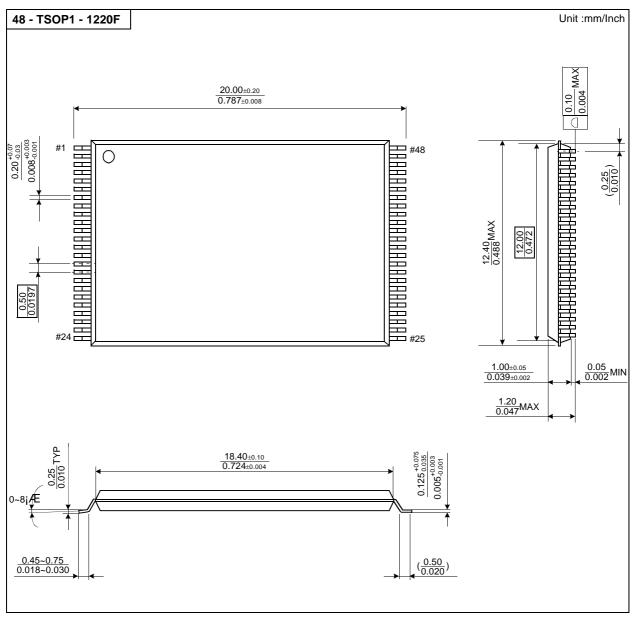

- K9F5608U0M-YCB0/YIB0 : 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

### **GENERAL DESCRIPTION**

The K9F5608U0M are a 32M(33,554,432)x8bit NAND Flash Memory with a spare 1,024K(1,048,576)x8bit. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. A program operation programs the 528byte page in typically 200µs and an erase operation can be performed in typically 2ms on a 16K-byte block. Data in the page can be read out at 50ns cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command inputs. The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verify and margining of data. Even the write-intensive systems can take advantage of the K9F5608U0M's extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm.

The K9F5608U0M-YCB0/YIB0 is an optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility.

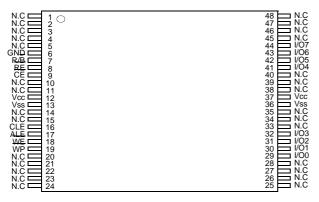

### **PIN CONFIGURATION**

### K9F5608U0M-YCB0/YIB0

### **PIN DESCRIPTION**

| Pin Name    | Pin Function                      |

|-------------|-----------------------------------|

| 1 III Name  | T III T direction                 |

| I/O0 ~ I/O7 | Data Input/Outputs                |

| CLE         | Command Latch Enable              |

| ALE         | Address Latch Enable              |

| CE          | Chip Enable                       |

| RE          | Read Enable                       |

| WE          | Write Enable                      |

| WP          | Write Protect                     |

| GND         | GND input for enabling spare area |

| R/B         | Ready/Busy output                 |

| Vcc         | Power                             |

| Vss         | Ground                            |

| N.C         | No Connection                     |

NOTE : Connect all Vcc and Vss pins of each device to common power supply outputs. Do not leave Vcc or Vss disconnected.

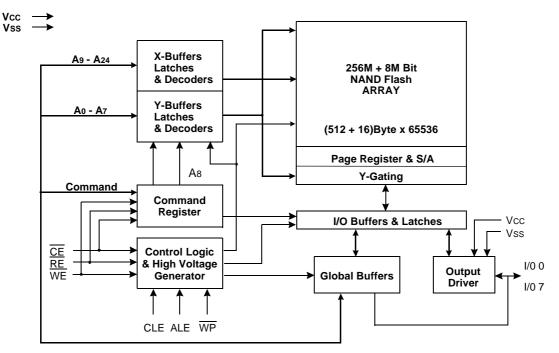

### Figure 1. FUNCTIONAL BLOCK DIAGRAM

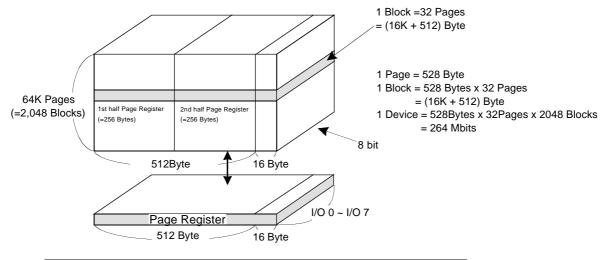

## Figure 2. ARRAY ORGANIZATION

|           | I/O 0 | I/O 1 | I/O 2 | I/O 3 | I/O 4 | I/O 5 | I/O 6 | I/O 7 |                |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|----------------|

| 1st Cycle | Ao    | A1    | A2    | Аз    | A4    | A5    | A6    | A7    | Column Address |

| 2nd Cycle | A9    | A10   | A11   | A12   | A13   | A14   | A15   | A16   | Row Address    |

| 3rd Cycle | A17   | A18   | A19   | A20   | A21   | A22   | A23   | A24   | (Page Address) |

$\label{eq:NOTE:Column Address: Starting Address of the Register.$

00h Command(Read) : Defines the starting address of the 1st half of the register.

01h Command(Read) : Defines the starting address of the 2nd half of the register.

$^{\ast}$  As is set to "Low" or "High" by the 00h or 01h Command.

### **PRODUCT INTRODUCTION**

The K9F5608U0M is a 264Mbit(276,824,064 bit) memory organized as 65,536 rows(pages) by 528 columns. Spare sixteen columns are located from column address of 512 to 527. A 528-byte data register is connected to memory cell arrays accommodating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 16 cells that are serially connected to form a NAND structure. Each of the 16 cells resides in a different page. A block consists of the 32 pages formed by two NAND structures, totaling 8,448 NAND structures of 16 cells. The array organization is shown in Figure 2. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 2,048 separately erasable 16K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9F5608U0M.

The K9F5608U0M has addresses multiplexed into 8 I/O's. This scheme dramatically reduces pin counts and allows systems upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Data is latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. All commands require one bus cycle except for Block Erase command which requires two cycles: one cycle for erase-setup and another for erase-execution after block address loading. The 32M byte physical space requires 25 addresses, thereby requiring three cycles for byte-level addressing: column address, low row address and high row address, in that order. Page Read and Page Program need the same three address cycles following the required command input. In Block Erase operation, however, only the two row address cycles are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the K9F5608U0M.

| Function     | 1st. Cycle             | 2nd. Cycle | Acceptable Command during Busy |

|--------------|------------------------|------------|--------------------------------|

| Read 1       | 00h/01h <sup>(1)</sup> | -          |                                |

| Read 2       | 50h <sup>(2)</sup>     | -          |                                |

| Read ID      | 90h                    | -          |                                |

| Reset        | FFh                    | -          | 0                              |

| Page Program | 80h                    | 10h        |                                |

| Block Erase  | 60h                    | D0h        |                                |

| Read Status  | 70h                    | -          | 0                              |

### Table 1. COMMAND SETS

NOTE : 1. The 00h command defines starting address of the 1st half of registers.

The 01h command defines starting address of the 2nd half of registers.

After data access on the 2nd half of register by the 01h command, the status pointer is

automatically moved to the 1st half register(00h) on the next cycle.

2. The 50h command is valid only when the GND inout (pin # 6) is low level.

# **FLASH MEMORY**

### **PIN DESCRIPTION**

### Command Latch Enable(CLE)

The CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the  $\overline{WE}$  signal.

### Address Latch Enable(ALE)

The ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of  $\overline{\text{WE}}$  with ALE high.

### Chip Enable(CE)

The  $\overline{CE}$  input is the device selection control. When  $\overline{CE}$  goes high during a read operation the device is returned to standby mode. However, when the device is in the Busy state during program or erase,  $\overline{CE}$  high is ignored, and does not return the device to standby mode.

### Write Enable(WE)

The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.

### Read Enable(RE)

The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.

#### GND (Pin # 6)

Connect this input pin to GND or set to static low state unless the sequential read mode excluding spare area is used.

#### I/O Port : I/O 0 ~ I/O 7

The I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.

#### Write Protect(WP)

The  $\overline{WP}$  pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the  $\overline{WP}$  pin is active low.

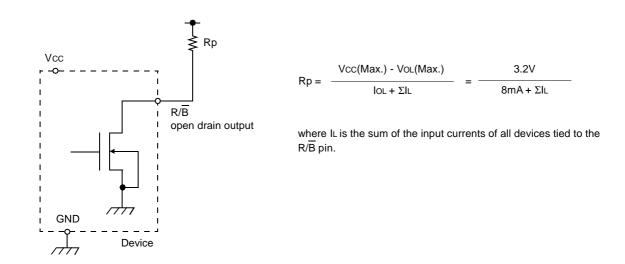

### Ready/Busy(R/B)

The R/B output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled.

# **FLASH MEMORY**

### **ABSOLUTE MAXIMUM RATINGS**

| Paran                       | neter           | Symbol | Rating        | Unit |  |

|-----------------------------|-----------------|--------|---------------|------|--|

| Voltage on any pin relative |                 | Vin    | -0.6 to + 4.6 | V    |  |

| voltage on any pin relative | 0 0 0 55        | Vcc    | -0.6 to + 4.6 | V    |  |

| Temperature Under Bias      | K9F5608U0M-YCB0 | TBIAS  | -10 to +125   | °C   |  |

| Temperature Onder bias      | K9F5608U0M-YIB0 | TBIAS  | -40 to +125   |      |  |

| Storogo Tomporatura         | K9F5608U0M-YCB0 | Тото   | 65 to 1150    | °C   |  |

| Storage Temperature         | K9F5608U0M-YIB0 | Тѕтс   | -65 to +150   |      |  |

NOTE :

Minimum DC voltage is -0.3V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns. Maximum DC voltage on input/output pins is Vcc,+0.3V which, during transitions, may overshoot to Vcc+2.0V for periods <20ns.</li>

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **RECOMMENDED OPERATING CONDITIONS**

(Voltage reference to GND, K9F5608U0M-YCB0 :TA=0 to 70°C, K9F5608U0M-YIB0:TA=-40 to 85°C)

| Parameter      | Symbol | Min | Тур. | Max | Unit |

|----------------|--------|-----|------|-----|------|

| Supply Voltage | Vcc    | 2.7 | 3.3  | 3.6 | V    |

| Supply Voltage | Vss    | 0   | 0    | 0   | V    |

### DC AND OPERATING CHARACTERISTICS(Recommended operating conditions otherwise noted.)

|                                                          | Parameter          | Symbol   | Test Conditions                           | Min     | Тур | Max     | Unit |

|----------------------------------------------------------|--------------------|----------|-------------------------------------------|---------|-----|---------|------|

| Operating Sequential Read Icc1 tRC=50ns, CE=VIL, IOUT=0r |                    |          |                                           | -       | 10  | 20      |      |

| Current                                                  | Program            | Icc2     | -                                         | -       | 10  | 20      |      |

|                                                          | Erase Icc3 10 20   | 20       | mA                                        |         |     |         |      |

| Stand-by Cu                                              | urrent(TTL)        | ISB1     | CE=VIH, WP=GND input (Pin #6)= 0V/Vcc     | -       | -   | 1       | -    |

| Stand-by Cu                                              | urrent(CMOS)       | ISB2     | CE=Vcc-0.2, WP=GND input (Pin#6) = 0V/Vcc | - 10 50 |     | _       |      |

| Input Leaka                                              | ge Current         | Iц       | VIN=0 to 3.6V                             | -       | -   | ±10     | μA   |

| Output Leak                                              | age Current        | Ilo      | Vout=0 to 3.6V                            | -       | -   | ±10     | 1    |

| Input High V                                             | /oltage            | Vін      | -                                         | 2.0     | -   | Vcc+0.3 |      |

| Input Low V                                              | oltage, All inputs | VIL      | -                                         | -0.3    | -   | 0.8     | V    |

| Output High                                              | Voltage Level      | Vон      | Іон=-400μА                                | 2.4     | -   | -       | V    |

| Output Low                                               | Voltage Level      | Vol      | OL IOL=2.1mA 0.4                          |         | 0.4 | 1       |      |

| Output Low                                               | Current(R/B)       | IOL(R/B) | Vol=0.4V                                  | 8       | 10  | -       | mA   |

# **FLASH MEMORY**

### VALID BLOCK

| Parameter          | Symbol | Min  | Тур. | Max  | Unit   |

|--------------------|--------|------|------|------|--------|

| Valid Block Number | Nvв    | 2013 | -    | 2048 | Blocks |

NOTE :

1. The K9F5608U0M may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not try to access these invalid blocks for program and erase. Refer to the attached technical notes for a appropriate management of invalid blocks.

2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block

### **AC TEST CONDITION**

(K9F5608U0M-YCB0 :TA=0 to 70°C, K9F5608U0M-YIB0:TA=-40 to 85°C, VCC=2.7V~3.6V unless otherwise)

| Parameter                      | Value                   |

|--------------------------------|-------------------------|

| Input Pulse Levels             | 0.4V to 2.4V            |

| Input Rise and Fall Times      | 5ns                     |

| Input and Output Timing Levels | 1.5V                    |

| Output Load (3.0V +/-10%)      | 1 TTL GATE and CL=50pF  |

| Output Load (3.3V +/-10%)      | 1 TTL GATE and CL=100pF |

### CAPACITANCE(TA=25°C, VCC=3.3V, f=1.0MHz)

| Item                     | Symbol | Test Condition | Min | Max | Unit |

|--------------------------|--------|----------------|-----|-----|------|

| Input/Output Capacitance | Cı/o   | VIL=0V         | -   | 10  | pF   |

| Input Capacitance        | CIN    | VIN=0V         | -   | 10  | pF   |

NOTE : Capacitance is periodically sampled and not 100% tested.

### **MODE SELECTION**

| CLE | ALE              | CE | WE | RE | GND                | WP        | Mode                          |                       |  |

|-----|------------------|----|----|----|--------------------|-----------|-------------------------------|-----------------------|--|

| Н   | L                | L  |    | н  | Х                  | Х         | Read Mode                     | Command Input         |  |

| L   | Н                | L  |    | Н  | Х                  | Х         |                               | Address Input(3clock) |  |

| Н   | L                | L  |    | Н  | Х                  | Н         | Write Mode                    | Command Input         |  |

| L   | Н                | L  |    | Н  | Х                  | Н         | Address Input(3clock)         |                       |  |

| L   | L                | L  |    | Н  | L/H <sup>(3)</sup> | Н         | Data Input                    |                       |  |

| L   | L                | L  | Н  | ▼  | L/H <sup>(3)</sup> | Х         | Sequential Read & Data Output |                       |  |

| L   | L                | L  | Н  | Н  | L/H <sup>(3)</sup> | Х         | During Read(E                 | Busy)                 |  |

| Х   | Х                | Х  | Х  | Х  | L/H <sup>(3)</sup> | Н         | During Progra                 | m(Busy)               |  |

| Х   | Х                | Х  | Х  | Х  | Х                  | Н         | During Erase(Busy)            |                       |  |

| Х   | X <sup>(1)</sup> | Х  | Х  | Х  | Х                  | L         | Write Protect                 |                       |  |

| Х   | Х                | Н  | Х  | Х  | 0V/Vcc(2)          | 0V/Vcc(2) | Stand-by                      |                       |  |

NOTE : 1. <u>X</u> can be VIL or VIH. 2. WP should be biased to CMOS high or CMOS low for standby. 3. When GND input is high, spare area is deselected.

### **Program/Erase Characteristics**

| Parameter                        | Symbol      | Min   | Тур | Max | Unit |        |

|----------------------------------|-------------|-------|-----|-----|------|--------|

| Program Time                     | tPROG       | -     | 200 | 500 | μs   |        |

| Number of Partial Program Cycles | Main Array  | Non   | -   | -   | 2    | cycles |

| in the Same Page                 | Spare Array | – Nop | -   | -   | 3    | cycles |

| Block Erase Time                 | tBERS       | -     | 2   | 3   | ms   |        |

# **FLASH MEMORY**

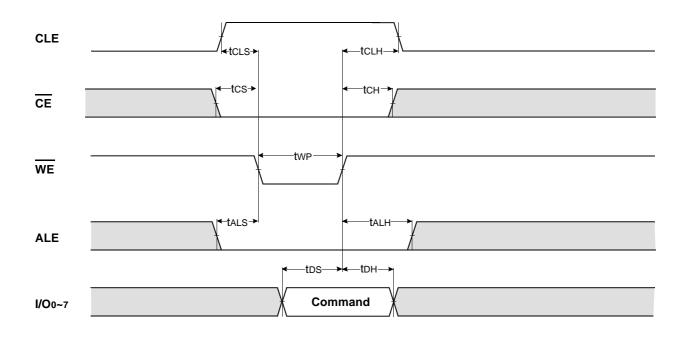

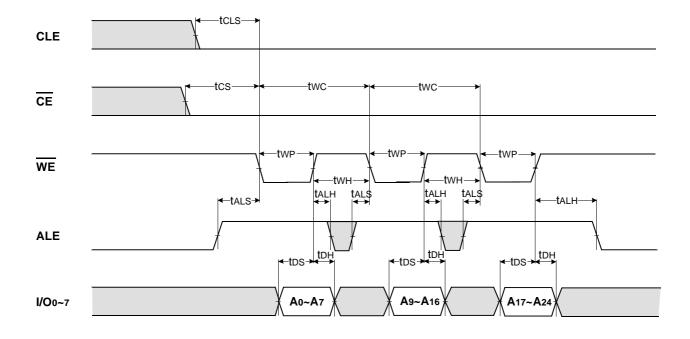

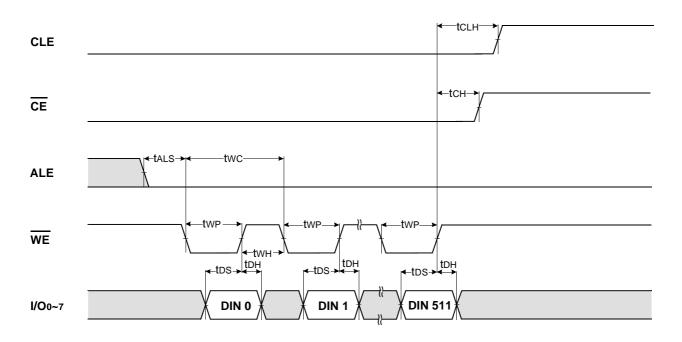

### AC Timing Characteristics for Command / Address / Data Input

| Parameter         | Symbol | Min               | Max | Unit |

|-------------------|--------|-------------------|-----|------|

| CLE Set-up Time   | tCLS   | 0                 | -   | ns   |

| CLE Hold Time     | tCLH   | 10                | -   | ns   |

| CE Setup Time     | tcs    | 0                 | -   | ns   |

| CE Hold Time      | tсн    | 10                | -   | ns   |

| WE Pulse Width    | tWP    | 25 <sup>(1)</sup> | -   | ns   |

| ALE Setup Time    | tals   | 0                 | -   | ns   |

| ALE Hold Time     | talh   | 10                | -   | ns   |

| Data Setup Time   | tDS    | 20                | -   | ns   |

| Data Hold Time    | tDH    | 10                | -   | ns   |

| Write Cycle Time  | twc    | 50                | -   | ns   |

| WE High Hold Time | twн    | 15                | -   | ns   |

NOTE : 1. If tCS is set less than 10ns, tWP must be minimum 35ns, otherwise, tWP may be minimum 25ns.

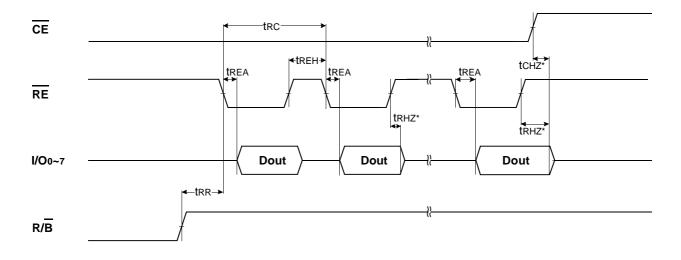

### **AC Characteristics for Operation**

| Parameter                                                 | Symbol  | Min | Max            | Unit |

|-----------------------------------------------------------|---------|-----|----------------|------|

| Data Transfer from Cell to Register                       | tR      | -   | 10             | μs   |

| ALE to RE Delay( ID read )                                | tar1    | 100 | -              | ns   |

| ALE to RE Delay(Read cycle)                               | tAR2    | 50  | -              | ns   |

| CE to RE Delay( ID read)                                  | tCR     | 100 | -              | ns   |

| Ready to RE Low                                           | trr     | 20  | -              | ns   |

| RE Pulse Width                                            | tRP     | 30  | -              | ns   |

| WE High to Busy                                           | twв     | -   | 100            | ns   |

| Read Cycle Time                                           | tRC     | 50  | -              | ns   |

| RE Access Time                                            | trea    | -   | 35             | ns   |

| RE High to Output Hi-Z                                    | trhz    | 15  | 30             | ns   |

| CE High to Output Hi-Z                                    | tCHZ    | -   | 20             | ns   |

| RE High Hold Time                                         | treh    | 15  | -              | ns   |

| Output Hi-Z to RE Low                                     | tır     | 0   | -              | ns   |

| Last RE High to Busy(at sequential read)                  | trв     | -   | 100            | ns   |

| CE High to Ready(in case of interception by CE at read)   | tCRY    | -   | 50 +tr(R/B)(1) | ns   |

| CE High Hold Time(at the last serial read) <sup>(2)</sup> | tCEH    | 100 | -              | ns   |

| RE Low to Status Output                                   | trsto   | -   | 35             | ns   |

| CE Low to Status Output                                   | tcsто   | -   | 45             | ns   |

| WE High to RE Low                                         | twhr    | 60  | -              | ns   |

| RE access time(Read ID)                                   | treadid | -   | 35             | ns   |

| Device Resetting Time(Read/Program/Erase)                 | trst    | -   | 5/10/500       | μs   |

NOTE :

The time to Ready depends on the <u>value</u> of the pull-up resistor tied R/B pin.

To break the sequential read cycle, CE must be held high for longer time than tCEH.

If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us.

# **FLASH MEMORY**

### NAND Flash Technical Notes

#### Invalid Block(s)

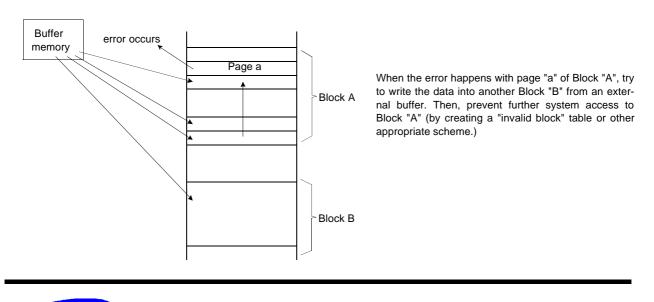

Invalid blocks are defined as blocks that contain one or more invalid bits whose reliability is not guaranteed by Samsung. The information regarding the invalid block(s) is so called as the invalid block information. Devices with invalid block(s) have the same quality level or as devices with all valid blocks and have the same AC and DC characteristics. An invalid block(s) does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select transistor. The system design must be able to mask out the invalid block(s) via address mapping. The 1st block of the NAND Flash, however, is fully guaranteed to be a valid block.

#### Identifying Invalid Block(s)

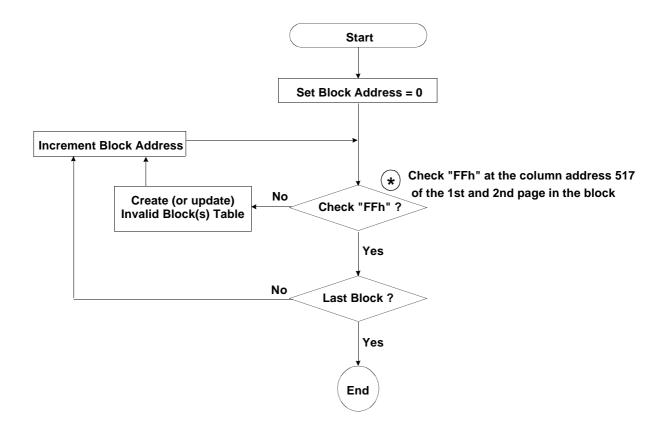

All device locations are erased(FFh) except locations where the invalid block(s) information is written prior to shipping. The invalid block(s) status is defined by the 6th byte in the spare area. Samsung makes sure that either the 1st or 2nd page of every invalid block has non-FFh data at the column address of 517. Since the invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the invalid block(s) based on the original invalid block information and create the invalid block table via the following suggested flow chart(Figure 1). Any intentional erasure of the original invalid block information is prohibited.

#### Figure 1. Flow chart to create invalid block table.

# **FLASH MEMORY**

### NAND Flash Technical Notes (Continued)

#### Error in write or read operation

Over its life time, the additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the actual data. The following possible failure modes should be considered to implement a highly reliable system. In the case of status read failure after erase or program, block replacement should be done. To improve the efficiency of memory space, it is recommended that the read or verification failure due to single bit error be reclaimed by ECC without any block replacement. The said additional block failure rate does not include those reclaimed blocks.

|       | Failure Mode       | Detection and Countermeasure sequence                                                                                    |

|-------|--------------------|--------------------------------------------------------------------------------------------------------------------------|

|       | Erase Failure      | Status Read after Erase> Block Replacement                                                                               |

| Write | Program Failure    | Status Read after Program> Block Replacement<br>Read back (Verify after Program)> Block Replacement<br>or ECC Correction |

| Read  | Single Bit Failure | Verify ECC -> ECC Correction                                                                                             |

### ECC

: Error Correcting Code --> Hamming Code etc. Example) 1bit correction & 2bit detection

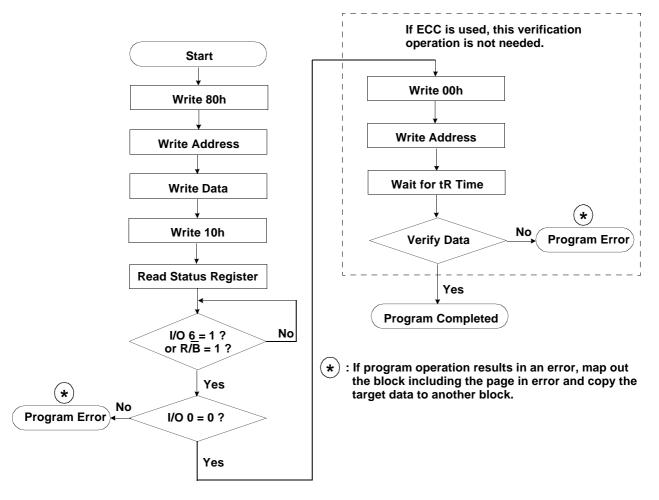

### Program Flow Chart

## **FLASH MEMORY**

### NAND Flash Technical Notes (Continued)

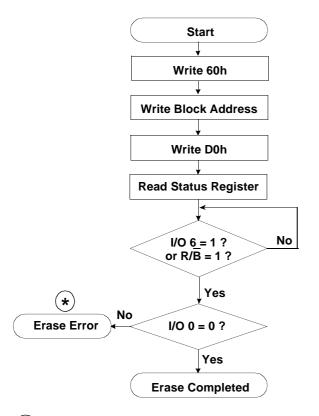

### Erase Flow Chart

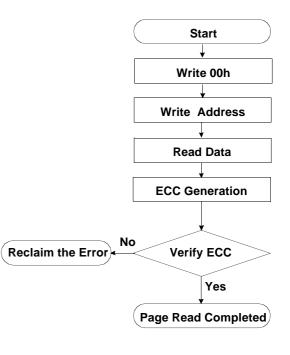

### Read Flow Chart

(\*) : If erase operation results in an error, map out the failing block and replace it with another block.

### **Block Replacement**

## **FLASH MEMORY**

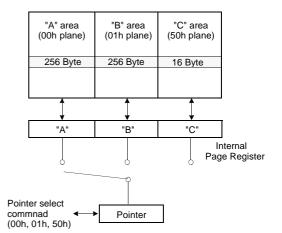

#### Pointer Operation of K9F5608U0M

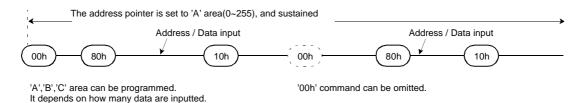

Samsung NAND Flash has three address pointer commands as a substitute for the two most significant column addresses. '00h' command sets the pointer to 'A' area(0~255byte), '01h' command sets the pointer to 'B' area(256~511byte), and '50h' command sets the pointer to 'C' area(512~527byte). With these commands, the starting column address can be set to any of a whole page(0~527byte). '00h' or '50h' is sustained until another address pointer command is inputted. '01h' command, however, is effective only for one operation. After any operation of Read, Program, Erase, Reset, Power\_Up is executed once with '01h' command, the address pointer returns to 'A' area by itself. To program data starting from 'A' or 'C' area, '00h' or '50h' command must be inputted before '80h' command is not necessary. To program data starting from 'B' area, '01h' command must be inputted right before '80h' command is written.

#### Table 1. Destination of the pointer

| Command | Pointer position | Area              |

|---------|------------------|-------------------|

| 00h     | 0 ~ 255 byte     | 1st half array(A) |

| 01h     | 256 ~ 511 byte   | 2nd half array(B) |

| 50h     | 512 ~ 527 byte   | spare array(C)    |

Figure 2. Block Diagram of Pointer Operation

#### (1) Command input sequence for programming 'A' area

#### (2) Command input sequence for programming 'B' area

The address pointer is set to 'B' area(256~512), and will be reset to 'A' area after every program operation is executed. Address / Data input Address / Data input 01h 10h 80h 10h 80h 01h 'B', 'C' area can be programmed. '01h' command must be rewritten before It depends on how many data are inputted. every program operation (3) Command input sequence for programming 'C' area The address pointer is set to 'C' area(512~527), and sustained Address / Data input Address / Data input 50h 80h 10h 50h 80h 10h

Only 'C' area can be programmed.

'50h' command can be omitted.

# **FLASH MEMORY**

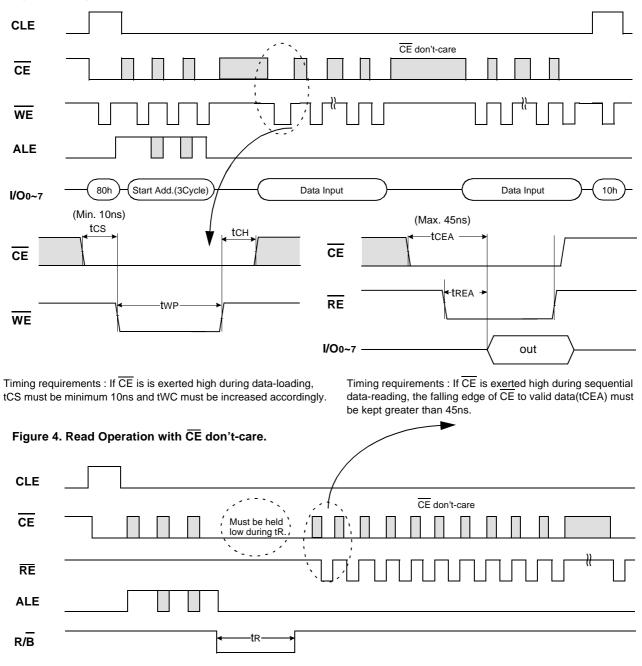

### System Interface Using $\overline{CE}$ don't-care.

SAMSUNG

**ELECTRONICS**

For an easier system interface,  $\overline{CE}$  may be inactive during the data-loading or sequential data-reading as shown below. The internal 528byte page registers are utilized as seperate buffers for this operation and the system design gets more flexible. In addition, for voice or audio applications which use slow cycle time on the order of u-seconds, de-activating  $\overline{CE}$  during the data-loading and reading would provide significant savings in power consumption.

### Figure 3. Program Operation with $\overline{CE}$ don't-care.

WE

Other

Other

Data Output(sequential)

Data Output(sequential)

Out

# **FLASH MEMORY**

## \* Command Latch Cycle

## \* Address Latch Cycle

SAMSUNG ELECTRONICS

## \* Input Data Latch Cycle

\* Sequential Out Cycle after Read(CLE=L, WE=H, ALE=L)

**NOTES :** Transition is measured ±200mV from steady state voltage with load. This parameter is sampled and not 100% tested.

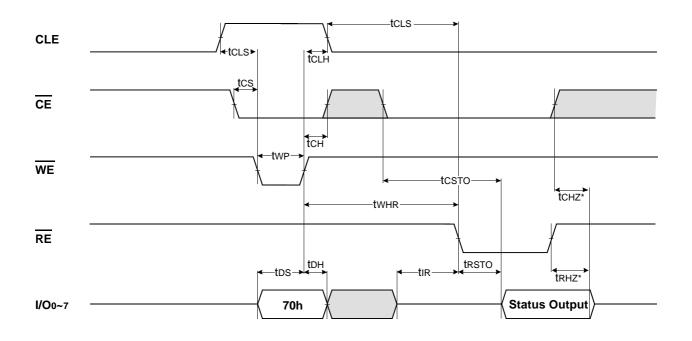

## \* Status Read Cycle

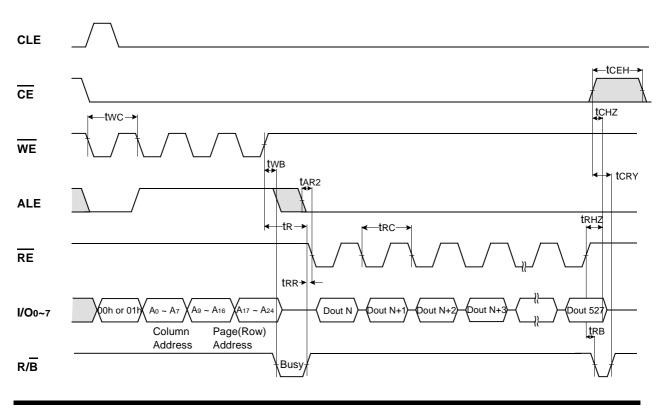

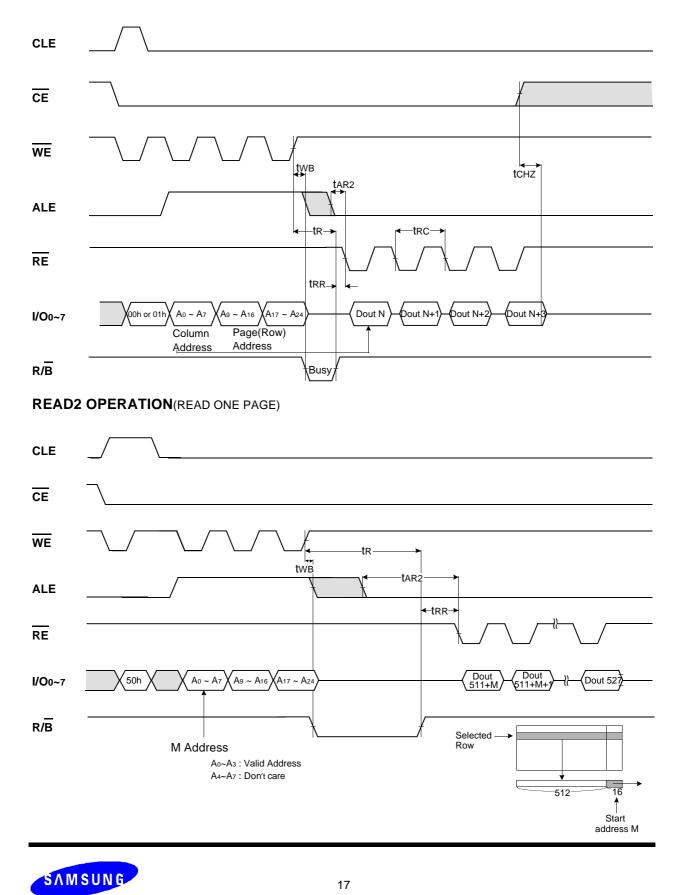

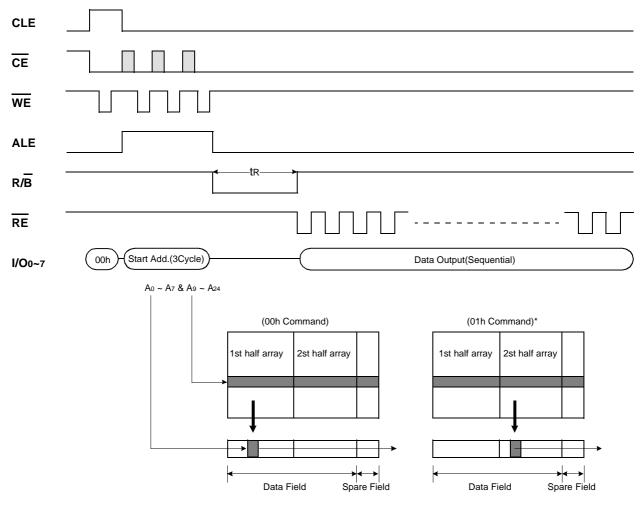

### READ1 OPERATION(READ ONE PAGE)

SAMSUNG ELECTRONICS

**READ1 OPERATION**(INTERCEPTED BY CE)

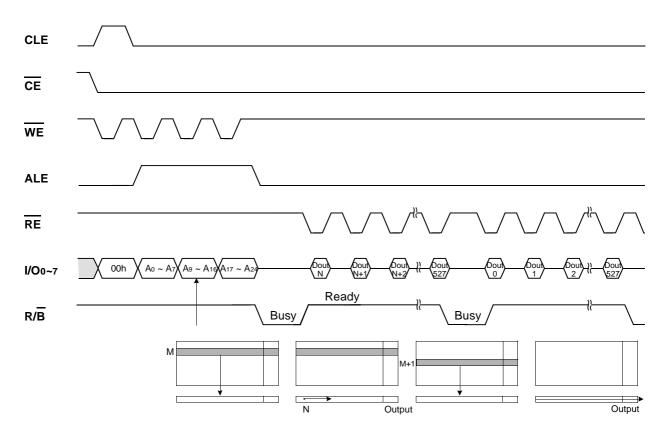

### SEQUENTIAL ROW READ OPERATION (WITHIN A BLOCK)

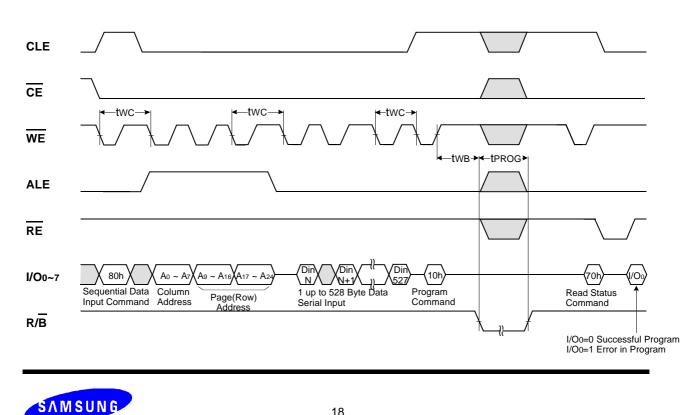

PAGE PROGRAM OPERATION

**FLASH MEMORY**

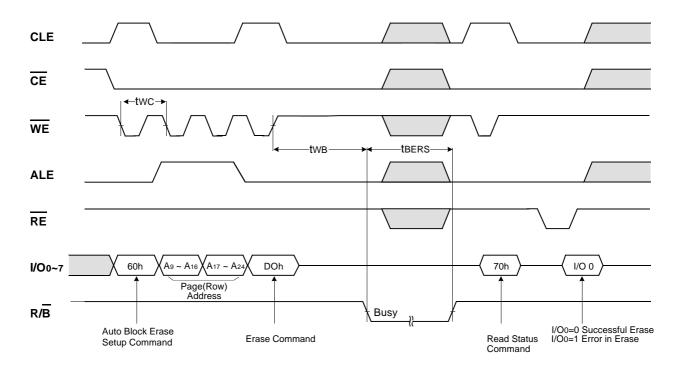

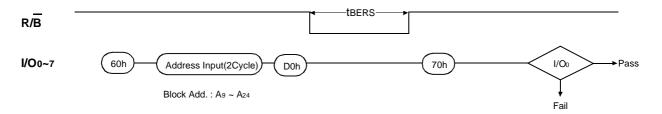

## **BLOCK ERASE OPERATION (ERASE ONE BLOCK)**

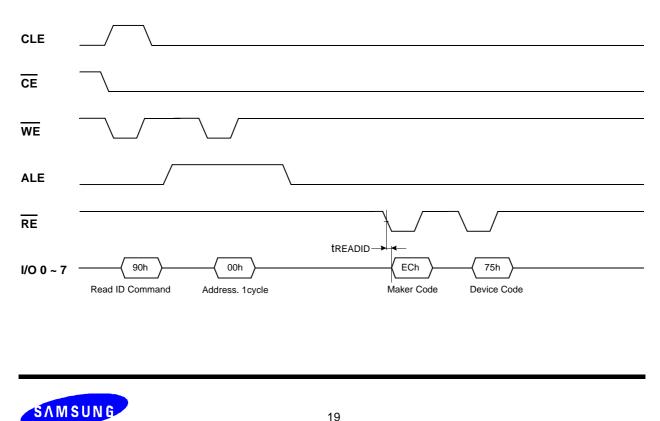

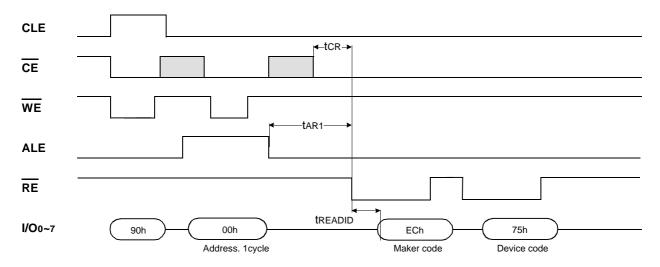

## **MANUFACTURE & DEVICE ID READ OPERATION**

### **DEVICE OPERATION**

### PAGE READ

Upon initial device power up, the device defaults to Read1 mode. This operation is also initiated by writing 00h to the command register along with three address cycles. Once the command is latched, it does not need to be written for the following page read operation. Three types of operations are available : random read, serial page read and sequential row read.

The random read mode is enabled when the page address is changed. The 528 bytes of data within the selected page are transferred to the data registers in less than  $10\mu s(t_R)$ . The system controller can detect the completion of this data transfer(tR) by analyzing the output of R/B pin. Once the data in a page is loaded into the registers, they may be read out in 50ns cycle time by sequentially pulsing RE. High to low transitions of the RE clock output the data stating from the selected column address up to the last column address(column 511 or 527 depending on the state of GND input pin).

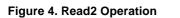

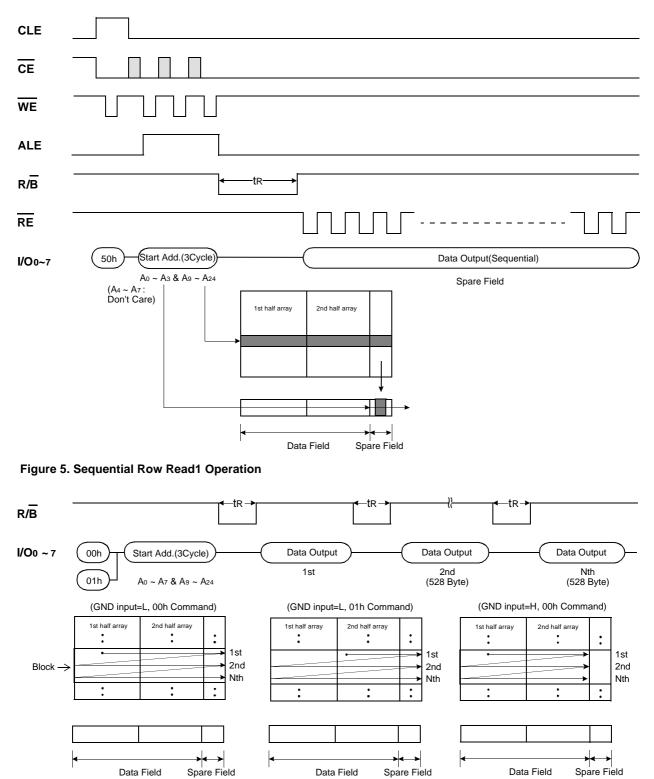

After the data of last column address is clocked out, the next page is automatically selected for sequential row read. Waiting 10µs again allows reading the selected page. The sequential row read operation is terminated by bringing CE high. The way the Read1 and Read2 commands work is like a pointer set to either the main area or the spare area. The spare area of bytes 512 to 527 may be selectively accessed by writing the Read2 command with GND input pin low. Addresses Ao to A3 set the starting address of the spare area while addresses A4 to A7 are ignored. Unless the operation is aborted, the page address is automatically incremented for sequential row read as in Read1 operation and spare sixteen bytes of each page may be sequentially read. The Read1 command(00h/01h) is needed to move the pointer back to the main area. Figures 3 thru 6 show typical sequence and timings for each read operation.

### Figure 3. Read1 Operation

\* After data access on 2nd half array by 01h command, the start pointer is automatically moved to 1st half array (00h) at next cycle.

The Sequential Read 1 and 2 operation is allowed only within a block and after the last page of a block is readout, the sequential read operation must be terminated by bringing  $\overline{CE}$  high. When the page address moves onto the next block, read command and address must be given.

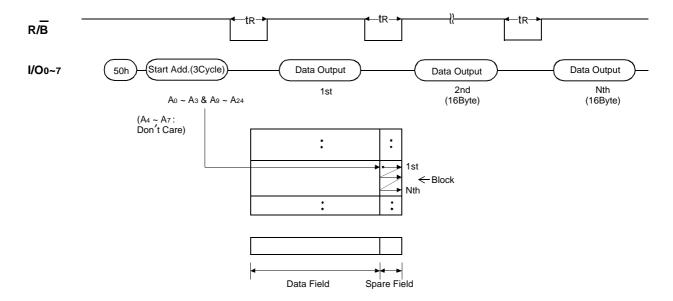

Figure 6. Sequential Row Read2 Operation (GND Input=Fixed Low)

#### PAGE PROGRAM

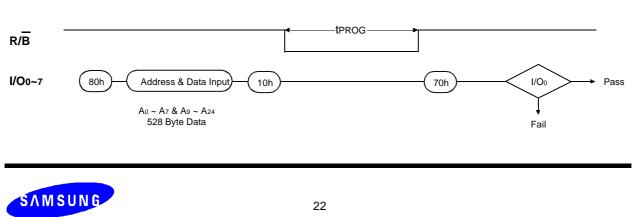

The device is programmed basically on a page basis, but it does allow multiple partial page programing of a byte or consecutive bytes up to 528, in a single page program cycle. The number of consecutive partial page programming operation within the same page without an intervening erase operation should not exceed 2 for main array and 3 for spare array. The addressing may be done in any random order in a block. A page program cycle consists of a serial data loading period in which up to 528 bytes of data may be loaded into the page register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell. Serial data loading can be started from 2nd half array by moving pointer. About the pointer operation, please refer to the attached technical notes.

The serial data loading period begins by inputting the Serial Data Input command(80h), followed by the three cycle address input and then serial data loading. The bytes other than those to be programmed do not need to be loaded. The Page Program confirm command(10h) initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the programming process. The internal write controller automatically executes the algorithms and timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command may be entered, with RE and CE low, to read the status register. The system controller can detect the completion of a program cycle by monitoring the R/B output, or the Status bit(I/O 6) of the Status Register. Only the Read Status command and Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status Bit(I/O 0) may be checked(Figure 7). The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command register remains in Read Status command mode until another valid command is written to the command register.

#### Figure 7. Program Operation

#### **BLOCK ERASE**

The Erase operation is done on a block(16K Byte) basis. Block address loading is accomplished in two cycles initiated by an Erase Setup command(60h). Only address A14 to A24 is valid while A9 to A13 is ignored. The Erase Confirm command(D0h) following the block address loading initiates the internal erasing process. This two-step sequence of setup followed by execution command ensures that memory contents are not accidentally erased due to external noise conditions.

At the rising edge of  $\overline{\text{WE}}$  after the erase confirm command input, the internal write controller handles erase and erase-verify. When the erase operation is completed, the Write Status Bit(I/O 0) may be checked. Figure 8 details the sequence.

#### Figure 8. Block Erase Operation

#### **READ STATUS**

The device contains a Status Register which may be read to find out whether program or erase operation is completed, and whether the program or erase operation is completed successfully. After writing <u>70h</u> command to the command register, a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of  $\overline{CE}$  or  $\overline{RE}$ , whichever occurs last. This two line control allows the system to poll the progress of each device in multiple memory connections even when R/B pins are common-wired.  $\overline{RE}$  or  $\overline{CE}$  does not need to be toggled for updated status. Refer to table 2 for specific Status Register definitions. The command register remains in Status Read mode until further commands are issued to it. Therefore, if the status register is read during a random read cycle, a read command(00h or 50h) should be given before sequential page read cycle.

| I/O # | Status                     | Definition                          |  |

|-------|----------------------------|-------------------------------------|--|

| I/O 0 | Program / Erase            | "0" : Successful Program / Erase    |  |

|       |                            | "1" : Error in Program / Erase      |  |

| I/O 1 |                            | "0"                                 |  |

| I/O 2 | Reserved for Future<br>Use | "0"                                 |  |

| I/O 3 |                            | "0"                                 |  |

| I/O 4 |                            | "0"                                 |  |

| I/O 5 |                            | "0"                                 |  |

| I/O 6 | Device Operation           | "0" : Busy "1" : Ready              |  |

| I/O 7 | Write Protect              | "0" : Protected "1" : Not Protected |  |

#### Table2. Read Status Register Definition

# **FLASH MEMORY**

#### **READ ID**

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h. Two read cycles sequentially output the manufacture code(ECh), and the device code (75h) respectively. The command register remains in Read ID mode until further commands are issued to it. Figure 9 shows the operation sequence.

#### Figure 9. Read ID Operation

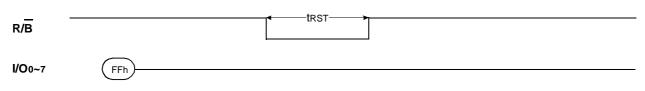

#### RESET

The device offers a reset feature, executed by writing FFh to the command register. When the device is in Busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value C0h when WP is high. Refer to table 3 for device status after reset operation. If the device is already in reset state a new reset command will not be accepted by the command register. The R/B pin transitions to low for tRST after the Reset command is written. Refer to Figure 10 below.

#### Figure 10. RESET Operation

#### **Table3. Device Status**

|                | After Power-up | After Reset              |

|----------------|----------------|--------------------------|

| Operation Mode | Read 1         | Waiting for next command |

# **FLASH MEMORY**

### READY/BUSY

The device has a R/B output that provides a hardware method of indicating the completion of a page program, erase and random read completion. The R/B pin is normally high but transitions to low after program or erase command is written to the command register or random read is started after address loading. It returns to high when the internal controller has finished the operation. The pin is an open-drain driver thereby allowing two or more R/B outputs to be Or-tied. An appropriate pull-up resister is required for proper operation and the value may be calculated by the following equation.

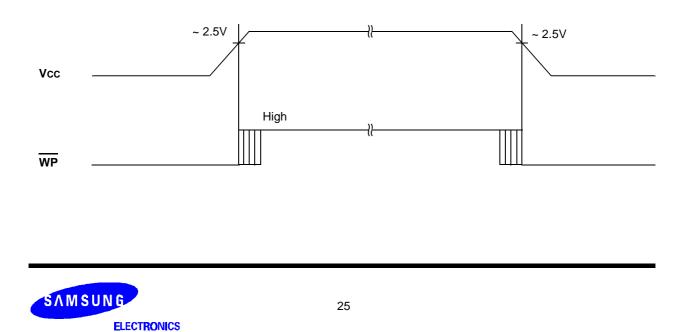

#### DATA PROTECTION

The device is designed to offer protection from any involuntary program/erase during power-transitions. An internal voltage detector disables all functions whenever Vcc is below about 2V. WP pin provides hardware protection and is recommended to be kept at VIL during power-up and power-down as shown in Figure 11. The two step command sequence for program/erase provides additional software protection.

#### Figure 11. AC Waveforms for Power Transition

# Package Dimensions

# **FLASH MEMORY**

### PACKAGE DIMENSIONS

### 48-PIN LEAD PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)