# M37753FFCFP M37753FFCHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER FLASH MEMORY VERSION

#### **DESCRIPTION**

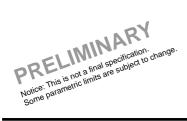

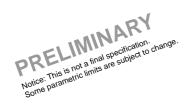

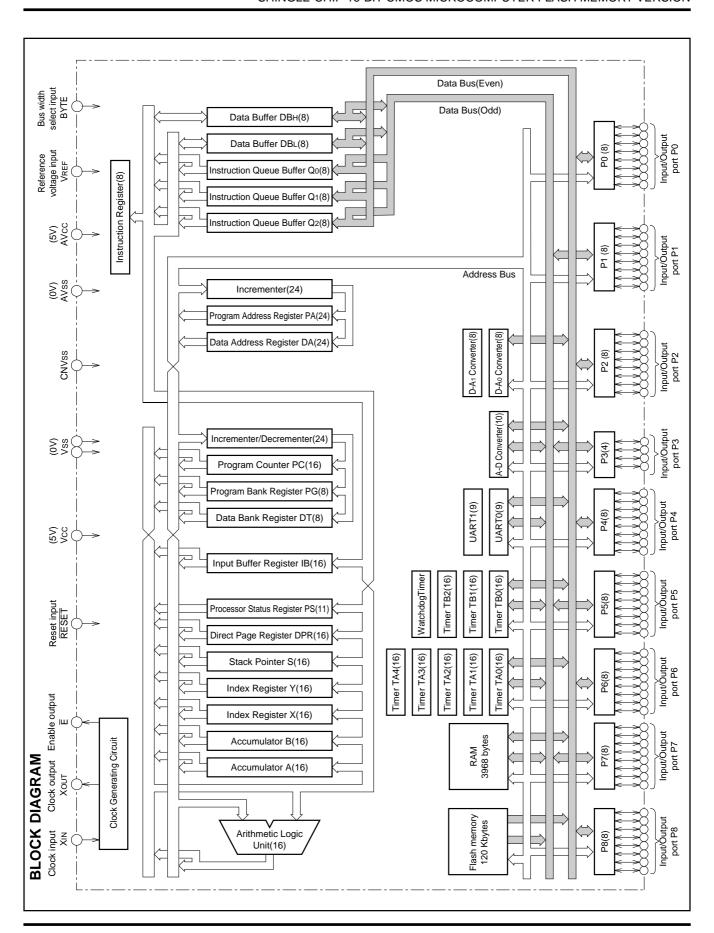

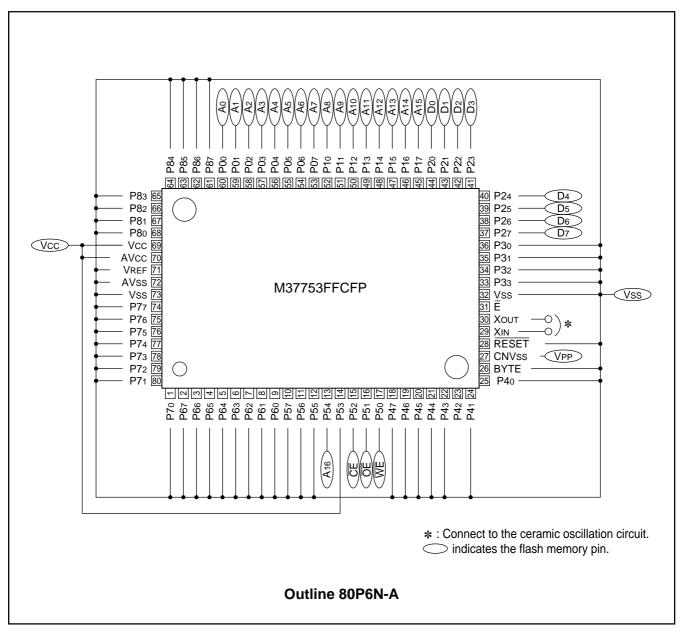

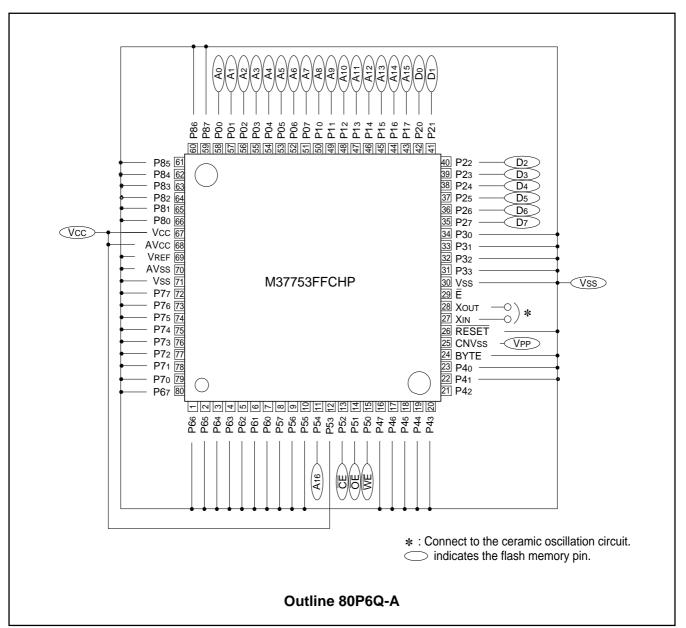

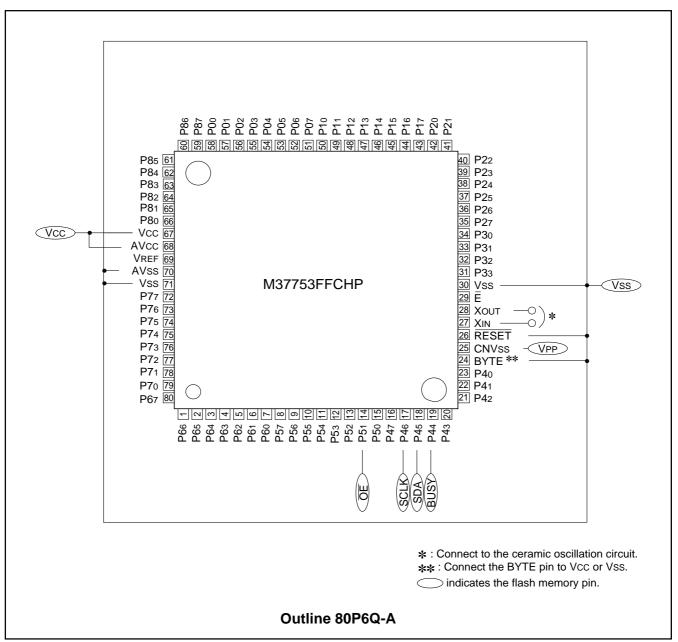

The M37753FFCFP and the M37753FFCHP are single-chip microcomputers designed with high-performance CMOS silicon gate technology, including the internal flash memory. These are housed in 80-pin plastic molded QFP.

These microcomputers have a CPU and a bus interface unit. The CPU is a 16-bit parallel processor that can also be switched to perform 8-bit parallel processing, and the bus interface unit enhances the memory access efficiency to execute instructions fast.

In addition to the 7700 Family basic instructions, the M37753FFCFP and the M37753FFCHP have 6 special instructions which contain instructions for signed multiplication/division; these added instructions improve the servo arithmetic performance to control hard disk drives and so on.

These microcomputers also include the flash memory, RAM, multiple-function timers, motor control function, serial I/O, A-D converter, D-A converter, and so on.

The internal flash memory can be programed and erased by using a PROM programmer or by control of the central processing unit (CPU). Therefore, these microcomputers can change the program easily even after they are mounted on the board.

#### DISTINCTIVE FEATURES

<Microcomputer mode>

| <microcomputer mode=""></microcomputer>                              |     |

|----------------------------------------------------------------------|-----|

| Number of basic machine instructions                                 | 09  |

| (103 basic instructions of 7700 Family + 6 special instructio        | ns) |

| Memory size Flash memory 120 Kbyt                                    | es  |

| RAM3968 by                                                           | es  |

| <ul> <li>■ Instruction execution time</li> </ul>                     |     |

| The fastest instruction at 40 MHz frequency 100                      | ns  |

| • Single power supply5V ±10                                          | %   |

| • Low power dissipation (at 40 MHz frequency) 125 mW (Ty             | p.) |

| ● Interrupts                                                         | els |

| Multiple-function 16-bit timer 5                                     | +3  |

| (three-phase motor drive waveform or pulse motor control wa          | ve- |

| form output)                                                         |     |

| Serial I/O (UART or clock synchronous)                               | . 2 |

| • 10-bit A-D converter 8-channel inp                                 | uts |

| 8-bit D-A converter 2-channel outp                                   | uts |

| • 12-bit watchdog timer                                              |     |

| ● Programmable input/output (ports P0—P8)                            | 68  |

| ● Small package [M37753FFCHP]                                        |     |

| 80-pin fine pitch QFP (lead pitch : 0.5 m                            | ım) |

| <flash memory="" mode=""></flash>                                    |     |

| ● Supply voltage Vcc = 5 V ± 10                                      | %   |

| ● Program/Erase voltage VPP = 12 V ± 5                               | %   |

| • Programming method Programming in unit of by                       | yte |

| Erasing method                                                       |     |

| Batch erasing and 2-division-block erasing (in CPU reprogramming mod | de) |

| <ul> <li>Program/Erase control by software command</li> </ul>        |     |

| • Number of times for programming/erasing 1                          | 00  |

#### **APPLICATION**

Control devices for personal computer peripheral equipment such as CD-ROM drives, hard disk drives, high density FDD, printers Control devices for office equipment such as copiers and facsimiles Control devices for industrial equipment such as communication and measuring instruments

Control devices for equipment required for motor control such as inverter air conditioner and general purpose inverter

# **FUNCTIONS (Microcomputer mode)**

| Parameter                         |                                | Functions                                                                                 |  |  |

|-----------------------------------|--------------------------------|-------------------------------------------------------------------------------------------|--|--|

| Number of basic machine instru    | ıctions                        | 109 (103 basic instructions of 7700 Family + 6 special instructions)                      |  |  |

| Instruction execution time        |                                | 100 ns (the fastest instruction at external clock 40 MHz frequency)                       |  |  |

| Mamanyaira                        | Flash memory                   | 120 Kbytes                                                                                |  |  |

| Memory size                       | RAM                            | 3968 bytes                                                                                |  |  |

| Innut/Outnut norto                | P0-P2, P4-P8                   | 8-bit × 8                                                                                 |  |  |

| Input/Output ports                | P3                             | 4-bit × 1                                                                                 |  |  |

| Multiple-function timers          | TA0, TA1, TA2, TA3, TA4        | 16-bit × 5                                                                                |  |  |

| Multiple-fullction timers         | TB0, TB1, TB2                  | 16-bit × 3                                                                                |  |  |

| Serial I/O                        |                                | (UART or clock synchronous serial I/O) × 2                                                |  |  |

| A-D converter                     |                                | 10-bit × 1(8 channels)                                                                    |  |  |

| D-A converter                     |                                | 8-bit × 2                                                                                 |  |  |

| Watchdog timer                    |                                | 12-bit × 1                                                                                |  |  |

| Dead-time timer                   |                                | 8-bit $\times$ 3                                                                          |  |  |

| Interrupts                        |                                | 5 external types, 16 internal types (Each interrupt can be set to priority levels 0 – 7.) |  |  |

| Clock generating circuit          |                                | Built-in (externally connected to a ceramic resonator or quartz crystal resonator         |  |  |

| Supply voltage                    |                                | 5 V±10 %                                                                                  |  |  |

| Power dissipation                 |                                | 125 mW (at external clock 40 MHz frequency)                                               |  |  |

| la mark/Outrout also marks mistic | Input/Output withstand voltage | 5 V                                                                                       |  |  |

| Input/Output characteristic       | Output current                 | 5 mA                                                                                      |  |  |

| Memory expansion                  |                                | Maximum 16 Mbytes                                                                         |  |  |

| Operating temperature range       |                                | −20 to 85 °C                                                                              |  |  |

| Device structure                  |                                | CMOS high-performance silicon gate process                                                |  |  |

| Package                           |                                | 80-pin plastic molded QFP                                                                 |  |  |

# **FUNCTIONS (Flash memory mode)**

|                            | Parameter               | Functions                                                           |  |  |

|----------------------------|-------------------------|---------------------------------------------------------------------|--|--|

| Supply voltage             |                         | 5 V ± 10 %                                                          |  |  |

| Program/Erase voltage      |                         | 12 V ± 5 %                                                          |  |  |

| Flash memory mode          |                         | 3 modes                                                             |  |  |

|                            |                         | (parallel I/O, serial I/O, CPU reprogramming)                       |  |  |

|                            | Parallel I/O mode       | Programming in unit of byte/120 Kbytes                              |  |  |

| Programming method         | Serial I/O mode         | Programming in unit of byte/120 Kbytes                              |  |  |

|                            | CPU reprogramming mode  | Programming in unit of byte/112 Kbytes                              |  |  |

|                            | Parallel I/O mode       | Batch erasing/120 Kbytes                                            |  |  |

| <b>.</b>                   | Serial I/O mode         | Batch erasing/120 Kbytes                                            |  |  |

| Erasing method             | CPU reprogramming mode  | Batch erasing/112 Kbytes or 2-division-block erasing                |  |  |

|                            | Cr o reprogramming mode | 2-division-block erasing: 56-Kbyte area to be erased is selectable. |  |  |

| Program/Erase control met  | hod                     | Program/Erase control by software command                           |  |  |

|                            | Parallel I/O mode       | 7 commands                                                          |  |  |

| Command number             | Serial IO mode          | 7 commands                                                          |  |  |

|                            | CPU reprogramming mode  | 7 commands                                                          |  |  |

| Number of times for Progra | ım/Erase                | 100                                                                 |  |  |

# M37753FFCFP M37753FFCHP

SHINGLE-CHIP 16-BIT CMOS MICROCOMPUTER FLASH MEMORY VERSION

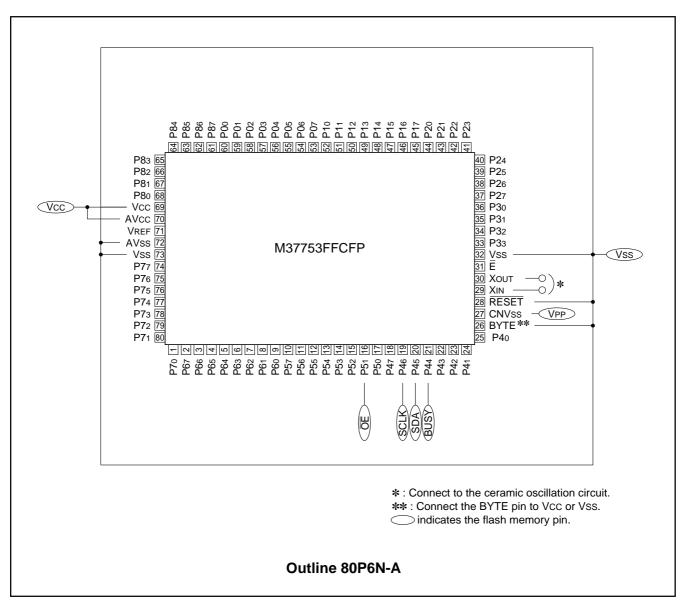

# PIN DESCRIPTION (MICROCOMPUTER MODE)

| Pin            | Name                    | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss       | Power supply            |                  | Supply 5 V±10 % to Vcc and 0 V to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CNVss          | CNVss input             | Input            | This pin controls the processor mode. Connect to Vss for single-chip mode or memory expansion mode. Connect to Vcc for microprocessor mode.                                                                                                                                                                                                                                                                                                                           |

| RESET          | Reset input             | Input            | This is reset input pin. The microcomputer is reset when supplying "L" level to this pin.                                                                                                                                                                                                                                                                                                                                                                             |

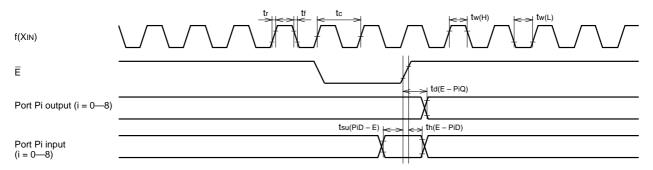

| XIN            | Clock input             | Input            | These are I/O pins of internal clock generating circuit. Connect a ceramic or quartz-crystal resonator between XIN and XOUT. When an external clock is used, the clock                                                                                                                                                                                                                                                                                                |

| Xout           | Clock output            | Output           | source should be connected to the XIN pin and the XOUT pin should be left open.                                                                                                                                                                                                                                                                                                                                                                                       |

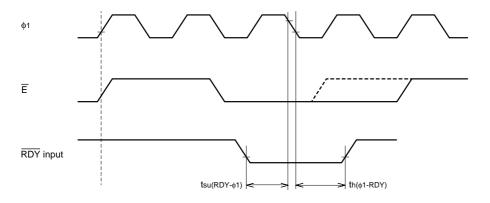

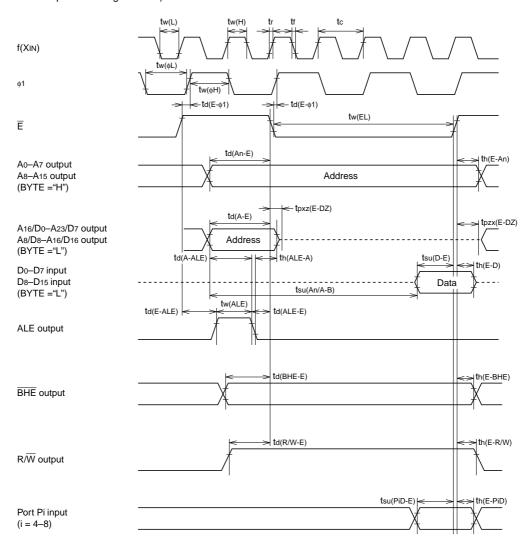

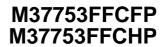

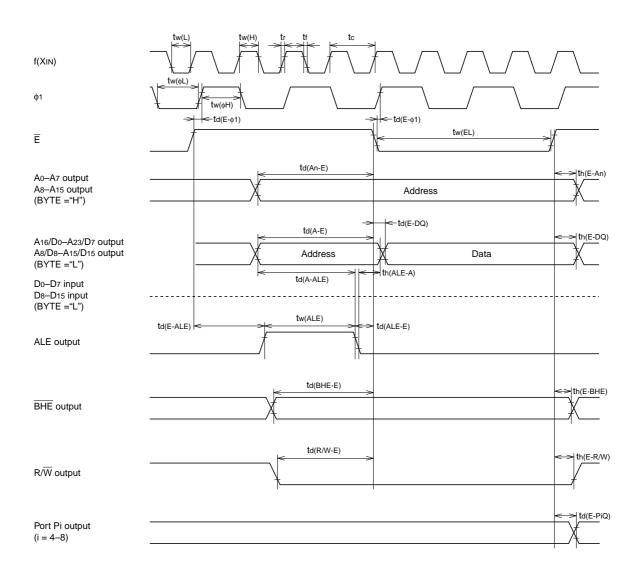

| Ē              | Enable output           | Output           | Data or instruction read, data write are performed when output from this pin is "L".                                                                                                                                                                                                                                                                                                                                                                                  |

| BYTE<br>(Note) | Bus width select input  | Input            | This pin determines whether the external data bus is 8-bit width or 16-bit width for memory expansion mode or microprocessor mode. The width is 16 bits when "L" signal inputs and 8 bits when "H" signal inputs.                                                                                                                                                                                                                                                     |

| AVCC,<br>AVSS  | Analog supply input     |                  | Power supply for the A-D converter and the D-A converter. Connect AVcc to Vcc and AVss to Vss externally.                                                                                                                                                                                                                                                                                                                                                             |

| VREF           | Reference voltage input | Input            | This is reference voltage input pin for the A-D converter and the D-A converter.                                                                                                                                                                                                                                                                                                                                                                                      |

| P00-P07        | I/O port P0             | I/O              | In single-chip mode, port P0 is an 8-bit I/O port. This port has an I/O direction register and each pin can be programmed for input or output. These ports are in the input mode when reset. Address (A0–A7) is output in memory expansion mode or microprocessor mode.                                                                                                                                                                                               |

| P10-P17        | I/O port P1             | I/O              | In single-chip mode, these pins have the same functions as port P0. When the BYTE pin is set to "L" in memory expansion mode or microprocessor mode and external data bus is 16-bit width, high-order data (D8–D15) is input or output if $\overline{\mathbb{E}}$ output is "L" and an address (A8–A15) is output if $\overline{\mathbb{E}}$ output is "H". When the BYTE pin is set to "H" and an external data bus is 8-bit width, only address (A8–A15) is output. |

| P20-P27        | I/O port P2             | I/O              | In single-chip mode, these pins have the same functions as port P0. In memory expansion mode or microprocessor mode, low-order data (D0–D7) is input or output when $\overline{E}$ output is "L" and an address (A16–A23) is output when $\overline{E}$ output is "H".                                                                                                                                                                                                |

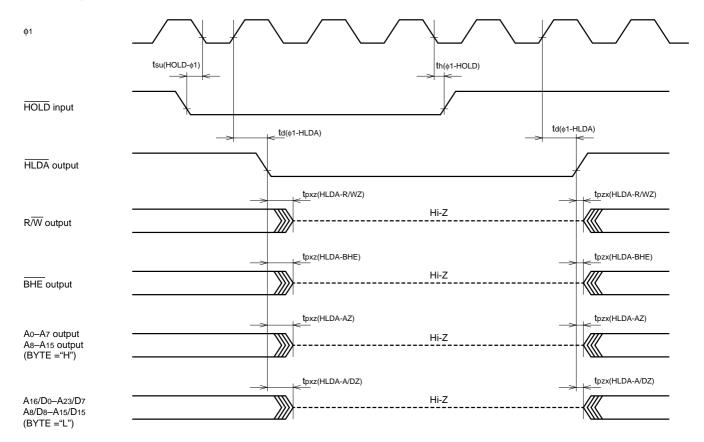

| P30-P33        | I/O port P3             | I/O              | In single-chip mode, these pins have the same functions as port <u>P0. In memory expansion mode or microprocessor mode</u> , R/W, BHE, ALE, and HLDA signals are output.                                                                                                                                                                                                                                                                                              |

| P40-P47        | I/O port P4             | I/O              | In single-chip mode, these pins have the same functions as port P0. In memory expansion mode or microprocessor mode, P40, P41, and P42 become $\overline{\text{HOLD}}$ and $\overline{\text{RDY}}$ input pins, and clock $\phi_1$ output pin respectively. Functions of other pins are the same as in single-chip mode. In memory expansion mode, P42 can be programmed as I/O port.                                                                                  |

| P50-P57        | I/O port P5             | I/O              | In addition to having the same functions as port P0 in single-chip mode, these pins also function as I/O pins for timer A0, timer A1, timer A2, timer A3, output pins for motor drive waveform, and input pins for key input interrupt.                                                                                                                                                                                                                               |

| P60-P67        | I/O port P6             | I/O              | In addition to having the same functions as port P0 in single-chip mode, these pins also function as the I/O pin for timer A4, input pins for external interrupt input INT0, INT1, and INT2, and input pins for timer B0, timer B1, and timer B2, and output pin for motor drive wave form.                                                                                                                                                                           |

| P70-P77        | I/O port P7             | I/O              | In addition to having the same functions as port P0 in single-chip mode, these pins also function as input pins for A-D converter.                                                                                                                                                                                                                                                                                                                                    |

| P80-P87        | I/O port P8             | I/O              | In addition to having the same functions as port P0 in single-chip mode, these pins also function as I/O pins for UART0, UART1, output pins for D-A converter, and input pins for INT3, INT4.                                                                                                                                                                                                                                                                         |

Note: It is impossible to change the input level of the BYTE pin in each bus cycle. In other words, bus width cannot be switched dynamically. Fix the input level of the BYTE pin to "H" or "L" according to the bus width used.

# PIN DESCRIPTION (FLASH MEMORY PARALLEL I/O MODE)

| Pin        | Name                    | Input<br>/Output | Functions                                                                                                                                                        |

|------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss   | Power supply            | _                | Supply 5 V ± 10 % to Vcc and 0 V to Vss.                                                                                                                         |

| CNVss      | VPP input               | Input            | Connect to 5 V ± 10 % in read-only mode, connect to 12 V ± 5 % in read/write mode.                                                                               |

| BYTE       | Bus width select input  | Input            | Connect to Vss.                                                                                                                                                  |

| RESET      | Reset input             | Input            | Connect to Vss.                                                                                                                                                  |

| XIN        | Clock input             | Input            | Connect a ceramic resonator between XIN and XOUT.                                                                                                                |

| Хоит       | Clock output            | Output           |                                                                                                                                                                  |

| Ē          | Enable output           | Output           | Keep it open.                                                                                                                                                    |

| AVcc, AVss | Analog supply input     | _                | Connect AVCC to VCC and AVss to Vss.                                                                                                                             |

| VREF       | Reference voltage input | Input            | Connect to Vss.                                                                                                                                                  |

| P00-P07    | Address input (A0-A7)   | Input            | Port P0 functions as 8-bit address input (A0–A7).                                                                                                                |

| P10-P17    | Address input (A8-A15)  | Input            | Port P1 functions as 8-bit address input (A8–A15).                                                                                                               |

| P20-P27    | Data I/O (D0-D7)        | I/O              | Function as 8-bit data's I/O pins (D0–D7).                                                                                                                       |

| P30-P33    | Input port P3           | Input            | Connect to Vss.                                                                                                                                                  |

| P40-P47    | Input port P4           | Input            | Keep P42 open. Connect P40, P41, P43–P47 to Vss.                                                                                                                 |

| P50-P57    | Control signal input    | Input            | P50, P51 and P52 function as the WE, OE and CE input pins respectively. P54 functions as the A16 input pin. Connect P53 to Vcc. Connect P55, P56 and P57 to Vss. |

| P60-P67    | Input port P6           | Input            | Connect to Vss.                                                                                                                                                  |

| P70-P77    | Input port P7           | Input            | Connect to Vss.                                                                                                                                                  |

| P80-P87    | Input port P8           | Input            | Connect to Vss.                                                                                                                                                  |

# PIN DESCRIPTION (FLASH MEMORY SERIAL I/O MODE)

| Pin             | Name                    | Input<br>/Output | Functions                                                                 |

|-----------------|-------------------------|------------------|---------------------------------------------------------------------------|

| Vcc, Vss        | Power supply            | _                | Supply 5 V ± 10 % to Vcc and 0 V to Vss.                                  |

| CNVss           | VPP input               | Input            | Connect to 12 V ± 5 %.                                                    |

| BYTE            | Bus width select input  | Input            | Connect to Vss or Vcc.                                                    |

| RESET           | Reset input             | Input            | Connect to Vss.                                                           |

| XIN             | Clock input             | Input            | Connect a ceramic resonator between XIN and XOUT.                         |

| Xout            | Clock output            | Output           |                                                                           |

| Ē               | Enable output           | Output           | "H" is output.                                                            |

| AVcc, AVss      | Analog supply input     | _                | Connect AVcc to Vcc and AVss to Vss.                                      |

| VREF            | Reference voltage input | Input            | Input an arbitrary level between the range of Vss and Vcc.                |

| P00-P07         | Input port P0           | Input            | Input "H" or "L", or keep them open.                                      |

| P10-P17         | Input port P1           | Input            | Input "H" or "L", or keep them open.                                      |

| P20-P27         | Input port P2           | Input            | Input "H" or "L", or keep them open.                                      |

| P30-P33         | Input port P3           | Input            | Input "H" or "L", or keep them open.                                      |

| P40–P43,<br>P47 | Input port P4           | Input            | Input "H" or "L" to P40, P41, P43, P47, or keep them open. Keep P42 open. |

| P44             | BUSY output             | Output           | This pin is for BUSY signal output.                                       |

| P45             | SDA I/O                 | I/O              | This pin is for serial data I/O.                                          |

| P46             | SCLK input              | Input            | This pin is for serial clock input.                                       |

| P50,<br>P52–P57 | Input port P5           | Input            | Input "H" or "L", or keep them open.                                      |

| P51             | Control signal input    | Input            | OE input pin                                                              |

| P60-P67         | Input port P6           | Input            | Input "H" or "L", or keep them open.                                      |

| P70-P77         | Input port P7           | Input            | Input "H" or "L", or keep them open.                                      |

| P80-P87         | Input port P8           | Input            | Input "H" or "L", or keep them open.                                      |

#### **BASIC FUNCTION BLOCKS**

The M37753FFCFP and the M37753FFCHP have the same functions as the M37753M8C-XXXGP and the M37753M8C-XXXHP except for the following.

Therefore, refer to the section on the M37753M8C-XXXGP and the M37753M8C-XXXHP.

- (1) Flash memory is included instead of ROM.

- (2) The memory size is different.

- (3) The memory area modification function is different.

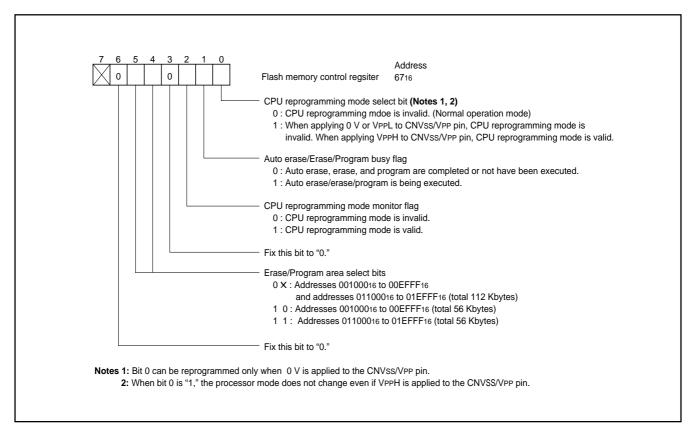

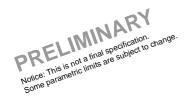

- (4) Part of the peripheral devices control registers is different. (Flash memory control register, flash command register, and bits

- 3, 4 of particular function select register 0 are added.)

#### **MEMORY**

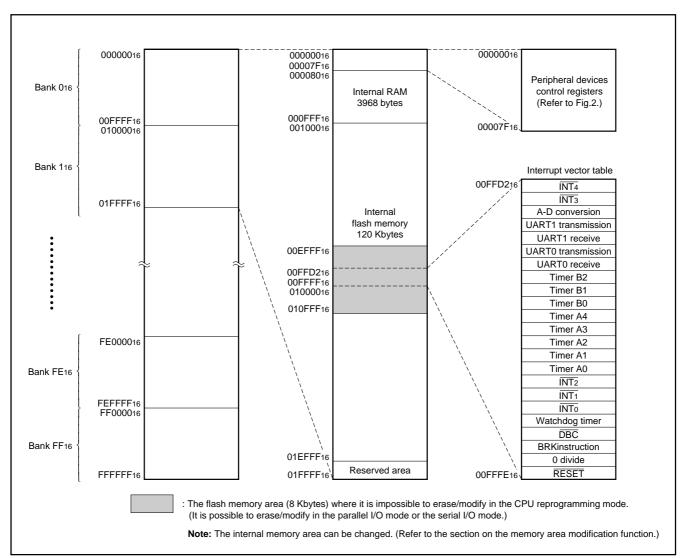

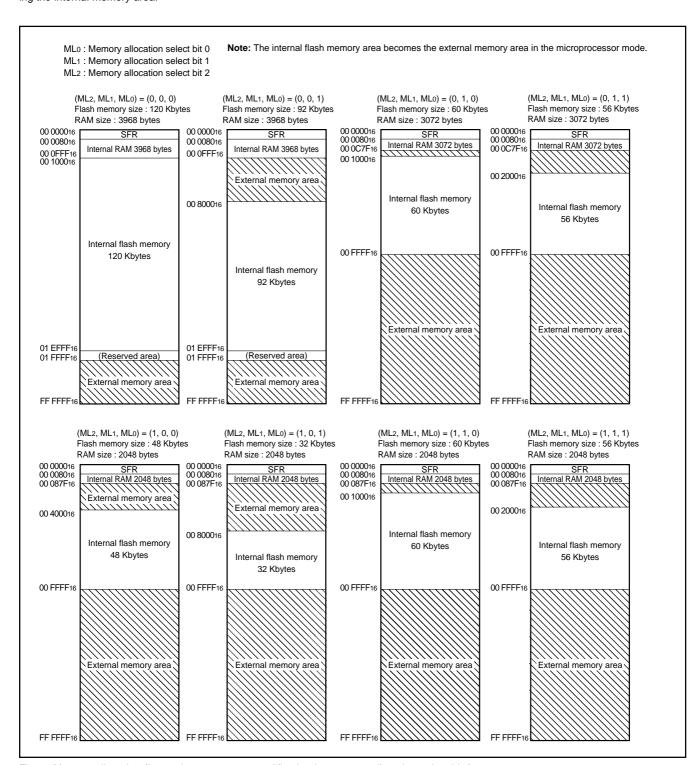

The memory map is shown in Figure 1.

Fig. 1 Memory map

| •                | decimal notation)                           | ,                | decimal notation)                                                            |

|------------------|---------------------------------------------|------------------|------------------------------------------------------------------------------|

| 000000           |                                             | 000040           | Count start register                                                         |

| 000001           | D + D0 - 1 +                                | 000041           |                                                                              |

| 000002           | Port P0 register                            | 000042           | One-shot start register                                                      |

| 000003           | Port PO direction register                  | 000043           | Up-down register                                                             |

| 000004<br>000005 | Port Pd direction register                  | 000044<br>000045 |                                                                              |

| 000005           | Port P1 direction register Port P2 register | 000045           | Timer A write register                                                       |

| 000007           | Port P3 register                            | 000047           | Timer A0 register                                                            |

| 000007           | Port P2 direction register                  | 000047           | A                                                                            |

| 000009           | Port P3 direction register                  | 000049           | Timer A1 register                                                            |

| 00000A           | Port P4 register                            | 00004A           | Timer A2 register                                                            |

| 00000B           | Port P5 register                            | 00004B           | Timer A2 register                                                            |

| 00000C           | Port P4 direction register                  | 00004C           | Timer A3 register                                                            |

| 00000D           | Port P5 direction register                  | 00004D           | Timer As register                                                            |

| 00000E           | Port P6 register                            | 00004E           | Timer A4 register                                                            |

| 00000F           | Port P7 register                            | 00004F           | Timos 711 register                                                           |

| 000010           | Port P6 direction register                  | 000050           | Timer B0 register                                                            |

| 000011           | Port P7 direction register                  | 000051           |                                                                              |

| 000012           | Port P8 register                            | 000052           | Timer B1 register                                                            |

| 000013           | Port P8 direction register                  | 000053           |                                                                              |

| 000014           | FUIL PO UITECTION REGISTER                  | 000054           | Timer B2 register                                                            |

| 000015<br>000016 |                                             | 000055<br>000056 | Timer A0 mode register                                                       |

| 000018           |                                             | 000057           | Timer A1 mode register                                                       |

| 000017           |                                             | 000057           | Timer A2 mode register                                                       |

| 000010           |                                             | 000059           | Timer A3 mode register                                                       |

| 000013<br>00001A | Waveform output mode register               | 000059<br>00005A | Timer A4 mode register                                                       |

| 00001R           | Dead-time timer                             | 00005R           | Timer B0 mode register                                                       |

| 00001D           | Pulse output data register 1                | 00005C           | Timer B1 mode register                                                       |

| 00001D           | Pulse output data register 0                | 00005D           | Timer B2 mode register                                                       |

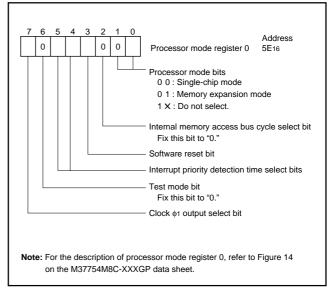

| 00001E           | A-D control register 0                      | 00005E           | Processor mode register 0                                                    |

| 00001F           | A-D control register 1                      | 00005F           | Processor mode register 1                                                    |

| 000020           |                                             | 000060           | Watchdog timer register                                                      |

| 000021           | A-D register 0                              | 000061           | Watchdog timer frequency select regsiter                                     |

| 000022           | A-D register 1                              | 000062           |                                                                              |

| 000023           | A-b register r                              | 000063           |                                                                              |

| 000024           | A-D register 2                              | 000064           | Comparator function select register                                          |

| 000025           | 77 D Togistor 2                             | 000065           | Flash command register                                                       |

| 000026           | A-D register 3                              | 000066           | Comparator result register                                                   |

| 000027           | <u> </u>                                    | 000067           | Flash memory control register                                                |

| 000028           | A-D register 4                              | 000068           | D-A register 0                                                               |

| 000029<br>00002A |                                             | 000069<br>00006A | D-A register 1                                                               |

| 00002A<br>00002B | A-D register 5                              | 00006A<br>00006B | D-A register 1                                                               |

| 00002B           |                                             | 00006C           | Particular function select register 0                                        |

| 00002C<br>00002D | A-D register 6                              | 00006C<br>00006D | Particular function select register 0  Particular function select register 1 |

| 00002D<br>00002E |                                             | 00006E           | INT4 interrupt control register                                              |

| 00002E           | A-D register 7                              | 00006E           | INT3 interrupt control register                                              |

| 000021           | UART0 transmit/receive mode register        | 000070           | A-D interrupt control register                                               |

| 000031           | UART0 baud rate register                    | 000071           | UART0 trasmit interrupt control register                                     |

| 000031           |                                             | 000071           | UART0 receive interrupt control register                                     |

| 000033           | UART0 transmit buffer register              | 000073           | UART1 trasmit interrupt control register                                     |

| 000034           | UART0 transmit/receive control register 0   | 000074           | UART1 receive interrupt control register                                     |

| 000035           | UART0 transmit/receive control register 1   | 000075           | Timer A0 interrupt control register                                          |

| 000036           |                                             | 000076           | Timer A1 interrupt control register                                          |

| 000037           | UART0 receive buffer register               | 000077           | Timer A2 interrupt control register                                          |

| 000038           | UART1 transmit/receive mode register        | 000078           | Timer A3 interrupt control register                                          |

| 000039           | UART1 baud rate register                    | 000079           | Timer A4 interrupt control register                                          |

| 00003A           | UART1 transmit buffer register              | 00007A           | Timer B0 interrupt control register                                          |

| 00003B           | Unit i transmit bullet legister             | 00007B           | Timer B1 interrupt control register                                          |

| 00003C           | UART1 transmit/receive control register 0   | 00007C           | Timer B2 interrupt control register                                          |

| 00003D           | UART1 transmit/receive control register 1   | 00007D           | INTo interrupt control register                                              |

| 00003E           | UART1 receive buffer register               | 00007E           | INT1 interrupt control register                                              |

| 00003F           | S 1 1 1000110 Dullot Toglotol               | 00007F           | INT2 interrupt control register                                              |

Fig. 2 Location of peripheral devices and interrupt control registers

|                                            | Address                             |                                                           | Address                               |

|--------------------------------------------|-------------------------------------|-----------------------------------------------------------|---------------------------------------|

| Port P0 direction register                 | (0416) 0016                         | Watchdog timer (6                                         | 6016)··· FFF16                        |

| Port P1 direction register                 | (0516) 0016                         | Watchdog timer frequency select register                  | (6116)                                |

| Port P2 direction register                 | (0816) 0 0 0 0 0 0 0                | Comparator function select register                       | (6416) 0016                           |

| Port P3 direction register                 | (0916)                              | Comparator result register                                | (6616) 0016                           |

| Port P4 direction register                 | (0C <sub>16</sub> ) 0016            | Flash memory control register                             | (6716)                                |

| Port P5 direction register                 | (0D16) 0016                         | D-A register 0                                            | (6816) 0016                           |

| Port P6 direction register                 | (1016) 0016                         | D-A register 1                                            | (6A <sub>16</sub> ) 0016              |

| Port P7 direction register                 | (1116) 0016                         | Particular function select register 0                     | (6C <sub>16</sub> ) 0016              |

| Port P8 direction register                 | (1416) 0016                         | Particular function select register 1                     | (6D <sub>16</sub> ) 0016              |

| Waveform output mode register              | (1A <sub>16</sub> ) 0016            | INT4 interrupt control register                           | (6E <sub>16</sub> )                   |

| Pulse output data register 1               | (1C <sub>16</sub> ) 0016            | INT3 interrupt control register                           | (6F <sub>16</sub> ) 0 0 0 0 0 0 0 0   |

| Pulse output data register 0               | (1D <sub>16</sub> ) 0 0 0 0 0 0     | A-D interrupt control register                            | (7016)                                |

| A-D control register 0                     | (1E <sub>16</sub> ) 0 0 0 0 ? ? ?   | UART 0 transmit interrupt control register                | (7116)                                |

| A-D control register 1                     | (1F <sub>16</sub> ) 0 0 0 0 0 1 1   | UART 0 receive interrupt control register                 | (7216)                                |

| UART 0 transmit/receive mode register      | (3016) 0016                         | UART 1 transmit interrupt control register                | (7316)                                |

| UART 1 transmit/receive mode register      | (3816) 0016                         | UART 1 receive interrupt control register                 | (7416)                                |

| UART 0 transmit/receive control register 0 | (3416)                              | Timer A0 interrupt control register                       | (7516)                                |

| UART 1 transmit/receive control register 0 | (3C <sub>16</sub> ) 0 1 0 0 0       | Timer A1 interrupt control register                       | (7616)                                |

| UART 0 transmit/receive control register 1 | (3516)                              | Timer A2 interrupt control register                       | (7716)                                |

| UART 1 transmit/receive control register 1 | (3D <sub>16</sub> ) 0 0 0 0 0 1 0   | Timer A3 interrupt control register                       | (7816)                                |

| Count start register                       | (4016) 0016                         | Timer A4 interrupt control register                       | (7916)                                |

| One-shot start register                    | (4216)                              | Timer B0 interrupt control register                       | (7A <sub>16</sub> )                   |

| Up-down register                           | (4416)                              | Timer B1 interrupt control register                       | (7B <sub>16</sub> )                   |

| Timer A write register                     | (4516)                              | Timer B2 interrupt control register                       | (7C <sub>16</sub> )                   |

| Timer A0 mode register                     | (5616) 0016                         | INTo interrupt control register                           | (7D <sub>16</sub> )                   |

| Timer A1 mode register                     | (5716) 0016                         | INT1 interrupt control register                           | (7E <sub>16</sub> )                   |

| Timer A2 mode register                     | (5816) 0016                         | INT2 interrupt control register                           | (7F <sub>16</sub> )                   |

| Timer A3 mode register                     | (5916) 0016                         | Processor status register PS                              | 0 0 0 ? ? 0 0 0 1 ? ?                 |

| Timer A4 mode register                     | (5A <sub>16</sub> ) 0016            | Program bank register PG                                  | 0016                                  |

| Timer B0 mode register                     | (5B <sub>16</sub> ) 0 0 1 0 0 0     | Program counter PCH                                       | Contents of FFFF16                    |

| Timer B1 mode register                     | (5C <sub>16</sub> ) 0 0 1 0 0 0     | Program counter PCL                                       | Contents of FFFE16                    |

| Timer B2 mode register                     | (5D <sub>16</sub> ) 0 0 1 0 0 0     | Direct page register DPR                                  | 000016                                |

| Processor mode register 0                  | (5E <sub>16</sub> ) 0 0 0 0 0 0 0 0 | Data bank register DT                                     | 0016                                  |

| Processor mode register 1                  | (5F <sub>16</sub> ) 0016            | Contents of other registers and RA itiallzed by software. | M are not initiallzed and must be in- |

Fig. 3 Microcomputer internal registers status after reset

#### MEMORY AREA MODIFICATION FUNCTION

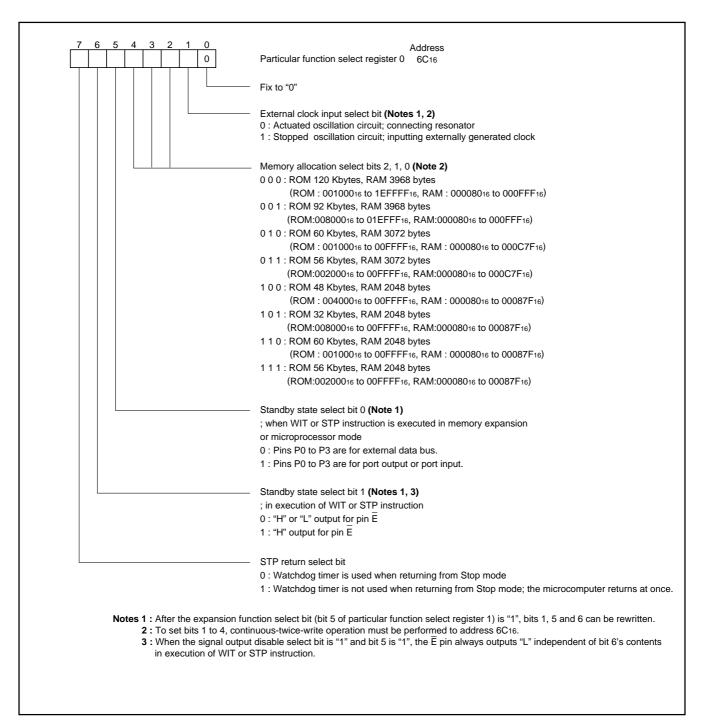

For the M37753FFCFP and the M37753FFCHP, the internal memory's size and address area can be changed by setting bits 2, 3, 4 (memory allocation select bits) of the particular function select register 0 (see figure 5). Figure 4 shows the memory map when changing the internal memory area.

Fig. 4 Memory allocation (Internal memory area modification by memory allocation select bits)

Fig. 5 Particular function select register 0 bit configuration

#### **FLASH MEMORY MODE**

The M37753FFCFP and the M37753FFCHP have the flash memory mode in addition to the normal operation mode (microcomputer mode). The user can use this mode to perform read, program, and erase operations for the internal flash memory.

The M37753FFCFP and the M37753FFCHP have three modes the user can choose: the parallel input/output and serial input/output mode, where the flash memory is handled by using the external programmer, and the CPU reprogramming mode, where the flash memory is handled by the central processing unit (CPU). The following explains these modes.

#### Flash memory mode 1 (parallel I/O mode)

The parallel I/O mode can be selected by connecting wires as shown in Figures 6, 7 and supplying power to the Vcc and VPP pins. In this mode, the M37753FFCFP and the M37753FFCHP operate as an equivalent of MITSUBISHI's CMOS flash memory M5M28F101. However, because the M37753FFCFP and the M37753FFCHP's internal memory has a capacity of 120 Kbytes, programming is available for addresses 0100016 to 1EFFF16, and make sure that the data in addresses 0000016 to 00FFF16 and addresses 1F00016 to 1FFFF16 are FF16. Note also that the M37753FFCFP and the M37753FFCHP do not contain a facility to read out a device identification code by applying a high voltage to address input (A9). Be careful not to erratically set program conditions when using a general-purpose PROM programmer.

Table 1 shows the pin assignments when operating in the parallel input/output mode.

Table 1. Pin assignments of M37753FFCFP and M37753FFCHP when operating in the parallel input/output mode

|               | M37753FFCFP/CHP   | M5M28F101 |

|---------------|-------------------|-----------|

| Vcc           | Vcc               | Vcc       |

| VPP           | CNVss             | VPP       |

| Vss           | Vss               | Vss       |

| Address input | Ports P0, P1, P54 | A0-A16    |

| Data I/O      | Port P2           | D0-D7     |

| CE            | P52               | CE        |

| OE            | P51               | ŌĒ        |

| WE            | P50               | WE        |

# Functional outline (Parallel input/output mode)

In the parallel input/output mode, the M37753FFCFP and the M37753FFCHP allow the user to choose an operation mode between the read-only mode and the read/write mode (software command control mode) depending on the voltage applied to the VPP pin. When VPP = VPPL, the read-only mode is selected, and the user can choose one of three states (e.g., read, output disable, or standby) depending on inputs to the  $\overline{\text{CE}}$ ,  $\overline{\text{OE}}$ , and  $\overline{\text{WE}}$  pins. When VPP = VPPH, the read/write mode is selected, and the user can choose one of four states (e.g., read, output disable, standby, or write) depending on inputs to the  $\overline{\text{CE}}$ ,  $\overline{\text{OE}}$ , and  $\overline{\text{WE}}$  pins. Table 2 shows assignment states of control input and each state.

#### Read

The microcomputer enters the read state by driving the  $\overline{CE}$ , and  $\overline{OE}$  pins low and the  $\overline{WE}$  pin high; and the contents of memory corresponding to the address to be input to address input pins (A0–A16). are output to the data input/output pins (D0–D7).

#### **Output disable**

The microcomputer enters the output disable state by driving the  $\overline{\text{CE}}$  pin low and the  $\overline{\text{WE}}$  and  $\overline{\text{OE}}$  pins high; and the data input/output pins enter the floating state.

#### Standby

The microcomputer enters the standby state by driving the  $\overline{\text{CE}}$  pin high. The M37753FFCFP and the M37753FFCHP are placed in a power-down state consuming only a minimal supply current. At this time, the data input/output pins enter the floating state.

#### Write

The microcomputer enters the write state by driving the VPP pin high (VPP = VPPH) and then the  $\overline{WE}$  pin low when the  $\overline{CE}$  pin is low and the  $\overline{OE}$  pin is high. In this state, software commands can be input from the data input/output pins, and the user can choose program or erase operation depending on the contents of this software command.

Table 2. Assignment sates of control input and each state

| Mode         | Pin State      | CE  | ŌĒ  | WE  | VPP  | Data I/O |

|--------------|----------------|-----|-----|-----|------|----------|

|              | Read           | VIL | VIL | ViH | VPPL | Output   |

| Read-only    | Output disable | VIL | VIH | ViH | VPPL | Floating |

|              | Standby        | VIH | ×   | ×   | VPPL | Floating |

|              | Read           | VIL | VIL | ViH | VPPH | Output   |

| Read/Write   | Output disable | VIL | VIH | ViH | VPPH | Floating |

| rtead/vviite | Standby        | ViH | ×   | ×   | VPPH | Floating |

|              | Write          | VIL | VIH | VIL | VPPH | Input    |

Note:  $\times$  can be VIL or VIH.

Fig. 6 Pin connection of M37753FFCFP when operating in parallel input/output mode

Fig. 7 Pin connection of M37753FFCHP when operating in parallel input/output mode

# Read-only mode

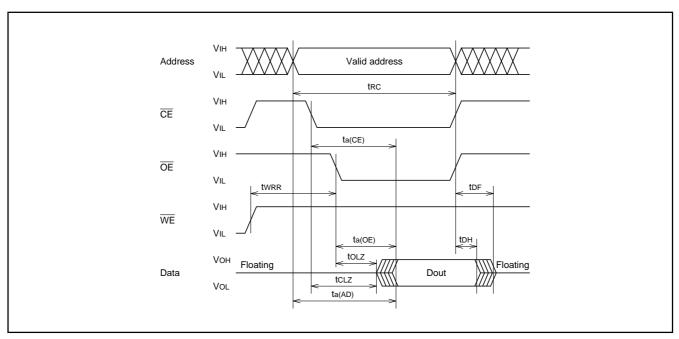

The microcomputer enters the read-only mode by applying VPPL to the VPP pin. In this mode, the user can input the address of a memory location to be read and the control signals at the timing shown in Figure 8, and the M37753FFCFP and the M37753FFCHP will output the contents of the user's specified address from data I/O pin to the external. In this mode, the user cannot perform any operation other than read.

Fig. 8 Read timing

# Read/Write mode

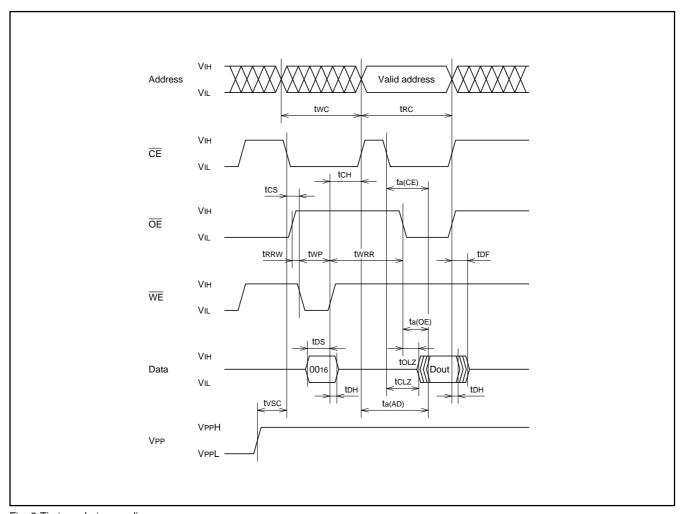

The microcomputer enters the read/write mode by applying VPPH to the VPP pin. In this mode, the user must first input a software command to choose the operation (e. g., read, program, or erase) to be performed on the flash memory (this is called the first cycle), and then input the information necessary for execution of the command (e.g., address and data) and control signals (this is called the second cycle). When this is done, the M37753FFCFP and the M37753FFCHP execute the specified operation.

Table 3 shows the software commands and the input/output information in the first and the second cycles. The input address is latched internally at the falling edge of the  $\overline{\text{WE}}$  input; software commands and other input data are latched internally at the rising edge of the  $\overline{\text{WE}}$  input.

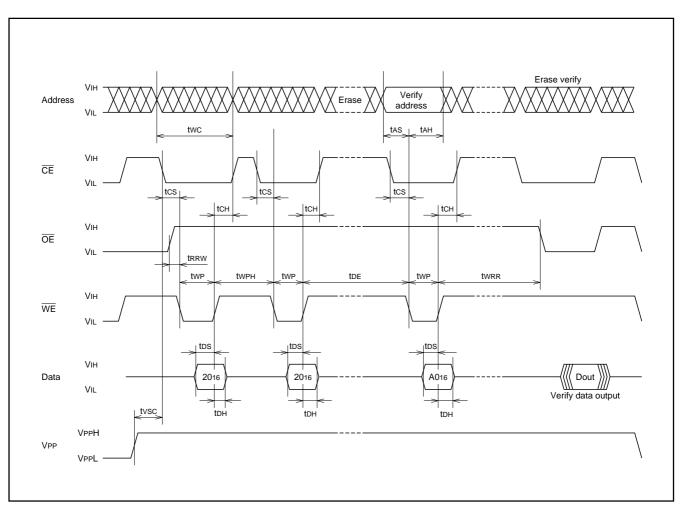

The following explains each software command. Refer to Figures 9 to 11 for details about the signal input/output timings.

Table 3. Software command (Parallel input/output mode)

| Symbol                | First          | cycle      | Second cycle    |                      |  |

|-----------------------|----------------|------------|-----------------|----------------------|--|

|                       | Address input  | Data input | Address input   | Data I/O             |  |

| Read                  | ×              | 0016       | Read address    | Read data (Output)   |  |

| Program               | ×              | 4016       | Program address | Program data (Input) |  |

| Program verify        | ×              | C016       | ×               | Verify data (Output) |  |

| Erase                 | ×              | 2016       | ×               | 2016 (Input)         |  |

| Erase verify          | Verify address | A016       | ×               | Verify data (Output) |  |

| Reset                 | ×              | FF16       | ×               | FF16 (Input)         |  |

| Device identification | ×              | 9016       | ADI             | DDI (Output)         |  |

Note: ADI = Device identification address : manufacturer's code 0000016, device code 0000116

DDI = Device identification data : manufacturer's code 1C16, device code D016

X can be VIL or VIH.

#### Read command

The microcomputer enters the read mode by inputting command code "0016" in the first cycle. The command code is latched into the internal command latch at the rising edge of the  $\overline{\text{WE}}$  input. When the address of a memory location to be read is input in the second cycle, with control signals input at the timing shown in Figure 9, the M37753FFCFP and the M37753FFCHP output the contents of the specified address from the data I/O pins to the external.

The read mode is retained until any other command is latched into the command latch. Consequently, once the M37753FFCFP and the M37753FFCHP enter the read mode, the user can read out the successive memory contents simply by changing the input address and executing the second cycle only. Any command other than the read command must be input beginning from its command code over again each time the user execute it. The contents of the command latch immediately after power-on is 0016.

Fig. 9 Timings during reading

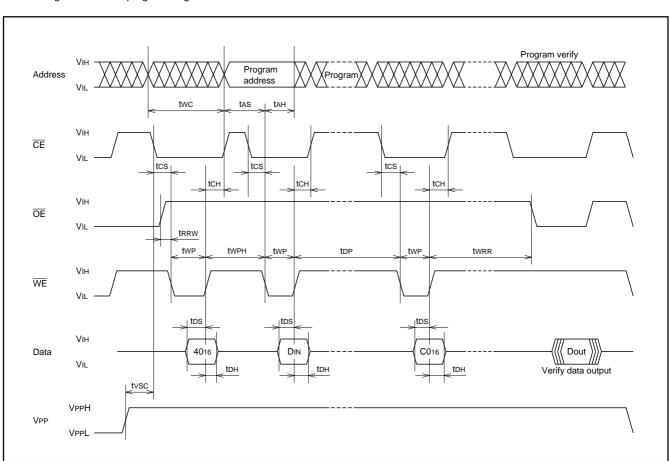

#### **Program command**

The microcomputer enters the program mode by inputting command code "4016" in the first cycle. The command code is latched into the internal command latch at the rising edge of the  $\overline{WE}$  input. When the address which indicates a program location and data are input in the second cycle, the M37753FFCPP and the M37753FFCHP internally latch the address at the falling edge of the  $\overline{WE}$  input and the data at the rising edge of the  $\overline{WE}$  input. The M37753FFCPP and the M37753FFCHP start programming at the rising edge of the  $\overline{WE}$  input in the second cycle and finishes programming within 10  $\mu s$  as measured by its internal timer. Programming is performed in units of bytes.

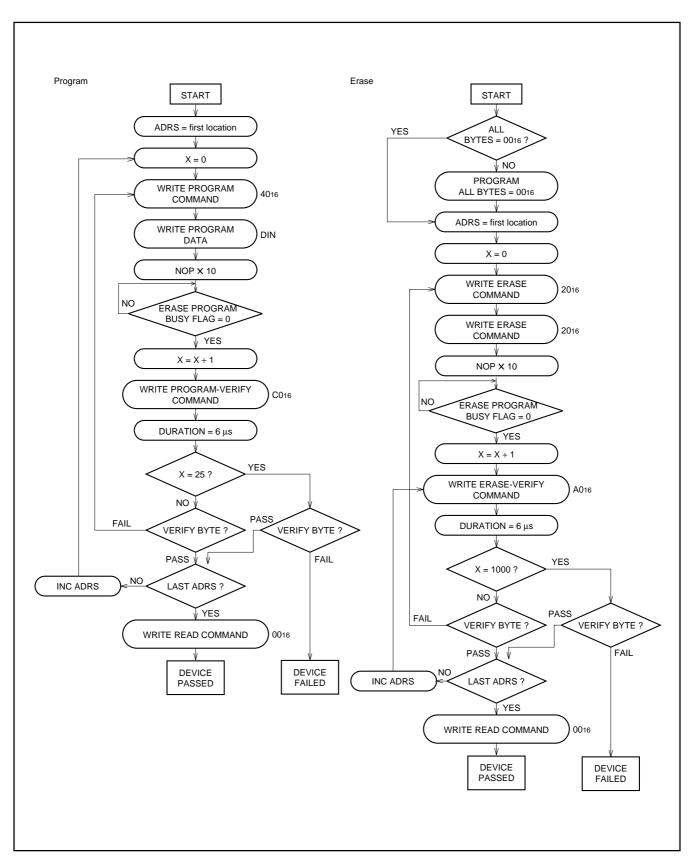

Note: A programming operation is not completed by executing the program command once. Always be sure to execute a program verify command after executing the program command. When the failure is found in this verification, the user must repeatedly execute the program command until the pass. Refer to Figure 12 for the programming flowchart.

# **Program verify command**

The microcomputer enters the program verify mode by inputting command code "C016" in the first cycle. This command is used to verify the programmed data after executing the program command. The command code is latched into the internal command latch at the rising edge of the  $\overline{\text{WE}}$  input. When control signals are input in the second cycle at the timing shown in Figure 10, the M37753FFCFP and the M37753FFCHP output the programmed address's contents to the external. Since the address is internally latched when the program command is executed, there is no need to input it in the second cycle.

Fig. 10 Input/output timings during programming (Verify data is output at the same timing as for read.)

#### **Erase command**

The erase command is executed by inputting command code 2016 in the first cycle and command code 2016 again in the second cycle. The command code is latched into the internal command latch at the rising edges of the WE input in the first cycle and in the second cycle, respectively. The erase operation is initiated at the rising edge of the WE input in the second cycle, and the memory contents are collectively erased within 9.5 ms as measured by the internal timer. Note that data 0016 must be written to all memory locations before executing the erase command.

**Note:** An erase operation is not completed by executing the erase command once. Always be sure to execute an erase verify command after executing the erase command. When the failure is found in this verification, the user must repeatedly execute the erase command until the pass. Refer to Figure 12 for the erase flowchart.

# **Erase verify command**

The user must verify the contents of all addresses after completing the erase command. The microcomputer enters the erase verify mode by inputting the verify address and command code A016 in the first cycle. The address is internally latched at the falling edge of the  $\overline{\text{WE}}$  input, and the command code is internally latched at the rising edge of the  $\overline{\text{WE}}$  input. When control signals are input in the second cycle at the timing shown in Figure 11, the M37753FFCFP and the M37753FFCHP output the contents of the specified address to the external.

Note: If any memory location where the contents have not been erased is found in the erase verify operation, execute the operation of "erase → erase verify" over again. In this case, however, the user does not need to write data 0016 to memory locations before erasing.

Fig. 11 Input/output timings during erasing (Verify data is output at the same timing as for read.)

#### Reset command

The reset command provides a means of stopping execution of the erase or program command safely. If the user inputs command code FF16 in the second cycle after inputting the erase or program command in the first cycle and again input command code FF16 in the third cycle, the erase or program command is disabled (i.e., reset), and the M37753FFCFP and the M37753FFCHP are placed in the read mode. If the reset command is executed, the contents of the memory does not change.

# **Device identification code command**

By inputting command code 9016 in the first cycle, the user can read out the device identification code. The command code is latched into the internal command latch at the rising edge of the  $\overline{\text{WE}}$  input. At this time, the user can read out manufacture's code 1C16 (i.e., MITSUBISHI) by inputting 000016 to the address input pins in the second cycle; the user can read out device code D016 (i. e., 1M-bit flash memory) by inputting 000116.

These command and data codes are input/output at the same timing as for read.

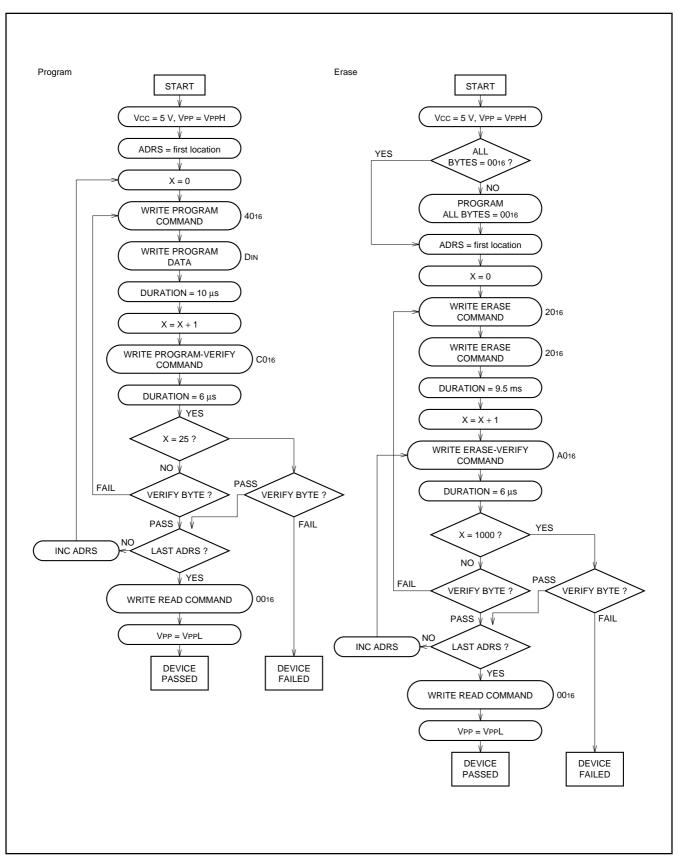

Fig. 12 Programming/Erasing algorithm flow chart

# DC ELECTRICAL CHARACTERISTICS (Ta = 25 °C, Vcc = 5 V ± 10 %, unless otherwise noted)

| Symbol | Domester.                       | To at a smallting a                                                                      |      | Limits |           |      |

|--------|---------------------------------|------------------------------------------------------------------------------------------|------|--------|-----------|------|

| Symbol | Parameter                       | Test conditions                                                                          | Min. | Тур.   | Max.      | Unit |

| ISB1   |                                 | VCC = 5.5 V, $\overline{\text{CE}}$ = VIH                                                |      |        | 1         | mA   |

| ISB2   | Vcc supply current (at standby) | $\frac{\text{VCC} = 5.5 \text{ V},}{\text{CE} = \text{VCC} \pm 0.2 \text{ V}}$           |      |        | 100       | μΑ   |

| ICC1   | Vcc supply current (at read)    | $VCC = 5.5 \text{ V}, \overline{CE} = VIL,$<br>tRC = 150  ns, IOUT = 0  mA               |      |        | 30        | mA   |

| ICC2   | Vcc supply current (at program) | VPP = VPPH                                                                               |      |        | 30        | mA   |

| Іссз   | Vcc supply current (at erase)   | VPP = VPPH                                                                               |      |        | 30        | mA   |

|        | VPP supply current (at read)    | 0≤Vpp≤Vcc                                                                                |      |        | 10        | μΑ   |

| IPP1   |                                 | VCC <vpp≤vcc +="" 1.0="" td="" v<=""><td></td><td></td><td>100</td><td>μΑ</td></vpp≤vcc> |      |        | 100       | μΑ   |

|        |                                 | VPP = VPPH                                                                               |      |        | 100       | μΑ   |

| IPP2   | VPP supply current (at program) | VPP = VPPH                                                                               |      |        | 30        | mA   |

| IPP3   | VPP supply current (at erase)   | VPP = VPPH                                                                               |      |        | 30        | mA   |

| VPPL   | VPP supply voltage (read only)  |                                                                                          | Vcc  |        | Vcc + 1.0 | V    |

| VPPH   | VPP supply voltage (read/write) |                                                                                          | 11.4 | 12.0   | 12.6      | V    |

Note: VIH, VIL, VOH, VOL, IIH, and IIL for the control input, address input, and data input/output pins conform to the standards for microcomputer modes (e.g., memory expansion and microprocessor modes).

# AC ELECTRICAL CHARACTERISTICS (Ta = 25 °C, Vcc = 5 V ± 10 %, unless otherwise noted)

# Read-only mode

| Symbol | Parameter                                          | Limits |      | Llait |

|--------|----------------------------------------------------|--------|------|-------|

|        |                                                    | Min.   | Max. | Unit  |

| trc    | Read cycle time                                    | 150    |      | ns    |

| ta(AD) | Address access time                                |        | 150  | ns    |

| ta(CE) | CE access time                                     |        | 150  | ns    |

| ta(OE) | OE access time                                     |        | 55   | ns    |

| tCLZ   | Output enable time (after CE)                      | 0      |      | ns    |

| tolz   | Output enable time (after $\overline{\text{OE}}$ ) | 0      |      | ns    |

| tDF    | Output floating time (after OE)                    |        | 35   | ns    |

| tDH    | Output valid time (after CE, OE, address)          | 0      |      | ns    |

| twrr   | Write recovery time (before read)                  | 6      |      | μs    |

# Read/Write mode

| Symbol | Parameter.                        | Limits |      | Unit |

|--------|-----------------------------------|--------|------|------|

|        | Parameter                         |        | Max. |      |

| twc    | Write cycle time                  | 150    |      | ns   |

| tAS    | Address set up time               | 0      |      | ns   |

| tah    | Address hold time                 | 60     |      | ns   |

| tDS    | Data setup time                   | 50     |      | ns   |

| tDH    | Data hold time                    | 10     |      | ns   |

| twrr   | Write recovery time (before read) | 6      |      | μs   |

| trrw   | Read recovery time (before write) | 0      |      | μs   |

| tcs    | CE setup time                     | 20     |      | ns   |

| tCH    | CE hold time                      | 0      |      | ns   |

| tWP    | Write pulse width                 | 60     |      | ns   |

| tWPH   | Write pulse waiting time          | 20     |      | ns   |

| tDP    | Program time                      | 10     |      | μs   |

| tDE    | Erase time                        | 9.5    |      | ms   |

| tvsc   | VPP setup time                    | 1      |      | μs   |

Note: The read timing in the read/write mode is the same timing as in the read-only mode.

# Flash memory mode 2 (serial I/O mode)

The M37753FFCFP and the M37753FFCHP have a function to serially input/output the software commands, addresses, and data required for operation on the internal flash memory (e. g., read, program, and erase) using only a few pins. This is called the serial I/ O (input/output) mode. This mode can be selected by driving the SDA (serial data input/output), SCLK (serial clock input ), and  $\overline{\text{OE}}$

pins high after connecting wires as shown in Figures 13, 14 and powering on the Vcc pin and then applying VPPH to the VPP pin.

In the serial I/O mode, the user can use seven types of software commands: bank (0, 1) select, read, program, program verify, auto erase, and error check.

Serial input/output is accomplished synchronously with the clock, beginning from the LSB (LSB first).

Fig. 13 Pin connection of M37753FFCFP when operating in serial I/O mode

Fig. 14 Pin connection of M37753FFCHP when operating in serial I/O mode

# Functional outline (Serial I/O mode)

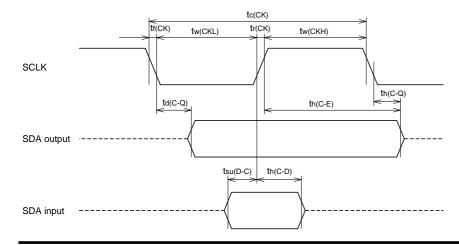

In the serial I/O mode, data is transferred synchronously with the clock using serial input/output. The input data is read from the SDA pin into the internal circuit synchronously with the rising edge of the serial clock pulse; the output data is output from the SDA pin synchronously with the falling edge of the serial clock pulse. Data is

transferred in units of eight bits.

In the first transfer, the user inputs the command code. This is followed by address input and data input/output according to the contents of the command. Table 4 shows the software commands used in the serial I/O mode. The following explains each software command.

Table 4. Software command (Serial I/O mode)

| Number of transfers | First command | Second                    | Third                     | Fourth               |  |

|---------------------|---------------|---------------------------|---------------------------|----------------------|--|

| Command             | code input    | Second                    | Tillia                    | T Guitii             |  |

| Bank 0 select       | E016          | <del></del>               | <del></del>               |                      |  |

| Bank 1 select       | E116          | <del></del>               | <del></del>               |                      |  |

| Read                | 0016          | Read address L (Input)    | Read address H (Input)    | Read data (Output)   |  |

| Program             | 4016          | Program address L (Input) | Program address H (Input) | Program data (Input) |  |

| Program verify      | C016          | Verify data (Output)      |                           |                      |  |

| Auto erase          | 3016          | 3016 (Input)              |                           |                      |  |

| Error check         | 8016          | Error code (Output)       |                           |                      |  |

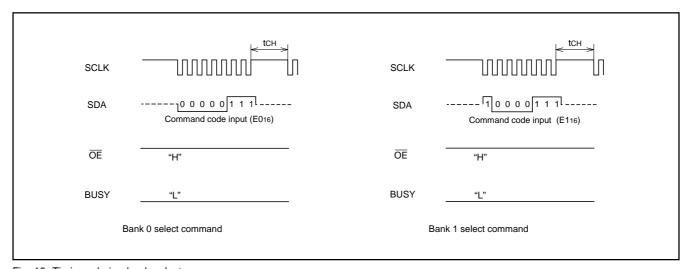

#### Bank select command

This is the command which specifies the bank of the flash memory, which is to be read/programmed, before executing the read command or the program command (and the program verify command). There are the bank 0 select command (command code "E016"), which selects bank 0 (addresses 0000016 to 0FFFF16), and the bank 1 select command (command code "E116"), which selects bank 1 (addresses 1000016 to 1FFFF16).

When any bank select command is input once, specified bank is

valid until the next bank select command is input. Accordingly, when the read command or the program command (and the program verify command) is executed to plural bytes in the same bank, if any bank select command is input first, it is unnecessary to input the bank select command again for the following bytes. When selecting the serial I/O mode (before bank command input), bank 0 is selected.

**Note:** Bank select command does not affect the auto erase command, that is to say, when executing the auto erase command, all flash memory is erased collectively regardless of specified bank.

And in the same way, the bank select command does not affect the error check command.

Fig. 15 Timings during bank select

# M37753FFCFP M37753FFCHP

#### SHINGLE-CHIP 16-BIT CMOS MICROCOMPUTER FLASH MEMORY VERSION

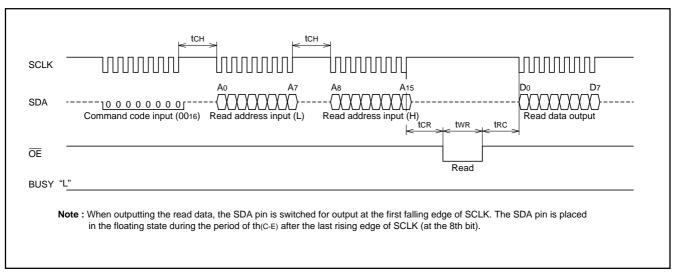

#### Read command

Input command code 0016 in the first transfer. Proceed and input the low-order 8 bits and the high-order 8 bits of the address and pull the  $\overline{\text{OE}}$  pin low. When this is done, the M37753FFCFP and the M37753FFCHP read out the contents of the specified address, and

then latch it into the internal data latch. When the  $\overline{OE}$  pin is released back high and serial clock is input to the SCLK pin, the read data that has been latched into the data latch is serially output from the SDA pin.

Fig. 16 Timings during reading

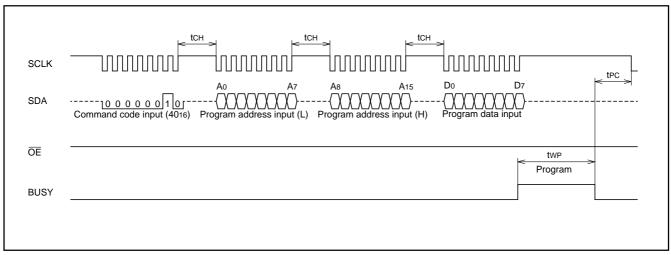

# **Program command**

Input command code 4016 in the first transfer. Proceed and input the low-order 8 bits and the high-order 8 bits of the address and then program data. Programming is initiated at the last rising edge of the serial clock during program data transfer. The BUSY pin is driven high during program operation. Programming is completed within 10  $\mu s$  as measured by the built-in timer, and the BUSY pin is pulled low.

Note: A programming operation is not completed by executing the program command once. Always be sure to execute a program verify command after executing the program command. In the case of failure in the verification, the user must repeatedly execute the program command until the pass in the verification. Refer to Figure 12 for the programming flowchart.

Fig. 17 Timings during programming

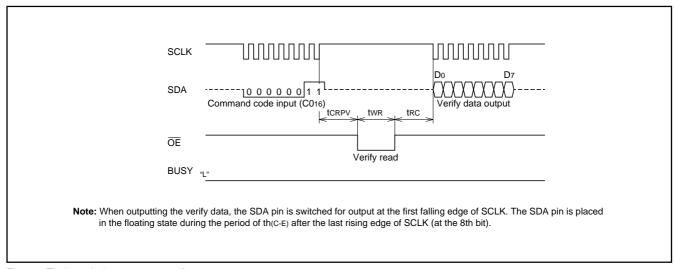

# Program verify command

Input command code C016 in the first transfer. Proceed and drive the  $\overline{\text{OE}}$  pin low. When this is done, the M37753FFCFP and the M37753FFCHP verify-read the programmed address's contents,

and then latch it into the internal data latch. When the  $\overline{\text{OE}}$  pin is released back high and serial clock is input to the SCLK pin, the verify data that has been latched into the data latch is serially output from the SDA pin.

Fig. 18 Timings during program verify

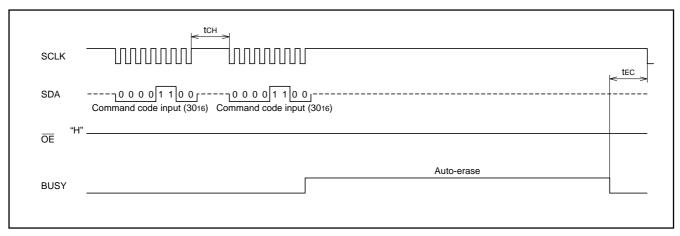

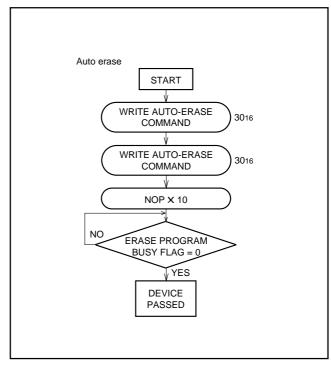

#### Auto erase command

Input command code 3016 in the first transfer and command code 3016 again in the second transfer. When this is done, the M37753FFCFP and the M37753FFCHP execute an auto erase command. Auto erase is initiated at the last rising edge of the serial clock. The BUSY pin is driven high during the auto erase operation. Auto

erase is completed when all memory contents are erased, and the BUSY pin is pulled low.

**Note:** In the auto erase operation, the M37753FFCFP and the M37753FFCHP automatically repeat the erase and verify operations internally. Therefore, erase is completed by executing the command once.

Fig. 19 Timings at auto-erasing

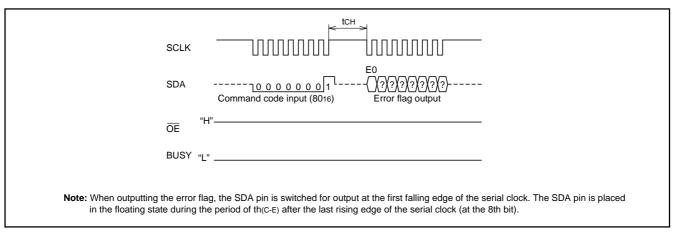

#### **Error check command**

Input command code 8016 in the first transfer, and the M37753FFCFP and the M37753FFCHP output error information from the SDA pin, beginning at the next falling edge of the serial clock. If the E0 of the 8-bit error information is 1, it indicates that a command error has occurred. A command error means that some invalid commands other than commands shown in Table 4 has been input.

When a command error occurs, the serial communication circuit sets the corresponding flag and stops functioning to avoid an erroneous programming or erase. When being placed in this state, the serial communication circuit does not accept the subsequent serial clock and data (even including an error check command). Therefore, if the

user wants to execute an error check command, temporarily drop the VPP pin input to the VPPL level to terminate the serial input/output mode. Then, place the M37753FFCFP and the M37753FFCHP into the serial I/O mode back again. The serial communication circuit is reset by this operation and is ready to accept commands. The error flag alone is not cleared by this operation, so the user can examine the serial communication circuit's error conditions before reset. This examination is done by the first execution of an error check command after the reset. The error flag is cleared when the user has executed the error check command. Because the error flag is undefined immediately after power-on, always be sure to execute the error check command.

Fig. 20 Timings at error checking

DC ELECTRICAL CHARACTERISTICS (Ta = 25 °C, Vcc = 5 V ± 10 %, VPP = 12 V ± 5 %, unless otherwise noted) Icc, IPP-relevant standards during read, program, and erase are the same as in the parallel input/output mode. VIH, VIL, VOH, VOL, IIH, and IIL for the SCLK, SDA, BUSY,  $\overline{OE}$  pins conform to the microcomputer modes.

#### **AC ELECTRICAL CHARACTERISTICS**

(Ta = 25 °C, Vcc = 5 V  $\pm$  10 %, VPP = 12 V  $\pm$  5 %, f(XIN) = 40 MHz, unless otherwise noted)

| Symbol   | Parameter                               | Lin         | Limits      |      |

|----------|-----------------------------------------|-------------|-------------|------|

|          |                                         | Min.        | Max.        | Unit |

| tch      | Serial transmission interval            | 400(Note 1) |             | ns   |

| tCR      | Read waiting time after transmission    | 400(Note 1) |             | ns   |

| twr      | Read pulse width                        | 320(Note 2) |             | ns   |

| tRC      | Transfer waiting time after read        | 400(Note 1) |             | ns   |

| tCRPV    | Waiting time before program verify      | 6           |             | μs   |

| twp      | Programming time                        |             | 10          | μs   |

| tPC      | Transfer waiting time after programming | 400(Note 1) |             | ns   |

| tEC      | Transfer waiting time after erase       | 400(Note 1) |             | ns   |

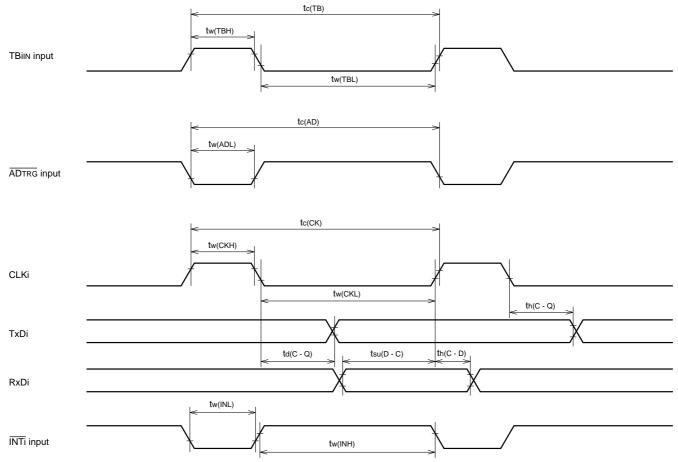

| tc(CK)   | SCLK input cycle time                   | 250         |             | ns   |

| tw(CKH)  | SCLK high-level pulse width             | 100         |             | ns   |

| tw(CKL)  | SCLK low-level pulse width              | 100         |             | ns   |

| tr(CK)   | SCLK rise time                          | 20          |             | ns   |

| tf(CK)   | SCLK fall time                          | 20          |             | ns   |

| td(C-Q)  | SDA output delay time                   | 0           | 90          | ns   |

| th(C-Q)  | SDA output hold time                    | 0           |             | ns   |

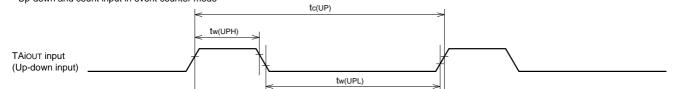

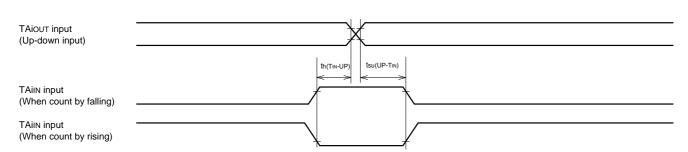

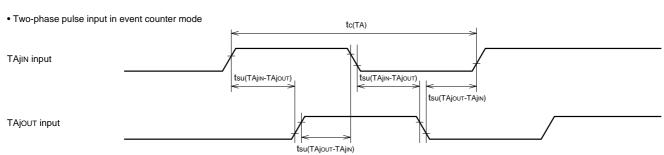

| th(C-E)  | SDA output hold time (only the 8th bit) | 120(Note 3) | 200(Note 4) | ns   |