www.fairchildsemi.com

# **FSDM101**

**Green Mode Fairchild Power Switch (FPS<sup>TM</sup>)**

#### **Features**

- Internal Avalanche Rugged Sense FET

- Precision Fixed Operating Frequency (67kHz)

- Internal Start-up Switch and Soft Start

- Under Voltage Lock Out (UVLO) with Hysteresis

- Pulse by Pulse Current Limit

- Over Load Protection (OLP)

- Over Voltage Protection (OVP)

- Internal Thermal Shutdown Function (TSD)

- Secondary Side Regulation

- Auto-Restart Mode

## Applications

- Charger & Adaptor for Mobile Phone, PDA & MP3

- Auxiliary Power for White Goods, PC, C-TV & Monitor

- SMPS for VCR, SVR, STB, DVD, and DVCD

- Adaptor for Camcorder

#### Description

The FSDM101 is an integrated Pulse Width Modulator (PWM) and Sense FET specially designed for high performance off-line Switch Mode Power Supplies (SMPS) with minimal external components. This device is a monolithic high voltage power switching regulator which combines a VDMOS Sense FET with a voltage mode PWM control block. The integrated PWM controller features include: a fixed oscillator, Under Voltage Lock Out (UVLO) protection, Leading Edge Blanking (LEB), optimized gate turn-on/ turn-off driver, thermal shut down protection (TSD), temperature compensated precision current sources for loop compensation and fault protection circuitry. When compared to a discrete MOSFET and controller or RCC switching converter solution, the FSDM101 reduces total component count, design size, weight and at the same time increases efficiency, productivity, and system reliability. This device is a basic platform well suited for cost effective designs of flyback converters.

| TYPICAL OUTPUT POWER CAPABILITY             |                            |           |  |  |  |

|---------------------------------------------|----------------------------|-----------|--|--|--|

| PRODUCT                                     | Open Frame <sup>(1)</sup>  |           |  |  |  |

| TROBUCT                                     | 230VAC ±15% <sup>(2)</sup> | 85-265VAC |  |  |  |

| FSDM101                                     | 13W 8W                     |           |  |  |  |

| PEAK OUTPUT POWER CAPABILITY <sup>(3)</sup> |                            |           |  |  |  |

| PRODUCT                                     | Open Frame <sup>(1)</sup>  |           |  |  |  |

| FRODUCT                                     | 230VAC ±15% <sup>(2)</sup> | 85-265VAC |  |  |  |

| FSDM101                                     | 17W                        | 12W       |  |  |  |

Table 1. Notes: 1. Maximum practical continuous power in an open frame design with a sufficient drain pattern as a heat sinker at 50°C ambient temperature. 2. 230 VAC or 100/115 VAC with doubler. 3. Peak output power means the maximum power can be handled instantaneously.

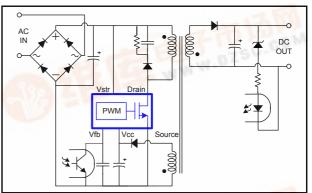

## **Typical Circuit**

Fise trademark of Fairchild Semiconductor Corporation.

#### FSDM101

#### Vstr 5 6,7,8 Drain Vcc 2 о<sub>н</sub> Voltage Ref Internal Bias UVLO 9.0/7.0V mosc A 400u SFET DRIVER PWM Q s Vfb 3 R \$ **\*** S/S 15mS $\overline{m}$ LEB NC 4 OLP love Rsense Reset Vth Ť s Q Vsd $\frac{1}{m}$ R OVP Γ Γ Min.20V $\frac{1}{m}$ TSD A/R

## Internal Block Diagram

Figure 2. Functional Block Diagram of FSDM101

## **Pin Definitions**

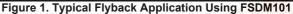

| Pin Number | Pin Name | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | GND      | Sense FET source terminal on primary side and internal control ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 2          | Vcc      | Positive supply voltage input. Although connected to an auxiliary transformer winding, current is supplied from pin 5 (Vstr) via an internal switch during startup (see Internal Block Diagram section). It is not until Vcc reaches the UVLO upper threshold (9V) that the internal start-up switch opens and device power is supplied via the auxiliary transformer winding.                                                                                                                                                                                   |  |  |

| 3          | Vfb      | The feedback voltage pin is the inverting input to the PWM comparator with nominal input levels between 0.5Vand 2.5V. It has a 0.40mA current source connected internally while a capacitor and optocoupler are typically connected externally. A feedback voltage of 4.5V triggers overload protection (OLP). There is a time delay while charging between 3V and 4.5V using an internal 2.5uA current source, which prevents false triggering under transient conditions, but still allows the protection mechanism to operate under true overload conditions. |  |  |

| 5          | Vstr     | The startup pin connects directly to the rectified AC line voltage source for FSDM101. For the FSDM101, at start up the internal switch supplies internal bias and charges an external storage capacitor placed between the Vcc pin and ground. Once this reaches 9V, the internal current source is disabled.                                                                                                                                                                                                                                                   |  |  |

| 6, 7, 8    | Drain    | The Drain pin is designed to connect directly to the primary lead of the transformer and is capable of switching a maximum of 650V. Minimizing the length of the trace connecting this pin to the transformer will decrease leakage inductance.                                                                                                                                                                                                                                                                                                                  |  |  |

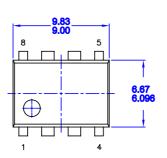

# Pin Configuration

Figure 3. Pin Configuration (Top View)

## **Absolute Maximum Ratings**

(Ta=25°C unless otherwise specified)

| Parameter                                     | Symbol     | Value              | Unit |  |

|-----------------------------------------------|------------|--------------------|------|--|

| Maximum Vstr Pin Voltage                      | VSTR,MAX   | 650                | V    |  |

| Maximum Drain Pin Voltage                     | VDRAIN,MAX | 650                | V    |  |

| Drain Current Pulsed <sup>(1)</sup>           | IDM        | 1.5                | ADC  |  |

| Continuous Drain Current (Tc=25°C)            | ID         | 0.5                | ADC  |  |

| Continuous Drain Current (Tc=100°C)           | ID         | 0.32               | ADC  |  |

| Single Pulsed Avalanche Energy <sup>(2)</sup> | Eas        | 10                 | mJ   |  |

| Maximum Supply Voltage                        | VCC,MAX    | 20                 | V    |  |

| Input Voltage Range                           | VFB        | –0.3 to VSTOP      | V    |  |

| Total Power Dissipation                       | PD         | -                  | W    |  |

| Operating Junction Temperature.               | TJ         | Internally limited | °C   |  |

| Operating Ambient Temperature.                | TA         | -25 to +85         | °C   |  |

| Storage Temperature Range.                    | TSTG       | -55 to +150        | °C   |  |

1. Repetitive rating: Pulse width limited by maximum junction temperature

2. L=24mH, starting Tj=25°C

## **Thermal Impedance**

| Parameter                   | Symbol                  | Value | Unit |

|-----------------------------|-------------------------|-------|------|

| 8DIP                        | · · · ·                 |       |      |

| Junction-to-Ambient Thermal | $\theta_{JA}^{(1)}$     | _(3)  | °C/W |

| Sunction-to-Ambient mermai  | $	heta_{JA^{(1)}}$      | _(4)  | °C/W |

| Junction-to-Case Thermal    | $\theta_{\rm JC}^{(2)}$ |       | °C/W |

#### Note:

1. Free standing without heatsink.

2. Measured on the GND pin close to plastic interface.

Soldered to 100mm<sup>2</sup> copper clad.

Soldered to 300mm<sup>2</sup> copper clad.

\* - all items are tested with the standard JESD 51-10(DIP)

## **Electrical Characteristics (Sense FET Part)**

(Ta = 25°C unless otherwise specified)

| arameter Symbol Condition                       |         | Min.                                                                           | Тур. | Max. | Unit |    |

|-------------------------------------------------|---------|--------------------------------------------------------------------------------|------|------|------|----|

| SENSE FET SECTION                               |         |                                                                                |      |      |      |    |

| Zaro Cata Valtago Drain Current                 |         | V <sub>DS</sub> =Max. Rating,<br>V <sub>GS</sub> =0V                           | -    | -    | 25   | μA |

| Zero Gate Voltage Drain Current                 | IDSS    | V <sub>DS</sub> =0.8Max. Rating,<br>V <sub>GS</sub> =0V, T <sub>C</sub> =125°C | -    | -    | 200  | μA |

| Static Drain-Source on Resistance (Note)        | RDS(ON) | V <sub>GS</sub> =10V, I <sub>D</sub> =0.5A                                     | -    | 14   | 19   | Ω  |

| Forward Trans conductance (Note)                | gfs     | V <sub>DS</sub> =50V, I <sub>D</sub> =0.5A                                     | 1.0  | 1.3  | -    | S  |

| Input Capacitance                               | CISS    |                                                                                | -    | 162  | -    | pF |

| Output Capacitance                              | Coss    | V <sub>GS</sub> =0V, V <sub>DS</sub> =25V,<br>f=1MHz                           | -    | 18   | -    |    |

| Reverse Transfer Capacitance                    | CRSS    |                                                                                | -    | 3.8  | -    |    |

| Turn on Delay Time                              | td(on)  | VDD=0.5B VDSS,                                                                 | -    | 9.5  | -    | -  |

| Rise Time                                       | tr      | ID=1.0A                                                                        | -    | 19   | -    |    |

| Turn Off Delay Time                             | td(off) | <ul> <li>(MOSFET switching time<br/>is essentially</li> </ul>                  | -    | 33   | -    | ns |

| Fall Time                                       | tf      | independent of operating temperature)                                          | -    | 42   | -    |    |

| Total Gate Charge<br>(Gate-Source + Gate-Drain) | Qg      | VGS=10V, ID=1.0A,<br>VDS=0.5B VDSS                                             | -    | 7.0  | -    |    |

| Gate-Source Charge                              | Qgs     | (MOSFET switching time                                                         | -    | 3.1  | -    | nC |

| Gate-Drain (Miller) Charge                      | Qgd     | is essentially<br>independent of operating<br>temperature)                     | -    | 0.4  | -    |    |

Note:

1. Pulse test: Pulse width  $\leq 300 \mu S,\,duty \leq 2\%$

<sup>2.</sup> S =  $\frac{1}{R}$

#### FSDM101

## Electrical Characteristics (Control Part) (Continued)

(Ta=25°C unless otherwise specified)

| Parameter                                       | Symbol                | Condition                                    | Min. | Тур. | Max. | Unit  |

|-------------------------------------------------|-----------------------|----------------------------------------------|------|------|------|-------|

| UVLO SECTION                                    |                       |                                              |      |      |      |       |

| Start Threshold Voltage                         | VSTART                | VFB=GND                                      | 8    | 9    | 10   | V     |

| Stop Threshold Voltage                          | VSTOP                 | VFB=GND                                      | 6    | 7    | 8    | V     |

| OSCILLATOR SECTION                              |                       |                                              |      | •    |      |       |

| Initial Accuracy                                | Fosc                  |                                              | 61   | 67   | 73   | kHz   |

| Frequency Change With Temperature (2)           | $\Delta F / \Delta T$ | $-25^{\circ}C \le Ta \le +85^{\circ}C$       | -    | ±5   | ±10  | %     |

| Maximum Duty Cycle                              | Dmax                  |                                              | 59   | 65   | 71   | %     |

| Minimum Duty Cycle                              | Dmin                  |                                              | -    | -    | 0    | %     |

| FEEDBACK SECTION                                |                       |                                              |      | •    |      |       |

| Feedback Source Current                         | IFB                   | Ta=25°C, $0V \le Vfb \le 3V$                 | 0.35 | 0.40 | 0.45 | mA    |

| Shutdown Feedback Voltage                       | VSD                   |                                              | 4.0  | 4.5  | 5.0  | V     |

| Shutdown Delay Current                          | IDELAY                | Ta=25°C, $3V \le Vfb \le VSD$                | 1.9  | 2.5  | 3.1  | μA    |

| REFERENCE SECTION                               |                       |                                              |      | •    |      |       |

| Output Voltage <sup>(1)</sup>                   | Vref                  | Ta=25°C                                      | 4.20 | 4.50 | 4.80 | V     |

| Temperature Stability <sup>(1)(2)</sup>         | Vref/∆T               | $-25^{\circ}C \le Ta \le +85^{\circ}C$       | -    | 0.3  | 0.6  | mV/°C |

| CURRENT LIMIT(SELF-PROTECTION)S                 | ECTION                |                                              |      | •    |      |       |

| Peak Current Limit <sup>(3)</sup>               | IOVER                 |                                              | 0.65 | 0.75 | 0.85 | Α     |

| SOFT START SECTION                              |                       |                                              |      |      |      |       |

| Soft Start Time                                 | TSOFT                 |                                              | 10   | 15   | 20   | ms    |

| PROTECTION SECTION                              |                       |                                              |      |      |      |       |

| Thermal Shutdown Temperature <sup>(1)</sup>     | TSD                   | -                                            | 125  | 145  | -    | °C    |

| Over Voltage Protection                         | Vovp                  |                                              | 20   | -    | -    | V     |

| TOTAL STANDBY CURRENT SECTION                   |                       |                                              |      |      |      | •     |

| Start-up Charging Current                       | ISTR                  | V <sub>CC</sub> = 0V, V <sub>STR</sub> = 40V | 450  | 550  | 650  | μA    |

| Operating Supply Current<br>(Control Part Only) | IOP                   | $V_{CC} \le 16$                              | -    | 1.5  | 3.0  | mA    |

Note:

1. These parameters, although guaranteed, are not 100% tested in production

2. These parameters, although guaranteed, are tested in EDS (wafer test) process

3. Test current slope : di/dt = 150 mA/us

## Comparison Between FSDH0165 and FSDM101

| Function                     | FSDH0165       | FSDM101    | FSDM101 Advantages                                                                                                                                                                                                                                                                        |

|------------------------------|----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Soft-Start                   | not applicable | 15mS       | <ul> <li>Gradually increasing current limit<br/>during soft-start further reduces peak<br/>current and voltage component<br/>stresses</li> <li>Eliminates external components used<br/>for soft-start in most applications</li> <li>Reduces or eliminates output<br/>overshoot</li> </ul> |

| Drain Creepage at<br>Package | 1.02mm         | 3.56mm DIP | Greater immunity to arcing as a result<br>of build-up of dust, debris and other<br>contaminants                                                                                                                                                                                           |

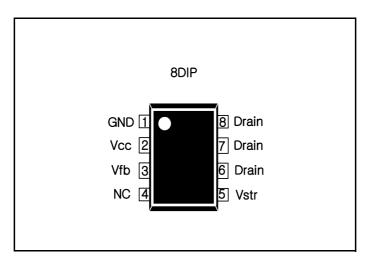

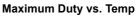

## **Typical Performance Characteristics**

(These characteristic graphs are normalized at Ta=25°C)

Frequency vs. Temp

## Typical Performance Characteristics (Continued)

(These characteristic graphs are normalized at Ta=25°C)

0

50

100

150

0.90

#### **Functional Description**

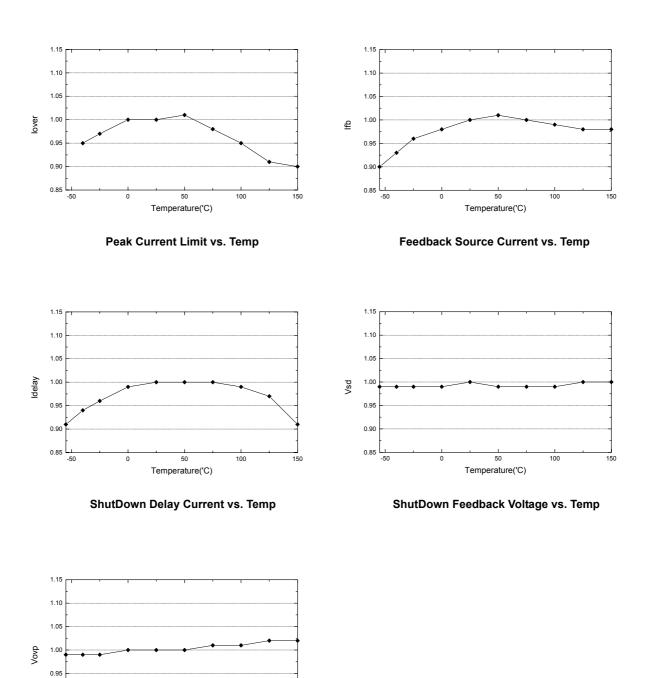

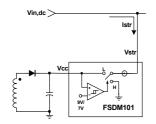

**1. Startup** : At startup, the internal high voltage current source supplies the internal bias and charges the external Vcc capacitor as shown in Figure 4. In the case of the FSDM101, when Vcc reaches 9V the device starts switching and the internal high voltage current source is disabled. The device continues to switch provided that Vcc does not drop below 7V. After startup, the bias is supplied from the auxiliary transformer winding.

Figure 4. Internal Startup Circuit

Calculating the Vcc capacitor is an important step to designing in the FSDM101. At initial start-up in the FSDM101, the stand-by maximum current is 100uA, supplying current to UVLO and Vref Block. The charging current (i) of the Vcc capacitor is equal to Istr - 100uA. After Vcc reaches the UVLO start voltage only the bias winding supplies Vcc current to device. When the bias winding voltage is not sufficient, the Vcc level decreases to the UVLO stop voltage. At this time Vcc oscillates. In order to prevent this ripple, it is recommended that the Vcc capacitor be sized between 10uF and 47uF.

Figure 5. Charging the Vcc Capacitor through Vstr

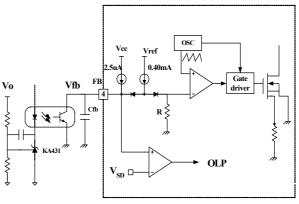

2. Feedback Control : The FSDM101 products are the voltage mode devices shown in Figure 6. Usually, an opto-coupler and KA431 type voltage reference are used to implement the feedback network. The feedback voltage is compared with an internally generated sawtooth waveform. This directly controls the duty cycle. When the KA431 reference pin voltage exceeds the internal reference voltage of 2.5V, the optocoupler LED current increases, pulling down the feedback voltage and reducing the duty cycle. This will happen when the input voltage increases or the output load decreases.

**3. Leading Edge Blanking (LEB)**: When the MOSFET is turned on, there usually exists a high current spike through the MOSFET. This is caused by primary side capacitance and secondary side rectifier reverse recovery. This could cause premature termination of the switching pulse if it exceeded the over-current threshold. Therefore, the FPS employs the leading edge blanking (LEB) circuit. This circuit inhibits the over current comparator for a short time after the MOSFET is turned on.

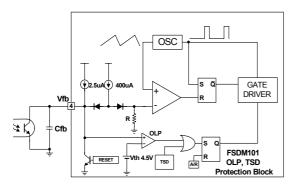

Figure 6. PWM and Feedback Circuit

4. Protection Circuit : The FSDM101 has three self protection functions: over-load protection (OLP), thermal shutdown (TSD) and over-voltage protection (OVP). Because these protection circuits are fully integrated into the IC with no external components, system reliability is improved without any cost increase. If either of these functions are triggered, the FPS starts an auto-restart cycle. Once the fault condition occurs, switching is terminated and the MOSFET remains off. This causes Vcc to fall. When Vcc reaches the UVLO stop voltage (7V), the protection is reset and the internal high voltage current source charges the Vcc capacitor. When Vcc reaches the UVLO start voltage (9V), the device attempts to resume normal operation. If the fault condition is no longer present start up will be successful. If it is, however, still present, the cycle is repeated. This is shown in Figure 7.

**Figure 7. Protection Block**

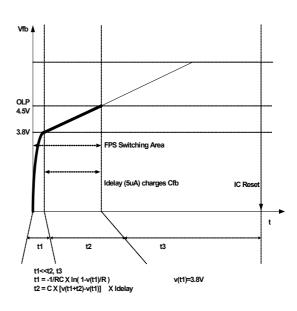

4.1 Over Load Protection (OLP) : Overload is a load current that exceeds a pre-set level due to an abnormal situation. If this occurs, the protection circuit should be triggered to protect the SMPS. It is possible that a short term load transient can occur under normal operation. If this occurs, the system should not shut down. In order to avoid false shutdowns, the over load protection circuit is designed to trigger after a delay. Therefore the device can discriminate between transient overloads and true fault conditions. The device is pulse-by-pulse current limited and therefore, for a given input voltage, the maximum input power is limited. If the load tries to draw more than this, the output voltage will drop below its set value. This reduces the opto-coupler LED current, which in turn, will reduce the photo-transistor current. Therefore, the 400uA current source will charge the feedback pin capacitor, Cfb, and the feedback voltage, Vfb, will increase. The input to the feedback comparator is clamped at around 3.8V. Therefore, once Vfb reaches 3.8V, the device is switching at maximum power. At this point the 400uA current source is blocked and the 2.5uA source continues to charge Cfb. Once Vfb reaches 4.5V, switching stops. Therefore the shutdown delay time is set by the time required to charge Cfb from 3.8V to 4.5V with 2.5uA, as shown in Figure 8.

**4.2 Thermal Shutdown (TSD) :** The Sense FET and the control IC are assembled in one package. This makes it easy for the control IC to detect the temperature of the Sense FET. When the temperature exceeds approximately 145°C, thermal shutdown is activated.

Figure 8. Over Load Protection Delay

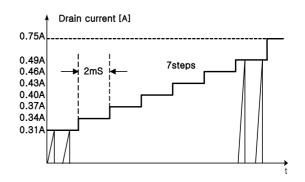

**5. Soft Start** : The FPS has an internal soft start circuit that increases the drain current limit together with the MOSFET current slowly after it starts up. The soft start time is typically 15msec as shown in Figure 9. It progressively increases during the start-up phase. The pulse width to the power switching devices is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors. The voltage on the output capacitors is progressively increased with the intention of smoothly establishing the required output voltage. Consequently it prevents transformer saturation and stress on the secondary diodes.

Figure 9. Internal Soft Start

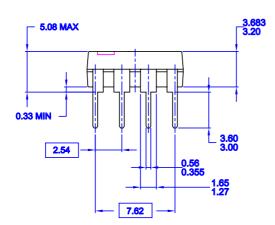

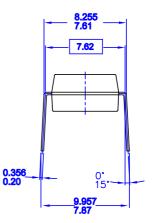

## **Package Dimensions**

**8DIP**

NOTES: UNLESS OTHERWISE SPECIFIED A) THIS PACKAGE CONFORMS TO JEDEC MS-001 VARIATION BA B) ALL DIMENSIONS ARE IN MILLIMETERS. C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS. D) DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994

MKT-N08FrevB

# **Ordering Information**

| Product Number | Package | Marking Code | Topr (°C) |

|----------------|---------|--------------|-----------|

| FSDM101        | 8DIP    | DM101        | 650V      |

FSDM101

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.