www.ti.com

GC1115

SLWS144-FEBRUARY 2005

# **Crest Factor Reduction Processor**

### **FEATURES**

- Significantly Reduces Signal Peaks to ≥ 6 dB PAR

- One 20-MHz or 2 Independent 10-MHz Channels

- Programmable Output PAR Down to 6 dB

- Programmable Cancellation Pulse Coefs

- Meets 3GPP TS 25.141 Down to 6 dB PAR

- Meets cdma2000 C.S0010 Down to 6 dB PAR

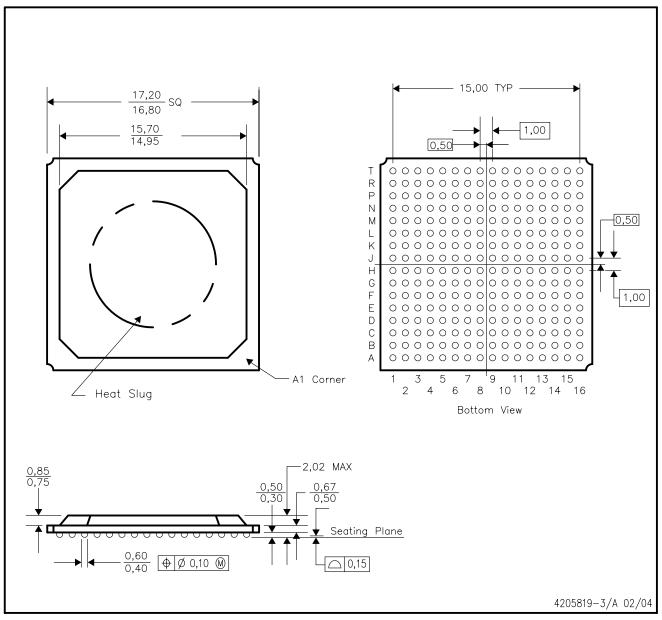

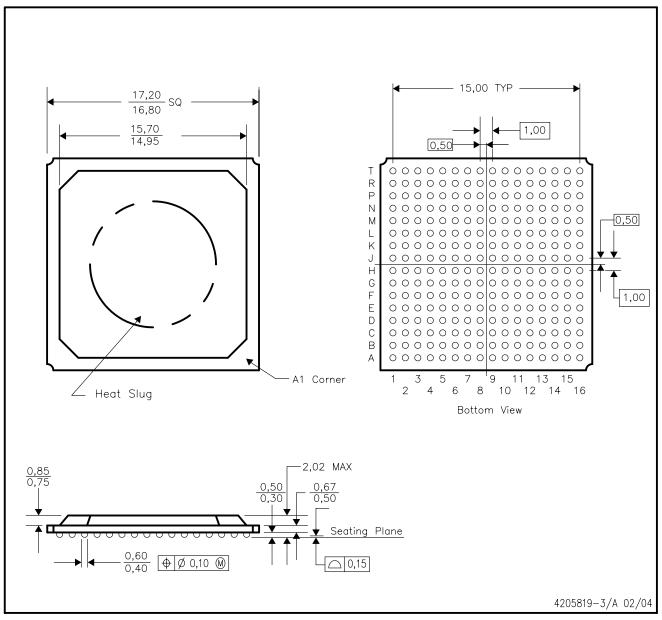

- 256-ball PBGA Package, 17 × 17 mm

- 1.2-V Core, 3.3 V I/O

### **APPLICATIONS**

- 3GPP (W-CDMA) Base Stations

- 3GPP2 (cdma2000) Base Stations

- CDMA Multi-Carrier Power Amps (MCPAs)

- CFR Reduction of OFDM, HSDPA Signals

- Two-Channel Transmit Diversity Applications

- Operates with TI DAC5687 (500 Msps)

### DESCRIPTION

The GC1115 is a flexible, programmable, wideband crest factor reduction (CFR) processor with a maximum composite bandwidth of 20 MHz. The GC1115 selectively reduces the peak-to-average ratio (PAR) of wideband digital signals provided in quadrature (I & Q) format, such as those used in third-generation (3G) code division multiple access (CDMA) wireless applications. By reducing the PAR of digital signals, the efficiency of follow-on power amplifiers (PAs) is improved, the D/A converter requirements are eased, and the out-of-band spectral regrowth caused by simple hard limiting is eliminated.

By including the GC1115, manufacturers of 3G BTS equipment can realize significant savings on power amplifier costs. The GC1115 meets multi-carrier 3G performance standards (PCDE, composite EVM, and ACLR) at PAR levels down to 6 dB. The GC1115 integrates easily into the transmit signal chain, between a digital upconverter such as the Texas Instruments GC5016 or GC5316 and a high-quality D/A converter, such as the Texas Instruments DAC5675 or DAC5687.

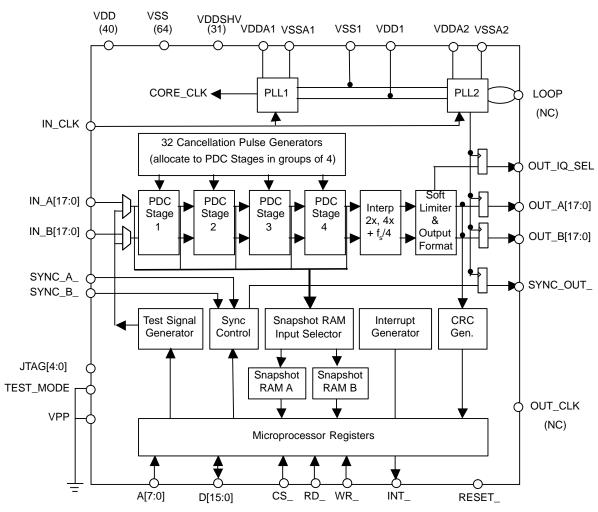

The GC1115 uses four cascaded stages of peak detection and cancellation (PDC) to remove over-threshold peaks from the input signal. Each PDC stage can be independently programmed with detection target peak levels and cancellation pulse coefficients. A pool of 32 cancellation pulse generators can be flexibly assigned in groups of 4 to any PDC stage. Spectrally shaped cancellation pulses are designed using any of the widely available FIR filter design programs, such as those from Matlab™, ADS™, etc. Cancellation pulses are designed to match the user's carrier frequency allocation. Cancellation pulse energy is bandlimited and thus is only added within allocated carrier bands. The GC1115's peak cancellation algorithm does not affect the signal's ACLR.

Input sampling rates to 130 Msamp/sec are supported, in either parallel or multiplexed I/Q modes, and in either twos complement or unsigned format. Output sampling rates to 130 Msamp/sec are supported in either parallel or multiplexed I/Q modes, and in either twos complement or unsigned format. A special one-channel output mode uses both GC1115 output ports to carry odd/even real output samples. The GC1115 includes an interpolator that increases the output sampling rate by 2x or 4x and optionally modulates the output signal to the f<sub>s</sub>/4 center frequency. Dual on-chip RAM banks provide either time-domain snapshots or long-term histogramming of the internal peak cancellation signal chain at five user-selected points, enabling real-time monitoring of the CCDF function. A power level meter monitors either the GC1115 input or output power level.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **FUNCTIONAL BLOCK DIAGRAM**

### **Related Documents**

- GC1115 Evaluation Module (EVM) User's Guide

- Application Note: GC1115 Configuration for UMTS (W-CDMA) Base Stations

- Application Note: GC1115 Configuration for 3GPP2 (cdma2000) Base Stations

- Matlab code for cancellation pulse design

### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGE                          | DEVICE     |

|----------------|----------------------------------|------------|

| -40°C to 85°C  | 256-PBGA Plastic Ball Grid Array | GC1115IZDJ |

### INTRODUCTION

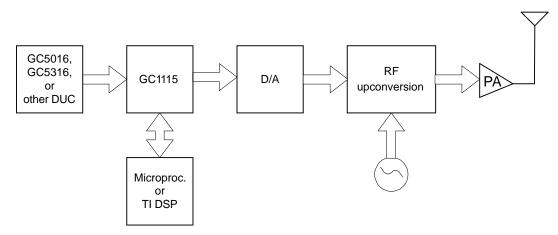

Figure 1 shows the typical usage of the GC1115 crest factor reduction processor in the transmit signal chain of a wireless base station.

Figure 1. Wireless System Using the GC1115

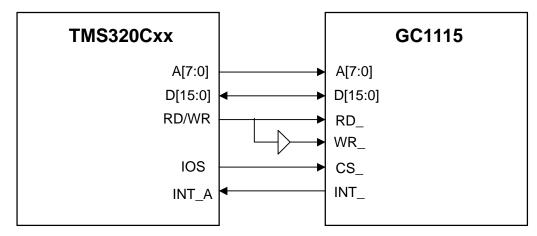

The GC1115 is initialized and controlled using an 8-bit address (A) and a 16-bit data (D) bus. These pins, along with the read  $(\overline{RD})$ , write  $(\overline{WR})$ , and chip select  $(\overline{CS})$  pins, allow users to modify the control registers of the GC1115.

Signals are provided to the GC1115 using two 18-bit input ports, IN\_A[17:0] and IN\_B[17:0], which are typically driven by a digital upconverter such as the GC5016, GC5316, or similar. The GC1115 can accept either one or two input channels.

When the GC1115 is configured to process two input channels, IN\_A[17:0] carries channel 0's multiplexed I & Q samples, while IN\_B[17:0] carries channel 1's multiplexed I & Q samples. The GC1115 output samples are provided to a D/A converter using two 18-bit output ports, OUT\_A[17:0] and OUT\_B[17:0]. The GC1115 output may appear on one or both output ports, depending on which output mode (real or complex; parallel or multiplexed; odd-even) is selected.

### NOTE:

The D/A converter must **not** use the GC1115's OUT\_CLK signal. OUT\_CLK is for test purposes only. OUT\_CLK's phase is not aligned with the data on the OUT\_A and OUT\_B ports. OUT\_CLK may contain jitter in excess of that required to clock high-speed D/A converters.

## Why Cancel Peaks?

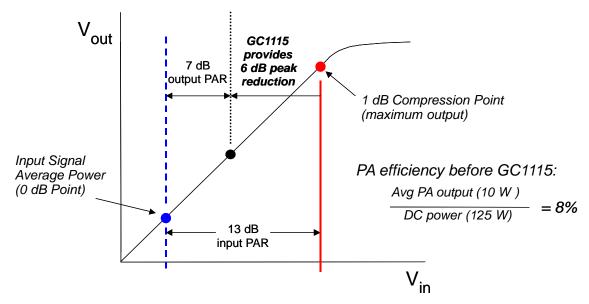

The purpose of the GC1115 is to lower the peak-to-average ratio (PAR) of composite digital communication signals. Specifically, wideband code division multiple access (W-CDMA) and orthogonal frequency division multiplexed (OFDM) signals have high peak-to-average ratios (PARs) ranging from 10 dB to 15 dB. After D/A conversion, a power amplifier (PA) amplifies the resulting analog signal. In order to accommodate the high PAR of W-CDMA and OFDM signals, the peak signal level must be at or below the 1 dB compression point of the PA, which is usually accommodated by backing off the input drive to the power amplifier.

Figure 2 illustrates the effects of a decrease in peak-to-average ratio on a PA's V<sub>in</sub> vs V<sub>out</sub> graph.

Figure 2. Reducing the Peak-to-Average Ratio (PAR)

However, since the peak-to-average ratio of CDMA signals is so high, the average power is relatively low, consequently resulting in a low PA efficiency (output power divided by input power). By decreasing the peak-to-average ratio, the average power of the peak-reduced signal at the output of the GC1115 can be increased, decreasing PA back-off thus also increasing PA efficiency.

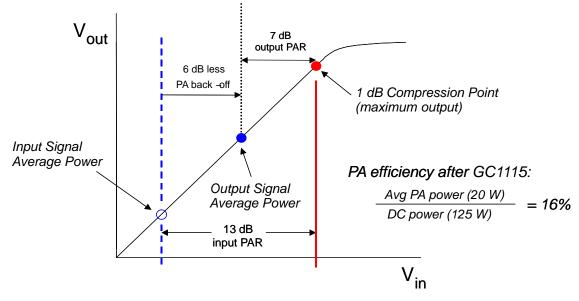

Figure 3 illustrates that the decrease in PAR can then be used to increase the average signal power while still keeping the peaks below the PA's 1 dB compression point. The GC1115 can typically limit the output PAR of CDMA signals to between 6 dB and 7 dB while still meeting all relevant 3GPP or 3GPP2 requirements. This decreased PAR enables a 2 dB to 3 dB increase in PA drive, which in turn allows PA manufacturers to achieve 2 dB to 3 dB more PA output power. As PAs represent a significant percentage of the capital equipment cost of base stations, using a 10 W PA instead of a 20 W PA (for example) significantly decreases base station costs.

Figure 3. Increasing PA Efficiency

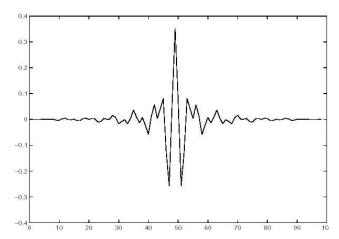

### How Peak Cancellation Works: Time Domain View

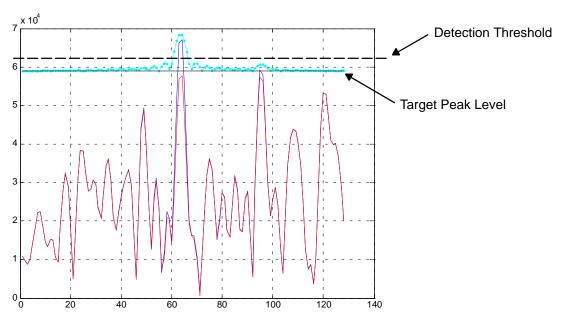

Figure 4 provides a time-domain example of GC1115 operation. Figure 4 shows the magnitude of the complex input signal in blue, and the magnitude of the complex, peak-reduced signal (after GC1115 processing) in red. [Note: for users who print this data sheet on a black-and-white printer, the input signal is a solid line, while the output signal is a finely dotted line.] Notice that for most of the 130 samples in this example, the red output waveform is identical to the blue input waveform. However, the GC1115 has reduced the magnitude of samples around two peaks (one at sample 63, one at sample 95) that exceed the detection threshold. The aqua-colored waveform above the gain threshold line demonstrates the magnitude of the cancellation pulse that was subtracted from the complex input waveform. Notice that the GC1115's PDC stages each have two independent thresholds:

- 1. Detection threshold: interpolated peaks above the detection threshold are candidates for cancellation

- 2. Target peak level: detected peaks will be reduced to the target peak level, assuming cancellation resources are available

Independent detection and target peak levels allow the GC1115 greater flexibility in peak reduction processing.

Figure 4. Peak Cancellation Example: Time Domain

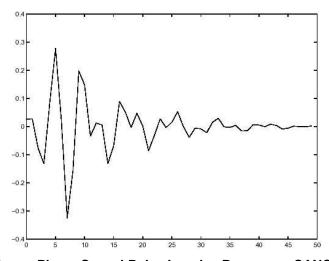

### How Peak Cancellation Works: Frequency Domain View

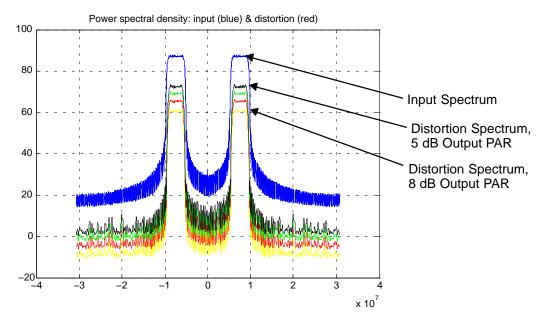

Figure 5 demonstrates the frequency-domain effects of peak cancellation. In Figure 5, the original signal's frequency response is shown in blue. The output signal's frequency response looks identical and is not shown. The yellow (8 dB PAR), red (7 dB PAR), green (6 dB PAR), and black (5 dB PAR) curves show the spectra of just the added signal (GC1115 input – GC1115 output) to achieve peak reduction. The difference between the input and output signals is the signal distortion. [Note: for users who print this data sheet on a black-and-white printer, the input spectrum is a solid line, while the output spectra are finely dotted lines.] Note that the distortion is not significant in the spectral response:

- 1. The out-of-band energy of the distortion added by the GC1115 during peak cancellation is 70 to 80 dB below the signal and hence is not an issue. The out-of-band energy is only a weak function of the target PAR level.

- 2. The amount of in-band distortion energy rises with decreasing output PAR. This is to be expected, because lower PAR thresholds result in more peaks being canceled. Lower PAR levels require more energy to cancel the peaks, thus increasing the distortion level.

The GC1115 reduces the amplitude of peaks in a way that keeps the out-of-band (ACLR) energy well below required levels. Users can determine how much in-band distortion is acceptable by monitoring the effects of peak cancellation at a given output PAR, using two key in-band distortion metrics for CDMA signals:

- 1. peak code domain error, or PCDE, and

- 2. composite error vector magnitude, or EVM

Various CFR signal quality metrics (ACLR, PCDE, EVM, CCDF) will be further discussed in a subsequent section.

Figure 5. Spectral View of Distortion

## **SUMMARY OF GC1115 FEATURES**

Refer to the GC1115 functional block diagram for the following discussion.

The GC1115 removes peaks from an input signal stream by subtracting user-designed, spectrally shaped cancellation pulses from detected peaks in the input waveform that are above a user-specified detection threshold. The cancellation pulse's spectral shape matches that of the GC1115 input signal's single- or multi-carrier configuration. This cancellation pulse design methodology ensures that energy is only added into frequency bands where signal energy is located, minimizing out-of-band energy that could otherwise increase ACLR/ACPR.

Cancellation pulses may be real or complex. Real cancellation pulses are used when the input signal spectrum is symmetric, while complex cancellation pulses are used when the input signal spectrum is asymmetric. A single cancellation pulse reduces the peak amplitude of multiple samples around each signal peak while maintaining both the in-band (PCDE, cEVM) and out-of-band (ACLR) signal quality requirements. Peaks are cancelled to a user-specified level, which is called the output peak-to-average ratio, or PAR. The GC1115 provides four sequential peak detection and cancellation (PDC) stages to remove peaks. The PDC stage thresholds are normally set so that earlier stages remove the largest peaks, while later stages remove smaller, remaining peaks.

During peak detection, an effective 256x oversampling process identifies the exact magnitude and location of interpolated peaks. In other words, the interpolated waveform approximates the output of the follow-on D/A converter. The interpolated waveform can therefore have a larger amplitude than any of the D/A's individual input samples. The GC1115's effective 256x oversampling allows both the magnitude and the location of peaks (after D/A conversion) to be predicted prior to the actual D/A conversion process. If the magnitude of the interpolated peak is above the detection threshold of the PDC stage, the peak is a candidate for peak cancellation. Detected peaks are always cancelled, unless all of the cancellation resources assigned to a given stage are already busy. When all of a PDC stage's cancellation resources are already busy canceling other peaks, subsequent PDC stages will again detect and cancel the *missed* peak, if that stage's resources allow.

The GC1115 contains a total of 32 cancellation pulse generators (also called cancelers) per channel that are allocated in groups of four to PDC stages. The normal allocation of the 32 cancelers is as follows:

- PDC Stage 1 uses 4 cancelers

- PDC Stage 2 uses 8 cancelers

- PDC Stage 3 uses 12 cancelers

- PDC Stage 4 uses 8 cancelers

The allocation of cancelers should correspond to the detection threshold (DETECT\_TSQD) for each PDC Stage. A PDC stage with a lower detection threshold will find more peaks than a PDC stage with a higher detection threshold. As mentioned above, the detection threshold for PDC stages 1 and 2 is set to detect and cancel the largest peaks (typically those above 8 or 9 dB PAR), while PDC stages 3 and 4 detect and cancel peaks at the desired output PAR (typically between 6 and 8 dB). Since the largest peaks are the ones that would cause the most distortion in the PA if they were not cancelled, setting the detection threshold higher in PDC Stages 1 and 2 ensures that the large peaks will be canceled.

Cancellation pulse coefficients are stored in special GC1115 RAM blocks. The GC1115 RAM blocks can store up to 256 real or 128 complex cancellation pulse coefficients and their associated first and second derivatives. Cancellation coefficients are signed, 12-bit integer value between –2048 and +2047. Each cancellation coefficient RAM supports up to four cancelers. Cancellation pulse generator RAMs assigned to the same stage normally contain the same coefficients, but each of the GC1115's eight cancellation RAMs may contain different coefficients. The cancellation pulse coefficients are normalized, i.e. the largest coefficient magnitude is always +2047 (1.0). However, both the magnitude and the phase of the normalized cancellation pulses are adjusted before the cancellation pulse is added to the input waveform during peak cancellation, ensuring proper alignment with the samples of the input signal.

While the subtraction of cancellation pulses reduces the peak amplitude in the region immediately surrounding a detected peak, this subtraction may also introduce new, smaller, over-threshold peaks away from the region of the peak. This phenomenon is called *peak regrowth*. Peak regrowth is an infrequent phenomenon whose effects are mitigated by using four serial PDC stages. If Stage N causes peak regrowth, Stage N+1 and subsequent stages will detect and cancel the regrowth peaks, assuming the PDC stages have available pulse cancelers. Regrowth peaks, when they occur, are usually just a few percent (or less) over the PAR threshold.

Following the four PDC stages, the GC1115 also contains an interpolator and a soft limiter. When enabled, the interpolator supports 2x real, 2x complex, and 4x real interpolation. The real output modes also modulate the signal by  $f_s/4$ . The soft limiter acts as a fixed-length AGC that optionally attenuates the input signal over a fixed-length window of up to 33 samples surrounding the detected over-threshold peak. Under nearly all circumstances, the soft limiter should be bypassed.

The GC1115 operates most efficiently when there are at least 2.5 complex samples per Hertz of bandwidth. For example, a four-carrier (20 MHz) 3G stack should be sampled at no less than 50 Msamp/sec, while a single-carrier 3G system can be sampled as low as 12.5 Msamp/sec. Under certain circumstances, the input signal can be represented using as few as 2.0 complex samples per Hz.

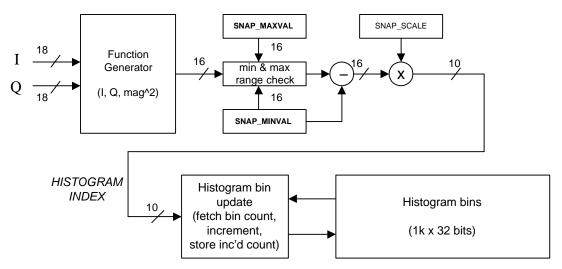

The GC1115 contains two flexible, user-programmable snapshot RAMs. The snapshot memories operate either in capture or in histogram mode. In the capture mode, 1024 consecutive I and Q samples are stored in one of the snapshot RAMs. During capture mode, 32 bits per complex sample (16 bits I, 16 bits Q) are captured. The lower 2 LSBs of each real and imaginary 18-bit sample are dropped.

Each of the two snapshot RAMs receives samples from one of five user-selected test probe points:

- 1. At the GC1115 input

- 2. After PDC Stage 1

## TEXAS INSTRUMENTS www.ti.com

#### SLWS144-FEBRUARY 2005

- 3. After PDC Stage 2

- 4. After PDC Stage 3

- 5. After PDC Stage 4

When operating in histogram mode, the snapshot RAMs generate a histogram of the real part, the imaginary part, or the power of each complex sample. In histogram mode, millions of samples can be characterized using the snapshot RAM's 32-bit bin counters, thus providing a statistically significant number of events for CCDF and related magnitude distribution measurements.

Each of the GC1115's PDC stages can be bypassed by clearing a corresponding bit in the CONTROL register. Although bypassing a stage removes that stage's peak cancellation capability, it also removes the latency introduced by the peak detection and cancellation process itself, and reduces power consumption as well.

The GC1115 includes an on-chip test signal generator that can create DC levels, sawtooth waveforms, and a filtered random number generator with Gaussian-like peak-to-average statistics (i.e. approximately 10 dB PAR). In conjunction with a CRC generator, the test signal generator can be used to verify proper, expected behavior of the GC1115 without applying an input signal to the GC1115 IN\_A and IN\_B ports. The CRC generator processes the GC1115 output samples and generates a periodic, 16-bit checksum. Since both the test signal generator and the CRC generator can be synchronized to the same sync source, the presence of a predictable, periodic value in the CRC register indicates that the GC1115 internal circuitry is operating as expected. TI provides several GC1115 configurations (starting test generator register values, sample periods, and expected CRC value at the end of each period) that enable GC1115 users to test for proper GC1115 internal operation. The test signal generator can also be used without the CRC generator, providing a suite of general-purpose test signals (DC, sawtooth, pseudo-LFSR) to exercise ICs attached to the GC1115 output ports, OUT A and OUT B.

## CFR PERFORMANCE METRICS FOR CDMA SIGNALS: CCDF, ACLR, PCDE, cEVM

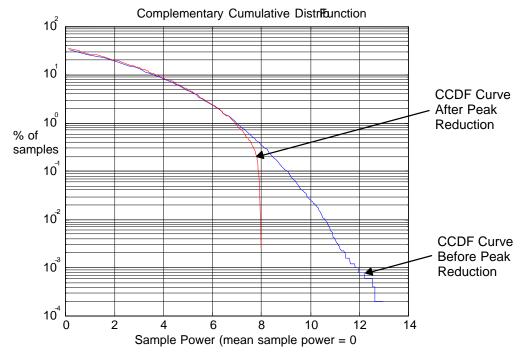

The GC1115 reduces peaks by subtracting spectrally shaped waveforms from detected peaks in the input signal whose interpolated magnitude is above a user-specified output PAR threshold. Researchers in peak reduction techniques use a graph called the complementary cumulative distribution function, or CCDF, to display the probability that a particular sample has a given magnitude. The x-axis of a CCDF curve begins at 0 dB, defined as the average power of the signal, and extends to the peak value of the waveform. The y-axis of a CCDF curve lists the probability (usually on a log scale) that a given complex sample has a certain magnitude. Plotting the before and after CCDF curves on the same graph demonstrates that the GC1115 peak reduction algorithms have achieved their primary purpose: reducing peaks to a user-specified level. In Figure 6, the input CCDF curve is shown in blue and the output CCDF curve (after GC1115 peak reduction) is shown in red.

Figure 6. Example Complementary Cumulative Distribution Function (CCDF)

Because the GC1115 modifies samples of the input waveform during peak reduction, the peak reduction process introduces certain distortions. The nature of these distortions is well understood and is under the user's control. GC1115 users have great flexibility in determining the overall distortion level. Distortion can be quantified in several ways:

- By analyzing the spectrum of the distortion (input-output) signal

- By analyzing the out-of-band output noise level in neighboring channels (also called the adjacent channel leakage ratio, or ACLR)

- By measuring a composite error vector magnitude (cEVM) level

- By determining the interference level (caused peak reduction) in the CDMA code *noise floor*, this metric is called the peak code domain error, or PCDE

- By monitoring bit error rate (BER) at the receiver

The two dominant 3G standards, W-CDMA (3GPP) and cdma2000 (3GPP2), have developed a set of standardized requirements for ACLR, cEVM, and PCDE. Because a wide variety of valid CDMA waveforms exist, the 3G standards bodies have also specified a set of test waveforms called *test models* to verify all elements in the downlink signal processing chain. Test models also allow BTS developers to compare the performance of competing signal processing devices, including crest factor reduction processors, on identical input signals.

Texas Instruments quantified GC1115 behavior with extensive 3G Test Model 1, Test Model 3, and Test Model 5 signals, and in both single-carrier and multi-carrier configurations. For all tests, TI measured the following parameters:

- CCDF

- ACLR

- PCDE

- CEVM

The following paragraphs review the relevant 3G requirements for these parameters. Subsequent sections present test results that demonstrate the GC1115's ability to meet all relevant 3G requirements at output PAR levels to 6 dB.

## Relevant 3GPP (W-CDMA) Requirements

The GC1115 is designed to meet the following 3GPP specifications. The Test Models used to verify these specifications are described in 3GPP TS 25.141, Section 6.1.1 of Release 6 (2002-12).

- ACLR: At least 45 dB ACLR at 5 MHz below the first (or above the last) active W-CDMA carrier in the band, and at least 50 dB ACLR at 10 MHz below the first (or above the last) active W-CDMA carrier in the band, (TS 25.141, Section 6.5.2.2), using Test Model 1.

- NOTE: The GC1115 supports > 70 dB ACLR using 85-tap cancellation pulses or longer.

- EVM: ≤ 17.5% for QPSK modulation (TS 25.141, Section 6.7.1), using Test Model 4.

- NOTE: The GC1115 provides ≤ 17.5% cEVM for all Test Models with output PAR down to 6 dB.

- PCDE: ≤- 33 dB (TS 25.141, Section 6.7.2), using Test Model 3.

- NOTE: The GC1115 provides ≤ -33 PCDE for all Test Models with output PAR down to 6 dB.

- Spurious emissions: various (TS 25.141, Section 6.5.3), using Test Model 1.

## Relevant cdma2000 Requirements

Ref. 3GPP2 C.S0010-A (March 30, 2001):

- Section 4.2: Modulation Requirements (Rho waveform quality)

- Section 4.3: RF Output Power Requirements

- Section 4.4: Limitations on Emissions

# SUMMARY OF GC1115 PERFORMANCE USING 3G TEST MODEL SIGNALS

| 3G Test Signal | # of cxrs |       | PCDE (Spec: < -33 dB) |       |       | Composite EVM (Spec: < 17.5%) |       |       | 5%)   |

|----------------|-----------|-------|-----------------------|-------|-------|-------------------------------|-------|-------|-------|

|                |           | 8 dB  | 7 dB                  | 6 dB  | 5 dB  | 8 dB                          | 7 dB  | 6 dB  | 5 dB  |

| TM1_64         | 1         | -50.7 | -46.2                 | -41.7 | -38.3 | 3.3%                          | 5.4%  | 8.5%  | 11.7% |

| TM1_64         | 2         | -50.1 | -45.6                 | -42.2 | -37.8 | 3.4%                          | 5.8%  | 8.7%  | 12.7% |

| TM1_64         | 4         | -49.8 | -47.2                 | -43.3 | -39.8 | 3.9%                          | 4.9%  | 7.6%  | 10.8% |

| TM3_32         | 1         | -46.3 | -41.4                 | -37.1 | -34.4 | 3.9%                          | 6.5%  | 9.7%  | 13.5% |

| TM3_32         | 2         | -44.5 | -42.3                 | -38.2 | -36.3 | 4.5%                          | 7.0%  | 9.3%  | 12.3% |

| TM3 32         | 4         | -42.5 | -39.1                 | -35.6 | -34.2 | 7.0%                          | 10.0% | 13.2% | 15.5% |

Table 1. 3GPP PCDE and Composite EVM Performance

### Test Conditions:

- a. Each simulation processed 614.400 input samples (one 10 msec frame at 61.44 Msamp/sec)

- b. PCDE and composite EVM were measured using a Rohde & Schwarz FSU

- c. Cancellation pulse lengths varied from 75 to 181

- d. ACLR depends mostly on cancel pulse length. Cancel pulse lengths of 85 achieve -70 dB ACLR for four-carrier UMTS signals. Cancel pulse lengths of 115 achieve -70 dB ACLR for single-carrier UMTS signals.

- e. Multi-carrier Test Model signals used frames that were staggered by 2 msec between carriers

- f. Stages 1 thru 4 were assigned 4, 8, 12, and 8 cancelers, respectively (total of 32 cancelers).

- g. For PAR = 7 dB, Stages 1 thru 4 used detection thresholds of 8, 7, 7, and 7 dB, respectively.

- h. For PAR = 6 dB, Stages 1 thru 4 used detection thresholds of 8, 7, 6, and 6 dB, respectively.

- i. For PAR = 5 dB, Stages 1 thru 4 used detection thresholds of 8, 6, 5, and 5 dB, respectively.

## **RESET**

The GC1115 supports three kinds of reset:

- PLL reset (only the PLLs are reset)

- 2. Hardware reset (all configuration registers are brought to their RESET values)

- 3. Datapath hardware reset

Setting specific bits in the RESET register activates these resets. Asserting the RESET pin of the GC1115 also causes hardware reset. Hardware reset results in the following GC1115 conditions:

- All input pins are put in their high-impedance state

- All output pins are put in their high-impedance state

- All internal registers are reset to their RESET states

- All state machines are placed in their initial (idle) states

- No config registers can be modified before clearing the config reset.

### **GC1115 Initialization Sequence**

The GC1115 initialization sequence requires the following register groups to be properly initialized:

- 1. RESET, PLL\_CONTROL, CLK\_CONTROL, IO\_CONTROL

- 2. CONTROL, IO\_MODE, DECIMATE, RESOURCE\_MASK, DELAY\_MASK

- 3. SYNC registers

- 4. TSQD detection threshold and target peak level registers

- 5. INTERP registers

- 6. OUT\_GAIN, OUT\_OFFSET

- 7. CANCEL MODE, CANCEL LENGTH, CANCEL DELAY, cancellation coefficients

The following paragraphs describe in general terms how each of these registers is initialized to achieve the desired user-specified peak reduction performance.

### RESET, PLL CONTROL, CLK CONTROL, IO CONTROL

The RESET register contains four bits that can individually reset:

- The memory-mapped registers

- The GC1115 internal datapath

- The "core" PLL

- The output PLL

At GC1115 startup, hardware RESET always precedes all other register accesses and this asserts all internal reset registers. Configuration control reset must also be cleared before performing subsequent configuration steps.

After the RESET bits have been asserted, the PLL\_CONTROL and CLK\_CONTROL registers should be initialized to the desired values. The GC1115 normally operates at four times the input sample rate, while the output clock rate is determined by several additional factors (decimation, interpolation, and output format and mode). The CLK\_CONTROL register determines the PLL multiplying factors that control the GC1115 core clock and output clock frequencies. Finally, the IO\_CONTROL register determines the input and output format (twos complement or unsigned), the output enabled state (tri-stated or enabled), and the output bit width (18, 16, 14, or 12 bits).

The GC1115 PLLs require a warm-up time of at least 1 µs from PLL\_CONTROL modification to PLL reset release, and at least 100 µs from PLL\_CONTROL and CLK\_CONTROL modification to PLL reset release before the internal clock is stable.

## CONTROL, IO\_MODE, DECIMATE, RESOURCE\_MASK, DELAY\_MASK

The CONTROL register contains six control bits that selectively enable or disable the four PDC stages, the interpolator, and the soft limiter. The DECIMATE register allows users to decimate the input sample stream by 1 (no decimation) or 2. The RESOURCE\_MASK register determines which of the eight cancellation pulse SRAMs are updated with new cancel pulse coefficients when a CANCEL\_SYNC event occurs. Similarly, the DELAY\_MASK register determines which of the four PDC stages are affected by changes to the CANCEL DELAY register when the DELAY SYNC event occurs.

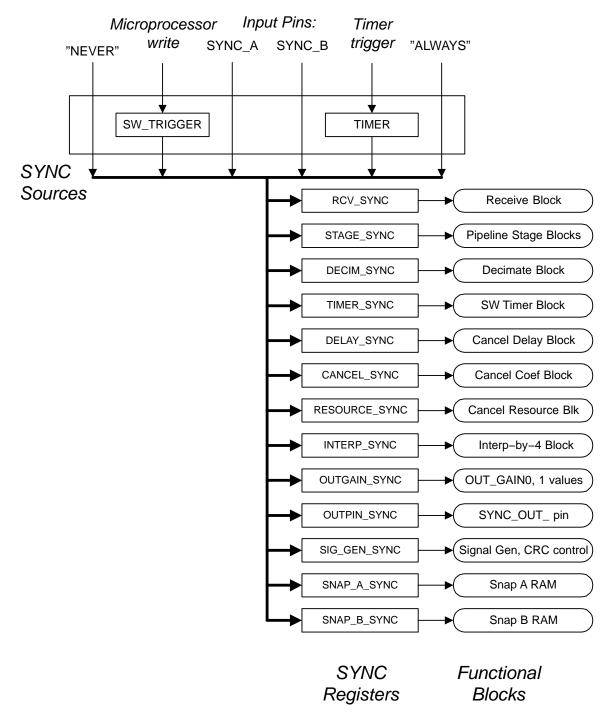

## **SYNC Registers**

The GC1115 contains a group of SYNC registers that control the behavior of thirteen different sync-related functions. A subsequent section discusses GC1115 synchronization alternatives. This section only describes the registers that must be properly initialized prior to GC1115 operation. Four datapath SYNC registers (RCV\_SYNC, STAGE\_SYNC, DECIM\_SYNC, and INTERP\_SYNC) **must** be synchronized by a hardware event before the GC1115 will process input samples. Four additional ancillary SYNC registers (DELAY\_SYNC, CANCEL\_SYNC, RESOURCE\_SYNC, and OUTGAIN\_SYNC) must be synchronized by a hardware or software event before the GC1115 properly applies cancellation coefficients and gains. TI recommends that the four datapath SYNC registers be synchronized using a SYNC\_A or SYNC\_B hardware event, and that the ancillary SYNC registers be synchronized using a SW\_TRIGGER software event. Note that the SYNC registers must be initialized BEFORE the corresponding hardware or software event occurs. For example, CANCEL\_SYNC must be initialized before the cancellation coefficients are transferred from the GC1115's shadow RAM to the internal canceler RAMs.

## TSQD (Threshold) and RESOURCE\_CNT Registers

The behavior of each PDC stage is controlled by two threshold registers (DETECT\_TSQDx and GAIN\_TSQDx) and one resource (RESOURCE\_CNTx) register, where x represents a specific stage (from 1 to 4). These 16-bit registers contain the scaled threshold-squared values for the stage's detection threshold and target peak level. The 16-bit RESOURCE\_CNT registers contain the number of cancellation resources (from 0 to 8) assigned to the stage. NOTE: if a RESOURCE\_CNT register is set to N ( $0 \le N \le 8$ ), that PDC stage can cancel up to  $4 \times N$  peaks simultaneously. A *resource* represents a canceler RAM. Up to four cancellation pulse generators are supported by each canceler RAM.

## **INTERP Registers**

A programmable output interpolator follows the GC1115's four PDC stages. The GC1115 interpolator operates in one of four modes:

- Bypass (the default condition)

- Interpolate by 2 (complex output)

- Interpolate by 2 (real output centered at fs/4)

- Interpolate by 4 (real output centered at fs/4)

The interpolator's filter coefficients are programmable and must therefore be initialized, even in *bypass* mode, before the GC1115 starts processing input samples. A total of 40 interpolator registers (from D0\_COEF0 thru D3\_COEF9) must be initialized before the GC1115 processes input data.

# **OUT\_GAIN** and **OUT\_OFFSET** Registers

The GC1115 output circuitry includes individual I and Q gain and offset registers that allow users to compensate for I/Q imbalances in subsequent D/A converters and/or subsequent analog I/Q modulators. Because the OUT\_GAIN and OUT\_OFFSET registers are user-programmable, they must be properly initialized before the GC1115 starts processing input samples. OUT\_GAIN registers are normally initialized to 0x2000 (gain of 1.0), and OUT\_OFFSET registers are usually initialized to 0x0000.

## CANCEL\_MODE, CANCEL\_LENGTH, CANCEL\_DELAY, Cancellation Coefficients

The GC1115 applies user-specified cancellation coefficients to detected peaks. Cancellation coefficients can contain either real or complex values, to support both symmetric and asymmetric input spectra. For this reason, the CANCEL\_MODE, CANCEL\_LENGTH, and CANCEL\_DELAY registers must be properly initialized before the GC1115 begins processing input samples. The cancellation coefficients themselves (in either real or complex format) must be copied to the GC1115 canceler RAMs in a two-step process:

- The microprocessor or FPGA writes the cancellation coefficients to memory-mapped shadow RAM registers

- The shadow RAM registers are copied to one or more (of a total of eight) cancellation pulse SRAMs after a CANCEL\_SYNC event occurs.

The CANCEL\_MODE register determines whether the GC1115 is using real or complex coefficients (corresponding to a symmetric or an asymmetric input spectrum), as well as whether coefficient symmetry is to be exploited. Coefficient symmetry (mirrored coefficients) only applies when using real coefficients. The CANCEL\_MODE register also contains a four-bit field that indicates a timeout or hysteresis value. A non-zero timeout value indicates that the PDCs are to examine the envelope of the input signal, rather than the magnitude of the input signal. TI-provided Matlab cancel pulse design software automatically calculates the timeout value.

The CANCEL\_LENGTH register specifies the number of unique cancellation coefficients used to cancel peaks. The CANCEL\_MODE register settings affect the interpretation of CANCEL\_LENGTH. The following table describes how CANCEL\_LENGTH and CANCEL\_DELAY are used, depending on CANCEL\_MODE:

Table 2. Relationship Between CANCEL\_MODE, CANCEL\_LENGTH, and CANCEL\_DELAY

| CANCEL_MODE               | CANCEL_LENGTH           | CANCEL_DELAY |

|---------------------------|-------------------------|--------------|

| 0 (Real, unique coefs)    | N (odd, from 15 to 255) | (N-1)/2      |

| 1 (Real, mirrored coefs)  | N (odd, from 15 to 255) | N            |

| 1 (Complex, unique coefs) | N (odd, from 15 to 127) | (N-1)/2      |

### **OPERATING MODES**

The GC1115 supports a variety of operating modes that accommodate a range of input formats, number of channels, and follow-on A/D converter and transmit architectures. Users select a specific input and output operating mode that depends upon:

- The number of channels (one or two)

- The input sampling rate:

- Up to 130 Msamp/sec in 1-channel mode

- Up to 65 Msamp/sec in 2-channel mode

- Down to 25 Msamp/sec in 1-channel parallel mode

- Down to 12.5 Msamp/sec in 1-channel multiplexed mode, or in 2-channel mode

- The input format (parallel or multiplexed)

- The input decimation factor (1, 2, or 4)

- The output interpolator mode (bypass, 2x real, 2x complex, 4x real)

- The output format (parallel, multiplexed, or odd-even; real or complex)

- The internal GC1115 clock rate (up to 320 MHz)

- The PLL multiplier (1x, 2x, or 4x)

The following constraints restrict the allowed combinations of the previously listed parameters:

- 1. Maximum input pin toggling rate: 130 MHz

- 2. Maximum output pin toggling rate in single-ended mode: 130 MHz

- 3. Maximum internal GC1115 clock rate: 305 MHz (IN\_CLK x1, x2, x4)

- 4. Minimum PLL-driven internal GC1115 clock rate (at divide-by-1 PLL output): 100 MHz

- 5. Minimum IN\_CLK rate: 25 MHz (using the 4x PLL multiplier with IN\_CLK = 25 MHz generates the 100 MHz minimum PLL output rate, at divide-by-1 PLL output)

Table 3 and Table 4 summarize the available one-channel and two-channel operating modes of the GC1115, respectively.

**Table 3. One-Channel Operating Modes**

| INPUT FOR-<br>MAT | OUTPUT<br>FORMAT | DECIM | INTERP | PLL MULT | IN_CLK<br>(MHz) | CORE CLK<br>(MHz) | OUT_CLK<br>(MHz) | f <sub>s</sub> /4 (MHz) |

|-------------------|------------------|-------|--------|----------|-----------------|-------------------|------------------|-------------------------|

| Parallel          | Parallel         | 1     | 1      | 4        | 25 - 75         | 100 - 305         | 25 - 80          | NA                      |

| Parallel          | Parallel         | 1     | 2c     | 4        | 25 - 65         | 100 - 260         | 50 - 130         | NA                      |

| Parallel          | Parallel         | 2     | 1      | 2        | 50 - 130        | 100 - 260         | 25 - 65          | NA                      |

| Parallel          | Parallel         | 2     | 2c     | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Parallel          | Muxed            | 1     | 1      | 4        | 25 - 65         | 100 - 260         | 50 - 130         | NA                      |

| Parallel          | Muxed            | 1     | 2c     | 4        | 25 - 32.5       | 100 - 305         | 100 - 130        | NA                      |

| Parallel          | Muxed            | 2     | 1      | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Parallel          | Muxed            | 2     | 2c     | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Parallel          | Odd/Even         | 1     | 2r     | 4        | 25 - 75         | 100 - 305         | 50 - 160         | 12.5 - 40               |

| Parallel          | Odd/Even         | 1     | 4r     | 4        | 25 - 75         | 100 - 305         | 100 - 250        | 25 - 62.5               |

| Parallel          | Odd/Even         | 2     | 2r     | 2        | 50 - 130        | 100 - 260         | 100 - 250        | 25 - 62.5               |

| Parallel          | Odd/Even         | 2     | 4r     | 2        | 50 - 130        | 100 - 260         | 100 - 250        | 25 - 62.5               |

| Muxed             | Parallel         | 1     | 1      | 2        | 50 - 130        | 100 - 260         | 25 - 65          | NA                      |

| Muxed             | Parallel         | 1     | 2c     | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Muxed             | Parallel         | 2     | 1      | 1        | 100 - 130       | 100 - 130         | 25 - 32.5        | NA                      |

| Muxed             | Parallel         | 2     | 2c     | 1        | 100 - 130       | 100 - 130         | 50 - 65          | NA                      |

| Muxed             | Muxed            | 1     | 1      | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Muxed             | Muxed            | 1     | 2c     | 2        | 50 - 65         | 100 - 130         | 100 - 130        | NA                      |

| Muxed             | Muxed            | 2     | 1      | 1        | 100 - 130       | 100 - 130         | 25 - 32.5        | NA                      |

| Muxed             | Muxed            | 2     | 2c     | 1        | 100 - 130       | 100 - 130         | 50 - 65          | NA                      |

| Muxed             | Odd/Even         | 1     | 2r     | 2        | 50 - 130        | 100 - 260         | 25 - 65          | 12.5 - 32.5             |

| Muxed             | Odd/Even         | 1     | 4r     | 2        | 50 - 130        | 100 - 260         | 50 - 130         | 25 - 32.5               |

| Muxed             | Odd/Even         | 2     | 2r     | 1        | 100 - 130       | 100 - 130         | 25 - 32.5        | 12.5 - 16.25            |

| Muxed             | Odd/Even         | 2     | 4r     | 1        | 100 - 130       | 100 - 130         | 50 - 65          | 25 - 32.5               |

# **Table 4. Two-Channel Operating Modes**

| INPUT<br>FORMAT | OUTPUT<br>FORMAT | DECIM | INTERP | PLL MULT | IN_CLK<br>(MHz) | CORE CLK<br>(MHz) | OUT_CLK<br>(MHz) | f <sub>s</sub> /4 (MHz) |

|-----------------|------------------|-------|--------|----------|-----------------|-------------------|------------------|-------------------------|

| Muxed           | Muxed            | 1     | 1      | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Muxed           | Muxed            | 1     | 2c     | 2        | 50 - 130        | 100 - 260         | 100 - 260        | NA                      |

| Muxed           | Muxed            | 2     | 1      | 1        | 100 - 130       | 100 - 130         | 50 - 65          | NA                      |

| Muxed           | Muxed            | 2     | 2c     | 1        | 100 - 130       | 100 - 130         | 100 - 130        | NA                      |

| Muxed           | Real             | 1     | 2r     | 2        | 50 - 130        | 100 - 260         | 50 - 130         | NA                      |

| Muxed           | Real             | 2     | 2r     | 1        | 100 - 130       | 100 - 130         | 50 - 130         | NA                      |

# **Clock Generation and PLL Operation**

The GC1115 internal clock is normally generated through an on-board PLL. The PLL output frequency is 1, 2, or 4 times the frequency of the user-provided IN\_CLK signal. For example, if the GC1115 is provided with an input signal stream at 61.44 Msamp/sec and the PLL is configured to operate at 4x, the GC1115's internal clock rate will be 245.76 MHz. The GC1115's functional blocks require four internal clock cycles per sample. This rule affects the selection of related decimation and interpolation factors at a given input sampling rate. In addition, the GC1115's PLL divide-by-1 output frequency must fall between 100 MHz and 305 MHz. The 100 MHz minimum PLL output clock rate is driven by the PLL design, while the 305 MHz maximum PLL output clock rate is limited by the GC1115's internal logic design. Alternately, the GC1115's internal PLL can be bypassed, effectively using IN\_CLK directly as the GC1115 chip clock. However, in this mode, each input sample must be presented to the input port(s) for four consecutive clock cycles, and the DECIM register must be set to 4. Using this *bypass PLL* configuration allows users to operate the GC1115 at input sampling rates lower than 25 Msamp/sec.

#### NOTE:

Users may have to adjust the clock phase, relative to the data, for proper operation during *bypass PLL* mode. Note that DECIM\_SYNC may also have to be enabled on a particular user-selected sample phase (1 of 4 phases) in order to achieve proper operation during bypass PLL mode.

GC1115 users should be aware that the choice of input operating mode affects IN\_CLK and thus also affects the PLL clock. Specifically, GC1115 users must ensure the relationships shown in Table 5:

|                 | ,        | ,                          |

|-----------------|----------|----------------------------|

| IN_CLK<br>(MHz) | PLL MODE | GC1115 CORE CLOCK<br>(MHz) |

| 25 - 75         | 4x       | 100 - 305                  |

| 50 - 130        | 2x       | 100 - 260                  |

| 100 - 130       | 1x       | 100 - 130                  |

| 1 - 125         | Bypass   | 1 - 125                    |

Table 5. IN CLK. PLL Mode, and Core Clock

GC1115 users should also be aware that the core clock affects the choice of output operating mode. Specifically, GC1115 users must ensure the relationships shown in Table 6. Notice that the odd-even output mode requires that the interpolator operate in one of its two real-output modes: 2x real or 4x real.

Table 6. Core Clock and Interp Mode

| GC1115 CORE CLOCK<br>(MHz) | INTERP MODE  | OUTPUT FORMAT | OUTPUT CLOCK RATE (MHz) |

|----------------------------|--------------|---------------|-------------------------|

| 100 - 305                  | Bypass       | Parallel      | 25 - 75                 |

| 100 - 260                  | Bypass       | Muxed I/Q     | 50 - 130                |

| 100 - 260                  | 2x (complex) | Parallel      | 50 - 130                |

| 100 - 130                  | 2x (complex) | Muxed I/Q     | 100 - 130               |

| 100 - 305                  | 2x (real)    | Odd/Even      | 25 - 75                 |

| 100 - 260                  | 4x (real)    | Odd/Even      | 50 - 130                |

## **Summary of Registers Affecting GC1115 Clocks**

The following GC1115 registers affect the input, core, and output clocks:

- PLL CONTROL (0x1): determines PLL multiplier (1x, 2x, 4x, bypass) and source of Tx feedback

- CLK\_CONTROL (0x2): determines relationship of IN\_CLK and OUT\_CLK to CORE\_CLK

- IO\_MODE (0x9): determines the number of channels (1 or 2), the input data format (parallel, muxed), and the output data format (parallel, muxed, odd-even)

- DECIMATE (0xC): determines the downsampling of the input stream prior to GC1115 processing

- INTERP\_CTL (0x80): determines the interpolator operating mode (bypass, 2x complex, 2x real, 4x real). Note that INTERP\_CTL and IO\_MODE must be consistent to ensure proper operation!

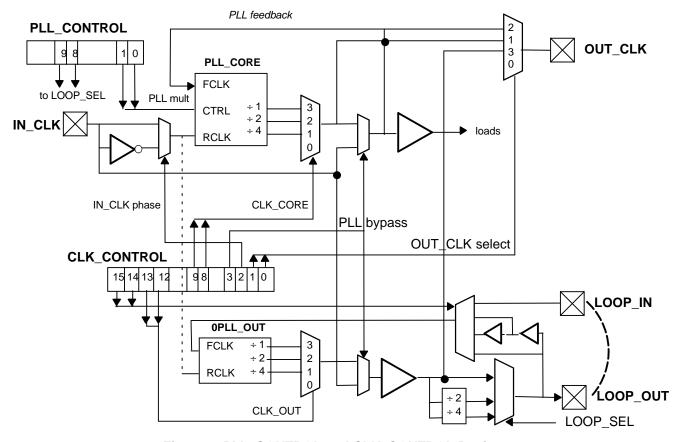

Figure 7 demonstrates the GC111 registers that determine the various internal clock frequencies.

Figure 7. PLL\_CONTROL and CLK\_CONTROL Registers

## **DETAILED DESCRIPTION OF GC1115 FUNCTIONAL BLOCKS**

## **Microprocessor Interface Registers and Interrupts**

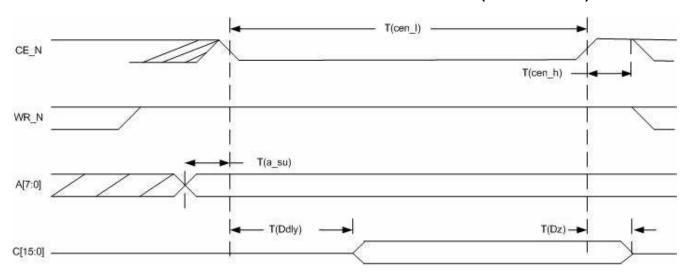

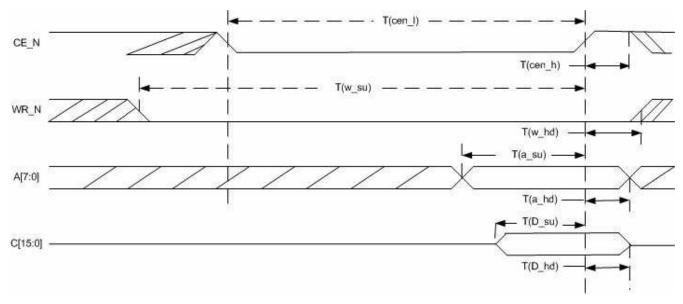

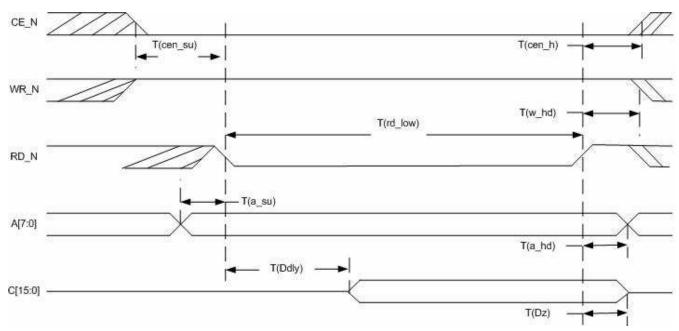

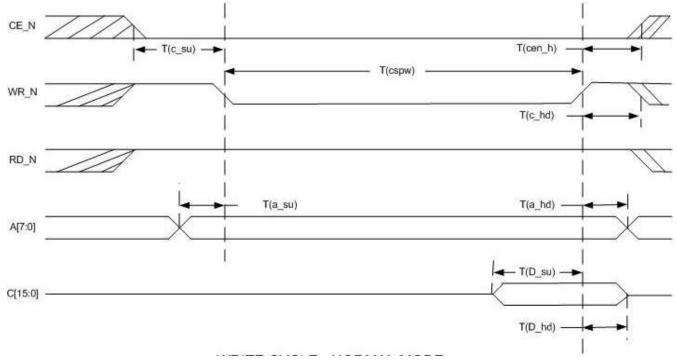

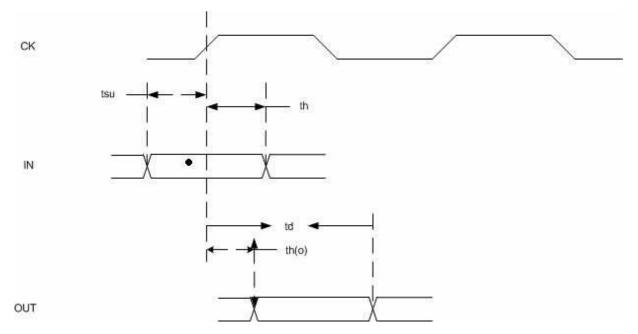

The GC1115's microprocessor interface presents the device as a set of memory-mapped registers to the controlling microprocessor or DSP. All aspects of the GC1115 are configured, monitored, and controlled through these registers. The microprocessor interface consists of a 16-bit bi-directional data bus D[15:0], an 8-bit address bus A[7:0], a write strobe  $\overline{WR}$ , a read strobe  $\overline{RD}$ , and a chip select  $\overline{CS}$ . The  $\overline{WR}$  pin selects between the two-pin and three-pin operation:

- (three-pin mode; WR is used) separate read strobe on RD pin and write strobe on WR pin

- (two-pin mode; WR is grounded) combined RD/WR signal using the GC1115's RD pin.

#### NOTE:

The GC1115 rev0 silicon does not support three-pin mode. Please use two-pin mode with rev0 silicon.

Figure 8 demonstrates a glueless interface between a generic Texas Instruments TMS320Cxx DSP chip and a GC1115, assuming that the CG1115 is the only device in the DSP's I/O memory space. If the TMS320Cxx DSP controls multiple devices in its I/O memory space, additional external address decoding is required to generate CS.

The microprocessor or DSP can configure the GC1115 to generate an interrupt at the occurrence of various GC1115 internal events. Please refer to the description of the INT\_MAP and INT\_MASK registers for a complete description of these events.

# **DETAILED DESCRIPTION OF GC1115 FUNCTIONAL BLOCKS (continued)**

The GC1115 microprocessor interface operates at speeds between 33 MHz and 100 MHz. Register read/write accesses are faster than RAM read/write accesses. RAM access is used for snapshot RAM and shadow RAM. Please refer to the timing diagrams for specific information on GC1115 register access rates. RAM access is limited to 33 MHz.

Figure 8. TMS320Cxx - GC1115 Interface

Users configure the GC1115 by writing control information into a set of 16-bit memory-mapped registers. The registers are accessed using the GC1115's A[7:0], D[15:0],  $\overline{\text{CS}}$ ,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  pins. The complete register map is described in detail in a subsequent section. Certain GC1115 registers can be modified at any time during GC1115 operation, while other registers may not be modified until certain conditions are met. Table 7 summarize these restrictions. The GC1115 will strictly enforce the update restrictions listed in Table 7. If a particular update condition is not met, the GC1115 will not update the specified register.

Table 7. GC1115 Register Updates

|           | Tuble 1. Go 1110 Register Spuares |                                                                  |  |  |  |  |

|-----------|-----------------------------------|------------------------------------------------------------------|--|--|--|--|

| ADDRESS   | NAME                              | WHEN CAN REGISTER BE UPDATED?                                    |  |  |  |  |

| 0         | RESET                             | Any time                                                         |  |  |  |  |

| 1         | PLL_CONTROL                       | Any time                                                         |  |  |  |  |

| 2         | CLK_CONTROL                       | Any time                                                         |  |  |  |  |

| 3         | CONTROL                           | Any time                                                         |  |  |  |  |

| 4         | INT_MAP                           | After GC1115 sends an interrupt                                  |  |  |  |  |

| 5         | INT_MASK                          | Any time                                                         |  |  |  |  |

| 6         | MASK_REV                          | READ ONLY                                                        |  |  |  |  |

| 7         | SW_TRIGGER                        | Any time                                                         |  |  |  |  |

| 8         | IO_CONTROL                        | Any time                                                         |  |  |  |  |

| 9         | IO_MODE                           | After GC1115 receives IN_CLK                                     |  |  |  |  |

| 10 (0xA)  | POWER_CTL                         | Any time                                                         |  |  |  |  |

| 11 (0xB)  | POWER                             | READ ONLY                                                        |  |  |  |  |

| 12 (0xC)  | DECIMATE                          | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 13 (0xD)  | TIMER_HI_RST                      | When timer is OFF                                                |  |  |  |  |

| 14 (0xE)  | TIMER_LO_RST                      | When timer is OFF                                                |  |  |  |  |

| 15 (0xF)  | CANCEL_MODE                       | Any time                                                         |  |  |  |  |

| 16 (0x10) | CANCEL_LENGTH                     | Any time                                                         |  |  |  |  |

| 17 (0x11) | CANCEL_ADDRESS                    | Any time                                                         |  |  |  |  |

| 18 (0x12) | CANCEL_DATA                       | Any time                                                         |  |  |  |  |

| 19 (0x13) | RESOURCE_MASK                     | Any time                                                         |  |  |  |  |

| 20 (0x14) | DELAY_MASK                        | Any time                                                         |  |  |  |  |

# **DETAILED DESCRIPTION OF GC1115 FUNCTIONAL BLOCKS (continued)**

# Table 7. GC1115 Register Updates (continued)

|            | Table 7. GC1115 Register Updates (continued) |                                                                  |  |  |  |  |

|------------|----------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| ADDRESS    | NAME                                         | WHEN CAN REGISTER BE UPDATED?                                    |  |  |  |  |

| 21 (0x15)  | SIG_GEN_CTL                                  | Any time                                                         |  |  |  |  |

| 22 (0x16)  | SIG_GEN_BASE                                 | Any time                                                         |  |  |  |  |

| 23 (0x17)  | SIG_GEN_INC                                  | Any time                                                         |  |  |  |  |

| 24 (0x18)  | CRC_RESULT                                   | Any time                                                         |  |  |  |  |

| 25 (0x19)  | RCV_SYNC                                     | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 26 (0x1A)  | STAGE_SYNC                                   | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 27 (0x1B)  | DECIM_SYNC                                   | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 28 (0x1C)  | TIMER_SYNC                                   | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 29 (0x1D)  | DELAY_SYNC                                   | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 30 (0x1E)  | CANCEL_SYNC                                  | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 31 (0x1F)  | RESOURCE_SYNC                                | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 32 (0x20)  | INTERP_SYNC                                  | Any time (after change, output may be invalid for a few samples) |  |  |  |  |

| 33 (0x21)  | OUTGAIN_SYNC                                 | Any time                                                         |  |  |  |  |

| 34 (0x22)  | OUTPIN_SYNC                                  | Any time                                                         |  |  |  |  |

| 35 (0x23)  | SIG_GEN_SYNC                                 | Any time                                                         |  |  |  |  |

| 36 (0x24)  | SNAP_A_SYNC                                  | Any time                                                         |  |  |  |  |

| 37 (0x25)  | SNAP_B_SYNC                                  | Any time                                                         |  |  |  |  |

| 48 (0x30)  | RESOURCE_CNT1                                | Any time                                                         |  |  |  |  |

| 49 (0x31)  | DETECT_TSQD1                                 | Any time                                                         |  |  |  |  |

| 50 (0x32)  | GAIN_TSQD1                                   | Any time                                                         |  |  |  |  |

| 51 (0x33)  | CANCEL_DELAY1                                | Any time                                                         |  |  |  |  |

| 56 (0x38)  | RESOURCE_CNT2                                | Any time                                                         |  |  |  |  |

| 57 (0x39)  | DETECT_TSQD2                                 | Any time                                                         |  |  |  |  |

| 58 (0x3A)  | GAIN_TSQD2                                   | Any time                                                         |  |  |  |  |

| 59 (0x3B)  | CANCEL_DELAY2                                | Any time                                                         |  |  |  |  |

| 64 (0x40)  | RESOURCE_CNT3                                | Any time                                                         |  |  |  |  |

| 65 (0x41)  | DETECT_TSQD3                                 | Any time                                                         |  |  |  |  |

| 66 (0x42)  | GAIN_TSQD3                                   | Any time                                                         |  |  |  |  |

| 67 (0x43)  | CANCEL_DELAY3                                | Any time                                                         |  |  |  |  |

| 72 (0x48)  | RESOURCE_CNT4                                | Any time                                                         |  |  |  |  |

| 73 (0x49)  | DETECT_TSQD4                                 | Any time                                                         |  |  |  |  |

| 74 (0x4A)  | GAIN_TSQD4                                   | Any time                                                         |  |  |  |  |

| 75 (0x4B)  | CANCEL_DELAY4                                | Any time                                                         |  |  |  |  |

| 96 (0x60)  | SNAP_A_CONTROL                               | Any time                                                         |  |  |  |  |

| 97 (0x61)  | SNAP_A_STATUS                                | READ ONLY                                                        |  |  |  |  |

| 98 (0x62)  | SNAP_A_ADDRESS                               | Any time                                                         |  |  |  |  |

| 99 (0x63)  | SNAP_A_DATA                                  | Any time                                                         |  |  |  |  |

| 100 (0x64) | SNAP_A_MINVAL                                | When Snap A is OFF                                               |  |  |  |  |

| 101 (0x65) | SNAP_A_MAXVAL                                | When Snap A is OFF                                               |  |  |  |  |

| 102 (0x66) | SNAP_A_SCALER                                | When Snap A is OFF                                               |  |  |  |  |

| 103 (0x67) | SNAP_A_HISTCOUNT                             | When Snap A is OFF                                               |  |  |  |  |

| 112 (0x70) | SNAP_B_CONTROL                               | Any time                                                         |  |  |  |  |

| 113 (0x71) | SNAP_B_STATUS                                | READ ONLY                                                        |  |  |  |  |

| 114 (0x72) | SNAP_B_ADDRESS                               | Any time                                                         |  |  |  |  |

| 115 (0x73) | SNAP_B_DATA                                  | Any time                                                         |  |  |  |  |

| 116 (0x74) | SNAP_B_MINVAL                                | When Snap B is OFF                                               |  |  |  |  |

# **DETAILED DESCRIPTION OF GC1115 FUNCTIONAL BLOCKS (continued)**

# Table 7. GC1115 Register Updates (continued)

| ADDRESS    | NAME             | WHEN CAN REGISTER BE UPDATED? |

|------------|------------------|-------------------------------|

| 117 (0x75) | SNAP_B_MAXVAL    | When Snap B is OFF            |

| 118 (0x76) | SNAP_B_SCALER    | When Snap B is OFF            |

| 119 (0x77) | SNAP_B_HISTCOUNT | When Snap B is OFF            |

| 127 (0x7F) | COUNTER_VAR      | Any time                      |

| 128 (0x80) | INTERP_CTL       | When interpolator is bypassed |

| 129 (0x81) | (reserved)       | (reserved)                    |

| 130 (0x82) | D0_COEF0         | When interpolator is bypassed |

|            |                  | •••                           |

| 169 (0xA9) | D3_COEF9         | When interpolator is bypassed |

| 192 (0xC2) | SOFT_LENGTH      | When soft limiter is bypassed |

| 193 (0xC3) | SOFT_TSQD        | When soft limiter is bypassed |

| 194 (0xC4) | SOFT_COEF0       | When soft limiter is bypassed |

|            |                  |                               |

| 209 (0xD1) | SOFT_COEF15      | When soft limiter is bypassed |

| 210 (0xD2) | SOFT_TAB_SCALE   | When soft limiter is bypassed |

| 211 (0xD3) | SOFT_INVGAIN0    | When soft limiter is bypassed |

|            |                  | •••                           |

| 242 (0xF2) | SOFT_INVGAIN31   | When soft limiter is bypassed |

| 243 (0xF3) | OUT_GAIN0        | When soft limiter is bypassed |

| 244 (0xF4) | OUT_GAIN1        | When soft limiter is bypassed |

| 245 (0xF5) | OUT_OFFSET_I0    | When soft limiter is bypassed |

| 246 (0xF6) | OUT_OFFSET_Q0    | When soft limiter is bypassed |

| 247 (0xF7) | OUT_OFFSET_I1    | When soft limiter is bypassed |

| 248 (0xF8) | OUT_OFFSET_Q1    | When soft limiter is bypassed |

# **Setting Detection Thresholds and Target Peak Levels**

The most obvious user-specified parameter for a CFR processor is the desired output PAR. The output PAR determines the largest sample magnitude on the output ports of the GC1115. Ultimately, the PAR determines the maximum Vin voltage of the PA. This maximum value is then adjusted to fit just under the 1 dB compression point of the PA. The average power of the GC1115 input samples (0 dB point on the CCDF curve) can be calculated from a group of input samples. TI provides a Matlab function that uses a group of input samples to calculate the 16-bit threshold-squared values that are loaded into the GC1115's DETECT\_TSQD and GAIN\_TSQD registers (one pair of registers for each of four stages; total of eight TSQD registers). Upon request, TI will provide the Matlab source code (m-file) for the threshold calculations based on input samples.

Alternately, GC1115 users can use the GC1115's built-in hardware power measurement capability to determine the average input power. The detection thresholds and target peak levels can then be calculated from the average input power.

GC1115 threshold settings are based on a threshold SQUARED (power) value, not a threshold (magnitude) value. The following example demonstrates how the GC1115's threshold-squared values are calculated, using the Matlab language:

```

Calculate the average power of the complex input array x, and the desired fractional (magnitude)

્ર

threshold, given the user-specified target peak level (in dB).

용

avgMag

= sqrt(mean(abs(x).^2));

frac

= avgMag * 10 ^ (dB_target /

્ટ્ર

Derive the following threshold-related values from the target PAR magnitude:

signed, 14-bit threshold value (a magnitude!)

્ર

thresh

threshSqd threshold set as a 16-bit mag-squared value (reduced from a 29-bit mag-squared value)

= floor (frac * 2^13);

% set the threshold relative to signed 14-bit samples

thresh

threshSqd = floor((thresh ^ 2)/(2^13)); % maq-sqd of a 14-bit value = 28 bits plus an add = 29

bits

% Divide by 2^13 to convert to 16-bit thresh-sqd value

```

The GC1115 uses four sequential PDC stages to achieve the desired output PAR. For output PAR levels below 8 dB, both cEVM and PCDE performance is improved if the earlier stages have higher detection thresholds (set to 8 dB or 7 dB), while later stages contain the final, desired threshold (7 dB, 6 dB, or 5 dB, for instance). In all cases, the GAIN\_TSQD registers should be set to the target peak level (desired output PAR). When the desired output PAR is at or above 8 dB, the DETECT\_TSQD and GAIN\_TSQD registers are set as shown in Table 8:

| STAGE | DETECT_TSQD | GAIN_TSQD |

|-------|-------------|-----------|

| 1     | my_tsqd     | my_tsqd   |

| 2     | my_tsqd     | my_tsqd   |

| 3     | my_tsqd     | my_tsqd   |

| 4     | my_tsqd     | my_tsqd   |

Table 8. Detection and Gain Thresholds, PAR ≥ 8 dB

When the desired output PAR is below 8 dB, the recommended DETECT\_TSQD and GAIN\_TSQD register settings are set as shown in Table 9:

Table 9. Detection and Gain Thresholds, PAR < 8 dB

| STAGE | DETECT_TSQD               | GAIN_TSQD |  |

|-------|---------------------------|-----------|--|

| 1     | min(8 dB, my_tsqd + 2 dB) | my_tsqd   |  |

| 2     | min(7 dB, my_tsqd+1 dB)   | my_tsqd   |  |

| 3     | my_tsqd                   | my_tsqd   |  |

| 4     | my_tsqd                   | my_tsqd   |  |

# **Designing Cancellation Pulse Coefficients**

Cancellation pulse coefficient design is identical to FIR filter design. The goal of designing cancellation pulses is to mirror the signal energy of the input signal. If the input signal contains one carrier, the cancellation pulse's center frequency and bandwidth will have the same center frequency and bandwidth as that carrier. For multi-carrier signals, multiple single-carrier cancellation pulses are added together to create a spectrum that is identical to the spectrum of the multi-carrier input signal. The goal of cancellation pulse design is to place energy ONLY in those frequency regions where the input signal has appreciable energy, i.e. in the carrier bands themselves. This design method ensures that cancellation pulse energy is inserted only where input signal energy is already present, and to avoid placing any additional energy outside those bands, since such out-of-band energy would worsen ACLR performance.

Upon request, TI will provide Matlab code that demonstrates how cancellation pulses are designed. This Matlab software requires the following input parameters:

- Input sampling rate

- Single-carrier bandwidth

- Carrier center frequencies

- Desired cancellation pulse length (an odd number; from 15 to 255 for real cancel pulses, and from 15 to 127 for complex cancel pulses)

The Matlab cancellation pulse design software then calls a standard Matlab FIR filter design function (such as fir1, firls, or remez) to design a prototype cancellation pulse whose bandwidth matches the single-carrier bandwidth input parameter. If the input signal contains two or more carriers, copies of this prototype filter will be translated to the center frequency of each carrier and the copies summed together.

### **Cancellation Coefficient Shadow RAM**

The GC1115 uses a derivative-based approximation method to calculate highly accurate phase shifts of the cancellation pulse. The approximation method requires not only the cancellation coefficients themselves to be stored in the GC1115, but also the coefficients' first and second derivatives. The cancellation coefficient shadow RAM contains 768 unique addresses that hold up to 256 unique cancellation coefficients and their first and second derivatives.

### NOTE:

Upon request, TI will provide a Matlab script that calculates the proper first and second derivatives from user-designed cancellation coefficients.

Shadow RAM is physically distinct from canceler RAM. This distinction is fully explained in the section entitled Shadow RAM and Canceler RAMs, below. The microprocessor or DSP controlling the GC1115 can only access the shadow RAM.

Cancellation coefficient shadow RAM is used differently, depending on the CANCEL\_MODE setting (real or complex coefficients; unique or mirrored coefficients). Table 10, Table 11, and Table 12 illustrate how cancellation coefficients are stored and accessed in the GC1115's cancellation coefficient shadow RAM.

Table 10. Real, Unique Coefficients

| TYPE OF DATA     | ADDRESS           | COEFFICIENT             |

|------------------|-------------------|-------------------------|

| Coefficients     | 0                 | coef[0]                 |

|                  | 1                 | coef[1]                 |

|                  | 2                 | coef[2]                 |

|                  |                   |                         |

|                  | CANCEL_LENGTH-1   | coef[CANCEL_LENGTH-1]   |

| First derivative | 256               | deriv1[0]               |

|                  | 257               | deriv1[1]               |

|                  | 258               | deriv1[2]               |

|                  |                   |                         |

|                  | 255+CANCEL_LENGTH | deriv1[CANCEL_LENGTH-1] |

Table 10. Real, Unique Coefficients (continued)

| TYPE OF DATA      | ADDRESS           | COEFFICIENT             |

|-------------------|-------------------|-------------------------|

| Second derivative | 512               | deriv2[0]               |

|                   | 513               | deriv2[1]               |

|                   | 514               | deriv2[2]               |

|                   |                   |                         |

|                   | 511+CANCEL_LENGTH | deriv2[CANCEL_LENGTH-1] |

# Coefficient access pattern:

coef[0], coef[1], ..., coef[CANCEL\_LENGTH-2], coef[CANCEL\_LENGTH-1]

**Table 11. Real, Mirrored Coefficients**

| TYPE OF DATA      | ADDRESS          | COEFFICIENT      |

|-------------------|------------------|------------------|

| Coefficients      | Same as Table 10 | Same as Table 10 |

| First derivative  | Same as Table 10 | Same as Table 10 |

| Second derivative | Same as Table 10 | Same as Table 10 |

## Coefficient access pattern:

$coef[0], \ coef[1], \ \dots, \ coef[CANCEL\_LENGTH-2], \ coef[CANCEL\_LENGTH-1], \ coef[CANCEL\_LENGTH-2], \ coef[CANCEL\_LENGTH-3], \dots, \ coef[0].$

**Table 12. Complex Coefficients**

| TYPE OF DATA                      | ADDRESS           | COEFFICIENT                |

|-----------------------------------|-------------------|----------------------------|

| Complex coefs (real part)         | 0                 | coef_re[0]                 |

|                                   | 1                 | coef_re[1]                 |

|                                   | 2                 | coef_re[2]                 |

|                                   |                   |                            |

|                                   | CANCEL_LENGTH-1   | coef_re[CANCEL_LENGTH-1]   |

| Complex coefs (imaginary part)    | 128               | coef_im[0]                 |

|                                   | 129               | coef_im[1]                 |

|                                   | 130               | coef_im[2]                 |

|                                   |                   |                            |

|                                   | 127+CANCEL_LENGTH | coef_im[CANCEL_LENGTH-1]   |

| First derivative (real part)      | 256               | deriv1_re[0]               |

|                                   | 257               | deriv1_re[1]               |

|                                   | 258               | deriv1_re[2]               |

|                                   |                   |                            |

|                                   | 255+CANCEL_LENGTH | deriv1_re[CANCEL_LENGTH-1] |

| First derivative (imaginary part) | 384               | deriv1_im[0]               |

|                                   | 385               | deriv1_im[1]               |

|                                   | 386               | deriv1_im[2]               |

|                                   |                   |                            |

|                                   | 383+CANCEL_LENGTH | deriv1_im[CANCEL_LENGTH-1] |

| Second derivative (real part)     | 512               | deriv2_re[0]               |

|                                   | 513               | deriv2_re[1]               |

|                                   | 514               | deriv2_re[2]               |

|                                   |                   |                            |

|                                   | 511+CANCEL_LENGTH | deriv2_re[CANCEL_LENGTH-1] |

### Table 12. Complex Coefficients (continued)

| TYPE OF DATA                       | ADDRESS           | COEFFICIENT                |

|------------------------------------|-------------------|----------------------------|

| Second derivative (imaginary part) | 640               | deriv2_im[0]               |

|                                    | 641               | deriv2_im[1]               |

|                                    | 642               | deriv2_im[2]               |

|                                    |                   |                            |

|                                    | 639+CANCEL_LENGTH | deriv2_im[CANCEL_LENGTH-1] |

### Coefficient access pattern:

{coef\_re[0], coef\_im[0]}, {coef\_re[1], coef\_im[1]}, ..., {coef\_re[CANCEL\_LENGTH-1], coef\_im[CANCEL\_LENGTH-1]}

## Writing Cancellation Coefficients to Shadow RAM

The GC1115 uses the CANCEL\_ADDR register as a coefficient memory pointer to access cancellation coefficient shadow RAM. This indirect addressing method requires only two registers (CANCEL\_ADDR and CANCEL\_DATA) in the GC1115 memory map, while allowing GC1115 users access to 768 unique shadow RAM addresses.

To access a particular shadow RAM location, the microprocessor or DSP that controls the GC1115 first writes the desired address into the CANCEL\_ADDR register. To write to the shadow RAM, the microprocessor or DSP then writes the desired coefficient value to the CANCEL\_DATA register. A write to (or read from) the CANCEL\_DATA register automatically post-increments the address in the CANCEL\_ADDR register. The following example demonstrates how the CANCEL\_ADDR auto-increment feature is used to initialize the first three cancellation coefficient shadow RAM locations mem(0), mem(1), and mem(2):

| STEP | REGISTER    | VALUE | CANCEL_ADDR<br>AUTO-INCREMENT | COMMENTS       |

|------|-------------|-------|-------------------------------|----------------|

| 1    | CANCEL_ADDR | 0     | 0                             | addr = 0       |

| 2    | CANCEL_DATA | 0x111 | 0->1                          | mem(0) = 0x111 |

| 3    | CANCEL_DATA | 0x456 | 1→2                           | mem(1) = 0x456 |

| 4    | CANCEL_DATA | 0x321 | 2-3                           | mem(2) = 0x321 |

Alternately, the microprocessor or DSP software can specify a shadow RAM address (0..767) with each CANCEL\_DATA access. This mode is useful when updating non-contiguous shadow RAM addresses. The following example demonstrates how the CANCEL\_ADDR direct-addressing mode is used to initialize the first three cancellation coefficient shadow RAM locations mem(0), mem(2), and mem(1), in non-sequential order (just to demonstrate the direct addressing capability):

| STEP | REGISTER    | VALUE | CANCEL_ADDR<br>AUTO-INCREMENT | COMMENTS       |

|------|-------------|-------|-------------------------------|----------------|

| 1    | CANCEL_ADDR | 0     | 0                             | addr = 0       |

| 2    | CANCEL_DATA | 0x111 | 0->1                          | mem(0) = 0x111 |

| 3    | CANCEL_ADDR | 2     | 2                             | addr = 2       |

| 4    | CANCEL_DATA | 0x321 | 2-3                           | mem(2) = 0x321 |

| 5    | CANCEL_ADDR | 1     | 1                             | addr = 1       |

| 6    | CANCEL_DATA | 0x456 | 1→2                           | mem(1) = 0x456 |

### **Shadow RAM and Canceler RAMs**

The GC1115 contains eight unique canceler RAM memories that hold cancellation coefficients and their derivatives. Each of the eight unique canceler RAMs can be accessed up to four times per IN\_CLK clock period, and each of the cancelers has its own canceler RAM pointer. This structure allows four cancelers to be supported by one canceler RAM per IN\_CLK clock period. This structure also makes it possible to store eight different cancellation coefficient sets in the GC1115 (although this option is not recommended). With a total of

eight canceler RAMs, the GC1115 can have up to 32 cancelers running independently per channel (four cancelers per canceler RAM per channel). Cancellation pulse resources are allocated in groups of four per channel, i.e. one canceler RAM at a time, to the four PDC stages. The registers RESOURCE\_CNT1 thru RESOURCE\_CNT4 specify how many canceler RAMs are allocated to each PDC stage. The total number of resources cannot exceed 8.

The CANCEL\_ADDR and CANCEL\_DATA registers are used to write to an independent "shadow RAM". Using the CANCEL\_ADDR and CANCEL\_DATA registers, the GC1115's controlling microprocessor or DSP writes cancellation coefficients and derivative values to this shadow RAM, and not directly to the canceler RAMs themselves. When a COEF\_SYNC synchronization event occurs, the contents of the shadow RAM are copied (one value per internal GC1115 clock cycle) to those canceler RAMs whose corresponding bit is set in the RESOURCE\_MASK register. Using the RESOURCE\_CNT registers, cancelers may be separately taken off-line, updated, and brought back on-line in seamless operation. This approach ensures that the GC1115 is never without cancellation resources.

To summarize, cancellation coefficients and their derivatives are written to canceler RAMs as follows:

- Using CANCEL\_ADDR and CANCEL\_DATA, write up to 768 canceler coefficients and their derivatives to shadow RAM

- 2. Using the RESOURCE\_MASK register, specify which canceler RAMs are to be initialized from shadow RAM when the COEF\_SYNC event occurs

- 3. Using the COEF\_SYNC register, specify which event (SW\_TRIGGER, timer, SYNC\_A, SYNC\_B, etc.) will trigger the COEF\_SYNC event

- 4. After the COEF\_SYNC event occurs, the GC1115 copies 3 × CANCEL\_LENGTH values from shadow RAM to the canceler RAMs selected by the RESOURCE\_MASK register. During each internal clock cycle, one shadow RAM value is copied simultaneously to the canceler RAMs enabled by their corresponding RESOURCE\_MASK bits. The total canceler RAM copy time depends on CANCEL\_LENGTH and on the time spent waiting for the selected RAMs to become idle, not on how many canceler RAMs are enabled for update in the RESOURCE\_MASK register.

- 5. After the GC1115 has copied 3 × CANCEL\_LENGTH values from shadow RAM to canceler RAM, the microprocessor or DSP can optionally be interrupted, if bit 6 of INT\_MASK was set prior to Step 3. Alternately, bit 6 of INT\_MAP can be polled to determine when the shadow RAM copy completes.